#### MAX22520

# One-Time Programmable (OTP) Industrial Sensor Output Driver

#### **General Description**

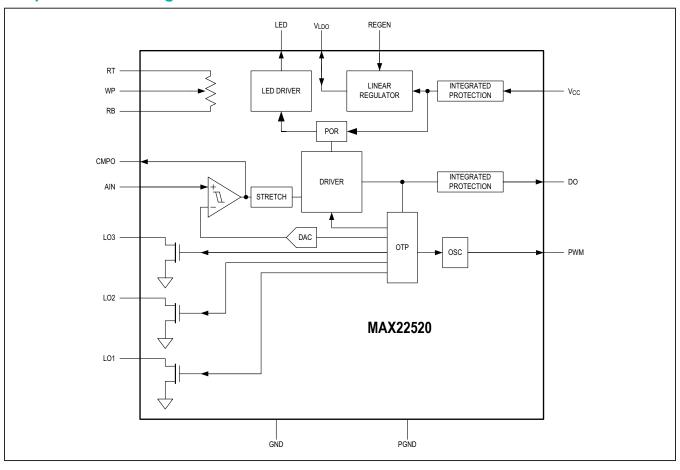

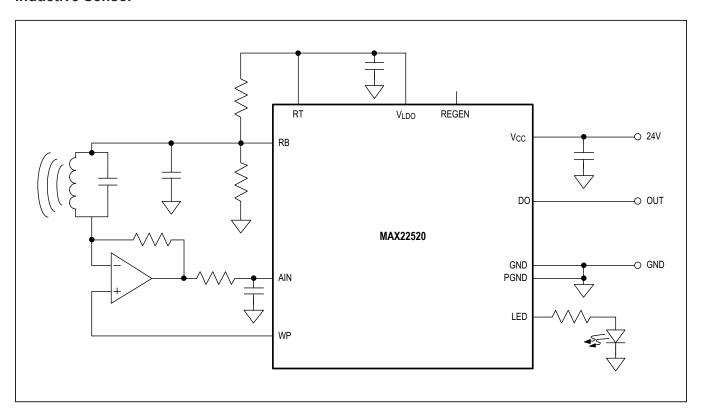

The MAX22520 24V line driver for industrial sensors incorporates a one-time programmable (OTP) analog interface for signal conditioning of binary switching sensors. Sensor calibration and configuration settings can be permanently programmed with the inline data interface using one-time programming (OTP). Additionally, an accurate integrated linear regulator provides a programmable (3.3V or 5V) low-noise supply for analog signal sensing circuitry.

The driver output (DO) is configurable using the Maxim<sup>®</sup> 1-Wire<sup>®</sup> protocol and an OTP interface to permanently operate in a normally-open or normally-closed state and in a high-side (PNP), low-side (NPN), or push-pull configuration. The maximum driver load current can be programmed to 100mA (min) or 200mA (min).

Configuration and OTP programming are done using  $V_{CC}$ , DO, and GND. This use of the standard three-wire interface pins simplifies programming at the end-of-line, when the sensor is already in its final housing.

The MAX22520 also features a programmable comparator, PWM oscillator, and digital potentiometer. These integrated functions further support sensor calibration for analog sensing circuitry. Additionally, an on-board LED driver provides visual feedback of the logic state of the sensor DO output.

Robust protection enables the MAX22520 to function in harsh industrial environments. DO,  $V_{CC}$ , and GND are all protected against hot-plug events,  $\pm 1 kV/500\Omega$  surge events, reverse-polarity, short circuits, and ESD strikes.

The MAX22520 operates from a wide 4.75V/8V to 36V supply and is available in a 20-bump wafer-level package (WLP) (2mm x 2.5mm, 0.5mm pitch). The device operates over the  $-40^{\circ}C$  to  $+105^{\circ}C$  temperature range.

## **Applications**

- Industrial Binary Sensors

- Proximity Switches

- Inductive and Magnetic Sensors

#### **Benefits and Features**

- High Configurability Supports a Wide Range of Sensor Designs

- Programmable Driver Configuration: High-Side (PNP), Low-Side (NPN), or Push-Pull

- Programmable Driver Current Limit: 100mA (min), 200mA (min)

- Programmable Linear Regulator Voltage: 3.3V (typ), 5V (typ)

- Input Comparator with Programmable Thresholds

- Digital Potentiometer with Programmable 6-bit Tap

- PWM Oscillator with Programmable Duty Cycles

- 4.75V/8V (min) to +36V Supply Voltage

- Integrated LED Driver for Visual Feedback

- Robust Design for Harsh Industrial Environments

- Reverse Polarity Protection on DO, V<sub>CC</sub>, and GND

- · Short Circuit Protection on DO

- · Thermal Shutdown Protection

- ±6kV IEC 61000-4-2 Air-Gap ESD Protection

- ±6kV IEC 61000-4-2 Contact Discharge ESD Protection

- $\pm 1 \text{kV} / 500 \Omega$  IEC 61000-4-5 Surge Protection

- -40°C to +105°C Operating Temperature Range

- 1µF Capacitive Load Drive Capability

- · Fast Demagnetization of Inductive Loads

- Small Form Factor for Compact Designs

- Ultra-Small (2mm x 2.5mm) 20-bump WLP

Ordering Information appears at end of data sheet.

1-Wire is a registered trademark of Maxim Integrated Products, Inc. Maxim is a registered trademark of Maxim Integrated Products, Inc.

# **Simplified Block Diagram**

### MAX22520

# One-Time Programmable (OTP) Industrial Sensor Output Driver

## **Absolute Maximum Ratings**

| All voltages referenced to GND unless otherwise specified. | RT, RB, WP0.3V to (V <sub>LDO</sub> + 0.3V)                   |

|------------------------------------------------------------|---------------------------------------------------------------|

| V <sub>CC</sub> 36V to +36V                                | Continuous Current into V <sub>CC</sub> and GND±1A            |

| PGND0.3V to +0.3V                                          | Continuous Current into DO±500mA                              |

| DO max[(V <sub>CC</sub> – 36V), -36V]                      | Continuous Current into Any Other Pin±50mA                    |

| to $min[(V_{CC} + 36V), +36V]$                             | Continuous Power Dissipation (Multilayer Board)               |

| REGEN0.3V to $min[(V_{CC} + 0.3V), +6V]$                   | (T <sub>A</sub> = +70°C, derate at 21mW/°C above +70°C)1500mW |

| $V_{LDO}$ 0.3V to min[( $V_{CC} + 0.3V$ ), +6V]            | Operating Temperature Range40°C to +105°C                     |

| LO1, LO2, LO3, CMPO,                                       | Junction Temperature+150°C                                    |

| AIN, PWM, LED0.3V to (V <sub>LDO</sub> + 0.3V)             | Storage Temperature Range40°C to +150°C                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

| PACKAGE TYPE: WLP20                    |                                |  |  |  |

|----------------------------------------|--------------------------------|--|--|--|

| Package Code                           | W201K2+1                       |  |  |  |

| Outline Number                         | 21-1000314                     |  |  |  |

| Land Pattern Number                    | Refer to Application Note 1891 |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD   |                                |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 47.6°C/W                       |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

### **Electrical Characteristics**

$(V_{CC} = V_{CC(MIN)})$  to 36V, GND = 0V,  $C_{LDO} = 0.1 \mu F$  to  $1.2 \mu F$ ,  $C_{LOAD}$  on DO = 1nF, REGEN is unconnected, all logic inputs at  $V_{LDO}$  or GND,  $T_A = -40 ^{\circ} C$  to +105°C, unless otherwise noted. Typical values are at  $V_{CC} = 24 V$  and  $T_A = +25 ^{\circ} C$ .) (Note 1)

| PARAMETER                                                                | SYMBOL                        | CONDITIONS                                                                      |                                                                     | MIN  | TYP | MAX | UNITS |

|--------------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------|------|-----|-----|-------|

| SUPPLY (V <sub>CC</sub> )                                                |                               |                                                                                 |                                                                     |      |     |     |       |

| O                                                                        | \ /                           | V <sub>LDO</sub> = 3.3V                                                         |                                                                     | 4.75 |     | 36  |       |

| Supply Voltage                                                           | V <sub>CC</sub>               | V <sub>LDO</sub> = 5V                                                           | V <sub>LDO</sub> = 5V                                               |      |     | 36  | V     |

| V <sub>CC</sub> Undervoltage Lockout                                     |                               | V <sub>CC</sub> rising,                                                         | V <sub>LDO</sub> = 3.3V                                             | 4.1  |     | 4.7 |       |

| (UVLO) Threshold                                                         | $V_{TH}$                      | DO active                                                                       | V <sub>LDO</sub> = 5V                                               | 6.0  |     | 7.0 | V     |

| V <sub>CC</sub> UVLO Threshold<br>Hysteresis                             | V <sub>HTH</sub>              | V <sub>LDO</sub> = 3.3V or 5V                                                   |                                                                     |      | 0.5 |     | V     |

| V <sub>CC</sub> UVLO Debounce Filter                                     | tuvlo_flt                     | V <sub>CC</sub> rising                                                          |                                                                     | 50   | 64  | 80  | μs    |

|                                                                          |                               | V <sub>CC</sub> = 24V,<br>no external load on<br>V <sub>LDO</sub> , LED is off, | Normal operation,<br>PWM enabled,<br>DO in NPN or<br>push-pull mode |      | 2.2 | 3.5 | A     |

| V <sub>CC</sub> Supply Current                                           | upply Current I <sub>CC</sub> | RT, WP, and RB are unconnected, no load on DO                                   | Slave mode<br>operation, PWM<br>disabled, DO is in<br>PNP mode      |      | 1.3 | 2.2 | - mA  |

| OTP PROGRAMMING MODE (\                                                  | / <sub>CC</sub> , DO)         | 1                                                                               |                                                                     |      |     |     |       |

| V <sub>CC</sub> Supply in 1-Wire Access Mode                             | V <sub>CC_OA</sub>            |                                                                                 |                                                                     | 3.5  |     | 4.1 | V     |

| I <sub>CC</sub> Supply Current in 1-Wire Access Mode                     | I <sub>CC_OA</sub>            |                                                                                 |                                                                     |      |     | 3   | mA    |

| V <sub>CC</sub> Supply 1-Wire RAM<br>Mode                                | V <sub>CC_OWA</sub>           |                                                                                 |                                                                     | 3.5  |     | 36  | V     |

| I <sub>CC</sub> Supply Current in<br>1-Wire RAM Mode                     | I <sub>CC_OWA</sub>           | 3.8V ≤ V <sub>CC</sub> ≤ 36V                                                    |                                                                     |      |     | 5   | mA    |

| V <sub>CC</sub> Supply During OTP Burn                                   | V <sub>CC_OB</sub>            |                                                                                 |                                                                     | 12   |     | 34  | V     |

| I <sub>CC</sub> Supply Current in OTP<br>Burn                            | I <sub>CC_OB</sub>            | V <sub>CC</sub> = V <sub>CC_OB</sub>                                            |                                                                     |      | 24  |     | mA    |

| DO Receiver Rising Input<br>Threshold                                    | V <sub>DO_RX_R</sub>          | 1-Wire OTP access and 1-Wire RAM                                                |                                                                     |      | 1.2 | 2   | V     |

| DO Receiver Falling Input<br>Threshold                                   | V <sub>DO_RX_F</sub>          | 1-Wire OTP access and 1-Wire RAM                                                |                                                                     | 0.6  | 1.1 |     | V     |

| Required External Pullup<br>Voltage on DO During 1-Wire<br>Communication | V <sub>DO_PU</sub>            | 1-Wire OTP access and 1-Wire RAM                                                |                                                                     |      |     | 5.5 | V     |

| DO Output Low Voltage During 1-Wire Communication                        | V <sub>OL</sub>               | 100Ω pullup between V <sub>CC</sub> = V <sub>DO_PU</sub>                        | DO and V <sub>CC</sub> ,                                            |      |     | 0.3 | V     |

$(V_{CC} = V_{CC(MIN)} \text{ to 36V, GND = 0V, } C_{LDO} = 0.1 \mu\text{F to } 1.2 \mu\text{F, } C_{LOAD} \text{ on DO = 1nF, REGEN is unconnected, all logic inputs at } V_{LDO} \text{ or GND, } T_{A} = -40 ^{\circ}\text{C to } +105 ^{\circ}\text{C, unless otherwise noted.}$

| PARAMETER                              | SYMBOL                 | CONDITIONS                                                                                      |                         | MIN  | TYP                      | MAX                      | UNITS |

|----------------------------------------|------------------------|-------------------------------------------------------------------------------------------------|-------------------------|------|--------------------------|--------------------------|-------|

| LINEAR REGULATOR (V <sub>LDO</sub> ,   | REGEN)                 |                                                                                                 |                         | '    |                          |                          |       |

| LDO Output Voltage                     | V <sub>LDO</sub>       | REGEN is uncon-<br>nected, V <sub>CC(MIN)</sub>                                                 | LDOVSET = 0             | 3.17 | 3.30                     | 3.43                     | V     |

| LDO Output Voltage                     | VLDO                   | $\leq$ V <sub>CC</sub> $\leq$ 36V,<br>I <sub>LOAD</sub> = 30mA                                  | LDOVSET = 1             | 4.8  | 5.0                      | 5.2                      | V     |

| External V <sub>I DO</sub> Supply      |                        | REGEN = GND,                                                                                    | LDOVSET = 0             | 2.3  | 2.47                     | 2.7                      |       |

| Power-OK Threshold                     | V <sub>LDO_</sub> OK   | V <sub>CC(MIN)</sub> ≤ V <sub>CC</sub> ≤ 36V (Note 2)                                           | LDOVSET = 1             | 3.6  | 3.75                     | 3.9                      | V     |

| External V <sub>LDO</sub> Supply       |                        | REGEN = GND,                                                                                    | LDOVSET = 0             | 1.9  | 2.07                     | 2.2                      | .,,   |

| Undervoltage Lockout Threshold Voltage | V <sub>LDO_UVLO</sub>  | $V_{CC(MIN)} \le V_{CC} \le$ 36V (Note 2)                                                       | LDOVSET = 1             | 3.2  | 3.35                     | 3.5                      | V     |

| LDO Short Circuit Current<br>Limit     | I <sub>LDO_SC</sub>    | V <sub>LDO</sub> shorted to GND                                                                 |                         | 35   |                          |                          | mA    |

| V <sub>I DO</sub> Change Over          | ΔV <sub>LDO</sub>      | I <sub>LOAD</sub> = 1mA,                                                                        | V <sub>LDO</sub> = 3.3V |      | 5.6                      |                          | mr\/  |

| Temperature                            |                        | -40°C ≤ T <sub>A</sub> ≤ 105°C                                                                  | V <sub>LDO</sub> = 5V   |      | 7.5                      |                          | - mV  |

| V <sub>LDO</sub> Line Regulation       |                        | 8V ≤ V <sub>CC</sub> ≤ 36V, I <sub>LOAD</sub> = 1mA                                             |                         |      | 1                        |                          | mV    |

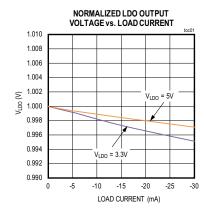

| V <sub>LDO</sub> Load Regulation       |                        | V <sub>LDO</sub> = 3.3V or 5V, 1mA ≤ I <sub>LOAD</sub> ≤ 30mA                                   |                         |      | 6                        |                          | mV    |

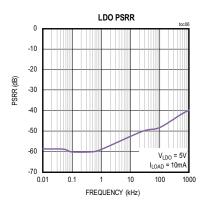

| LDO Power Supply<br>Rejection Ratio    | PSRR                   | I <sub>LOAD</sub> = 10mA, f = 100Hz, 500mV <sub>PP</sub>                                        |                         |      | 60                       |                          | μV    |

| DRIVER (DO)                            |                        |                                                                                                 |                         |      |                          |                          |       |

| DO High-Side On-Resistance             | R <sub>ON_H</sub>      | I <sub>SOURCE</sub> = 200mA                                                                     |                         |      | 2                        | 4.2                      | Ω     |

| DO Low-Side On-Resistance              | R <sub>ON_L</sub>      | I <sub>SINK</sub> = 200mA                                                                       |                         |      | 2                        | 4.2                      | Ω     |

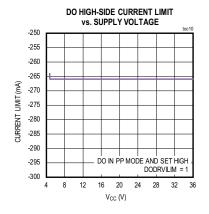

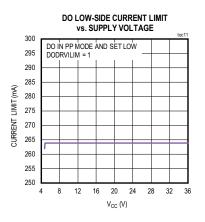

| DO Current Limit                       | lle e e l              | DO enabled                                                                                      | DOILIM = 0              | 110  | 132                      | 159                      | mA    |

| DO Current Limit                       | I <sub>DO_CL</sub>     | DO enabled                                                                                      | DOILIM = 1              | 220  | 264                      | 317                      |       |

| DO Leakage Current                     | I <sub>LKG_DO_PP</sub> | DO in push-pull mode impedance, 0V ≤ V <sub>DC</sub>                                            |                         | -12  |                          | +12                      | μА    |

| DO Weak Pulldown                       | I <sub>LKG_DO_HS</sub> | DO in PNP mode and high impedance,<br>0V ≤ V <sub>DO</sub> ≤ V <sub>CC</sub> , DOPUPD[1:0] = 10 |                         | +150 | +347                     | +450                     | μΑ    |

| DO Weak Pullup                         | lkg_do_ls              | DO in NPN mode and high impedance,<br>0V ≤ V <sub>DO</sub> ≤ V <sub>CC</sub> , DOPUPD[1:0] = 01 |                         | -450 | -320                     | -150                     | μA    |

| DO Output Negative<br>Clamp Voltage    | V <sub>CLN</sub>       | DO in PNP mode, 200mA clamp current flowing into DO                                             |                         |      | V <sub>CC</sub> -<br>42V | V <sub>CC</sub> -<br>36V | V     |

| DO Output Positive<br>Clamp Voltage    | V <sub>CLP</sub>       | DO in NPN mode, 200 flowing out of DO                                                           | OmA clamp current       | 36   | 42                       |                          | V     |

$(V_{CC} = V_{CC(MIN)} \text{ to 36V, GND = 0V, } C_{LDO} = 0.1 \mu\text{F to } 1.2 \mu\text{F, } C_{LOAD} \text{ on DO = 1nF, REGEN is unconnected, all logic inputs at } V_{LDO} \text{ or GND, } T_{A} = -40 ^{\circ}\text{C to } +105 ^{\circ}\text{C, unless otherwise noted.}$

| PARAMETER                                               | SYMBOL               | CONDITIONS                                                                                 |                                            | MIN | TYP  | MAX                       | UNITS  |

|---------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------|--------------------------------------------|-----|------|---------------------------|--------|

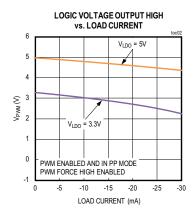

| LOGIC OUTPUTS (LO1, LO2, L                              | .03, CMPO, PW        | M, LED)                                                                                    |                                            |     |      |                           |        |

| Logic Output Low Voltage                                | V <sub>OL</sub>      | I <sub>SINK</sub> = 5mA                                                                    |                                            |     |      | 0.4                       | V      |

| Logic Output High Voltage                               | V <sub>OH</sub>      | LED, CMPO, PWM in Isource = 5mA                                                            | LED, CMPO, PWM in push-pull, ISOURCE = 5mA |     |      |                           | V      |

| Open-Drain Leakage                                      | ILEAK_LO             | LO1, LO2, LO3, PWM<br>output is high impedar<br>V <sub>OUT</sub> = V <sub>LDO</sub> or GND | nce,                                       | -1  |      | +1                        | μA     |

| COMPARATOR (AIN)                                        |                      |                                                                                            |                                            |     |      |                           |        |

| Number of OTP<br>Programmable Thresholds                | NV <sub>TH</sub>     | V <sub>T1</sub> , V <sub>T2</sub> (Note 4)                                                 |                                            |     | 2    |                           |        |

| Comparator Threshold Range                              | V <sub>TH_R</sub>    |                                                                                            |                                            | 0   |      | V <sub>LDO</sub><br>- 0.9 | V      |

| Comparator Threshold<br>Resolution in OTP               | V <sub>TH_RES</sub>  |                                                                                            |                                            |     | 6    |                           | Bits   |

| Comparator Threshold<br>Differential Nonlinearity (DNL) | V <sub>TH_DNL</sub>  |                                                                                            |                                            |     |      | +0.9                      | LSB    |

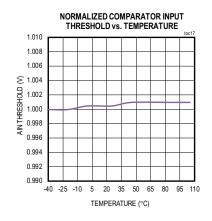

| Comparator Threshold<br>Temperature Variation           | ΔV <sub>TH</sub>     | Includes comparator and DAC,<br>REGEN = GND, 3.1V ≤ V <sub>LDO</sub> ≤ 5.2V<br>(Note 5)    |                                            | -9  |      | +9                        | mV     |

| PWM OSCILLATOR (PWM)                                    |                      |                                                                                            |                                            | '   |      |                           |        |

| Number of OTP<br>Programmable Duty Cycles               | NPWM <sub>DC</sub>   | (Note 6)                                                                                   |                                            |     | 2    |                           |        |

| Number of Programmable<br>PWM Duty Cycle Steps          | DC <sub>STEPS</sub>  | High-to-low/Open-to-c                                                                      | losed ratio                                |     | 512  |                           |        |

| PWM Duty Cycle Range                                    | DC <sub>RNG</sub>    | High-to-low/Open-to-c                                                                      | losed ratio                                | 0   |      | 99.8                      | %      |

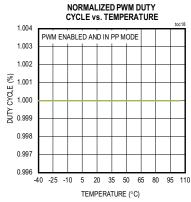

| PWM Duty Cycle Variation<br>Over Temperature            | ΔDC <sub>TMPCO</sub> |                                                                                            |                                            | 0   |      | 0                         | %      |

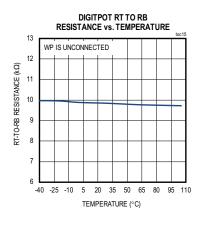

| DIGIPOT (RT, RB, WP)                                    |                      |                                                                                            |                                            |     |      |                           |        |

| End-to-End Resistance                                   | R <sub>EE</sub>      | RT to RB, WP unconnected                                                                   |                                            | 6.5 | 10   | 13.5                      | kΩ     |

| End-to-End Temperature<br>Coefficient                   | TC <sub>EE</sub>     | RT to RB, WP unconnected,<br>-40°C ≤ T <sub>A</sub> ≤ +105°C                               |                                            |     | -25  |                           | ppm/°C |

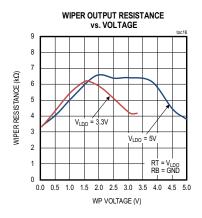

| Minor Output Immedans                                   | В                    | RT = V <sub>LDO</sub> ,                                                                    | V <sub>LDO</sub> = 3.3V                    |     |      | 7.6                       | kΩ     |

| Wiper Output Impedance                                  | R <sub>WP</sub>      | RB = GND                                                                                   | V <sub>LDO</sub> = 5V                      |     |      | 9                         | kΩ     |

| Wiper Output Impedance<br>Temperature Variation         | R <sub>WP_TC</sub>   | RT = V <sub>LDO</sub> , RB = GND,<br>I <sub>LOAD</sub> = 1µA on WP                         |                                            |     | 0.18 |                           | %/°C   |

$(V_{CC} = V_{CC(MIN)} \text{ to 36V, GND = 0V, } C_{LDO} = 0.1 \mu\text{F to } 1.2 \mu\text{F, } C_{LOAD} \text{ on DO = 1nF, REGEN is unconnected, all logic inputs at } V_{LDO} \text{ or GND, } T_{A} = -40 ^{\circ}\text{C to } +105 ^{\circ}\text{C, unless otherwise noted.}$

| PARAMETER                                        | SYMBOL              | CONDI                                                                                                 | TIONS                    | MIN  | TYP   | MAX  | UNITS |

|--------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------|--------------------------|------|-------|------|-------|

| Number of Programmable<br>Digipot Wiper Steps    | WP <sub>STEPS</sub> | Linear                                                                                                |                          |      | 64    |      |       |

| Wiper Setting Minimum Value                      | S <sub>MIN</sub>    | DIGIPOTSET[5:0] =                                                                                     | DIGIPOTSET[5:0] = 000000 |      |       |      | %     |

| Wiper Setting Maximum Value                      | S <sub>MAX</sub>    | DIGIPOTSET[5:0] = 111111                                                                              |                          |      | 100   |      | %     |

| Wiper Setting Differential<br>Nonlinearity (DNL) | RES <sub>DNL</sub>  |                                                                                                       |                          | -0.5 |       | +0.5 | LSB   |

| PROTECTION                                       |                     |                                                                                                       |                          |      |       |      |       |

| Thermal Shutdown                                 | T <sub>SHDN</sub>   | Junction temperature                                                                                  | e rising                 |      | +150  |      | °C    |

| Thermal Shutdown Hysteresis                      | T <sub>SH_HYS</sub> |                                                                                                       |                          |      | 15    |      | °C    |

| Reverse Polarity Current                         | I <sub>RP</sub>     | Any combination of \                                                                                  | CC, DO, and GND          |      | ±0.55 |      | mA    |

| ESD Protection                                   |                     | IEC 61000-4-2 Conta<br>C <sub>LOAD</sub> = 1nF on DO                                                  | 9                        |      | ±6    |      | 127   |

| (V <sub>CC</sub> , DO)                           |                     | IEC 61000-4-2 Airgap Discharge,<br>C <sub>LOAD</sub> = 1nF on DO                                      |                          |      | ±6    |      | - kV  |

| ESD Protection<br>(All Other Pins)               |                     | Human Body Model                                                                                      |                          | ±2   |       | kV   |       |

| SWITCHING CHARACTERISTI                          | CS / POWER OF       | N RESET (POR) TIMIN                                                                                   | IG                       |      |       |      |       |

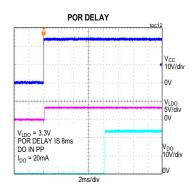

|                                                  |                     | Delay after V <sub>CC</sub> rises above V <sub>TH</sub> until DO and LED are active                   | PORDLY[1:0] = 00         | 6    | 8     | 10   | - ms  |

| DO 1 ED DOD D-1                                  | t <sub>PU_DO</sub>  |                                                                                                       | PORDLY[1:0] = 01         | 9    | 12    | 15   |       |

| DO, LED POR Delay                                |                     |                                                                                                       | PORDLY[1:0] = 10         | 12   | 16    | 20   |       |

|                                                  |                     |                                                                                                       | PORDLY[1:0] = 11         | 30   | 40    | 50   |       |

| POR Delay (All Other Pins)                       | t <sub>PU_O</sub>   |                                                                                                       |                          |      |       | 1    | ms    |

| SWITCHING CHARACTERISTI                          | CS / DO DRIVE       | R TIMING                                                                                              | ·                        |      |       |      |       |

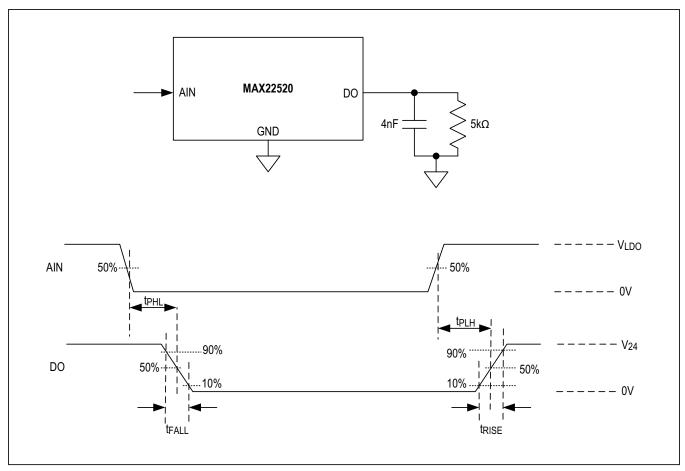

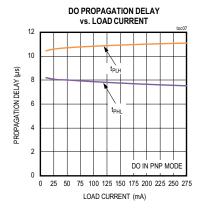

| Low-to-High Driver<br>Propagation Delay          | <sup>t</sup> PLH    | AIN to DO, $V_{CC}$ = 24V, $C_L$ = 4nF, $R_L$ = 5k $\Omega$ , to 50%, Push-pull or PNP mode, Figure 1 |                          |      | 9     | 16.5 | μs    |

| High-to-Low Driver<br>Propagation Delay          | <sup>t</sup> PHL    | AIN to DO, $V_{CC}$ = 24V, $C_L$ = 4nF, $R_L$ = 5k $\Omega$ , to 50%, Push-pull or NPN mode, Figure 1 |                          |      | 9     | 16.5 | μs    |

| DO Output Rise Time                              | <sup>t</sup> RISE   | $V_{CC}$ = 24V, $C_L$ = 4nF 90%, Push-pull mode                                                       |                          | 6    | 12    | μs   |       |

| DO Output Fall Time                              | tFALL               | $V_{CC}$ = 24V, $C_L$ = 4nF 10%, Push-pull mode                                                       |                          |      | 6     | 12   | μs    |

$(V_{CC} = V_{CC(MIN)})$  to 36V, GND = 0V,  $C_{LDO} = 0.1 \mu F$  to  $1.2 \mu F$ ,  $C_{LOAD}$  on DO = 1nF, REGEN is unconnected, all logic inputs at  $V_{LDO}$  or GND,  $T_A = -40 ^{\circ} C$  to  $+105 ^{\circ} C$ , unless otherwise noted. Typical values are at  $V_{CC} = 24 V$  and  $T_A = +25 ^{\circ} C$ .) (Note 1)

| PARAMETER                                                 | SYMBOL               | CONDITIONS                                                                                    | MIN | TYP  | MAX | UNITS |  |  |

|-----------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------|-----|------|-----|-------|--|--|

| SWITCHING CHARACTERISTI                                   | CS / DO DRIVE        | R PULSE STRETCH TIMING                                                                        |     |      |     |       |  |  |

| DO Stretched Pulse Length                                 | t <sub>PS</sub>      | DO pulse stretching enabled (PLSTEN = 1), AIN positive input pulse length < t <sub>PS</sub> . | 3.5 | 4.0  | 4.5 | ms    |  |  |

| SWITCHING CHARACTERISTICS / COMPARATOR TIMING (AIN, CMPO) |                      |                                                                                               |     |      |     |       |  |  |

| Comparator AIN to CMPO<br>Propagation Delay               | t <sub>COM_PD</sub>  | AIN to CMPO                                                                                   | 0.5 | 0.65 | 0.9 | μs    |  |  |

| AIN Rejected Input Pulse                                  | t <sub>PR</sub>      |                                                                                               | 0   |      | 200 | ns    |  |  |

| SWITCHING CHARACTERISTI                                   | CS / DO DRIVE        | R OVERCURRENT AUTORETRY TIMING                                                                |     |      |     |       |  |  |

| DO Overcurrent Detection<br>Time                          | tILIMDET             |                                                                                               |     | 500  |     | μs    |  |  |

| DO Overcurrent Turn-off Time                              | t <sub>ILIMOFF</sub> |                                                                                               |     | 50   |     | ms    |  |  |

| SWITCHING CHARACTERISTI                                   | CS / PWM OSCI        | LLATOR TIMING                                                                                 |     |      |     |       |  |  |

| PWM Oscillator Start-up Time                              | t <sub>PWM</sub>     | V <sub>CC</sub> rises above V <sub>TH</sub> to PWM active                                     |     | 64   |     | μs    |  |  |

| PWM Oscillator Center<br>Frequency                        | fPWM_C               |                                                                                               | 28  | 34   | 40  | kHz   |  |  |

| PWM Duty Cycle Switching<br>Delay                         | t <sub>PWM_SW</sub>  | Duty cycle switches after comparator logic output change                                      |     | 50   |     | μs    |  |  |

- Note 1: All devices are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design.

- Note 2: Program the LDOVSET bit in the OTP registers to set the UVLO threshold for V<sub>LDO</sub> when the internal regulator is disabled (REGEN = GND) and an external supply is connected to V<sub>LDO</sub>.

- **Note 3:** DO driver cannot be disabled during normal operation. When in push-pull configuration, the DO driver is in a high impedance state during thermal shutdown or during the power-on-reset (POR) delay.

- **Note 4:** Up to two comparator thresholds ( $V_{T1}$  and  $V_{T2}$ ) can be programmed in the OTP registers. If only one threshold is needed, set  $V_{T1} = V_{T2}$ . See the *Input Comparator (AIN, CMPO)* section for more information.

- Note 5: Not production tested. Guaranteed by design.

- Note 6: Up to two duty cycles (DC1 and DC2) can be programmed for the PWM output in the OTP registers. If only one duty cycle is needed, set DC1 = DC2. See the *PWM Oscillator* section for more information.

Figure 1. DO Driver Propagation Delays (Push-Pull Mode)

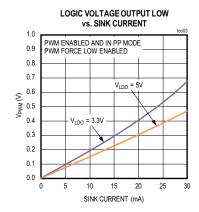

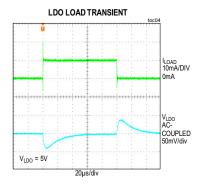

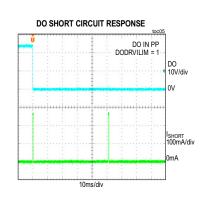

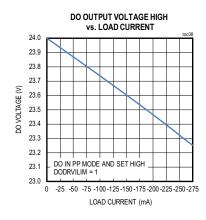

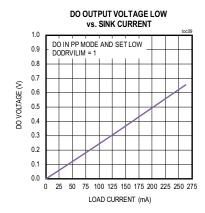

## **Typical Operating Characteristics**

$(V_{CC} = 24V, T_A = +25^{\circ}C, V_{LDO} \text{ unloaded})$

# One-Time Programmable (OTP) Industrial Sensor Output Driver

## **Typical Operating Characteristics (continued)**

$(V_{CC} = 24V, T_A = +25^{\circ}C, V_{LDO} \text{ unloaded})$

# **Pin Configuration**

# **Pin Description**

| PIN    | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER  |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A5     | V <sub>CC</sub>  | Supply Voltage. Bypass V <sub>CC</sub> to GND with a 10nF capacitor as close to the pin as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| B4     | GND              | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| B5     | PGND             | Power Ground. Connect PGND to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| LINEAR | REGULATO         | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| А3     | V <sub>LDO</sub> | LDO Supply Input/Linear Regulator Output. Bypass $V_{LDO}$ to GND with a 1µF capacitor. Leave REGEN unconnected to enable the internal regulator. $V_{LDO}$ can be 3.3V (typ) or 5V (typ) when the part is powered up and the part is not OTP programmed. Program the LDOVSET bit in the OTP registers to set $V_{LDO}$ to 3.3V (typ) or 5V (typ) when the internal regulator is enabled. Connect REGEN to GND to disable the internal regulator. Connect an external supply of 3.3V or 5V to $V_{LDO}$ when the internal regulator is disabled. Program the LDOVSET bit in the OTP registers to set the UVLO threshold for $V_{LDO}$ when the internal linear regulator is disabled and an external supply is connected to $V_{LDO}$ . |

| C4     | REGEN            | Linear Regulator Enable. Leave REGEN unconnected to enable the V <sub>LDO</sub> linear regulator.  Do not apply an external voltage to REGEN.  Connect REGEN to GND to disable the internal linear regulator. Apply an external 3.3V or 5V supply to V <sub>LDO</sub> when the internal regulator is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                          |

# **Pin Description (continued)**

| PIN               | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRIVER            |         |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D5                | DO      | Driver Output. DO is configurable in the OTP registers for PNP, NPN, push-pull, normally-open, or normally-closed operation. See the <u>Table 2. Logic Truth Table</u> and <u>OTP Register Map</u> for more information.  DO is the 1-Wire I/O when programming OTP registers or when the device is in OTP-transparent RAM mode. See the <u>One-Time Programming (OTP)</u> section for more information. |

| СОМРА             | RATOR   |                                                                                                                                                                                                                                                                                                                                                                                                          |

| D2                | AIN     | Analog Input of the Internal Comparator. Program up to two comparator thresholds (V <sub>T1</sub> , V <sub>T2</sub> ) in the OTP registers. See the <u>Table 2. Logic Truth Table</u> and <u>OTP Register Map</u> for more information.                                                                                                                                                                  |

| D4                | CMPO    | Comparator Logic Output.                                                                                                                                                                                                                                                                                                                                                                                 |

| LED DR            | IVER    |                                                                                                                                                                                                                                                                                                                                                                                                          |

| C5                | LED     | Push-pull Logic LED Driver Output. Connect an LED and current limiting resistor between LED and GND. See the <i>Table 2. Logic Truth Table</i> for more information.                                                                                                                                                                                                                                     |

| DIGIPO"           | Γ       |                                                                                                                                                                                                                                                                                                                                                                                                          |

| A1                | WP      | Digipot Wiper. Set the internal digipot resistance at WP by programming the DIGIPOTSET[5:0] bits in OTP. See the OTP Register Map for more information.                                                                                                                                                                                                                                                  |

| A2                | RT      | Digipot Top Terminal. Connect RT to V <sub>LDO</sub> or another external voltage.                                                                                                                                                                                                                                                                                                                        |

| A4                | RB      | Digipot Bottom Terminal. Connect RB to a voltage between GND and V <sub>RT</sub> .                                                                                                                                                                                                                                                                                                                       |

| LOGIC             | OUTPUTS |                                                                                                                                                                                                                                                                                                                                                                                                          |

| B1                | LO1     | Open-drain Logic Output 1. Set the LO1CFG[1:0] bits in the OTP registers to configure LO1 operation. See the OTP Register Map for more information.                                                                                                                                                                                                                                                      |

| C1                | LO2     | Open-drain Logic Output 2. Set the LO2CFG[2:0] bits in the OTP registers to configure LO2 operation. See the OTP Register Map for more information.                                                                                                                                                                                                                                                      |

| D1                | LO3     | Open-drain Logic Output 3. Set the LO3CFG bit in the OTP registers to configure LO3 operation. See the OTP Register Map for more information.                                                                                                                                                                                                                                                            |

| D3                | PWM     | Internal PWM Oscillator Output. Program the OTP registers to configure the PWM output for open-drain or push-pull operation and to set the duty cycle(s). See the <a href="https://orror.org/press/register/map">OTP Register Map</a> for more information.                                                                                                                                              |

| B2, B3,<br>C2, C3 | I.C.    | Internally Connected. Do not connect.                                                                                                                                                                                                                                                                                                                                                                    |

# One-Time Programmable (OTP) Industrial Sensor Output Driver

#### **Detailed Description**

The MAX22520 24V driver is optimized for use in 3-wire sensors operated in harsh industrial environments. Integrated analog interface I/Os are included to support sensor signal generation and signal conditioning for sensing circuitry.

This device is configurable through one-time programming (OTP) using a 1-Wire interface with the  $V_{CC}$ , DO, and GND pins. OTP programming can be done at the end-of-line, during sensor calibration and test. The 1-Wire interface allows the user to set analog and logic parameters (PWM duty cycles, comparator thresholds, and an integrated digipot). During programming, the comparator output (CMPO) logic state is available, providing a logic-level representation of the binary sensor output, allowing on-board calibration.

#### **OTP Configurable Functions**

<u>Table 1</u> shows the OTP configurable functions in the MAX22520. Two OTP banks are available to configure the device. Note that each OTP bank must be burnt

individually, in a separate burn step. See the <u>One-Time</u> Programming (OTP) section for more information.

#### LDO Linear Regulator (V<sub>LDO</sub>)

The MAX22520 includes an integrated programmable 3.3V/5V linear regulator output,  $V_{LDO}$ . Leave REGEN unconnected to enable the internal regulator. Set the LDOVSET bit in the OTP registers to 0 to set  $V_{LDO}$  = 3.3V (typ). Set LDOVSET = 1 to set  $V_{LDO}$  = 5V (typ).

V<sub>LDO</sub> can be 3.3V (typ) or 5V (typ) when the part is powered up and the part is not OTP programmed.

Connect REGEN to GND to disable the internal regulator. Apply an external voltage of 3.3V or 5V to  $V_{LDO}$  when the internal regulator is disabled. A voltage must be present on  $V_{LDO}$  when REGEN = GND for normal operation. Program the LDOVSET bit in the OTP registers to set the UVLO threshold for  $V_{LDO}$  when the internal regulator is disabled and an external supply is connected to  $V_{LDO}$ .

The logic outputs (LO1, LO2, LO3, PWM, and CMPO) and the internal comparator are referenced to  $V_{LDO}$  and GND.

**Table 1. OTP Configurable Functions**

| FUNCTION                                            | PROGRAMMABLE OPTIONS                                | OTP<br>BANK |

|-----------------------------------------------------|-----------------------------------------------------|-------------|

| V <sub>LDO</sub> Linear Regulator<br>Output Voltage | 3.3V<br>5V                                          | 1           |

| AIN Comparator                                      | VT1, VT2 Thresholds<br>Output Polarity              | 1           |

| DO Pulse<br>Stretching                              | Enable/Disable<br>Pulse Polarity                    | 1           |

| PWM<br>Configuration                                | Enable/Disable<br>Configuration<br>Normal Operation | 1           |

| Digipot<br>Resistance                               | 0kΩ to 10kΩ<br>Dependencies                         | 1           |

| LO1 Open-Drain<br>Logic Output                      | Static Low<br>Static High<br>Dependencies           | 1           |

| POR Delay                                           | 8ms<br>12ms<br>16ms<br>40ms                         | 1           |

| FUNCTION                          | PROGRAMMABLE OPTIONS                                      | OTP<br>BANK |

|-----------------------------------|-----------------------------------------------------------|-------------|

| PWM Duty Cycle                    | DC1, DC2<br>Switching<br>Dependencies                     | 2           |

| LO2 Open-Drain<br>Logic Output    | Static Low<br>Static High<br>Fault Output<br>Dependencies | 2           |

| LO3 Open-Drain<br>Logic Output    | Static Low<br>Static High                                 | 2           |

| DO Driver<br>Configuration        | NPN<br>PNP<br>Push-Pull                                   | 2           |

| DO Driver<br>Operating State      | Normally-Open<br>Normally-Closed                          | 2           |

| DO Driver Weak<br>Pullup/Pulldown | Disabled<br>Weak Pullup<br>Weak Pulldown                  | 2           |

| DO Driver<br>Current Limit        | 100mA<br>200mA                                            | 2           |

## One-Time Programmable (OTP) **Industrial Sensor Output Driver**

#### Input Comparator (AIN, CMPO)

A configurable integrated comparator provides the input signal that drives the DO driver output. The PWM output, digipot wiper position, and the logic states of the LO1 and LO2 outputs can also be configured to be dependent on the comparator output.

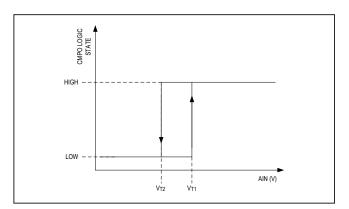

AIN is the input of the comparator. Two comparator thresholds (V<sub>T1</sub>, V<sub>T2</sub>) can be programmed in the OTP registers to define the switching hysteresis.

CMPO is a logic-level comparator output. CMPO can be programmed in the OTP registers to be in-phase or inverted compared to AIN.

#### Comparator Threshold Voltages (V<sub>T1</sub>, V<sub>T2</sub>)

Two threshold voltages (V<sub>T1</sub>, V<sub>T2</sub>) can be programmed for the internal comparator, each with a 6-bit resolution relative to V<sub>LDO</sub>. Set the thresholds by programming the VT1SET[5:0] and VT2SET[5:0] bits in the OTP registers. Calculate the programmed threshold voltages using the following equation::

$$V_{T_{-}} = \frac{VT\_SET[5:0]}{63} \times V_{LDO}$$

VT SET are the 6-bit words programmed into the C1 OTP2 and C1\_OTP3 registers. The V<sub>T1</sub> and V<sub>T2</sub> thresholds must be in the range of the 0V to  $(V_{LDO}$  - 0.9V). If  $V_{T1}$  and  $V_{T2}$  are not the same, ensure that the  $V_{T1}$ threshold is greater than the  $V_{T2}$  threshold ( $V_{T1} \ge V_{T2}$ ).

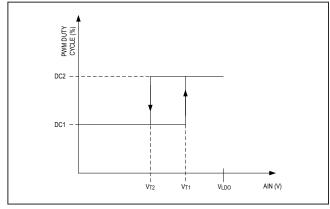

Multiple functions can be configured to depend on the AIN, V<sub>T1</sub>, and V<sub>T2</sub> voltages including the CMPO output, the state of the DO driver, and the PWM duty cycle. Figure 2 shows an example of the CMPO output operation when a comparator threshold and hysteresis are programmed.

To disable hysteresis, or if only one threshold is needed, set  $V_{T2} = V_{T1}$ .

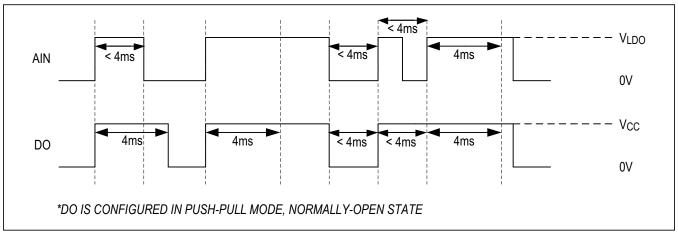

#### **Pulse Stretching**

When enabled in the OTP registers (PLSTEN = 1), positive or negative pulses received at AIN that are shorter than 4ms are stretched to 4ms (typ) at the output of the pulse stretcher circuitry. Pulses on DO are lengthened to match this output.

Select the AIN pulse polarity to be stretched at DO by setting the PLSTPOL bit in the OTP registers. Set PLSTPOL to 0 to stretch positive pulses on DO (PLSTEN = 1), as shown in Figure 3. Set PLSTPOL to 1 to stretch negative DO pulses on DO (PLSTEN = 1).

Very short pulses on AIN (< 200ns, max) are filtered out by the glitch filter that precedes the pulse stretcher and are not stretched when pulse stretching is enabled.

CMPO pulses are not stretched when pulse stretch is enabled.

Figure 2. Comparator Operation with Hysteresis

Figure 3. Sample Waveform with Positive Pulse Stretching

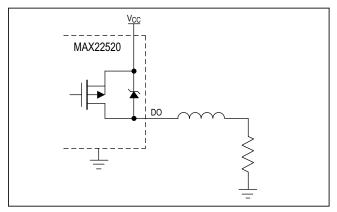

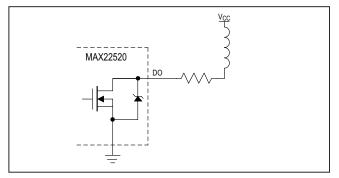

#### **Driver Output (DO)**

The DO driver output is configurable for high-side operation (PNP), low-side operation (NPN), or push-pull operation in a normally-open (NO) or normally-closed (NC) state in the OTP registers. An integrated LED output provides visual feedback of the state of DO at all times. See Table 2.

#### **DO Short Circuit Protection**

When the DO driver load current exceeds the programmed current limit threshold for longer than 500µs (typ), DO is disabled and the device enters autoretry mode. In autoretry mode, the driver is disabled for 50ms and then reenabled. If the fault condition is still present, the MAX22520 waits for 500µs (typ) and disables the driver again. The MAX22520 remains in autoretry mode until the fault condition is removed. The DO driver remains enabled and operates normally after the fault condition has been removed.

Select the DO driver current limit threshold to 100mA (min) or 200mA (min) by setting the DOILIM bit in the OTP registers.

**Table 2. Logic Truth Table**

| AIN            | D     |        |        |               |     |

|----------------|-------|--------|--------|---------------|-----|

| AIN<br>VOLTAGE | NO/NC | PNP    | NPN    | PUSH-<br>PULL | LED |

| L              | NO    | HIGH-Z | HIGH-Z | L             | OFF |

|                | NC    | Н      | L      | Н             | ON  |

| Н              | NO    | Н      | L      | Н             | ON  |

|                | NC    | HIGH-Z | HIGH-Z | L             | OFF |

Figure 4. High-Side Mode with Ground-Connected Load

#### **Driving Inductive Loads**

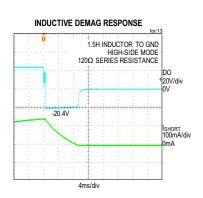

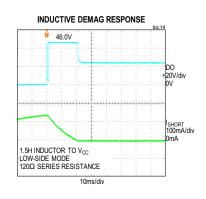

Inductive loads can be turned-off/demagnetized by the MAX22520 in NPN, PNP, and push-pull modes. The internal clamps on DO turn off both GND-connected and 24V-connected inductive loads fast due to their 42V (typ) positive clamping voltage and (V<sub>CC</sub> – 42V) (typ) negative clamping voltage. Inductive loads of up to 1.2H, with up to 200mA load current, can be turned off safely with supply voltages up to +36V.

#### Integrated Digipot (RT, RB, WP)

The MAX22520 features an integrated  $10k\Omega$  (typ) linear digital potentiometer that can be used for on-board sensor calibration. Connect the top of the digital potentiometer (RT) to V<sub>I DO</sub> or to another external voltage up to V<sub>I DO</sub>. Connect the bottom of the digital potentiometer (RB) to a voltage between ground and RT.

Setthewiperposition by programming the DIGIPOTSET[7:2] bits in the OTP registers. Calculate the voltage at WP using the following equation:

$$V_{WP} = \frac{\text{DIGIPOTSET[5:0]}}{64} \times (V_{RT} - V_{RB})$$

#### **LED Output**

The MAX22520 includes an integrated LED output for visual feedback on the state of the DO driver. The LED current source is on, when the DO driver is on (in PNP or NPN mode) or when DO is driven high in push-pull mode. See the Table 2. Logic Truth Table. The LED might turn on during power up while  $V_{CC} \le V_{CC}$  OA. The LED is guaranteed to be off for the power-on-reset POR delay (tpu DO) once VCC rises above the VCC OA.

#### **PWM Oscillator**

The MAX22520 features an internal 34kHz (typ) oscillator output, PWM. The PWM output is configurable in the OTP registers and is disabled by default.

Figure 5. Low-Side Mode with Supply-Connected Load

#### **Configuring the PWM Output**

The PWM oscillator is disabled by default but can be enabled and configured in the OTP registers. Set PWMEN to 1 to enable the PWM output. Set the PWMCFG bit to configure PWM as an open-drain or push-pull output. Set the PWM output permanently high, permanently low, or as a switching output by setting the PWMFH and PWMFL bits.

#### **PWM Duty Cycle**

The PWM output can be configured with up to two duty cycles (DC1 and DC2). Duty cycles can vary from 0% (min) to 99.8% (max) and have a 9-bit resolution. Calculate the duty cycle using the the following equation:

$$DC_{-} = \frac{PMWD_{-}[8:0]}{512} \times 100\%$$

During normal operation, the PWM duty cycle is determined by the state of the comparator AIN input voltage and programmed input voltage hysteresis (Figure 6). Set the  $V_{T1}$  and  $V_{T2}$  thresholds in the C1\_OTP2 and C1\_OTP3 registers.

Set DC1 = DC2, if only one duty cycle is required.

Use the following procedure to set the DC1 and DC2 duty cycles when the MAX22520 is in OTP-transparent RAM mode:

- 1) Write bit values to the C2\_OTP1 (0x1A) and/or C2\_ OTP2 (0x1B) registers to set the PWMD1[7:0] and/ or PWMD2[7:0] duty cycle bits.

- 2) Write bit values to the C2\_OTP0 (0x19) register.

Note that the C2 OTP0 (0x19) register must be written to after setting PWMD1[7:0] and/or PWMD2[7:0], even if the PWMD1[8] and/or PWMD2[8] bit values do not change. PWM duty cycles are not updated if step (2) is skipped.

#### **Voltage Transients**

Short-duration voltage transients that rise above the absolute maximum rating of the V<sub>CC</sub> pin occurs during ESD, surge, and hot plug events. With a 10nF bypass capacitor on the V<sub>CC</sub> line, the device is not damaged. Transients due to inductive kickback on DO when driving inductive loads up to 1.5H at 200mA or less may also bring the DO voltage above the absolute maximum rating, yet the device is not damaged. The absolute maximum ratings for V<sub>CC</sub> and DO should not be violated for any length of time by external sources.

#### **Thermal Protection**

Integrated circuitry protects the MAX22520 from thermal overload conditions. When the die temperature rises above 150°C (typ), the MAX22520 enters thermal shutdown and the DO driver, the LED driver, and the internal linear regulator (V<sub>I DO</sub>) are disabled. DO, LED, and V<sub>I DO</sub> are reenabled when the die temperatures fall below the 15°C thermal shutdown hysteresis to 135°C (typ).

#### **One-Time Programming (OTP)**

The MAX22520 features a high level of configurability through one-time programmable (OTP) registers. The state of the OTP bits are unknown if the part is powered up and has not been programmed. Once programmed, the selected functionality cannot be reprogrammed. Program the configurable options using the sensor interface pins (V<sub>CC</sub>, DO, and GND) and the 1-Wire interface protocol. For protocol information on the 1-Wire interface, refer to the design resources section on the 1-Wire Devices page and the 1-Wire tutorial video. The MAX22520 is only compatible with standard 1-Wire mode and requires a MSB-first data exchange.

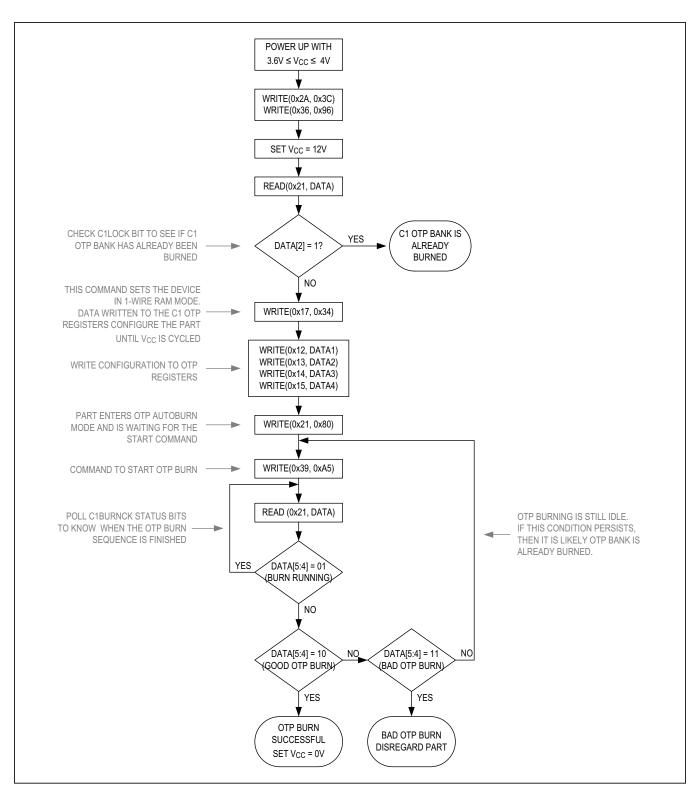

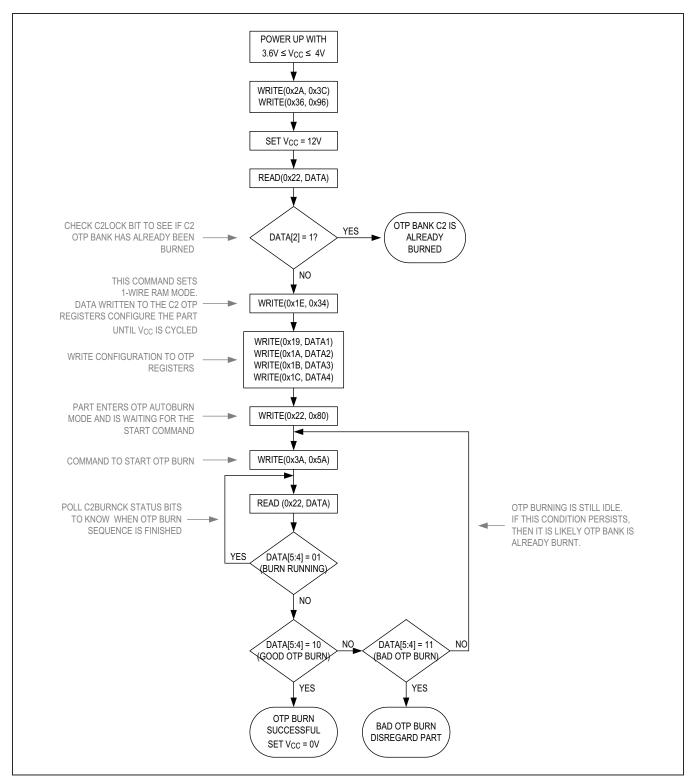

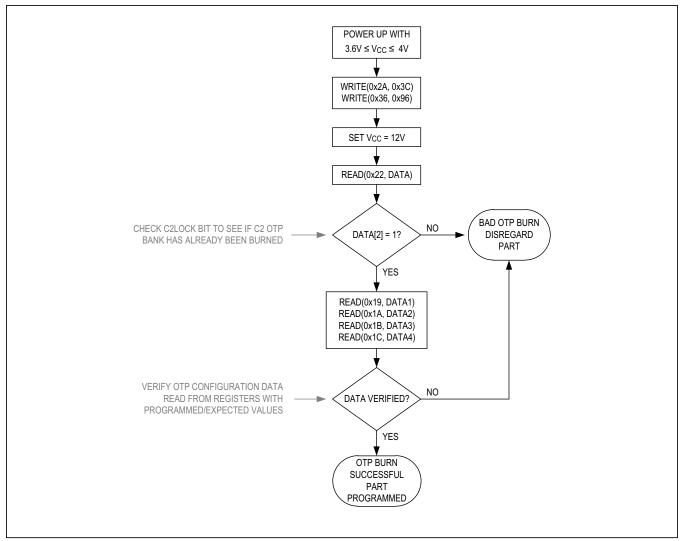

Two OTP banks are provided for all of the configurable options. Each OTP bank must be burnt individually, in a separate OTP burn. The flow charts in Figure 9 and Figure 10 outline the automatic OTP burn procedure.

Registers in the MAX22520 can be configured and verified by entering OTP-transparent mode before OTP is burned, or after. In this mode, all of the functionality, except DO. is available for programming. OTP registers return to their burned values (if already burned), or the default values (if not burned), when the  $V_{CC}$  supply is cycled.

#### 1-Wire Interface

Enable the 1-Wire interface for the MAX22520 by cycling the  $V_{CC}$  power supply to 0V and then raising  $V_{CC}$  to 3.8V (typ).

A 1-Wire access cycle is always initiated by the master controller sending a command byte that contains the access type (read or write) and the register address. The MAX22520 reads/writes the MSB first.

Figure 6. PWM Duty Cycle Hysteresis, Dependent on Comparator Thresholds

# One-Time Programmable (OTP) Industrial Sensor Output Driver

#### 1-Wire Write Byte

The first bit of the command byte is always 0 and is used by the MAX22520 as a START bit. Set the  $R/\overline{W}$  bit to 0 for write access. Send an 8-bit data byte after the command byte is sent (Figure 7).

#### 1-Wire Read Byte

1-Wire access is always initiated by the master controller. The first bit of the command byte is 0 and is used by the MAX22520 as a START bit. Set the  $R/\overline{W}$  bit to 1 for read access. The following bits in the command byte are the OTP register address.

The MAX22520 sends an 8-bit data byte to the master controller after the read command byte is received (<u>Figure 8</u>). The master must time the read slots during a read cycle.

#### **Entering OTP Mode**

To enter OTP mode, ensure the die temperature is at room temperature (25°C) and follow these steps:

1) Power cycle the MAX22520 and set the  $V_{CC}$  voltage between 3.5V and 4.1V. This enables the 1-Wire interface on the DO pin.

- Using the 1-Wire interface, write the RAM mode enable code (0x3C) to the 0x2A register. This write enables 1-Wire RAM mode, but the device does not yet enter RAM mode.

- 3) Write the RAM mode latch code (0x96) to the 0x36 register to enter RAM mode. At this point, the MAX22520 is set into RAM mode and V<sub>CC</sub> can be set to the normal operating voltage.

- Verify that the bank C1LOCK or C2LOCK bit is not set (indicating that the OTP has not been burned).

- Enter 1-Wire RAM mode to set the OTP register values and verify operation before OTP burn.

- Enable OTP autoburn functionality and send the command to start OTP burn.

The MAX22520 includes two OTP banks that must be burned individually, in separate burn steps, and the  $V_{CC}$  supply must be cycled after each burn. Figure 9 shows the burn sequence for the C1 OTP bank. Figure 10 shows the burn sequence for the C2 OTP bank.

| COMMAND BYTE (MASTER-TO-SLAVE) |       |       |                |                |       |       |              |  |

|--------------------------------|-------|-------|----------------|----------------|-------|-------|--------------|--|

| MSB<br>BIT 7                   | BIT 6 | BIT 5 | BIT 4          | BIT 3          | BIT 2 | BIT 1 | LSB<br>BIT 0 |  |

| START                          | R/W   | ADD5  | ADD4           | ADD3           | ADD2  | ADD1  | ADD0         |  |

|                                |       |       |                |                |       |       |              |  |

|                                |       |       | DATA BYTE (MA  | STER-TO-SLAVE) |       |       |              |  |

| MSB<br>BIT 7                   | BIT 6 | BIT 5 | DATA BYTE (MA: | STER-TO-SLAVE) | BIT 2 | BIT 1 | LSB<br>BIT 0 |  |

Figure 7. 1-Wire Write Byte

|              | COMMAND BYTE (MASTER-TO-SLAVE) |       |                |               |       |       |              |  |

|--------------|--------------------------------|-------|----------------|---------------|-------|-------|--------------|--|

| MSB<br>BIT 7 | BIT 6                          | BIT 5 | BIT 4          | BIT 3         | BIT 2 | BIT 1 | LSB<br>BIT 0 |  |

| START        | R/W                            | ADD5  | ADD4           | ADD3          | ADD2  | ADD1  | ADD0         |  |

|              |                                |       |                |               |       |       |              |  |

|              |                                |       | DATA BYTE (SLA | VE-TO-MASTER) |       |       |              |  |

| MSB<br>BIT 7 | BIT 6                          | BIT 5 | DATA BYTE (SLA | VE-TO-MASTER) | BIT 2 | BIT 1 | LSB<br>BIT 0 |  |

Figure 8. 1-Wire Read Byte

Figure 9. Bank 1 OTP Configuration Flow Chart

Figure 10. Bank 2 OTP Configuration Flow Chart

### **Verify OTP Burn**

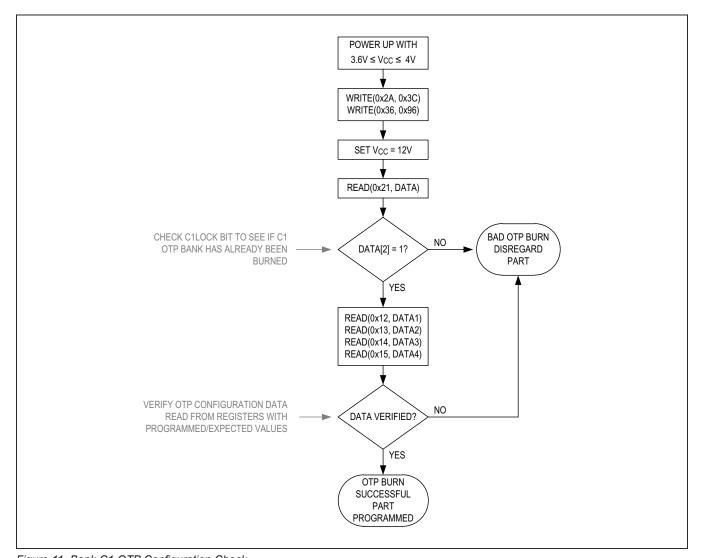

Once OTP burn is complete for the C1 or C2 banks, verify that the registers in the bank have been correctly programmed as shown in the <u>Figure 11</u> and <u>Figure 12</u> flow charts.

Figure 11. Bank C1 OTP Configuration Check

Figure 12. Bank C2 OTP Configuration Check

# **Register Map**

## **OTP Register Map**

| ADDRESS   | NAME             | MSB                             |                |        |          |             |         |              | LSB        |  |

|-----------|------------------|---------------------------------|----------------|--------|----------|-------------|---------|--------------|------------|--|

| OTP BANK1 | /BANK2           | l                               |                |        | l        |             |         |              |            |  |

| 0x00      | REV_ID[7:0]      |                                 |                |        | REVI     | D[7:0]      |         |              |            |  |

| 0x12      | C1_OTP0[7:0]     | DIGIPOTSET[5:0] PLSTEN LDOV SET |                |        |          |             |         | LDOV-<br>SET |            |  |

| 0x13      | C1_OTP1[7:0]     | PORD                            | LY[1:0]        | L01CF  | G[1:0]   | PWM-<br>CFG | PWMFH   | PWMFL        | PWMEN      |  |

| 0x14      | C1_OTP2[7:0]     | _                               | _              |        |          | VT1SI       | ET[5:0] |              |            |  |

| 0x15      | C1_OTP3[7:0]     | CMPO<br>POL                     | PLST-<br>POL   |        |          | VT2SI       | ET[5:0] |              |            |  |

| 0x17      | C1RAMEN[7:0]     |                                 |                |        | C1RAMM   | IODE[7:0]   |         |              |            |  |

| 0x19      | C2_OTP0[7:0]     | PWMD2<br>[8]                    | PWMD1<br>[8]   | DOILIM | DOPUI    | PD[1:0]     | DOST    | DOCF         | G[1:0]     |  |

| 0x1A      | C2_OTP1[7:0]     |                                 |                |        | PWMI     | 01[7:0]     |         |              |            |  |

| 0x1B      | C2_OTP2[7:0]     |                                 |                |        | PWME     | 02[7:0]     |         |              |            |  |

| 0x1C      | C2_OTP3[7:0]     | _                               | -              | _      | -        | LO3CFG      | L       | .02CFG[2:0   | O2CFG[2:0] |  |

| 0x1E      | C2RAMEN[7:0]     |                                 |                |        | C2RAMM   | IODE[7:0]   |         |              |            |  |

| 0x21      | C1_CHK[7:0]      | C1AU-<br>TOBURN                 | AINC-<br>MPOUT | C1BURI | NCK[1:0] | _           | C1LOCK  | _            | _          |  |

| 0x22      | C2_CHK[7:0]      | C2AU-<br>TOBURN                 | AINC-<br>MPOUT | C2BURI | NCK[1:0] | -           | C2LOCK  | _            | _          |  |

| 0x2A      | RAMMODEEN[7:0]   |                                 |                |        | RAME     | N[7:0]      |         |              |            |  |

| 0x36      | RAMMODEVAL[7:0]  |                                 | RAMVAL[7:0]    |        |          |             |         |              |            |  |

| 0x39      | C1_OTP_BURN[7:0] |                                 |                |        | C1BUF    | RN[7:0]     |         |              |            |  |

| 0x3A      | C2_OTP_BURN[7:0] |                                 |                |        | C2BUF    | RN[7:0]     |         |              |            |  |

## **Register Details**

## **REV\_ID** (0x00)

| BIT         | 7 | 6          | 5 | 4      | 3    | 2 | 1 | 0 |  |  |

|-------------|---|------------|---|--------|------|---|---|---|--|--|

| Field       |   | REVID[7:0] |   |        |      |   |   |   |  |  |

| Reset       |   | 0x02       |   |        |      |   |   |   |  |  |

| Access Type |   |            |   | Write, | Read |   |   |   |  |  |

| BITFIELD | BITS | DESCRIPTION   |

|----------|------|---------------|

| REVID    | 7:0  | Chip Revision |

## C1\_OTP0 (0x12)

| BIT         | 7 | 6               | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------|---|-----------------|---|---|---|---|---|---|

| Field       |   | DIGIPOTSET[5:0] |   |   |   |   |   |   |

| Reset       |   | 00000           |   |   |   |   |   |   |

| Access Type |   | Write, Read     |   |   |   |   |   |   |

| BITFIELD   | BITS | DESCRIPTION                                                                                                                                                    |

|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIGIPOTSET | 7:2  | Digipot Wiper Set Bits. Set the DIGIPOTSET[5:0] bits to set the resistance at WP. See the <u>Integrated Digipot (RT, RB, WP)</u> section for more information. |

| PLSTEN     | 1    | DO Pulse Stretch Enable 0 = Pulse stretching is disabled. 1 = Pulse stretching is enabled.                                                                     |

| LDOVSET    | 0    | Set the V <sub>LDO</sub> Output Voltage<br>0 = V <sub>LDO</sub> is 3.3V (typ)<br>1 = V <sub>LDO</sub> is 5V (typ)                                              |

# One-Time Programmable (OTP) Industrial Sensor Output Driver

# C1\_OTP1 (0x13)

| BIT         | 7      | 6           | 5      | 4           | 3           | 2           | 1           | 0           |

|-------------|--------|-------------|--------|-------------|-------------|-------------|-------------|-------------|

| Field       | PORD   | PORDLY[1:0] |        | L01CFG[1:0] |             | PWMFH       | PWMFL       | PWMEN       |

| Reset       | (      | )           | 0      | 0           | 0           | 0           | 0           | 0           |

| Access Type | Write, | Read        | Write, | Read        | Write, Read | Write, Read | Write, Read | Write, Read |

| BITFIELD | BITS | DESCRIPTION                                                                                                                                                                                                                                                                                                                     |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PORDLY   | 7:6  | Power-On Reset Delay Select<br>00 = 8ms<br>01 = 12ms<br>10 = 16ms<br>11 = 40ms                                                                                                                                                                                                                                                  |

| L01CFG   | 5:4  | L01 Open-Drain Logic Output Configuration 00 = Static low 01 = Static open 10 = L01 is set by the comparator output:         Comparator Output High: L01 is ON         Comparator Output Low: L01 is OFF 11 = L01 is set by the comparator output:         Comparator Output High: L01 is OFF Comparator Output Low: L01 is OFF |