### **General Description**

The MAX2307 is an integrated RF upconverter-driver optimized for the Japanese cellular frequency band. It can also be used for applications in the US cellular and ISM bands. Its low current consumption (15mA at -15dBm output) extends the average talk time.

The image rejection is done using only two external inductors at the upconverter output because the image frequency in Japanese cellular phones is typically 330MHz away. This realizes the image rejection with no current consumption penalty and only two inexpensive off-chip components, saving cost and valuable board space.

The MAX2307 has a separate shutdown control for the LO buffer to minimize VCO pulling. It comes in an ultrasmall 3×4 ultra-chipscale package (UCSP).

### Features

- Ultra-Small Implementation Size

- Low Off-Chip Component Count

- 15mA at -15dBm POUT

- 34mA at +6.5dBm POUT and -53dBc ACPR

- <1µA Shutdown Mode</p>

- Separate Shutdown for LO Buffer

- ♦ No External Logic Interface Circuitry Required

### Applications

Cellular Handsets cdmaOne™ Handsets ISM Band

### **Ordering Information**

| PART       | PART TEMP. RANGE PIN-P |          |

|------------|------------------------|----------|

| MAX2307EBC | -40°C to +85°C         | 3×4 UCSP |

-

cdmaOne is a trademark of CDMA Development Group.

###

\_ Maxim Integrated Products 1

For price, delivery, and to place orders, please contact Maxim Distribution at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

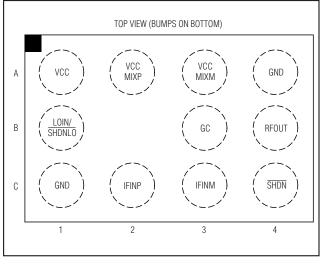

### **Pin Configuration**

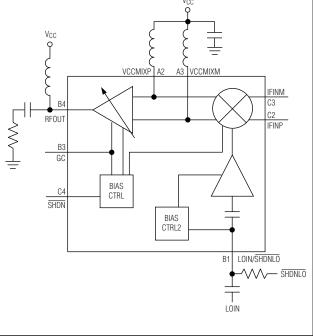

# Block Diagram

### ABSOLUTE MAXIMUM RATINGS

| V <sub>CC</sub> , RFOUT to GND           | 0.3V to +5.5V |

|------------------------------------------|---------------|

| SHDN to GND                              |               |

| RF, IF Input Power                       |               |

| Continuous Power Dissipation ( $T_A = +$ | 70°C)         |

| 3×4 UCSP (derate 80mW/°C above -         | +70°Ć)628mW   |

| Operating Temperature Range | 40°C to +85°C  |

|-----------------------------|----------------|

| Junction Temperature        | +150°C         |

| Storage Temperature Range   | 65°C to +160°C |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +2.8V \text{ to } +4.2V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ no RF/IF signals applied}, V_{\overline{SHDN}} = V_{\overline{SHDNLO}} = +1.8V.$  Typical values are at  $V_{CC} = +3.0V$ ,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted).

| PARAMETER                          | SYMBOL          | CONDITIONS                                                         | MIN | ТҮР  | MAX  | UNITS |

|------------------------------------|-----------------|--------------------------------------------------------------------|-----|------|------|-------|

| Supply Voltage                     | V <sub>CC</sub> |                                                                    | 2.8 |      | 4.2  | V     |

| Shutdown Supply Current            | Icc             | $\overline{\text{SHDN}} = \overline{\text{SHDNLO}} = 0.6 \text{V}$ |     | 0.1  | 20   | μA    |

| Standby Supply Current             | Icc             | $\overline{\text{SHDN}} = 0.6V, \overline{\text{SHDNLO}} = 1.8V$   |     | 2.5  | 4    | mA    |

|                                    |                 | $V_{GC} = 2.2V, P_{OUT} = +6.5dBm$                                 |     | 33.5 | 42   |       |

| Supply Current (Note 1)            | Icc             | $V_{GC} = 2.2V, P_{OUT} = +2dBm$                                   |     | 29.5 | 38   | mA    |

|                                    |                 | $V_{GC} = 0.5V$                                                    |     | 14   | 20   |       |

| Supply Current with No RF Drive    | ICC             | $V_{GC} = 2.2V$                                                    |     | 28   | 36.5 | mA    |

| Gain Control Voltage               | V <sub>GC</sub> |                                                                    | 0   |      | 3.0  | V     |

| SHDN, SHDNLO Logic High            |                 |                                                                    | 1.8 |      |      | V     |

| SHDN, SHDNLO Logic Low             |                 |                                                                    | 0   |      | 0.6  | V     |

| SHDN, SHDNLO Logic Current<br>High |                 |                                                                    |     |      | 1    | μA    |

| SHDN, SHDNLO Logic Current<br>Low  |                 |                                                                    | 1   |      |      | μA    |

### **AC ELECTRICAL CHARACTERISTICS**

(MAX2307 Evaluation Kit, V<sub>CC</sub> = +2.8V to +4.2V, T<sub>A</sub> = -40°C to +85°C, f<sub>RF</sub> = 887MHz to 925MHz, f<sub>LO</sub> = 722MHz to 760MHz, f<sub>IF</sub> = 165MHz, P<sub>IFIN</sub> = -20dBm, P<sub>LOIN</sub> = -15dBm, V<sub>SHDN</sub> = V<sub>SHDNLO</sub> = +1.8V, 50 $\Omega$  system. Typical values are at V<sub>CC</sub> = 3.0V, V<sub>SHDN</sub> = V<sub>SHDNLO</sub> = 1.8V, f<sub>RF</sub> = 906MHz, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                       | SYMBOL | CONDITIONS                                                                                  | MIN  | TYP  | MAX  | UNITS  |

|---------------------------------|--------|---------------------------------------------------------------------------------------------|------|------|------|--------|

| RF Frequency Range (Note 2)     |        |                                                                                             | 887  |      | 925  | MHz    |

|                                 |        | $V_{GC} = 2.2V, V_{CC} = 3.0V, T_A = +25^{\circ}C$                                          | 21.5 | 24.5 | 27.5 |        |

| Power Gain                      | G      | $V_{GC}$ = 2.2V, $V_{CC}$ = 2.8V to 4.2V, $T_{A}$ = $T_{MIN}$ to $T_{MAX}$                  | 17   | 24.5 | 32.5 | dB     |

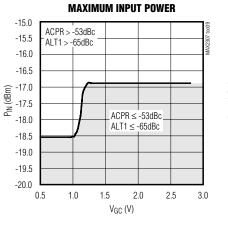

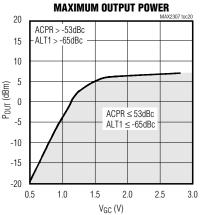

| Output Power                    | Pout   | $V_{GC} = 2.2V$ , ACPR $\leq$ -53dBc, ALT $\leq$ -65dBc                                     | 4.5  | 6.5  |      | dBm    |

| LO Input Power Level            |        |                                                                                             | -15  | -12  | -5   | dBm    |

| Gain Control Range              |        | $V_{GC}$ = 0.5V to 2.2V, $P_{IFIN}$ = -30dBm                                                | 18   | 23   |      | dB     |

| Gain Control Slope (Note 3)     |        | $V_{GC}$ = 0.5V to 2.2V, $P_{IFIN}$ = -30dBm                                                |      | 32   | 36   | dB/V   |

| Adjacent Channel Power Ratio    | ACPR1  | Offset = ±885kHz in 30kHz BW                                                                |      |      | -53  | dBc    |

| Alternate Channel Power Ratio   | ACPR2  | Offset = ±1.98MHz in 30kHz BW                                                               |      |      | -65  | dBc    |

| RX Band Noise Power<br>(Note 4) | Durana | $P_{OUT} = 6.5 dBm$                                                                         |      | -134 | -131 | dBm/Hz |

|                                 | PNOISE | $P_{IFIN} = -50 dBm$ , $V_{GC} = 0.5 V$                                                     |      | -147 |      |        |

| LO Leakage                      |        | POUT from +6.5dBm to -8dBm                                                                  |      | -43  | -30  | dBc    |

| Image Leakage (Note 1)          |        | $P_{OUT}$ from 6.5dBm to -8dBm, $f_{RF}$ = 887MHz to 925MHz, $f_{IMAGE}$ = 557MHz to 595MHz |      | -40  | -25  | dBc    |

Note 1: Minimum and maximum limits are guaranteed by design and characterization.

**Note 2:** See *Typical Operating Characteristics* for operation outside this frequency range.

Note 3: Slope measured with  $V_{GC}$  = +0.5V and  $V_{GC}$  = +0.8V.

**Note 4:**  $f_{RF} = 925MHz$ , noise measured at 870MHz.

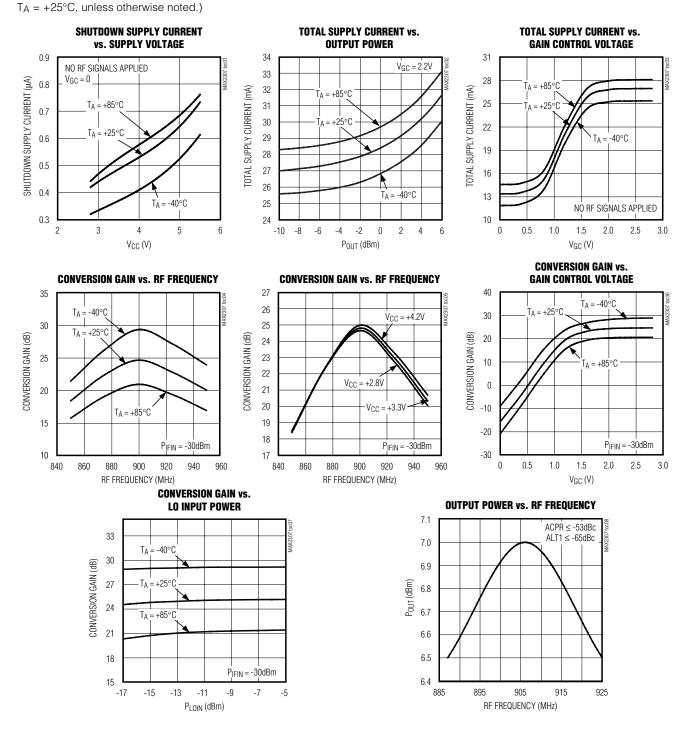

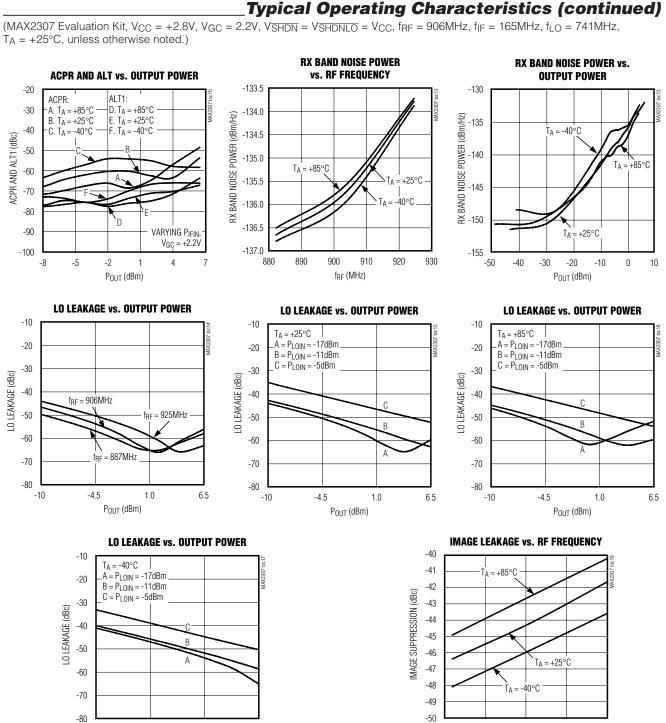

$(MAX2307 \text{ Evaluation Kit}, V_{CC} = +2.8V, V_{GC} = 2.2V, V_{\overline{SHDN}} = V_{\overline{SHDNLO}} = V_{CC}, f_{RF} = 906 \text{MHz}, f_{IF} = 165 \text{MHz}, f_{LO} = 741 \text{MHz}, f_{IC} = 741 \text$

**Typical Operating Characteristics**

M/IXI/M

885

895

905

RF FREQUENCY (MHz)

915

925

MAX2307

-10

-4.5

P<sub>OUT</sub> (dBm)

1.0

6.5

### Typical Operating Characteristics (continued)

$(MAX2307 \text{ Evaluation Kit}, V_{CC} = +2.8V, V_{GC} = 2.2V, V_{\overline{SHDN}} = V_{\overline{SHDNLO}} = V_{CC}, f_{RF} = 906 \text{MHz}, f_{IF} = 165 \text{MHz}, f_{LO} = 741 \text{MHz}, f_{IC} = 741 \text$  $T_A = +25^{\circ}C$ , unless otherwise noted.)

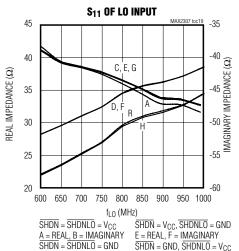

$<sup>\</sup>overline{SHDN} = \overline{GND}, \overline{SHDNLO} = V_{CC}$ C = REAL, D = IMAGINARY G = REAL, H = IMAGINARY

### **Pin Description**

| PIN    | NAME                | FUNCTION                                                                                                                                                                                                                                                       |  |  |

|--------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A1     | VCC                 | Supply Pin. Bypass with 100pF and $0.01\mu$ F capacitors as close to the pin as possible.                                                                                                                                                                      |  |  |

| A2, A3 | VCCMIXP,<br>VCCMIXM | Mixer Supply Pins. Require pullup inductors, which are used as part of the image rejection filter network. Supply to inductors should be locally bypassed with 100pF and 0.01µF capacitors.                                                                    |  |  |

| B1     | LOIN/<br>SHDNLO     |                                                                                                                                                                                                                                                                |  |  |

| B3     | GC                  | Gain Control Pin. Apply a voltage between 0 to 3V to vary the gain of the IC.                                                                                                                                                                                  |  |  |

| B4     | RFOUT               | PA Driver Output. Requires an inductor pullup and a DC-blocking capacitor. These components are also the matching elements.                                                                                                                                    |  |  |

| A4, C1 | GND                 | GND Connection. Solder directly to the PCB ground plane, with three ground vias around the corner of the UCSP, as close to bump as possible. It is imperative that GND sees a low inductance to the system ground plane. See the MAX2307 EV Kit as an example. |  |  |

| C2, C3 | IFINP,<br>IFINM     | Upconverter IF Inputs. AC-couple IF signals to these pins.                                                                                                                                                                                                     |  |  |

| C4     | SHDN                | Shutdown Control. HIGH turns on the device except the LO buffer, LOW turns off the device except the LO buffer.                                                                                                                                                |  |  |

/N/IXI/N

# MAX2307

# **Low-Power Cellular Upconverter-Driver**

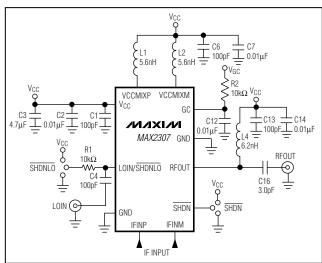

### **Typical Operating Circuit**

### \_Applications Information

### Local Oscillator LOIN/SHDNLO Input

The LO input is a single-ended broadband port. The LO signal is mixed with the input IF signal and the resulting upconverted output appears on the RFOUT pin. AC-couple the LO pin with a capacitor having less than  $3\Omega$  reactance at the LO frequency. This device also contains an internal LO buffer and supports an LO signal ranging from -15dBm to -5dBm.

SHDNLO turns the LO buffer on and off independent of the rest of the IC and shares the same pin as LOIN. To avoid loading of the LO, connect a 10k $\Omega$  isolation resistor between the LOIN/SHDNLO pin and the SHDNLO logic output. The SHDNLO control can help reduce VCO pulling in gated-transmission mode by providing a means to keep the LO buffer on while the upconverter and driver turn on and off.

**IF Input** The MAX2307 has a differential IF input port for interfacing to differential IF filters. AC-couple the IF pins with a capacitor. The typical IF input frequency is 165MHz, but device can operate from 130MHz to 230MHz. The differential impedance between the two IF inputs is approximately  $400\Omega$  in parallel with 0.5pF.

### Mixer

The MAX2307 uses a double-balanced differential upconverting mixer. Two inductors connecting the mixer output pins (A2 and A3) to V<sub>CC</sub> in conjunction with an on-chip capacitor achieve image suppression. This method allows image rejection with no current consumption penalty, and permits much higher Q than

///XI//

using on-chip inductors to ensure sufficient selectivity for image rejection. The Q of the off-chip tank inductor directly determines the image suppression level and usable bandwidth.

The MAX2307 also provides a continuous variable gain function, enabling at least 20dB of gain control using an external control voltage input.

**PA Driver**

The MAX2307 utilizes a class AB driver stage. Unlike class A or B, class AB action offers both good linearity and low current consumption. Current consumption of class AB is proportional to the output power at high drive levels.

RFOUT is an open-collector output that requires an external inductor to V<sub>CC</sub> for proper biasing. For optimum performance, implement an impedance-matching network. The configuration and values for the matching network depend on the transmit frequency, performance, and desired output impedance. For simultaneous optimum linearity and return loss, the real part of the load impedance should be about 100 $\Omega$ . The device's internal 0.5pF shunt parasitic needs to be absorbed by the matching network. For matching network values for the Japanese cellular transmit band, see the MAX2307 EV kit data sheet.

### Layout Issues

For best performance, pay close attention to powersupply issues, as well as to the layout of the RFOUT matching network. The EV kit can be used as a layout example. Ground connections and supply bypassing are the most important.

### Power Supply and SHDN\_ Bypassing

Bypass V<sub>CC</sub> with a 100pF capacitor in parallel with a  $0.01\mu$ F RF capacitor. Use separate vias to the ground plane for each of the bypass capacitors and minimize trace length to reduce inductance. Use three separate vias to the ground plane for each ground pin.

### **Power-Supply Layout**

To minimize coupling between different sections of the IC, the ideal power-supply layout is a star configuration with a large decoupling capacitor at a central V<sub>CC</sub> node. The V<sub>CC</sub> traces branch out from this central node, each going to a separate V<sub>CC</sub> node in the PC board. At the end of each trace is a bypass capacitor with low ESR at the RF frequency of operation. This arrangement provides local decoupling at each V<sub>CC</sub> pin. At high frequencies, any signal leaking out of one supply pin sees a relatively high impedance (formed by the V<sub>CC</sub> trace inductance) to the central V<sub>CC</sub> node, and an even higher impedance to any other supply pin, as

well as a low impedance to ground through the bypass capacitor.

**Impedance-Matching Network Layout** The RFOUT matching network is very sensitive to layout-related parasitics. To minimize parasitic inductance, keep all traces short and place components as close as possible to the chip. To minimize parasitic capacitance, minimize the area of the plane. **Chip Information**

TRANSISTOR COUNT: 693 PROCESS TECHNOLOGY: Silicon Bipolar

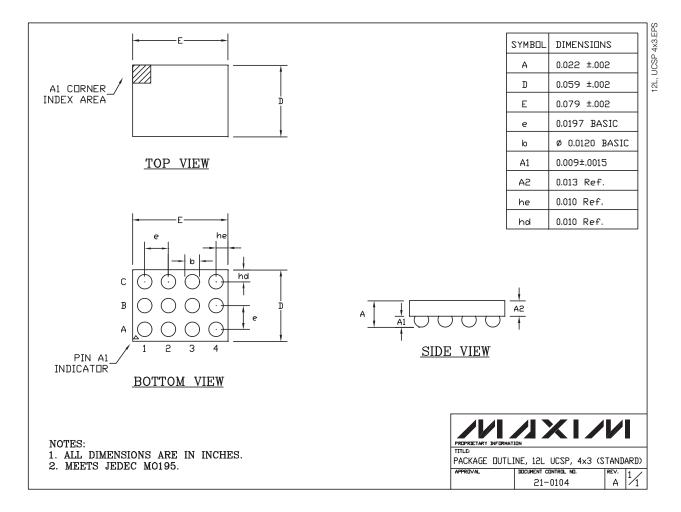

### **Package Information**