Click here to ask an associate for production status of specific part numbers.

#### MAX25222/MAX25222C

## Automotive 4-Channel TFT-LCD Power Supply with VCOM Buffer and ASIL B Features

#### **General Description**

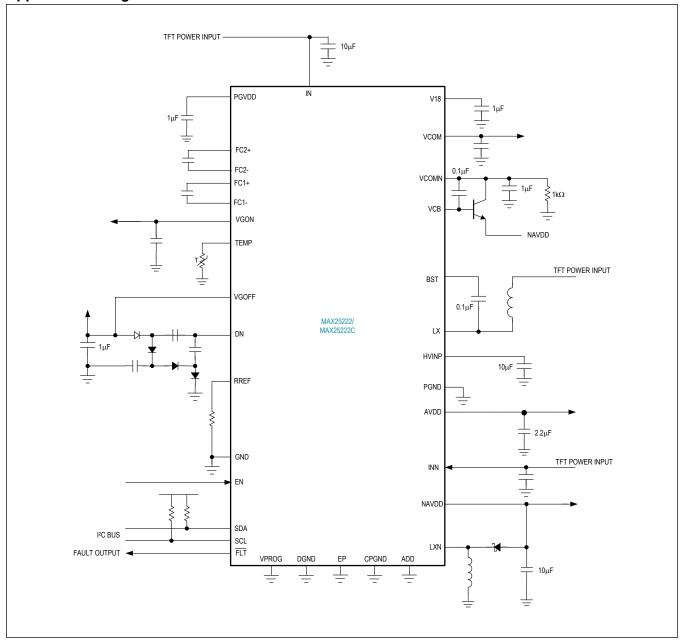

The MAX25222/MAX25222C are 4-channel TFT-LCD power ICs that provide symmetrical positive AVDD and negative NAVDD supplies as well as VG<sub>ON</sub> and VG<sub>OFF</sub> gate supplies. In addition, a VCOM buffer with output voltage range above and below ground and a temperature measurement block are integrated.

These devices contain non-volatile memory so that the values of all outputs can be calibrated for the lifetime of the device (maximum five times).

Programming is carried out using the built-in I<sup>2</sup>C interface, which can also be used to read back diagnostic information. A stand-alone mode is available after the device has been programmed.

The temperature sensor interface block measures the temperature optionally allowing the VCOM output voltage to be adjusted depending on the measured temperature.

The MAX25222/MAX25222C include extensive diagnostics to aid in fulfilling the ASIL B safety level.

The MAX25222/MAX25222C are available in a TQFN package and operate in the -40°C to 125°C temperature range.

### **Applications**

- Infotainment Displays

- Central Information Displays

- Instrument Clusters

#### **Benefits and Features**

- High Integration

- Synchronous Boost Provides AVDD of 4.2V to 10.5V at up to 200mA

- NAVDD Inverter Output at up to -200mA

- 15mA VG<sub>ON</sub> Output (7.6V to 20.2V) from 3x Regulated Charge Pump

- VG<sub>OFF</sub> (-18.2V to -5.6V) from Regulated Charge Pump at up to -15mA (Charge-Pump Doubler)

- Controlled Sequencing during Power-On and Power-Off of All Rails

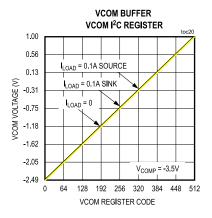

- VCOM Output Range +1V to -2.49V in 6.83mV Steps

- NTC Input for Temperature Measurement/ Compensation

- Low EMI

- 420kHz/2.1MHz Switching Frequency with Spread Spectrum

- I<sup>2</sup>C Control/Diagnostic Interface with FLTB (Interrupt) Output

- · UV Diagnostics on All Outputs

- · OV Diagnostics on All Outputs

- · Bandgap Reference Out of Range

- Stuck FLTB Pin

- · Communication Parity Check

- VCOM DAC Fault

- Versatile

- Non-Volatile Output Voltage Settings on AVDD/ NAVDD, VG<sub>ON</sub>, VG<sub>OFF</sub>, VCOM, and Sequencing

- Supports Stand-Alone Operation Mode after Programming

- Compact 5mm x 5mm TQFN32 Package

- AEC-Q100 Grade 1

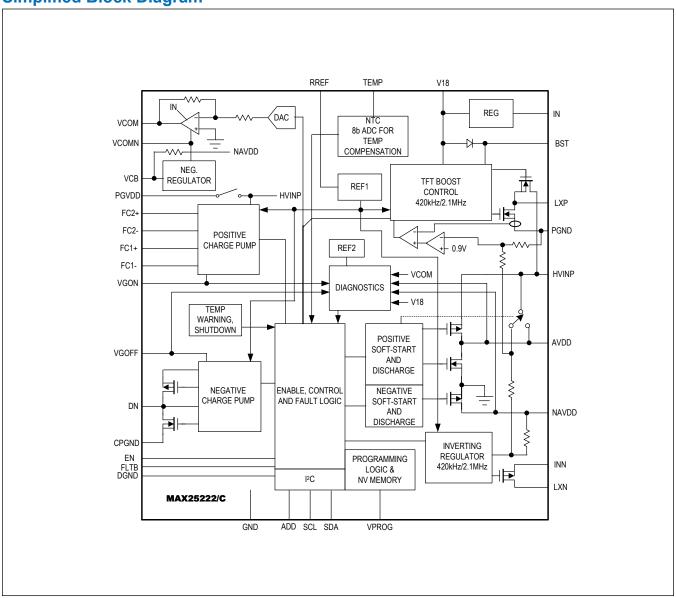

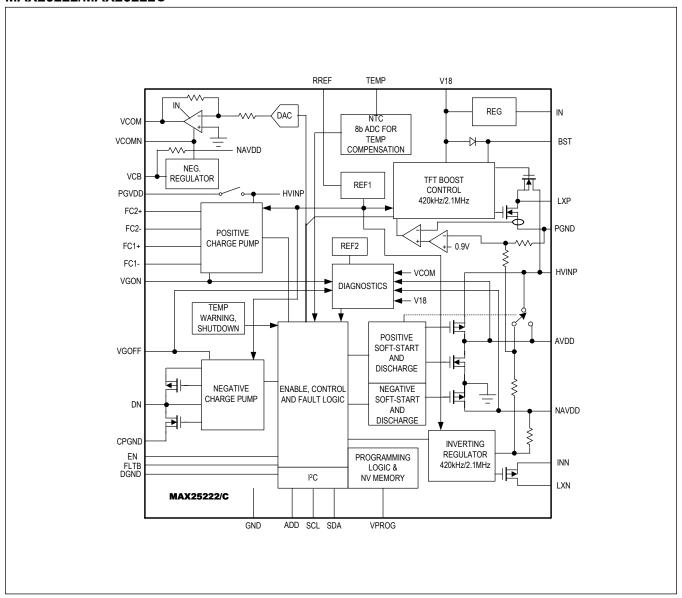

### **Simplified Block Diagram**

### **TABLE OF CONTENTS**

| General Description                               |    |

|---------------------------------------------------|----|

| Applications                                      |    |

| Benefits and Features                             |    |

| Simplified Block Diagram                          | 2  |

| Absolute Maximum Ratings                          | 7  |

| Package Information                               | 7  |

| TQFN                                              | 7  |

| TQFN-SW                                           | 7  |

| Electrical Characteristics                        | 8  |

| Typical Operating Characteristics                 | 14 |

| Pin Configuration                                 | 16 |

| MAX25222/MAX25222C                                | 16 |

| Pin Description                                   | 17 |

| Functional Diagrams                               |    |

| MAX25222/MAX25222C                                |    |

| Detailed Description                              | 20 |

| Power-Up State                                    | 20 |

| Switching Frequency                               | 20 |

| Stand-Alone Operation                             | 20 |

| I <sup>2</sup> C Read-Only Mode                   | 20 |

| Source Driver Power Supplies                      | 21 |

| Gate-Driver Power Supplies                        | 21 |

| Sequencing                                        |    |

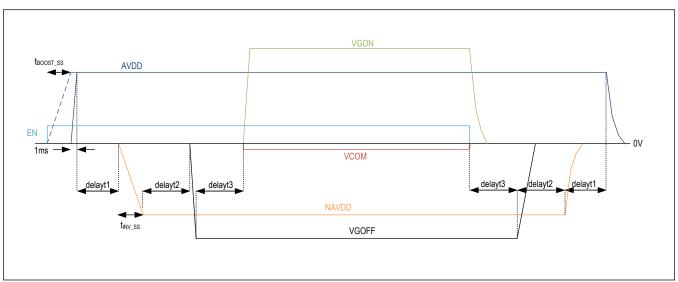

| Sequencing Diagram                                | 22 |

| VCOM Buffer                                       | 22 |

| VCOMN Negative Power Supply                       | 23 |

| Limiting the Range of VCOM Voltage                | 23 |

| VCOM Temperature Compensation                     | 23 |

| NTC Connection Diagram                            | 24 |

| Internal Temperature Sensor                       | 24 |

| Temperature Compensation Curve                    | 24 |

| Fault Handling                                    |    |

| Undervoltage Faults on Source and Gate Outputs    |    |

| Overvoltage Faults on the Source and Gate Outputs |    |

| Further Faults                                    |    |

| Thermal Warning and Shutdown                      | 26 |

| NV Memory                                         | 26 |

| Auto-Refresh Function                             | 26 |

| BURN, REBOOT and RESTART Commands                 | 26 |

### TABLE OF CONTENTS (CONTINUED)

| I <sup>2</sup> C Interface                                         |    |

|--------------------------------------------------------------------|----|

| I <sup>2</sup> C Slave Addresses                                   | 27 |

| Parity Checking                                                    | 27 |

| Register Map                                                       |    |

| MAX25222/MAX25222C                                                 |    |

| Register Details                                                   |    |

| Applications Information                                           |    |

| Boost Converter                                                    | 46 |

| Boost Converter Inductor Selection                                 | 46 |

| Boost Output Filter Capacitor Selection                            | 46 |

| Boost Input Filter Capacitor                                       | 46 |

| Setting the AVDD Voltage                                           | 46 |

| NAVDD Inverting Regulator                                          | 46 |

| NAVDD Regulator Inductor Selection                                 | 46 |

| NAVDD External Diode Selection                                     |    |

| NAVDD Output Capacitor Selection                                   |    |

| Setting the VG <sub>ON</sub> and VG <sub>OFF</sub> Output Voltages | 47 |

| VCOM Block                                                         | 47 |

| VCB Transistor                                                     | 47 |

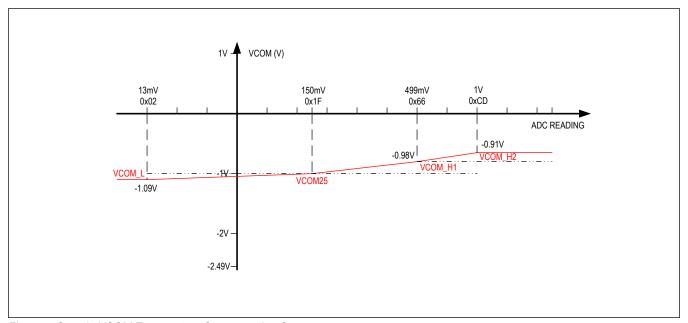

| VCOM Temperature Compensation Example                              | 47 |

| Sample VCOM Temperature Compensation Curve                         | 48 |

| Using the NV Memory                                                | 48 |

| Layout Considerations                                              |    |

| Typical Application Circuits                                       | 50 |

| Applications Diagram                                               | 50 |

| Ordering Information                                               | 51 |

| Revision History                                                   | 52 |

# Automotive 4-Channel TFT-LCD Power Supply with VCOM Buffer and ASIL B Features

| LIST OF FIGURES                                         |    |

|---------------------------------------------------------|----|

| Figure 1. Sequencing Example (Sequence 1, Not to Scale) | 22 |

| Figure 2. Possible NTC Connection                       | 24 |

| Figure 3. Temperature Compensation Curve                | 24 |

| Figure 4. Sample VCOM Temperature Compensation Curve    | 48 |

# Automotive 4-Channel TFT-LCD Power Supply with VCOM Buffer and ASIL B Features

### LIST OF TABLES

| able 1. Device Behavior after Start-Up      |     |

|---------------------------------------------|-----|

| able 2. Available Sequences                 | . 1 |

| able 3. VCOM Settings                       | 2   |

| able 4. FLTB Duty Cycle in Stand-Alone Mode |     |

| able 5. I <sup>2</sup> C Slave Addresses    | 7   |

| able 6. ADC Result vs Temperature           |     |

| able 7. VCOM Setting Example                | 7   |

### **Absolute Maximum Ratings**

| IN, INN to GND           | 0.3V to +6V                                       | VCOMN to GNDV                            | 18 - 6V to V18 + 0.3V           |

|--------------------------|---------------------------------------------------|------------------------------------------|---------------------------------|

| IN to INN                | 0.3V to +0.3V                                     | PGVDD, FC1-, FC2-, DN to GND             | 0.3V to HVINP + 0.3V            |

| V18 to GND               | 0.3V to +2.2V                                     | FC1+ to GND0.                            | 3V to PGVDD + 0.3V              |

| HVINP to GND             | 0.3V to 16V                                       | FC2+ TO FC1+                             | 0.3V to +22V                    |

| LXP, AVDD to GND         | 0.3V to HVINP + 0.3V                              | VG <sub>ON</sub> to FC2+                 | 0.3V to +22V                    |

| BST to GND               | 0.3V to +16V                                      | FC2+, VG <sub>ON</sub> to GND            | 0.3V to +24V                    |

| BST to LXP               | 0.3V to +2.2V                                     | EN, FLTB, SCL, SDA to GND                | 0.3V to +6V                     |

| LXN to INN               | 22V to +0.3V                                      | ADD, TEMP, R <sub>REF</sub> to GND       | 0.3V to V18 + 0.3V              |

| PGND, CPGND, DGND to GND | 0.3V to +0.3V                                     | V <sub>PROG</sub> to GND                 | 0.3V to +14V                    |

| VCB to GND               | V18 - 22V to V18 + 0.3V                           | Continuous Power Dissipation (Multilayer | Board) ( $T_A = +70^{\circ}C$ , |

| NAVDD to GND             | V <sub>V18</sub> - 16V to V <sub>V18</sub> + 0.3V | derate 21.3mW/°C above +70°C)            | 2222mW                          |

| VG <sub>OFF</sub> to GND | V <sub>V18</sub> - 22V to V <sub>V18</sub> + 0.3V | Operating Temperature Range              | 40°C to +125°C                  |

| VCOM to GND              | VCOMN - 0.3V to IN + 0.3V                         | •                                        |                                 |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### **TQFN**

| Package Code                            | T3255+6C       |

|-----------------------------------------|----------------|

| Outline Number                          | <u>21-0140</u> |

| Land Pattern Number                     | 90-0603        |

| Thermal Resistance, Single-Layer Board: |                |

| Junction to Ambient (θ <sub>JA</sub> )  | 47°C/W         |

| Junction to Case (θ <sub>JC</sub> )     | 3°C/W          |

| Thermal Resistance, Four-Layer Board:   |                |

| Junction to Ambient (θ <sub>JA</sub> )  | 36°C/W         |

| Junction to Case (θ <sub>JC</sub> )     | 3°C/W          |

#### **TQFN-SW**

| Package Code                            | T3255Y+6C        |

|-----------------------------------------|------------------|

| Outline Number                          | <u>21-100041</u> |

| Land Pattern Number                     | <u>90-100066</u> |

| Thermal Resistance, Single-Layer Board: |                  |

| Junction to Ambient (θ <sub>JA</sub> )  | 47°C/W           |

| Junction to Case $(\theta_{JC})$        | 3°C/W            |

| Thermal Resistance, Four-Layer Board:   |                  |

| Junction to Ambient $(\theta_{JA})$     | 36°C/W           |

| Junction to Case $(\theta_{JC})$        | 3°C/W            |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

(V<sub>IN</sub> = 3.3V, V<sub>INN</sub> = 3.3V, Limits are 100% guaranteed between  $T_A$  = -40°C and  $T_A$  = +125°C.)

| PARAMETER                                           | SYMBOL               | CONDITIONS                                                                                           | MIN                 | TYP  | MAX   | UNITS |

|-----------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------|---------------------|------|-------|-------|

| INPUT SUPPLY                                        |                      |                                                                                                      | 1                   |      |       | '     |

| IN Voltage Range                                    |                      |                                                                                                      | 2.65                |      | 5.5   | V     |

| IN UVLO Threshold                                   | IN_UVLO_R            | Rising                                                                                               | 2.4                 | 2.5  | 2.57  | V     |

| IN UVLO Hysteresis                                  | IN_UVLO_HY<br>S      |                                                                                                      |                     | 100  |       | mV    |

| IN Shutdown Current                                 | I <sub>IN_SHDN</sub> | EN = GND, V <sub>IN</sub> = 3.3V, T <sub>A</sub> = +25°C                                             |                     | 7    | 12    | μA    |

| IN Quiescent Current                                | I <sub>IN Q</sub>    | V <sub>EN</sub> = V <sub>IN</sub> = 3.3V, no switching.                                              |                     | 1.5  | 2.5   | mA    |

| V18 REGULATOR                                       |                      |                                                                                                      | •                   |      |       |       |

| V18 Output Voltage                                  |                      |                                                                                                      | 1.72                | 1.8  | 1.88  | V     |

| V18 Current Limit                                   |                      |                                                                                                      | 60                  |      |       | mA    |

| V18 Undervoltage<br>Lockout                         |                      | V18 rising                                                                                           | 1.6                 | 1.65 | 1.7   | V     |

| V18 Undervoltage<br>Hysteresis                      |                      |                                                                                                      |                     | 150  |       | mV    |

| V18OOR Diagnostic<br>Levels                         |                      |                                                                                                      | -8                  |      | +8    | %     |

| OSCILLATOR                                          | 1                    |                                                                                                      |                     |      |       | 1     |

| On and the second                                   | fвооsтн              | f <sub>SW</sub> bit = 0, dither disabled. Switching frequency for boost, inverter, and charge pumps. | 1950                | 2100 | 2250  | Id In |

| Operating Frequency                                 | fBOOSTL              | f <sub>SW</sub> bit = 1, dither disabled. Switching frequency for boost, inverter, and charge pumps. | 385                 | 420  | 455   | kHz   |

| Frequency Dither                                    | f <sub>BOOSTD</sub>  |                                                                                                      |                     | ±6   |       | %     |

| BOOST REGULATOR                                     |                      |                                                                                                      | •                   |      |       |       |

| HVINP Output Voltage<br>Range                       | V <sub>HVINP</sub>   |                                                                                                      | V <sub>IN</sub> + 1 |      | 10.5  | V     |

| AVDD Output Voltage<br>Range                        |                      |                                                                                                      | 4.2                 |      | 10.5  | V     |

| AVDD Adjustment Step<br>Size                        |                      |                                                                                                      |                     | 0.1  |       | V     |

| AVDD Output<br>Regulation                           | V <sub>AVDD</sub>    | avdd[5:0] = 0x1A, full load current and input voltage range                                          | 6.664               | 6.8  | 6.936 | V     |

| Oscillator Maximum                                  |                      | 420kHz switching frequency                                                                           | 87                  | 88.5 | 90    | 0/    |

| Duty Cycle                                          |                      | 2.1MHz switching frequency                                                                           | 84                  | 87   | 90    | - %   |

| Low-Side Switch On-<br>Resistance                   | LXP_RON_LS           | I <sub>LXP</sub> = 0.1A                                                                              |                     | 0.1  | 0.2   | Ω     |

| Synchronous Rectifier<br>On-Resistance              |                      |                                                                                                      |                     | 0.1  | 0.2   | Ω     |

| Synchronous Rectifier<br>Zero-Crossing<br>Threshold | ZX_TH                |                                                                                                      |                     | 70   |       | mA    |

| LXP Leakage Current                                 | LXP_L_LEAK           | V <sub>EN</sub> = 0V, V <sub>LXP</sub> = 10.5V                                                       |                     |      | 20    | μA    |

| LXP Current Limit                                   | ILIMPH               | Duty cycle = 50%                                                                                     | 1.7                 | 2    | 2.3   | Α     |

### **Electrical Characteristics (continued)**

$(V_{IN} = 3.3V, V_{INN} = 3.3V, Limits are 100\%$  guaranteed between  $T_A = -40$ °C and  $T_A = +125$ °C.)

| PARAMETER                                                                                 | SYMBOL                          | CONDITIONS                                                                                               | MIN   | TYP                         | MAX  | UNITS |

|-------------------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------|-------|-----------------------------|------|-------|

| Soft-Start Period                                                                         | t <sub>BOOST_SS</sub>           | Current-limit ramp                                                                                       |       | 5                           |      | ms    |

| INVERTING REGULATO                                                                        | R                               |                                                                                                          |       |                             |      |       |

| Oscillator Maximum                                                                        |                                 | 2.1MHz switching frequency                                                                               | 92    | 95                          |      | - %   |

| Duty Cycle                                                                                | INV_MAXDC                       | 420kHz switching frequency                                                                               | 88    | 90                          |      | /0    |

| V <sub>AVDD</sub> + V <sub>NAVDD</sub><br>Regulation Voltage                              | V <sub>NAVDD_AVD</sub><br>D_REG | $V_{INN}$ = 2.65V to 5.5V, $V_{AVDD}$ = 6.8V, 1mA < $I_{NAVDD}$ < 200mA, $I_{AVDD}$ = same load as NAVDD | -34   | 0                           | 34   | mV    |

| LXN On-Resistance                                                                         | LXN_RON                         | INN to LXN, I <sub>LXN</sub> = 0.1A                                                                      |       | 0.25                        | 0.5  | Ω     |

| LXN Leakage Current                                                                       | LXN_LEAK                        | $V_{IN} = 3.6V$ , $V_{LXN} = V_{NAVDD} = -6.8V$ , $T_A = +25$ °C                                         |       |                             | 20   | μA    |

| LXN Current Limit                                                                         | ILIMNH                          | Duty cycle = 80%                                                                                         | 1.55  | 1.9                         | 2.25 | Α     |

| Soft-Start Period                                                                         | t <sub>INV_SS</sub>             | Current-limit ramp                                                                                       |       | 5                           |      | ms    |

| NAVDD Discharge<br>Resistance                                                             |                                 |                                                                                                          |       | 2                           |      | kΩ    |

| POSITIVE CHARGE-PUN                                                                       | IP REGULATOR                    | ł                                                                                                        |       |                             |      |       |

| VG <sub>ON</sub> Threshold for<br>Charge-Pump Switching<br>Enable                         |                                 |                                                                                                          |       | V <sub>HVINP</sub> -<br>0.8 |      | V     |

| FC1-, FC2- Switches<br>Current Limit, High-Side                                           |                                 |                                                                                                          | 90    | 120                         |      | mA    |

| FC1-, FC2- Switches<br>Current Limit, Low-Side                                            |                                 |                                                                                                          | 72    | 100                         |      | mA    |

| FC1-, FC2- to CPGND<br>On-Resistance                                                      |                                 |                                                                                                          |       | 4                           | 6.5  | Ω     |

| FC1-, FC2- to HVINP<br>On-Resistance                                                      |                                 |                                                                                                          |       | 6                           | 10.5 | Ω     |

| FC2+ to PGVDD, FC1+<br>to FC2+ and VG <sub>ON</sub> to<br>FC1+ Switches On-<br>Resistance |                                 |                                                                                                          |       | 2.5                         | 4.5  | Ω     |

| VG <sub>ON</sub> Voltage Range,<br>I <sup>2</sup> C Mode                                  |                                 |                                                                                                          | 7.6   |                             | 20.2 | V     |

| VG <sub>ON</sub> Adjustment Step<br>Size, I <sup>2</sup> C Mode                           |                                 |                                                                                                          |       | 0.2                         |      | V     |

| VG <sub>ON</sub> Output Voltage                                                           | V <sub>VGON</sub>               | vgon[5:0] = 0x16, full load current and V <sub>HVINP</sub> > 5V, charge-pump tripler                     | 11.7  | 12                          | 12.3 | V     |

| VG <sub>ON</sub> Discharge<br>Resistance                                                  |                                 |                                                                                                          | 2.2   | 3                           | 3.8  | kΩ    |

| NEGATIVE CHARGE-PU                                                                        | MP REGULATO                     | R                                                                                                        |       |                             |      |       |

| DN Current Limit                                                                          |                                 |                                                                                                          | 75    | 100                         |      | mA    |

| VG <sub>OFF</sub> Voltage Range,<br>I <sup>2</sup> C Mode                                 |                                 |                                                                                                          | -18.2 |                             | -5.6 | V     |

| VG <sub>OFF</sub> Adjustment Step<br>Size, I <sup>2</sup> C Mode                          |                                 |                                                                                                          |       | 0.2                         |      | V     |

### **Electrical Characteristics (continued)**

$(V_{IN} = 3.3V, V_{INN} = 3.3V, Limits are 100\%$  guaranteed between  $T_A = -40$ °C and  $T_A = +125$ °C.)

| PARAMETER                                                                 | SYMBOL              | CONDITIONS                                                                      | MIN   | TYP | MAX  | UNITS |

|---------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------|-------|-----|------|-------|

| VG <sub>OFF</sub> Output-Voltage<br>Accuracy                              |                     | vgoff[5:0] = 0x16, full load current and input voltage range, 420kHz operation. | -10.3 | -10 | -9.7 | V     |

| DN On-Resistance,<br>High-Side                                            |                     |                                                                                 |       | 6   | 10   | Ω     |

| DN On-Resistance,<br>Low-Side                                             |                     | I <sub>DN</sub> = -10mA                                                         |       | 3.5 | 6.5  | Ω     |

| VG <sub>OFF</sub> Discharge<br>Current                                    |                     |                                                                                 |       | 1.5 |      | mA    |

| SEQUENCE SWITCHES                                                         |                     |                                                                                 |       |     |      |       |

| AVDD ON Resistance                                                        | R <sub>ONAVDD</sub> | Between HVINP and AVDD, I <sub>AVDD</sub> = 200mA                               |       | 0.5 | 1    | Ω     |

| AVDD Current Limit                                                        | ILIM <sub>POS</sub> |                                                                                 | 300   |     | 600  | mA    |

| AVDD Discharge<br>Resistance                                              |                     |                                                                                 |       | 1.2 |      | kΩ    |

| PGVDD On-Resistance                                                       |                     | (HVINP-PGVDD), I <sub>PGVDD</sub> = 3mA                                         |       | 6   | 9    | Ω     |

| PGVDD Current Limit                                                       |                     | Expires when PGVDD charging is completed                                        | 80    | 100 |      | mA    |

| FAULT PROTECTION                                                          |                     |                                                                                 |       |     |      |       |

| Fault Timeout                                                             |                     | tfault[1:0] = 10                                                                |       | 60  |      | ms    |

| Fault Retry Time                                                          |                     | tretry[1:0] = 10 or 11                                                          |       | 1.9 |      | s     |

| FLTB Output Frequency                                                     |                     | Stand-alone mode only                                                           | 0.88  | 1   | 1.12 | kHz   |

| FLTB Output Duty<br>Cycle, VG <sub>ON</sub> or VG <sub>OFF</sub><br>Fault |                     | Stand-alone mode only                                                           |       | 75  |      | %     |

| FLTB Output Duty Cycle with AVDD, NAVDD, or HVINP Fault                   |                     | Stand-alone mode only                                                           |       | 50  |      | %     |

| FLTB Output Duty<br>Cycle, VCOM Fault                                     |                     | Stand-alone mode only                                                           |       | 25  |      | %     |

| AVDD Undervoltage<br>Fault Threshold                                      |                     | Relative measurement between HVINP and AVDD                                     | 80    | 85  | 90   | %     |

| HVINP Overvoltage<br>Fault Threshold                                      |                     | Of set value                                                                    | 110   | 115 | 120  | %     |

| AVDD Short-Circuit Fault Threshold                                        |                     | Relative measurement between HVINP and AVDD                                     | 35    | 40  | 45   | %     |

| NAVDD Undervoltage<br>Fault Threshold                                     |                     | Measured with respect to AVDD                                                   | 80    | 85  | 90   | %     |

| NAVDD Overvoltage<br>Fault Threshold                                      |                     |                                                                                 | 110   | 115 | 120  | %     |

| NAVDD Short-Circuit<br>Fault Threshold                                    |                     | Measured with respect to AVDD                                                   | 35    | 40  | 45   | %     |

| VG <sub>ON</sub> Undervoltage<br>Fault Threshold                          |                     | Of set value                                                                    | 80    | 85  | 90   | %     |

| VG <sub>ON</sub> Overvoltage Fault<br>Threshold                           |                     | Of set value                                                                    | 110   | 115 | 120  | %     |

### **Electrical Characteristics (continued)**

$(V_{IN} = 3.3V, V_{INN} = 3.3V, Limits are 100\%$  guaranteed between  $T_A = -40$ °C and  $T_A = +125$ °C.)

| PARAMETER                                          | SYMBOL               | CONDITIONS                                             | MIN   | TYP                         | MAX  | UNITS         |

|----------------------------------------------------|----------------------|--------------------------------------------------------|-------|-----------------------------|------|---------------|

| VG <sub>ON</sub> Short-Circuit<br>Fault Threshold  |                      | VG <sub>ON</sub> Falling, MAX25222ATJ only             |       | V <sub>HVINP</sub> -<br>1.1 |      | V             |

| VG <sub>OFF</sub> Undervoltage<br>Fault Threshold  |                      | Of set value                                           | 80    | 85                          | 90   | %             |

| VG <sub>OFF</sub> Overvoltage<br>Fault Threshold   |                      | Of set value                                           | 110   | 115                         | 120  | %             |

| VG <sub>OFF</sub> Short-Circuit<br>Fault Threshold |                      | MAX25222ATJ only                                       | 35    | 40                          | 45   | %             |

| Short-Circuit and<br>Overload Fault Delay          |                      |                                                        |       | 10                          |      | μs            |

| Bandgap Out-Of-Range<br>Diagnostic Threshold       |                      |                                                        |       | <u>+</u> 11                 |      | %             |

| VCOM BUFFER                                        |                      |                                                        |       |                             |      |               |

| VCOMN Output Voltage                               |                      | I <sub>VCOM</sub> = 120mA, V <sub>NAVDD</sub> = -10.5V |       | -3.5                        | -3.2 | V             |

| VCB Output Current                                 |                      |                                                        | 5     | 12                          | 21   | mA            |

| VCOM Output Current<br>Limit, Sinking              |                      | Dynamic output current, t < t <sub>FAULT</sub>         | 120   | 200                         | 300  | mA            |

| VCOM Output Current<br>Limit, Sourcing             | I <sub>LIMCOMP</sub> | Dynamic output current, t < t <sub>FAULT</sub>         | 120   | 200                         | 300  | mA            |

| VCOM Overcurrent<br>Detection Threshold            |                      |                                                        | 60    | 70                          | 85   | % of ILIMCOME |

| VCOM Offset Voltage,<br>Complete Range             |                      | $V_{VCOM}$ = -2.49V and $V_{VCOM}$ = +1V, no load      | -25   |                             | +25  | mV            |

| VCOM Offset Voltage,<br>25°C                       |                      | T <sub>A</sub> = +25°C, VCOM = -0.5V                   | -6    |                             | +6   | mV            |

| VCOM Offset Voltage                                |                      | VCOM = -0.5V                                           | -10   |                             | +10  | mV            |

| VCOM Output Voltage<br>Range                       |                      | Temperature compensation disabled                      | -2.49 |                             | 1    | V             |

| VCOM DAC Step Size                                 |                      |                                                        |       | 6.83                        |      | mV            |

| VCOM Buffer Slew Rate                              |                      | C <sub>VCOM</sub> = 10nF, VCOM from -2.49V to +1V      |       | 0.72                        |      | V/µs          |

| VCOM Fault Threshold                               |                      | Deviation from set voltage                             |       | <u>+</u> 0.25               |      | V             |

| VCOM Fault Detection<br>Filter Time                |                      | tfault[1:0] = 10                                       |       | 60                          |      | ms            |

| VCOM Discharge<br>Resistance                       |                      | to GND                                                 | 9     | 14                          | 22   | kΩ            |

| R <sub>REF</sub> INPUT                             |                      |                                                        |       |                             |      |               |

| R <sub>REF</sub> Input Voltage<br>Range            |                      |                                                        | 0     |                             | 1.25 | V             |

| R <sub>REF</sub> ADC Resolution                    |                      |                                                        |       | 4.88                        |      | mV            |

| R <sub>REF</sub> Conversion Rate                   |                      |                                                        |       | 128                         |      | kHz           |

| TEMP Voltage                                       | $V_{TEMP}$           | I <sub>TEMP</sub> = 10μA to 500μA                      |       | 625                         |      | mV            |

| TEMP Current Mirror<br>Gain                        |                      | I <sub>TEMP</sub> = 10μA to 500μA                      |       | 1                           |      | μΑ/μΑ         |

### **Electrical Characteristics (continued)**

$(V_{IN} = 3.3V, V_{INN} = 3.3V, Limits are 100\%$  guaranteed between  $T_A = -40$ °C and  $T_A = +125$ °C.)

| PARAMETER                                           | SYMBOL            | CONDITIONS                                    | MIN  | TYP | MAX  | UNITS |

|-----------------------------------------------------|-------------------|-----------------------------------------------|------|-----|------|-------|

| Internal Temperature<br>Sensor Voltage              |                   | T <sub>A</sub> = +25°C                        |      | 620 |      | mV    |

| R <sub>REF</sub> DAC Offset                         |                   |                                               |      | 5   |      | mV    |

| R <sub>REF</sub> DAC Full-Scale<br>Error            |                   |                                               |      | 5   |      | mV    |

| R <sub>REF</sub> DAC Gain Error                     |                   |                                               | -0.4 |     | +0.4 | %     |

| R <sub>REF</sub> DAC Differential<br>Non-linearity  |                   |                                               |      | 0.5 |      | LSB   |

| R <sub>REF</sub> DAC Integral Non-<br>Linearity     |                   |                                               |      | 0.5 |      | LSB   |

| LOGIC INPUTS and OUT                                | PUTS (EN, SCL     | , ADD, SDA)                                   |      |     |      |       |

| EN Glitch Filter                                    | EN_BLK            |                                               |      | 10  |      | μs    |

| EN Minimum Low Time<br>For Reset                    |                   | C <sub>V18</sub> = 1μF                        | 1    |     |      | ms    |

| EN Input Logic-High                                 |                   |                                               | 1.22 |     |      | V     |

| EN Input Logic-Low                                  |                   |                                               |      |     | 0.6  | V     |

| ADD Input Logic-High                                |                   |                                               | 1.22 |     |      | V     |

| ADD Input Logic-Low                                 |                   |                                               |      |     | 0.66 | V     |

| ADD Input Pulldown<br>Current                       |                   |                                               |      | 10  | 12   | μA    |

| SCL, SDA Input, Logic-<br>High                      |                   |                                               | 1.22 |     |      | V     |

| SCL, SDA Input, Logic-<br>Low                       |                   |                                               |      |     | 0.6  | V     |

| SCL Input Leakage<br>Current                        |                   |                                               | -1   |     | +1   | μA    |

| FLTB, SDA Output Low<br>Voltage                     | $V_{OL}$          | Sinking 5mA                                   |      |     | 0.4  | V     |

| FLTB, SDA Output<br>Leakage Current                 | I <sub>LEAK</sub> | 5.5V                                          | -1   |     | +1   | μА    |

| PROGRAMMING VOLTA                                   | GE                |                                               |      |     |      |       |

| V <sub>PROG</sub> Voltage                           |                   |                                               | 8.2  | 8.5 | 8.8  | V     |

| V <sub>PROG</sub> Voltage<br>Undervoltage Threshold |                   | V <sub>PROG</sub> rising                      |      | 8   | 8.2  | V     |

| V <sub>PROG</sub> Voltage<br>Overvoltage Threshold  |                   | V <sub>PROG</sub> falling                     | 8.8  | 9   |      | V     |

| VPROG Input Current                                 |                   | During NV programming, T <sub>A</sub> = +25°C |      | 9   | 25   | mA    |

| NV Programming Time                                 |                   |                                               |      | 16  | 20   | ms    |

| THERMAL SHUTDOWN                                    |                   |                                               |      |     |      |       |

| Thermal Warning<br>Threshold                        |                   |                                               |      | 125 |      | °C    |

| Thermal-Shutdown<br>Threshold                       | T <sub>SHDN</sub> |                                               |      | 160 |      | °C    |

### **Electrical Characteristics (continued)**

$(V_{IN} = 3.3V, V_{INN} = 3.3V, Limits are 100\%$  guaranteed between  $T_A = -40$ °C and  $T_A = +125$ °C.)

| PARAMETER                        | SYMBOL                | CONDITIONS | MIN  | TYP | MAX | UNITS |

|----------------------------------|-----------------------|------------|------|-----|-----|-------|

| Thermal-Shutdown<br>Hysteresis   | T <sub>SHDN_HYS</sub> |            |      | 15  |     | °C    |

| I <sup>2</sup> C INTERFACE       |                       |            | •    |     |     |       |

| Clock Frequency                  | f <sub>SCL</sub>      |            |      |     | 0.4 | MHz   |

| Hold Time (Repeated)<br>START    | thd:sta               |            | 600  |     |     | ns    |

| SCL Low Time                     | t <sub>LOW</sub>      |            | 1300 |     |     | ns    |

| SCL High Time                    | tHIGH                 |            | 600  |     |     | ns    |

| Setup Time (Repeated)<br>START   | tsu:sta               |            | 600  |     |     | ns    |

| Data Hold Time                   | t <sub>HD:DAT</sub>   |            | 0    |     |     | ns    |

| Data Setup Time                  | t <sub>SU:DAT</sub>   |            | 100  |     |     | ns    |

| Setup Time for STOP<br>Condition | tsu:sto               |            | 600  |     |     | ns    |

| Spike Suppression                |                       |            |      | 50  |     | ns    |

Note 1: Note 1: Limits are 100% tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

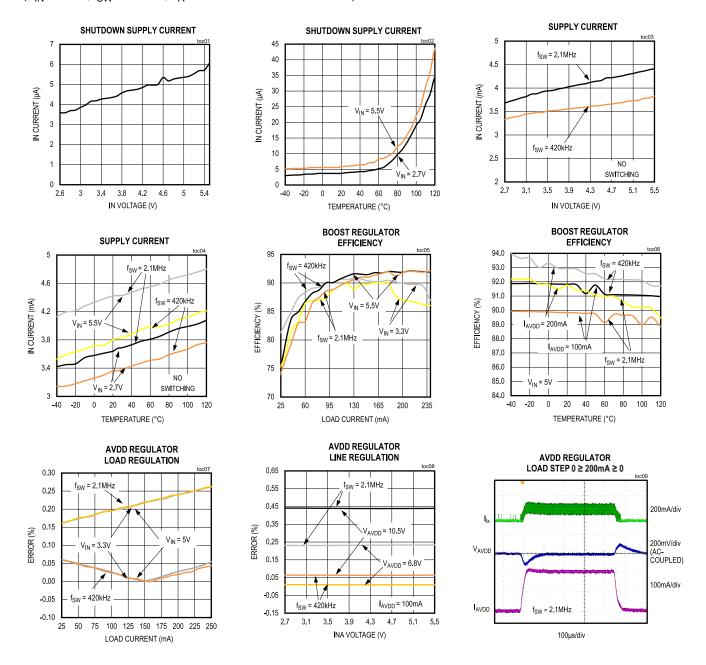

#### **Typical Operating Characteristics**

$(V_{IN} = +3.3V, f_{SW} = 2.1MHz, T_A = +25^{\circ}C \text{ unless otherwise noted.})$

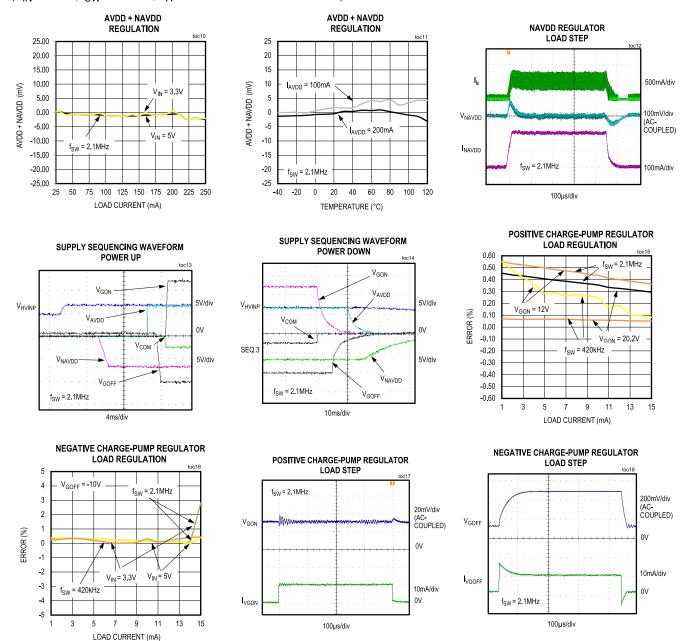

#### **Typical Operating Characteristics (continued)**

$(V_{IN} = +3.3V, f_{SW} = 2.1MHz, T_A = +25^{\circ}C \text{ unless otherwise noted.})$

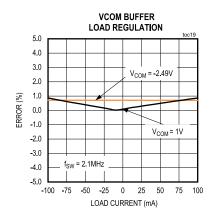

### **Typical Operating Characteristics (continued)**

$(V_{IN} = +3.3V, f_{SW} = 2.1MHz, T_A = +25^{\circ}C \text{ unless otherwise noted.})$

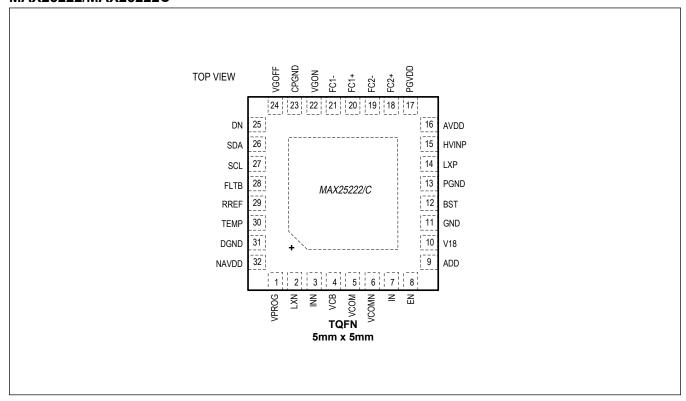

### **Pin Configuration**

#### MAX25222/MAX25222C

### **Pin Description**

| PIN | NAME              | FUNCTION                                                                                                                                                                                                                                                                                                                                   |

|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>PROG</sub> | Programming Voltage. Apply a voltage of 8.5V to this pin during the programming of non-volatile registers. Connect to GND through a resistor during normal operation.                                                                                                                                                                      |

| 2   | LXN               | DC-DC Inverting Converter Inductor/Diode Connection.                                                                                                                                                                                                                                                                                       |

| 3   | INN               | Inverting Converter Input. Connect 10μF + 0.1μF ceramic capacitors from this pin to ground for proper operation.                                                                                                                                                                                                                           |

| 4   | VCB               | Drive Output for External npn Pass Transistor for VCOMN regulator. Connect to the base of the external npn transistor.                                                                                                                                                                                                                     |

| 5   | VCOM              | Output of VCOM amplifier.                                                                                                                                                                                                                                                                                                                  |

| 6   | VCOMN             | Negative Supply for VCOM Buffer. Connect a ceramic capacitor of at least 1µF from VCOMN to GND.                                                                                                                                                                                                                                            |

| 7   | IN                | Supply Connection for Display Bias Circuitry. Bypass IN with local 10μF and 0.1μF capacitors.                                                                                                                                                                                                                                              |

| 8   | EN                | Enable Input Pin. When EN is low, the device is in shutdown. When EN is taken high, the device is active. In stand-alone mode, the outputs are turned on in the stored sequence when EN goes high.                                                                                                                                         |

| 9   | ADD               | Device Address Select pin. Connect to GND or V18 to Select the Device I <sup>2</sup> C Address. See the I <sup>2</sup> C address table. To use stand-alone mode (without I <sup>2</sup> C) leave the ADD pin open. In this mode, the device turns on all outputs in the programmed sequence when EN is taken high.                         |

| 10  | V18               | Output of Internal 1.8V Regulator. Connect a 1µF capacitor from V18 to GND.                                                                                                                                                                                                                                                                |

| 11  | GND               | Ground Connection                                                                                                                                                                                                                                                                                                                          |

| 12  | BST               | Bootstrap Capacitor Connection for Synchronous Rectifier Driver. Connect a 0.1µF ceramic capacitor between BST and LXP.                                                                                                                                                                                                                    |

| 13  | PGND              | Ground Connection for Boost Switching Device and VCOM Buffer. Connect to GND using a low-impedance trace.                                                                                                                                                                                                                                  |

| 14  | LXP               | Switching Node of Boost Converter. Connect the boost inductor between LXP and IN.                                                                                                                                                                                                                                                          |

| 15  | HVINP             | Boost Output and Input to Positive and Negative Charge-Pump Drivers. Bypass HVINP with a 10µF output capacitor placed close to the pin.                                                                                                                                                                                                    |

| 16  | AVDD              | Switched Output of Boost Converter. Connect a bypass capacitor of value 2.2µF from AVDD to PGND.                                                                                                                                                                                                                                           |

| 17  | PGVDD             | Supply Voltage for Positive Charge Pump. PGVDD is connected to HVINP by means of an internal switch when the positive charge pump is enabled. Bypass PGVDD with a ceramic capacitor of $1\mu$ F to GND.                                                                                                                                    |

| 18  | FC2+              | Positive Connection for Second Flying Capacitor. Connect a 22nF capacitor from FC2- to FC2+.                                                                                                                                                                                                                                               |

| 19  | FC2-              | Negative Connection for Second Flying Capacitor. Connect a 22nF capacitor from FC2- to FC2+.                                                                                                                                                                                                                                               |

| 20  | FC1+              | Positive Connection for First Flying Capacitor. Connect a 22nF capacitor from FC1- to FC1+.                                                                                                                                                                                                                                                |

| 21  | FC1-              | Negative Connection for First Flying Capacitor. Connect a 22nF capacitor from FC1- to FC1+.                                                                                                                                                                                                                                                |

| 22  | VG <sub>ON</sub>  | Output of Positive Charge-Pump Block. Connect a 1µF capacitor from VG <sub>ON</sub> to GND.                                                                                                                                                                                                                                                |

| 23  | CPGND             | Ground Connection for Charge Pumps.                                                                                                                                                                                                                                                                                                        |

| 24  | VG <sub>OFF</sub> | Output of Negative Charge-Pump Block. Connect a 1µF capacitor from this pin to GND.                                                                                                                                                                                                                                                        |

| 25  | DN                | Negative Charge-Pump Push-Pull Drive Output.                                                                                                                                                                                                                                                                                               |

| 26  | SDA               | Bidirectional I <sup>2</sup> C Data Pin.                                                                                                                                                                                                                                                                                                   |

| 27  | SCL               | I <sup>2</sup> C Clock Pin.                                                                                                                                                                                                                                                                                                                |

| 28  | FLTB              | Open-Drain, Active-Low Fault Output. Connect a pullup resistor from FLTB to a logic supply ≤5V. In stand-alone mode, the duty cycle of the FLTB pin indicates an error condition, if present (see <u>Table 4</u> ). When the serial interface is used, FLTB is either a 0 (indicating data to be read from the internal registers) or a 1. |

# Automotive 4-Channel TFT-LCD Power Supply with VCOM Buffer and ASIL B Features

## **Pin Description (continued)**

| PIN | NAME             | FUNCTION                                                                                                                                                                  |

|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29  | R <sub>REF</sub> | Reference Resistor Pin. When using the temperature compensation function, connect a resistor from R <sub>REF</sub> to GND. If unused, leave R <sub>REF</sub> unconnected. |

| 30  | TEMP             | Temperature Sensor Pin. When using the temperature compensation function, connect an NTC from TEMP to GND. If unused, leave TEMP unconnected.                             |

| 31  | DGND             | Logic Ground.                                                                                                                                                             |

| 32  | NAVDD            | Negative Source-Driver Output Voltage. Connect ceramic capacitors of value 0.1µF and 10µF from this pin to GND with the smallest capacitor closest to the pin.            |

### **Functional Diagrams**

#### MAX25222/MAX25222C

#### **Detailed Description**

The MAX25222/MAX25222C are 4-channel TFT-LCD power ICs that provide symmetrical positive AVDD and negative NAVDD supplies as well as  $VG_{ON}$  and  $V_{GOFF}$  gate supplies. In addition, a VCOM buffer with output voltage range above and below ground and a temperature-measurement block are integrated.

These devices contain non-volatile memory so that the values of all outputs can be calibrated for the lifetime of the device.

Programming is carried out using the built-in I<sup>2</sup>C interface, which can also be used to read back diagnostic information. Operation in stand-alone mode is also possible.

The temperature-sensor interface block determines the temperature by measuring the voltage on the  $R_{REF}$  pin when a temperature-sensitive component, such as an NTC, is connected to TEMP. The VCOM output voltage can be adjusted as a function of the measured temperature.

#### **Power-Up State**

When power is applied, the MAX25222/MAX25222C are in low-quiescent-current mode until the EN pin is taken high. When EN is taken high (if the device supply voltage on IN exceeds the undervoltage lockout voltage of 2.5V), the 1.8V regulator is turned on and the device is functional after a delay of 1ms. Subsequent operation depends on the device configuration and type as shown in Table 1.

#### **Table 1. Device Behavior after Start-Up**

| DEVICE    | ADD = 0                                                                | ADD PIN FLOATING                            | ADD = V18                                                              |

|-----------|------------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------|

| MAX25222  | Outputs turned on when start bit in register REG_CTRL is written to 1. | Outputs turned on immediately when EN high. | Outputs turned on when start bit in register REG_CTRL is written to 1. |

| MAX25222C | Outputs turned on immediately when EN high.                            | Outputs turned on immediately when EN high. | Outputs turned on immediately when EN high.                            |

If the non-volatile memory has been written to previously and the ADD pin is open (stand-alone mode), the stored values are read and the outputs are turned on in the programmed sequence when the EN pin is taken high. Otherwise, the device powers up with the default voltages of 6.8V (AVDD), 12V (VG<sub>ON</sub>), and -10V (VG<sub>OFF</sub>).

Alternatively, when I<sup>2</sup>C is used, all values can be programmed and the outputs turned on using the START bit in the REG\_CTRL register. The values can subsequently be stored in non-volatile memory using the burn\_otp command, if required.

If at any time the internal 1.8V regulator is out of range, the v18oor bit is set in register FAULT2 and the FLTB pin is asserted low, assuming the device is being used in I<sup>2</sup>C mode. No other action is taken unless the V18 voltage is below its undervoltage lockout level.

#### **Switching Frequency**

The switching frequency of the boost and inverting converters and the charge pumps is set using the  $f_{SW}$  bit in register CONFIG. When  $f_{SW}$  is 0, the switching frequency is 2.1MHz. When  $f_{SW}$  is set to 1, the switching frequency is 420kHz. The switching frequency can have spread-spectrum applied to improve EMI performance using the en\_ss bit in register CONFIG.

#### **Stand-Alone Operation**

Stand-alone operation is used when the device has already been programmed and should start up with the preprogrammed values when power is applied and the EN pin taken high. In stand-alone mode, leave the ADD pin unconnected.

#### I<sup>2</sup>C Read-Only Mode

The MAX25222C starts up immediately with the pre-programmed values when power is applied and the EN pin taken high. If the ADD pin is connected to V18, the I<sup>2</sup>C interface is in read-only mode and can only be used to read the device registers, writing is not possible. The 7-bit I<sup>2</sup>C address of the device is 0x29 (0x53 when the read bit is added) in this mode.

#### **Source Driver Power Supplies**

The source-driver power supplies consist of a boost converter with output switch and an inverting buck-boost converter that generate up to +10.5V maximum and down to -10.5V minimum, respectively, and can deliver up to 200mA on the positive regulator and -200 mA on the negative regulator. The positive source-driver power supply's regulation voltage (AVDD) is set by writing the avdd[5:0] value in the AVDD\_SET register using the I<sup>2</sup>C interface, and can be programmed into non-volatile memory. The default AVDD output voltage is 6.8V.

The negative source-driver supply voltage (NAVDD) is automatically tightly regulated to -AVDD within ±34mV. NAVDD cannot be adjusted independently of AVDD.

The AVDD boost converter is a current-mode converter with two internal switches and internal compensation. The direct output of the converter is HVINP while AVDD is a switched-output version. The NAVDD converter is a current-mode converter with one internal switch, an external diode and internal compensation.

#### **Gate-Driver Power Supplies**

The positive gate-driver power supply (VG<sub>ON</sub>) is a regulated charge-pump tripler and generates up to  $\pm 20.2$ V. Note also that the maximum output voltage is 3 x AVDD - R<sub>ONTOTAL</sub> x I<sub>VGON</sub> x K, where R<sub>ONTOTAL</sub> is typically 30 $\Omega$  and K is a factor 0.75. In cases where a doubler charge pump is sufficient, set the cp\_2stage bit and leave pins FC1- and FC1+ unconnected in order to increase efficiency.

The negative gate-driver power supply (VG<sub>OFF</sub>) generates a maximum negative voltage of -18.2V and requires external diodes and capacitors. The VG<sub>ON</sub> and VG<sub>OFF</sub> blocks switch at the same frequency as the AVDD and NAVDD converters.

Both supplies are capable of output currents up to 15mA, assuming sufficient headroom. The VG<sub>ON</sub> and VG<sub>OFF</sub> regulation voltages are set by writing the vgon[5:0] and vgoff[5:0] values in the register map using the  $I^2$ C interface, and can be stored in the non-volatile section of the register map.

#### Sequencing

The power-on and power-off sequences are controlled by the seq\_set[2:0] bits in the VCOM\_L register. The setting should be written before the sequence is to be executed and should not be changed during the turn-on or turn-off sequences. The sequence options are as follows:

Table 2. Available Sequences

|                 | SEQU     | JENCE SET | BITS     | POWER-ON          |                       |                             |                             | POWE                        |                       |                       |                       |                 |

|-----------------|----------|-----------|----------|-------------------|-----------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------|-----------------------|-----------------------|-----------------|

| Sequence<br>No. | seq_set2 | seq_set1  | seq_set0 | 1st               | 2nd<br>after t1<br>ms | 3rd<br>after t2<br>ms       | 4th<br>after t3<br>ms       | 1st                         | 2nd<br>after t3<br>ms | 3rd<br>after t2<br>ms | 4th<br>after t1<br>ms | NOTES           |

| 1               | 0        | 0         | 0        | AVDD              | NAVDD                 | VG <sub>OFF</sub>           | VG <sub>ON</sub> /<br>VCOM  | VGON/<br>VCOM               | VG <sub>OFF</sub>     | NAVDD                 | AVDD                  |                 |

| 2               | 0        | 0         | 1        | AVDD              | NAVDD                 | VG <sub>ON</sub>            | VG <sub>OFF</sub> /<br>VCOM | VG <sub>OFF</sub> /<br>VCOM | VG <sub>ON</sub>      | NAVDD                 | AVDD                  |                 |

| 3               | 0        | 1         | 0        | NAVDD             | AVDD                  | VG <sub>OFF</sub>           | VG <sub>ON</sub> /<br>VCOM  | VG <sub>ON</sub> /<br>VCOM  | VG <sub>OFF</sub>     | AVDD                  | NAVDD                 | Default setting |

| 4               | 0        | 1         | 1        | NAVDD             | AVDD                  | VGON                        | VG <sub>OFF</sub> /<br>VCOM | VG <sub>OFF</sub> /<br>VCOM | VG <sub>ON</sub>      | AVDD                  | NAVDD                 |                 |

| 5               | 1        | 0         | 0        | NAVDD             | VG <sub>OFF</sub>     | AVDD                        | VG <sub>ON</sub> /<br>VCOM  | VGON/<br>VCOM               | AVDD                  | VG <sub>OFF</sub>     | NAVDD                 |                 |

| 6               | 1        | 0         | 1        | VG <sub>OFF</sub> | VG <sub>ON</sub>      | NAVDD                       | AVDD/<br>VCOM               | AVDD/<br>VCOM               | NAVDD                 | VG <sub>ON</sub>      | VG <sub>OFF</sub>     |                 |

| 7               | 1        | 1         | 0        | AVDD/<br>NAVDD    | VG <sub>OFF</sub>     | VG <sub>ON</sub> /<br>VCOM  | _                           | VG <sub>ON</sub> /<br>VCOM  | VG <sub>OFF</sub>     | AVDD/<br>NAVDD        | _                     |                 |

| 8               | 1        | 1         | 1        | AVDD/<br>NAVDD    | VG <sub>ON</sub>      | VG <sub>OFF</sub> /<br>VCOM | _                           | VG <sub>OFF</sub> /<br>VCOM | VGON                  | AVDD/<br>NAVDD        | _                     |                 |

The times in Table 2 are determined by the delayt1, delayt2 and delayt3 settings in the DELAY-VCOM\_LSB register. The

fastest power-up is obtained by setting the delays to 0.

The output voltages are not monitored during off sequencing; each output is turned off in turn using the programmed delays. When the delays are set to zero, outputs are turned off in sequence with 1ms delays .A sequence can be stored in non-volatile memory by writing to the burn\_otp\_reg register.

The V18 linear regulator is powered down 200ms after the power-down sequence is complete. After this time, the device is in shut-down mode and can be restarted by setting the EN input high.

#### **Sequencing Diagram**

Figure 1. Sequencing Example (Sequence 1, Not to Scale)

#### **VCOM Buffer**

The VCOM output voltage is programmed using I<sup>2</sup>C to a value between -2.49V and +1V. The 9-bit value can also be stored in non-volatile memory. The most-significant bits of the VCOM voltage setting are in the VCOM25 register while the least-significant bit is the vcom25\_0 bit in the DELAY-DELAYVCOM\_LSB register.

The VCOM buffer can output peak currents up to  $\pm 120$ mA. If the VCOM output voltage deviates from the set value by more than 0.25V, a VCOM fault is detected and flagged with the vcom\_flt bit in the FAULT2 register. When this fault is detected, the VCOM buffer continues to function—it is not automatically disabled. Note that a fault condition can lead to high power dissipation in the VCOM buffer and could lead to thermal shutdown of the entire device. If the VCOM buffer is continuously in current limit for more than the time set by tfault[1:0], it is disabled together with the AVDD, NAVDD, VGH and VGL outputs to avoid damage to the IC. Also in this case the vcom\_flt bit is set.

The maximum capacitive load on the VCOM output is 10nF. If higher capacitance loads are used, a series resistor should be employed to maintain stability.

To calculate the value to write to the VCOM25 register use the following equation:

$$VCOM25 = \frac{V_{COM} + 2.49}{0.00683}$$

The correspondence between the VCOM set value and the VCOM voltage is shown in Table 3.

#### **Table 3. VCOM Settings**

| VCOM25 REGISTER VALUE | VCOM VOLTAGE (V) |

|-----------------------|------------------|

| 0x1FF                 | 1                |

| 0x1FE                 | 0.9932           |

**Table 3. VCOM Settings (continued)**

| 0x16E | +0.0098 |

|-------|---------|

| 0x16D | +0.003  |

| 0x16C | -0.0039 |

|       |         |

| 0x002 | -2.4763 |

| 0x001 | -2.4832 |

| 0x000 | -2.49   |

#### **VCOMN Negative Power Supply**

A linear regulator is implemented to derive a regulated -3.5V for the VCOM buffer from the NAVDD supply. The npn transistor connected to the VCB pin acts as the pass transistor of the regulator. The peak output current of the regulator is the same as the peak negative drive current from the VCOM output, or at least 120mA. The device senses the voltage at VCOMN and regulates it to -3.5V by driving VCB. The peak drive current for the base of the external npn is at least 5mA.

#### Limiting the Range of VCOM Voltage

When temperature compensation is not enabled, it is possible to limit the excursion of VCOM to a range between the values set in the VCOM\_MIN and VCOM\_MAX registers. If an attempt is made to write a value outside the set range to VCOM25, the VCOM output voltage is not updated and the I<sup>2</sup>C interface issues a NACK.

#### **VCOM Temperature Compensation**

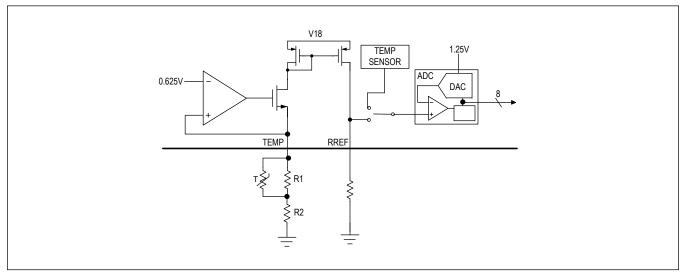

The VCOM output voltage can be compensated for temperature changes using a temperature-sensitive component (e.g. an NTC thermistor) connected to the TEMP input or an internal temperature sensor. Select the sensor to be used with the int\_sensor bit in the CONFIG register (the default configuration is to use the external sensor). The TEMP pin is forced to 625mV and the current drawn from it is mirrored on the R<sub>REF</sub> pin. The voltage generated due to the resistor on R<sub>REF</sub> is fed to the internal 8-bit ADC, which has a reference voltage of 1.25V. The input to the ADC is therefore as follows:

$$V_{\rm ADC} = \frac{0.625 \times R_{\rm RREF}}{R_{\rm TEMP}}$$

With reference to Figure 2:  $R_{TEMP} = (R_{NTC} \mid \mid R1) + R2$

The highly non-linear NTC characteristic can be modified depending on which temperature (cold, room, or hot) necessitates the highest resolution. As an example in <u>Figure 2</u>, a reference resistor is connected to  $R_{REF}$  while a combination of the NTC and two low-TC resistors R1 and R2 are connected to TEMP. In this way, an ADC reading that is steeper at higher temperatures is obtained, enhancing the resolution of the ADC there. When temperature compensation is enabled, the value of the voltage on the  $R_{REF}$  pin is available in the TEMP (0x01) register.

Temperature compensation is enabled by setting the T\_comp\_en bit in the DELAY-VCOM\_LSB register. When T\_comp\_en is high, the voltage on the R<sub>REF</sub> pin is measured and the VCOM output voltage is updated at a rate of 1Hz. At start-up, even with temperature compensation enabled, there is a delay before compensation becomes active due to the time needed to sample the temperature. For this reason, the device always starts up with the VCOM25 voltage value on VCOM.

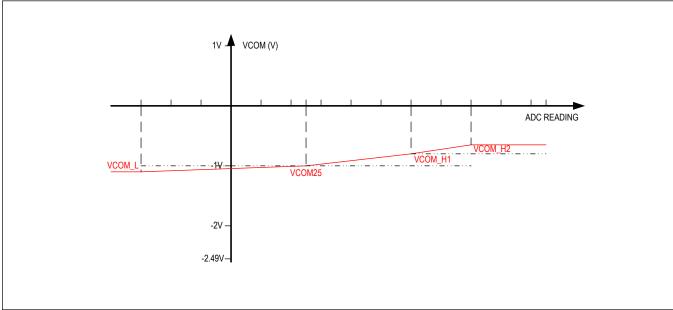

The VCOM value at +25°C is the value written in the VCOM25 register together with the LSB from DELAY-VCOM\_LSB register. This value serves as the reference for all other VCOM values. The 5-bit values in the VCOM\_L, and VCOM\_H1 registers represent the change in VCOM from the VCOM25 value at the temperature represented by an ADC reading of VTEMP\_L and VTEMP\_H1. The value in the VCOM\_H2 register represents the positive shift in VCOM from VCOM\_H1. The VCOM\_L value represents a negative shift in VCOM while VCOM\_H1 and VCOM\_H2 represent positive shifts.

#### **NTC Connection Diagram**

Figure 2. Possible NTC Connection

#### **Internal Temperature Sensor**

The internal temperature sensor senses the junction temperature of the IC which may be significantly different from the ambient temperature. To use the internal sensor, set the int\_sensor bit in the CONFIG register to 1. The internal temperature sensor has a temperature coefficient of 2mV/°C and a nominal output voltage of 620mV at +25°C.

When the internal temperature sensor is selected, it is connected directly to the ADC input.

#### **Temperature Compensation Curve**

Figure 3. Temperature Compensation Curve

#### **Fault Handling**

The reaction to faults is dependent on whether the device is in I<sup>2</sup>C or stand-alone mode.

In I<sup>2</sup>C mode, the following faults, if not masked, cause the FLTB pin to assert low: avdd\_uv, navdd\_uv, vgon\_uv, vgoff\_uv, vcom\_flt, nv\_flt, th\_shdn, vin\_uvlo, and par\_err. The th\_warn fault is masked by default and must be explicitly enabled using the th\_warn\_mask bit.

When the ADD pin is left floating (I<sup>2</sup>C interface not used), the FLTB pin outputs a pulse train of varying duty cycle depending on the detected fault as shown in Table 4.

**Table 4. FLTB Duty Cycle in Stand-Alone Mode**

| DUTY-CYCLE            | FAULT                                       |  |  |  |  |  |

|-----------------------|---------------------------------------------|--|--|--|--|--|

| 75%                   | VG <sub>ON</sub> or VG <sub>OFF</sub> fault |  |  |  |  |  |

| 50%                   | AVDD, NAVDD or HVINP fault                  |  |  |  |  |  |

| 25%                   | VCOM fault                                  |  |  |  |  |  |

| 0% (continuously low) | NV fault or thermal shutdown                |  |  |  |  |  |

The frequency at the FLTB pin is 1kHz when indicating a fault. If multiple faults are present, the highest-priority fault is indicated. The <u>Table 4</u> list is in order of priority with the highest priority listed last.

#### **Undervoltage Faults on Source and Gate Outputs**

When an undervoltage is detected on any of the AVDD, NAVDD,  $VG_{ON}$ , or  $VG_{OFF}$  outputs, all of the outputs are turned off and the appropriate fault bit is set in the FAULT1 register. At the same time, the FLTB pin asserts low. Depending on the setting of the tretry[1:0] bits, the subsequent behavior of the device is as follows:

- tretry = 01, 10 or 11: After 0.95s or 1.9s a retry is performed where all outputs are turned on in the appropriate sequence. If the fault is still present, the output will be disabled again after tfault[1:0]. A total of three retries are performed, after which no further retry attempts are performed (the device can be restarted by toggling power or the EN pin or by using the RESTART command). If tretry = 11 retries continue until the fault is removed and normal function can resume.

- tretry = 00: No retry is attempted (the device can be restarted by toggling power or the EN pin or by using the RESTART command).

If a short-circuit is encountered during start-up, device operation is halted, all outputs are disabled, and the subsequent behavior depends on the setting of retry[1:0] as described above. The short-circuit checks on  $VG_{ON}$  and  $VG_{OFF}$  are enabled 1ms after the pins are enabled. The C version does not have short-circuit checks on  $VG_{ON}$  and  $VG_{OFF}$ .