#### **General Description**

The MAX3744/MAX3745 transimpedance amplifiers provide a compact, low-power solution for communication up to 2.7Gbps. They feature 330nA input-referred noise at 2.1GHz bandwidth (BW) with 0.85pF input capacitance. The parts also have >2mAp-p AC input overload.

Both parts operate from a single +3.3V supply and consume 93mW. The MAX3744/MAX3745 are in a compact 30-mil x 50-mil die and require no external compensation capacitor. A space-saving filter connection is provided for positive bias to the photodiode through an on-chip  $580\Omega$  resistor to VCC. These features allow easy assembly into a low-cost TO-46 or TO-56 header with a photodiode.

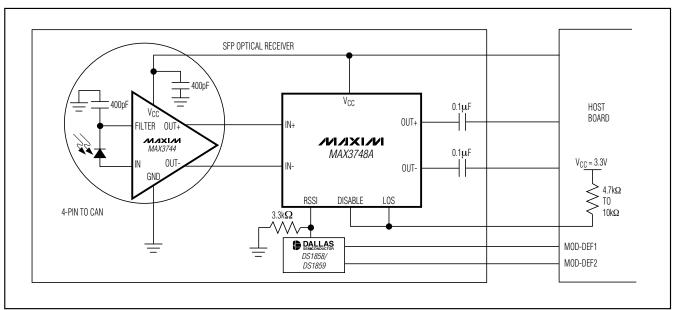

The MAX3744 and MAX3748A receiver chip set provides an RSSI output using a Maxim-proprietary interface technique. The MAX3744 preamplifier, MAX3748A postamplifier, and DS1858/DS1859 SFP controller meet all the SFF-8472 digital diagnostic requirements.

#### **Applications**

Up to 2.7Gbps SFF/SFP Optical Receivers Optimized for Small-Form-Factor Pluggable (SFP) **Optical Receivers**

## **Features**

- ♦ Up to 2.7Gbps (NRZ) Data Rates

- ♦ RSSI Implementation in 4-Pin TO-46 Header (MAX3744)

- ♦ 10psp-p Deterministic Jitter for <100µAp-p Input Current

- ♦ 330nA<sub>RMS</sub> Input-Referred Noise at 2.1GHz **Bandwidth**

- ◆ 28mA Supply Current at +3.3V

- ♦ 2GHz Small-Signal Bandwidth

- ♦ 2.0mAp-p AC Overload

- ♦ Die Size: 30 mils x 50 mils

#### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX3744E/D | -40°C to +85°C | Dice**      |

| MAX3745E/D | -40°C to +85°C | Dice**      |

<sup>\*\*</sup>Dice are guaranteed to operate from -40°C to +85°C, but are tested only at  $T_A = +25$ °C.

## **Typical Application Circuit**

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +2.97V \text{ to } +3.63V \text{ and } T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}.$  Typical values are at  $V_{CC} = +3.3V$ , source capacitance  $(C_{IN}) = 0.85 \text{pF}$ , and  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.) (Notes 1, 2)

| PARAMETER                                   | SYMBOL           | CONDITIONS                                                                                    |                        | MIN | TYP | MAX | UNITS             |

|---------------------------------------------|------------------|-----------------------------------------------------------------------------------------------|------------------------|-----|-----|-----|-------------------|

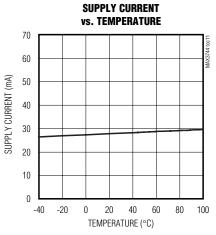

| Supply Current                              | Icc              | Including CML output current (I <sub>IN</sub> = 0)                                            |                        |     | 28  | 41  | mA                |

| Input Bias Voltage                          |                  |                                                                                               |                        |     |     | 1.0 | V                 |

| Input Overload                              |                  | (Note 3)                                                                                      |                        | 2   |     |     | mA <sub>P-P</sub> |

| Input-Referred Noise                        | - I <sub>N</sub> | C <sub>IN</sub> = 0.85pF, BW = 933MHz                                                         |                        |     | 206 |     | nARMS             |

|                                             |                  | C <sub>IN</sub> = 0.85pF, BW = 2.1GHz                                                         |                        |     | 330 | 430 |                   |

|                                             |                  | C <sub>IN</sub> = 0.85pF, BW = 18GHz                                                          |                        |     |     | 620 |                   |

|                                             |                  | C <sub>IN</sub> = 0.85pF, BW = 933MHz                                                         |                        |     | 206 |     |                   |

|                                             |                  | C <sub>IN</sub> = 0.6pF, BW = 2.1GHz                                                          |                        |     | 300 | 380 |                   |

|                                             |                  | C <sub>IN</sub> = 0.6pF, BW = 18GHz                                                           |                        |     |     | 550 |                   |

| Differential Transimpedance                 |                  | Differential output, I <sub>IN</sub> = 40µA <sub>AVE</sub>                                    |                        | 2.8 | 3.5 | 4.5 | kΩ                |

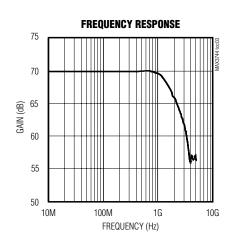

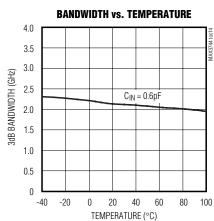

| Consult Circums Department of the (Nata C)  | BW               | -3dB, $C_{IN} = 0.6pF$                                                                        |                        | 1.8 | 2   |     | GHz               |

| Small-Signal Bandwidth (Note 3)             |                  | -3dB, C <sub>IN</sub> = 0.85pF                                                                |                        | 1.6 | 1.8 |     | GHZ               |

| Low-Frequency Cutoff                        |                  | -3dB, input current = 20µA <sub>AVE</sub> (Note 3)                                            |                        |     |     | 30  | kHz               |

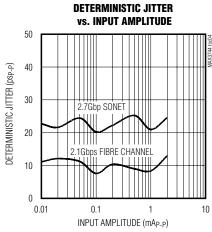

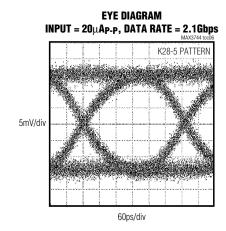

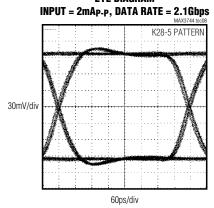

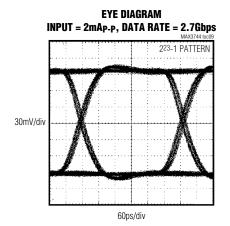

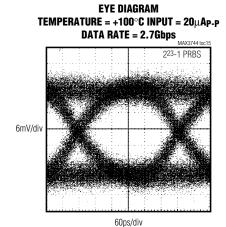

| Deterministic Jitter (Notes 3, 5)           | DJ               | 100µA <sub>P-P</sub> < input ≤ 2mA <sub>P-P</sub>                                             | 2.1Gbps, K28.5 pattern |     | 14  | 31  | 000.0             |

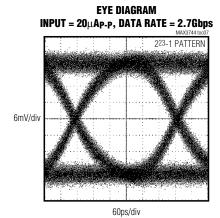

|                                             |                  |                                                                                               | 2.7Gbps, 231-1 pattern |     | 24  |     |                   |

|                                             |                  | 10μA <sub>P-P</sub> < input ≤ 100μA <sub>P-P</sub>                                            | 2.1Gbps, K28.5 pattern |     | 10  | 16  | psp-p             |

|                                             |                  |                                                                                               | 2.7Gbps, 231-1 pattern |     | 20  |     |                   |

| Filter Resistance                           |                  |                                                                                               | ·                      | 510 | 580 | 690 | Ω                 |

| Differential Output Resistance (OUT+, OUT-) |                  |                                                                                               |                        | 85  | 100 | 115 | Ω                 |

| Maximum Differential Output<br>Voltage      | V <sub>OD</sub>  | Input > $50\mu A_{AVE}$ , output termination $50\Omega$ to $V_{CC}$ (output in limited state) |                        | 220 | 280 | 400 | mV <sub>P-P</sub> |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +2.97 \text{V to } +3.63 \text{V and T}_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}.$  Typical values are at  $V_{CC} = +3.3 \text{V}$ , source capacitance  $(C_{IN}) = 0.85 \text{pF}$ , and  $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted.) (Notes 1, 2)

| PARAMETER                                                   | SYMBOL | CONDITIONS                                                                                                               |                  | MIN | TYP | MAX  | UNITS |

|-------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|------|-------|

| Single-Ended Output Common-<br>Mode Minimum Level (MAX3744) |        | Relative to V <sub>CC</sub> , I <sub>IN</sub> = 1mA <sub>AVE</sub>                                                       |                  | 540 | 490 |      | mV    |

| Output Data Transition Time                                 |        | Input > 200µAp-p 20% to 80% rise/fall time (Note 3)                                                                      |                  |     | 80  | 140  | ps    |

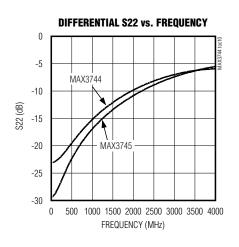

| Differential Output Beturn Less                             |        | Frequency ≤ 1GHz<br>1GHz < frequency ≤ 2GHz                                                                              |                  |     | 17  |      | ٩D    |

| Differential Output Return Loss                             |        |                                                                                                                          |                  |     | 10  |      | dB    |

| Power-Supply Noise Rejection                                | PSNR   | I <sub>IN</sub> = 0                                                                                                      | f < 1MHz         |     | 46  |      | dB    |

|                                                             |        | (Note 6)                                                                                                                 | 1MHz ≤ f < 10MHz |     | 34  |      | ub_   |

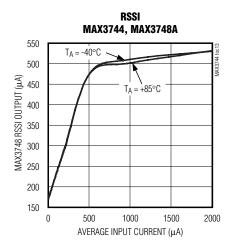

| RSSI Gain (MAX3744)                                         | ARSSI  | (Note 7)                                                                                                                 |                  |     | 21  |      | A/A   |

| RSSI Gain Stability (MAX3744)                               |        | 10log(A <sub>RSSI</sub> /A <sub>RSSI-NOM</sub> ) where A <sub>RSSI-NOM</sub> = A <sub>RSSI</sub> at 3.3V, +25°C (Note 3) |                  |     |     | 0.24 | dB    |

- **Note 1:** Die parameters are production tested at room temperature only, but are guaranteed by design and characterization from -40°C to +85°C.

- Note 2: Source capacitance represents the total capacitance at the IN pad during characterization of the noise and bandwidth parameters.

- Note 3: Guaranteed by design and characterization.

- Note 4: Input-referred noise is:

- Note 5: Deterministic jitter is the sum of pulse-width distortion (PWD) and pattern-dependent jitter (PDJ).

- Note 6: Power-supply noise rejection PSNR =  $-20\log(\Delta V_{OUT} / \Delta V_{CC})$ , where  $\Delta V_{OUT}$  is the differential output voltage and  $\Delta V_{CC}$  is the noise on  $V_{CC}$ .

- Note 7:

$$\begin{split} A_{RSSI} &= \frac{I_{OUT\_CM}(I_{IN} = 400\mu\text{A}) - I_{OUT\_CM}(I_{IN} = 0\mu\text{A})}{400\mu\text{A}} \\ \text{where } I_{OUT\_CM} &= \frac{I_{OUT+} + I_{OUT-}}{2} \\ \text{RSSI range is from } I_{IN} = 6\mu\text{A to } 500\mu\text{A} \end{split}$$

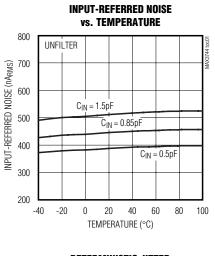

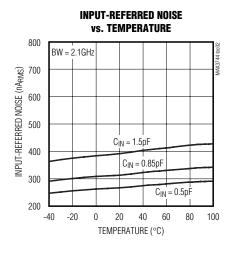

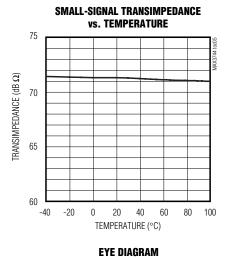

### **Typical Operating Characteristics**

( $V_{CC} = +3.3V$ ,  $C_{IN} = 0.85pF$ ,  $T_A = +25$ °C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

( $V_{CC} = +3.3V$ ,  $C_{IN} = 0.85pF$ ,  $T_A = +25$ °C, unless otherwise noted.)

### **Pin Description**

| MAX3744/<br>MAX3745<br>BOND PAD | NAME   | FUNCTION                                                                                                                                                                                                             |

|---------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3                            | Vcc    | Supply Voltage                                                                                                                                                                                                       |

| 2, 7                            | N.C.   | No Connection                                                                                                                                                                                                        |

| 4                               | IN     | TIA Input. Signal current from photodiode flows into this pin.                                                                                                                                                       |

| 5                               | FILTER | Provides bias voltage for the photodiode through a $580\Omega$ resistor to V <sub>CC</sub> . When grounded, this pin disables the DC cancellation amplifier to allow a DC path from IN to OUT+ and OUT- for testing. |

| 6, 10                           | GND    | Supply Ground                                                                                                                                                                                                        |

| 8                               | OUT-   | Inverting Data Output. Current flowing into IN causes the voltage at OUT- to decrease. For the MAX3744, the common mode between OUT+ and OUT- is proportional to the average input current.                          |

| 9                               | OUT+   | Noninverting Data Output. Current flowing into IN causes the voltage at OUT+ to increase. For the MAX3744, the common mode between OUT+ and OUT- is proportional to the average input current.                       |

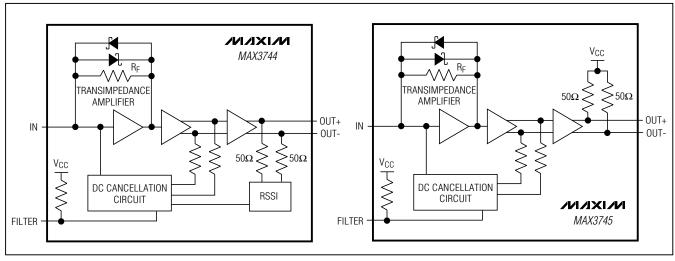

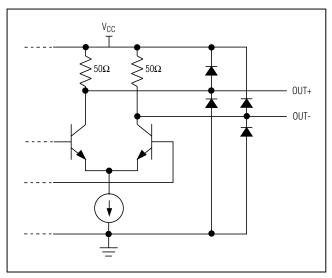

Figure 1. Functional Diagram

## **Detailed Description**

The MAX3744/MAX3745 are transimpedance amplifiers designed for up to 2.7Gbps SFF/SFP transceiver modules. A functional diagram of the MAX3744/MAX3745 is shown in Figure 1. The MAX3744/MAX3745 comprise a transimpedance amplifier stage, a voltage amplifier stage, an output buffer, and a direct-current (DC) feedback cancellation circuit. The MAX3744 also includes a signal strength indicator (RSSI). To provide this signal in

a standard 4-pin TO header, the RSSI level is added to the common mode of the differential data output pins.

#### **Transimpedance Amplifier Stage**

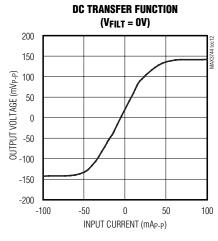

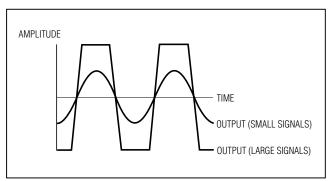

The signal current at the input flows into the summing node of a high-gain amplifier. Shunt feedback through the resistor RF converts this current to a voltage. In parallel with the feedback resistor are two back-to-back Schottky diodes that clamp the output signal for large input currents, as shown in Figure 2.

Figure 2. MAX3744/MAX3745 Limited Output

#### **Voltage Amplifier Stage**

The voltage amplifier stage provides gain and converts the single-ended input to differential outputs.

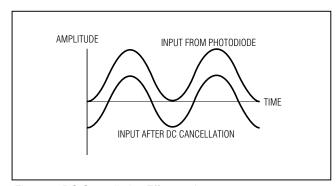

#### **DC Cancellation Circuit**

The DC cancellation circuit uses low-frequency feedback to remove the DC component of the input signal (Figure 3). This feature centers the input signal within the transimpedance amplifier's linear range, thereby reducing pulse-width distortion caused by large input signals. The DC cancellation circuit is internally compensated and therefore does not require external capacitors.

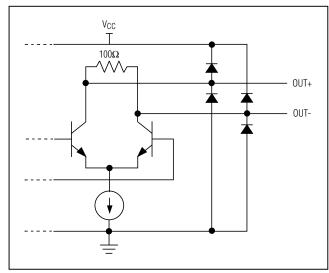

#### **Output Buffer**

The output buffer provides a reverse-terminated voltage output. The buffer is designed to drive a  $100\Omega$  differential load between OUT+ and OUT-. The MAX3744 must be DC-coupled to the MAX3748A. See Figures 4 and 5.

For optimum supply-noise rejection, the MAX3745 should be terminated with a matched load. If a single-ended output is required, the unused output should be terminated to a 50 $\Omega$  resistor to V<sub>CC</sub>. The MAX3745 does not drive a DC-coupled, 50 $\Omega$  grounded load; however, it does drive a compatible 50 $\Omega$  CML input.

#### Signal-Strength Indicator

The MAX3744 produces a signal proportional to the average photodiode current. This is added to the common mode of the data outputs OUT+ and OUT-. This signal is intended for use with the MAX3748A to provide a ground-referenced RSSI voltage.

## Applications Information

#### Signal-Strength Indicator

The SFF-8472 digital diagnostic specification requires monitoring of input receive power. The MAX3748A and MAX3744 receiver chipset allows for the monitoring of the average receive power by measuring the average DC current of the photodiode.

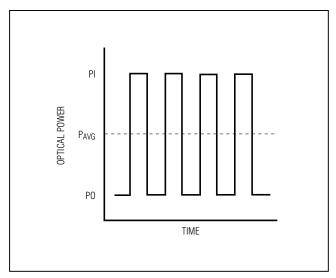

Figure 3. DC Cancellation Effect on Input

Figure 4. Equivalent Output MAX3744

Figure 5. Equivalent Output MAX3745

The MAX3744 preamp measures the average photodiode current and provides the information to the output common mode. The MAX3748A RSSI detect block senses the common-mode DC level of input signals IN+ and IN- and provides a ground-level-referenced output signal of the photodiode current. The advantage of this implementation is that it allows the TIA to be packaged in a low-cost conventional 4-pin TO-46 header.

The MAX3748A RSSI output is connected to an analog input channel of the DS1858/DS1859 SFP controller to convert the analog information into a 16-bit word. The DS1858/DS1859 provide the received power information to the host board of the optical receiver through a 2-wire interface. The DS1859 allows for internal calibration of the receive power monitor.

The MAX3744 and the MAX3748A have been optimized to achieve RSSI stability of better than 2.5dB within the  $6\mu A$  to  $500\mu A$  range of average input photodiode current. To achieve the best accuracy, Maxim recommends receive power calibration at the low end  $(6\mu A)$  and the high end  $(500\mu A)$  of the required range.

#### **Optical Power Relations**

Many of the MAX3744/MAX3745 specifications relate to the input signal amplitude. When working with optical receivers, the input is sometimes expressed in terms of average optical power and extinction ratio. Figure 6 and Table 1 show relations that are helpful for converting optical power to input signal when designing with the MAX3744/MAX3745. (Refer to Application Note HFAN–3.0.0: Accurately Estimating Optical Receiver Sensitivity.)

#### **Optical Sensitivity Calculation**

The input-referred RMS noise current (I<sub>N</sub>) of the MAX3744/MAX3745 generally determines the receiver sensitivity. To obtain a system bit-error rate (BER) of 1E-12, the signal-to-noise ratio must always exceed 14.1. The input sensitivity, expressed in average power, can be estimated as:

Sensitivity =

$$10log\left(\frac{14.1 \times I_N(r_e + 1)}{2\rho(r_e - 1)}1000\right)dBm$$

where  $\rho$  is the photodiode responsivity in A/W and IN is RMS current in amps.

#### **Input Optical Overload**

The overload is the largest input that the MAX3744/ MAX3745 can accept while meeting deterministic jitter specifications. The optical overload can be estimated in terms of average power with the following equation:

Overload =

$$10\log\left(\frac{2\text{mA}_{RMS}(r_e + 1)}{2\rho(r_e - 1)}1000\right)dBm$$

#### **Optical Linear Range**

The MAX3744/MAX3745 have high gain, which limits the output when the input signal exceeds 50µAp-p. The MAX3744/MAX3745 operate in a linear range (10% linearity) for inputs not exceeding:

Linear Range =

$$10\log\left(\frac{50\mu A_{RMS}(r_e + 1)}{2\rho(r_e - 1)}1000\right)dBm$$

**Table 1. Optical Power Relations**

| PARAMETER               | SYMBOL         | RELATION                                                        |

|-------------------------|----------------|-----------------------------------------------------------------|

| Average power           | Pavg           | $PAVG = (P_0 + P_1) / 2$                                        |

| Extinction ratio        | r <sub>e</sub> | $r_e = P_1 / P_0$                                               |

| Optical power of a 1    | P <sub>1</sub> | $P_1 = 2P_{AVG}(r_e) / (r_e + 1)$                               |

| Optical power of a zero | P <sub>0</sub> | $P_0 = 2P_{AVG} / (r_e + 1)$                                    |

| Signal amplitude        | Pin            | $P_{IN} = P_1 - P_0$ ; $P_{IN} = 2P_{AVG}(r_e - 1) / (r_e + 1)$ |

Note: Assuming 50% average duty cycle and mark density.

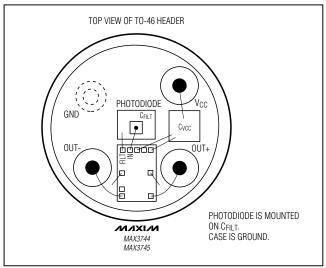

#### **Layout Considerations**

Noise performance and bandwidth are adversely affected by capacitance at the IN pad. Minimize capacitance on this pad and select a low-capacitance photodiode. Assembling the MAX3744/MAX3745 in die form using chip and wire technology provides the best possible performance. Figure 7 shows a suggested layout for a TO header for the MAX3744/MAX3745. The placement of the filter cap to minimize the ground loop of the photodiode is required to achieve the specified bandwidth. The OUT+ and OUT- bond wire lengths should also be minimized to meet the bandwidth specification. Special care should be taken to ensure that ESD at IN does not exceed 500V.

#### **Photodiode Filter**

Supply voltage noise at the cathode of the photodiode produces a current  $I = C_{PD} \Delta V/\Delta t$ , which reduces the receiver sensitivity ( $C_{PD}$  is the photodiode capacitance.) The filter resistor of the MAX3744/MAX3745, combined with an external capacitor, can be used to reduce this noise (see the *Typical Application Circuit*).

Current generated by supply noise voltage is divided between CFILTER and CPD. The input noise current due to supply noise is (assuming the filter capacitor is much larger than the photodiode capacitance):

INOISE = (VNOISE)(CPD) / (RFILTER)(CFILTER)

If the amount of tolerable noise is known, the filter capacitor can be easily selected:

CFILTER = (VNOISE)(CPD) / (RFILTER)(INOISE)

For example, with maximum noise voltage = 100mVp-p, CpD = 0.85pF, RFILTER = 600 $\Omega$ , and INOISE selected to be 350nA:

$C_{FILTER} = (100 \text{mV})(0.85 \text{pF}) / (600 \Omega)(350 \text{nA}) = 405 \text{pF}$

#### Wire Bonding

For high-current density and reliable operation, the MAX3744/MAX3745 use gold metalization. Connections to the die should be made with gold wire only, using ball-bonding techniques. Die thickness is typically 14 mils (0.4mm).

Figure 6. Optical Power Relations

Figure 7. Suggested Layout for TO-46 Header

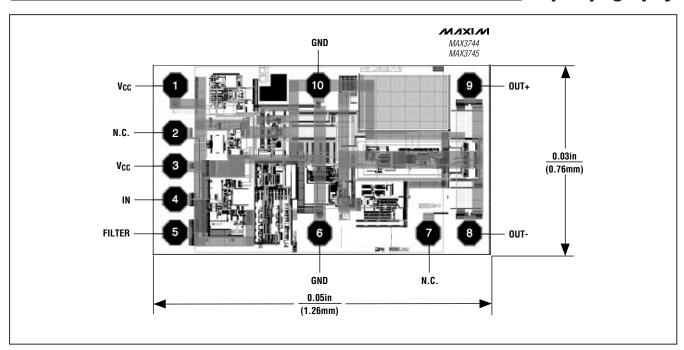

## **Chip Topography**

#### **Pad Coordinates**

| PAD | COORDINATES (μm)<br>X | COORDINATES (μm)<br>Υ |

|-----|-----------------------|-----------------------|

| 1   | 1.4                   | 495.6                 |

| 2   | 0                     | 336                   |

| 3   | 0                     | 224                   |

| 4   | 0                     | 112                   |

| 5   | 0                     | 0                     |

| 6   | 494.2                 | -1.4                  |

| 7   | 865.2                 | -1.4                  |

| 8   | 1005.2                | -1.4                  |

| 9   | 1005.2                | 495.6                 |

| 10  | 490                   | 495.6                 |

## **Chip Information**

**TRANSISTOR COUNT: 301** PROCESS: SiGe Bipolar SUBSTRATE: ISOLATED

DIE THICKNESS: 0.014in ±0.001in

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.