### **General Description**

The MAX3971 is a compact, low-power, 10.3Gbps limiting amplifier. It accepts signals over a wide range of input voltage levels and provides constant-level output voltages with controlled edge speeds. It functions as a data quantizer. The output of the amplifier is a 250mVP-P differential CML signal with a  $100\Omega$  differential termination.

The MAX3971 is designed to work with the MAX3970, a 10.3Gbps transimpedance amplifier (TIA). The limiting amplifier operates on a single +3.3V supply and consumes only 155mW. The part functions over the 0°C to +85°C temperature range. It also has a disable function that allows the outputs to be squelched if required by the application.

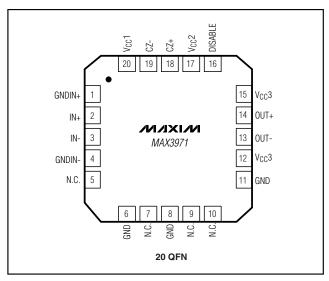

The MAX3971 is offered in die form and in a compact 4mm x 4mm, 20-pin QFN plastic package.

### **Applications**

10-Gigabit Ethernet Optical Receivers VSR OC-192 Receivers 10-Gigabit Fibre Channel Receivers

#### Features

- ♦ Single +3.3V Power Supply

- **♦ 155mW Power Consumption**

- ♦ 9.5mVp-p Input Sensitivity

- ♦ 800mVp-p Input Overload

- ♦ 3.4psp-p Deterministic Jitter

- ♦ Dice and 4mm x 4mm QFN Packages

- **♦ Output Disable Feature**

### **Ordering Information**

| PART       | TEMP. RANGE  | PIN-PACKAGE | PKG<br>CODE |

|------------|--------------|-------------|-------------|

| MAX3971UGP | 0°C to +85°C | 20 QFN      | G2044-4     |

| MAX3971U/D | 0°C to +85°C | Dice*       | _           |

<sup>\*</sup>Dice are designed to operate over a 0°C to +110°C junction temperature (T<sub>J</sub>) range, but are tested and guaranteed at  $T_A = +25$ °C.

Pin Configuration appears at end of data sheet.

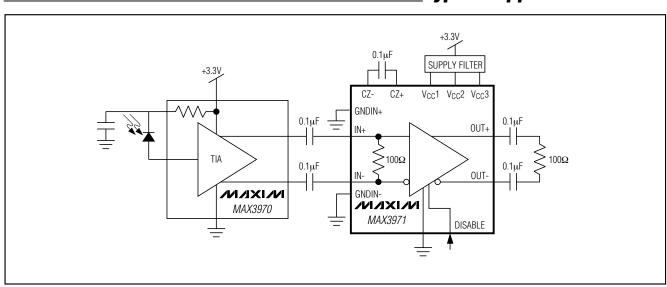

### **Typical Application Circuit**

MIXIM

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, VCC1, VCC2, VCC3         | 0.5V to +0.5V                |

|------------------------------------------|------------------------------|

| Voltage at IN+, IN-, DISABLE,            |                              |

| CZ+, CZ-, OUT+, OUT                      | $+0.5V$ to $(V_{CC} + 0.5V)$ |

| Differential Voltage Between CZ+ and CZ- | ±1V                          |

| Differential Voltage Between IN+ and IN  | ±2.5V                        |

| Continuous Power Dissipation (TA = +85°C |                              |

| 20-Lead QFN (derate 20mW/°C above        | +85°C)1.3W                   |

| Operating Ambient Temperature Range. | 40°C to +85°C  |

|--------------------------------------|----------------|

| Storage Temperature Range            | 55°C to +150°C |

| Die Attach Temperature               | +400°C         |

| Lead Temperature (soldering, 10s)    | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, T_A = 0 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}. \text{ Typical values are at } V_{CC} = +3.3 \text{V}, \text{ output load} = 50 \Omega \text{ to } V_{CC}, T_A = +25 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Data mark density is 50%.)

| PARAMETER                               | SYMBOL                          | CONDITIONS                                                     | MIN | TYP                       | MAX | UNITS             |

|-----------------------------------------|---------------------------------|----------------------------------------------------------------|-----|---------------------------|-----|-------------------|

| Supply Current                          | Icc                             |                                                                |     | 47                        | 85  | mA                |

| Small-Signal Bandwidth                  | BW                              |                                                                |     | 10                        |     | GHz               |

| Low-Frequency Cutoff                    |                                 | CZ = 0.1µF                                                     |     | 40                        | 160 | kHz               |

| Data Rate                               |                                 |                                                                |     | 10                        |     | Gbps              |

|                                         |                                 | 10mV <sub>P-P</sub> input, K28.5 pattern at 10.3Gbps (Note 1)  |     | 8                         |     |                   |

| Deterministic Jitter                    |                                 | 20mV <sub>P-P</sub> input, K28.5 pattern at 10.3Gbps (Note 1)  |     | 4.7                       | 14  | psp-p             |

|                                         |                                 | 800mV <sub>P-P</sub> input, K28.5 pattern at 10.3Gbps (Note 1) |     | 3.4                       | 7   |                   |

| Random Jitter                           |                                 | 20mV <sub>P-P</sub> to 800mV <sub>P-P</sub> (Note 2)           |     | 0.7                       | 1.0 | psRMS             |

| Transition Time, Output                 | t <sub>r</sub> , t <sub>f</sub> | 20% to 80%, OUT+, OUT-                                         |     | 20                        | 30  | ps                |

| Input Sensitivity                       | V <sub>IN-min</sub>             | BER = 1E-12, 2 <sup>23</sup> - 1PRBS, 10.3Gbps                 |     |                           | 9.5 | mV <sub>P-P</sub> |

| Input Overload                          | V <sub>IN-max</sub>             |                                                                | 800 |                           |     | mV <sub>P-P</sub> |

| Data Input Resistance                   | R <sub>IN</sub>                 | Single-ended                                                   | 42  | 52                        | 58  | Ω                 |

| Differential Data                       | V <sub>OD1</sub>                | DISABLE high                                                   |     | 1                         | 50  | mV <sub>P-P</sub> |

| Output-Voltage Swing                    | V <sub>OD2</sub>                | DISABLE low                                                    | 190 | 250                       | 400 | IIIVP-P           |

| Data Output Common-Mode<br>Voltage      | V <sub>CM</sub>                 |                                                                |     | V <sub>CC</sub> -<br>0.75 |     | V                 |

| Output Resistance                       | Rout                            | Single-ended                                                   | 42  | 52                        | 58  | Ω                 |

| Data Output Offset when DISABLE is High |                                 |                                                                |     | 75                        |     | mV <sub>P-P</sub> |

| DISABLE Input Current                   |                                 | High = V <sub>CC</sub> , low = GND                             |     | 0.05                      | 1   | mA                |

| DISABLE Input High Voltage              |                                 |                                                                | 2.8 |                           |     | V                 |

| DISABLE Input Low Voltage               |                                 |                                                                |     |                           | 1.4 | V                 |

**Note 1:** Deterministic jitter is measured with a K28.5 pattern (0011 1110 1011 0000 0101). It is the peak-to-peak deviation from the ideal time crossings, measured at the zero-level crossings of the differential output.

**Note 2:** Random jitter is measured with the minimum input signal applied. To achieve a bit error rate of 10<sup>-12</sup>, the peak-to-peak random jitter is 14.1 times the RMS random jitter.

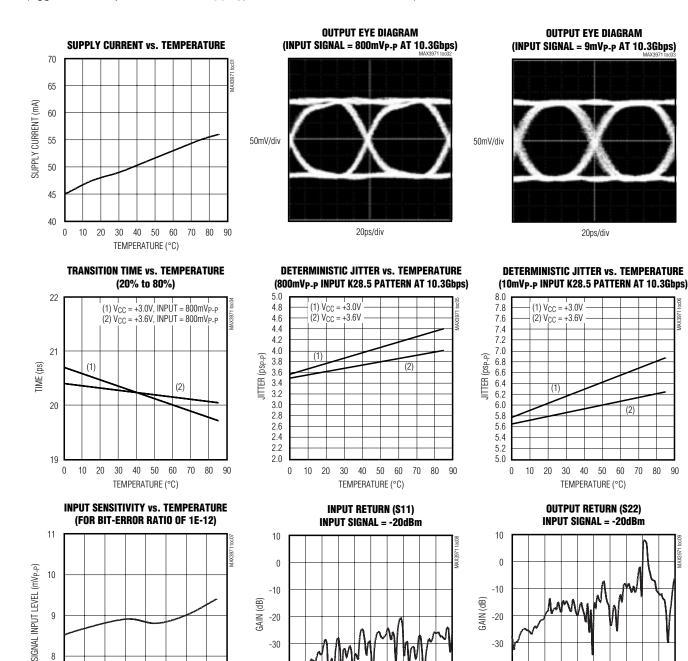

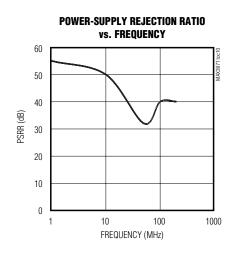

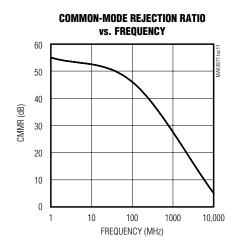

### **Typical Operating Characteristics**

-20

-30

-40

-50

100

2100

4100

FREQUENCY (MHz)

6100

8100

$(V_{CC} = +3.3V, output load = 50\Omega to V_{CC}, T_A = +25^{\circ}C, unless otherwise noted.)$

-20

-30

-40 -50

100

4100

FREQUENCY (MHz)

6100

8100

10,100

30

40 50 60

TEMPERATURE (°C)

70

9

8

10,100

## Typical Operating Characteristics (continued)

$(V_{CC} = +3.3V, output load = 50\Omega to V_{CC}, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Pin Description**

| PIN         | NAME              | FUNCTION                                                                                                                  |

|-------------|-------------------|---------------------------------------------------------------------------------------------------------------------------|

| 1           | GNDIN+            | Input Ground for Shielding Input Signal IN+. Not connected internally.                                                    |

| 2           | IN+               | Noninverting Input Signal                                                                                                 |

| 3           | IN-               | Inverting Input Signal                                                                                                    |

| 4           | GNDIN-            | Input Ground for Shielding Input Signal IN Not connected internally.                                                      |

| 5, 7, 9, 10 | N.C.              | No Connection. Leave unconnected.                                                                                         |

| 6, 8, 11    | GND               | Ground                                                                                                                    |

| 12, 15      | V <sub>CC</sub> 3 | Output Circuitry Power Supply                                                                                             |

| 13          | OUT-              | Inverting Output of Amplifier                                                                                             |

| 14          | OUT+              | Noninverting Output of Amplifier                                                                                          |

| 16          | DISABLE           | When High, the Outputs are Disabled                                                                                       |

| 17          | V <sub>CC</sub> 2 | Power Supply to Circuitry Other than Input and Output Circuits                                                            |

| 18          | CZ+               | Filter Capacitor for Offset Correction. Attach other side of a capacitor to pin 19. See the <i>Detailed Description</i> . |

| 19          | CZ-               | See pin 18.                                                                                                               |

| 20          | V <sub>CC1</sub>  | Input Circuitry Power Supply                                                                                              |

| EP          | Exposed<br>Pad    | Exposed Pad. Must be soldered to supply ground for proper electrical and thermal operation.                               |

# **Detailed Description and Applications Information**

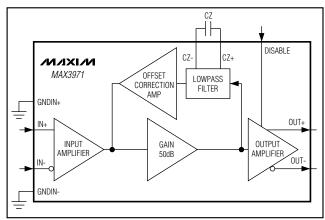

Figure 1 is a functional diagram of the MAX3971 limiting amplifier. The signal path consists of an input buffer followed by a gain stage and output amplifier. A feedback loop provides offset correction by driving the average value of the differential output to zero.

#### **Gain Stage and Offset Correction**

The limiting amplifier provides approximately 50dB gain. This large gain makes the amplifier susceptible to small DC offsets, which cause deterministic jitter. A low-frequency loop is integrated into the limiting amplifier to reduce output offset, typically to less than 2mV.

The external capacitor CZ is required to set the low-frequency cutoff for the offset correction loop and for stability. The time constant of the loop is set by the

Figure 1. Functional Diagram

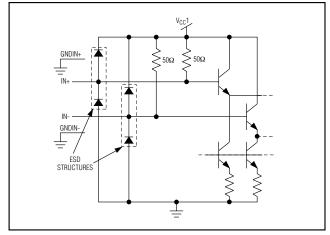

Figure 2. CML Input Equivalent Circuit

product of an equivalent 20k $\Omega$  on-chip resistor and the value of the off-chip capacitor, CZ. For stable operation, the minimum value of CZ is 0.01 $\mu$ F. To minimize pattern-dependent jitter, CZ should be as large as possible. For 10-Gigabit Ethernet applications, the typical value of CZ is 0.1 $\mu$ F. Keep CZ as close to the package as possible.

#### **CML Input Circuit**

The input buffer is designed to accept CML input signals such as the output from the MAX3970 transimpedance amplifier. An equivalent circuit for the input is shown in Figure 2. DC-coupling the inputs is not recommended because doing so prevents the part's offset correction circuitry from working properly. Thus, AC-coupling capacitors are required on the input.

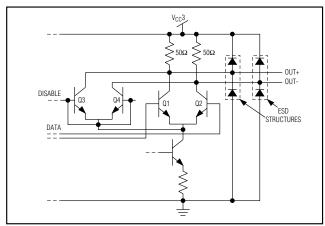

#### **CML Output Circuit**

An equivalent circuit for the output network is shown in Figure 3. It consists of two  $50\Omega$  resistors connected to VCC driven by the collectors of an output differential transistor pair (Q1 and Q2). The differential output signals are clamped by transistors Q3 and Q4 when the DISABLE input is high.

#### **Disable Function**

A logic signal can be applied to the DISABLE pin to squelch the output signal. When the output is disabled, an offset is added to the output, preventing the following stage from oscillating (if DC-coupled).

Figure 3. CML Input Equivalent Circuit Showing Clamping Circuit for Squelching the Output Signal

#### **Layout Considerations**

Circuit board layout and design can significantly affect the MAX3971's performance. Use good high-frequency techniques, including fixed-impedance transmission lines for the high-frequency data signal. Use a multilayer board with solid ground plane. Minimize the inductance between MAX3971 and the ground plane.

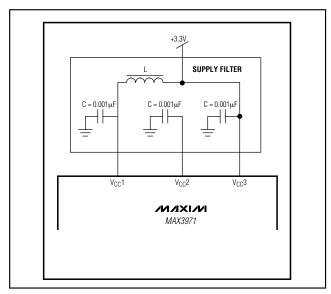

The MAX3971 uses three power supply pins (V<sub>CC</sub>1, V<sub>CC</sub>2, V<sub>CC</sub>3). The input circuitry of the MAX3971 is supplied by V<sub>CC</sub>1. The output drivers have a separate supply (V<sub>CC</sub>3), which usually has large pulsing currents. All other circuitry is powered by V<sub>CC</sub>2. It is possible to simply connect the three pins together. However, better isolation of the input circuitry is ensured by using a supply filter. For optimal isolation, Figure 4 shows a possible supply filtering circuit. Element L, a ferrite bead, provides isolation between a noisy V<sub>CC</sub>3 and sensitive V<sub>CC</sub>1.

Figure 4. Power-Supply Filter

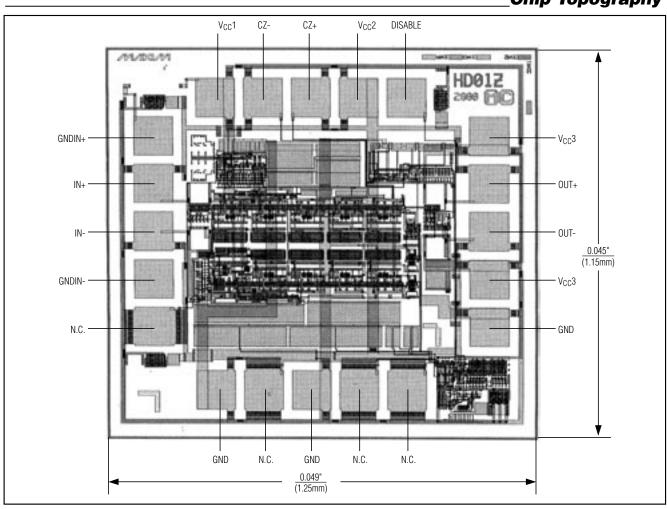

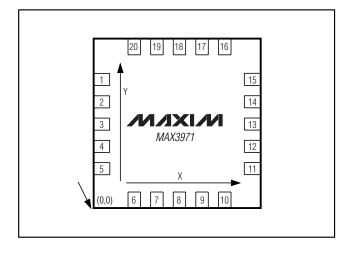

### Pin Configuration

### Chip Information

TRANSISTOR COUNT: 1803

PROCCESS: SiGe Bipolar

SUBSTRATE: Electrically Isolated

# Chip Topography

## Chip Topography (continued)

| MAX3971    |                          |                          |  |  |  |  |  |

|------------|--------------------------|--------------------------|--|--|--|--|--|

| PIN NUMBER | X DIMENSION<br>(MICRONS) | Y DIMENSION<br>(MICRONS) |  |  |  |  |  |

| 1          | 0                        | 672                      |  |  |  |  |  |

| 2          | 0                        | 546                      |  |  |  |  |  |

| 3          | 0                        | 420                      |  |  |  |  |  |

| 4          | 0                        | 294                      |  |  |  |  |  |

| 5          | 0                        | 168                      |  |  |  |  |  |

| 6          | 163.8                    | 0                        |  |  |  |  |  |

| 7          | 289.8                    | 0                        |  |  |  |  |  |

| 8          | 415.8                    | 0                        |  |  |  |  |  |

| 9          | 541.8                    | 0                        |  |  |  |  |  |

| 10         | 667.8                    | 0                        |  |  |  |  |  |

| 11         | 884.8                    | 168                      |  |  |  |  |  |

| 12         | 884.8                    | 294                      |  |  |  |  |  |

| 13         | 884.8                    | 420                      |  |  |  |  |  |

| 14         | 884.8                    | 546                      |  |  |  |  |  |

| 15         | 884.8                    | 672                      |  |  |  |  |  |

| 16         | 667.8                    | 772.8                    |  |  |  |  |  |

| 17         | 541.8                    | 772.8                    |  |  |  |  |  |

| 18         | 415.8                    | 772.8                    |  |  |  |  |  |

| 19         | 289.8                    | 772.8                    |  |  |  |  |  |

| 20         | 163.8                    | 772.8                    |  |  |  |  |  |

- All dimensions are in microns.

- Pad dimensions:

PASSIVATION OPENING: 94.4 microns × 94.4 microns

METAL: 102.4 microns × 102.4 microns

All measurements specify the lower left corner of the pad

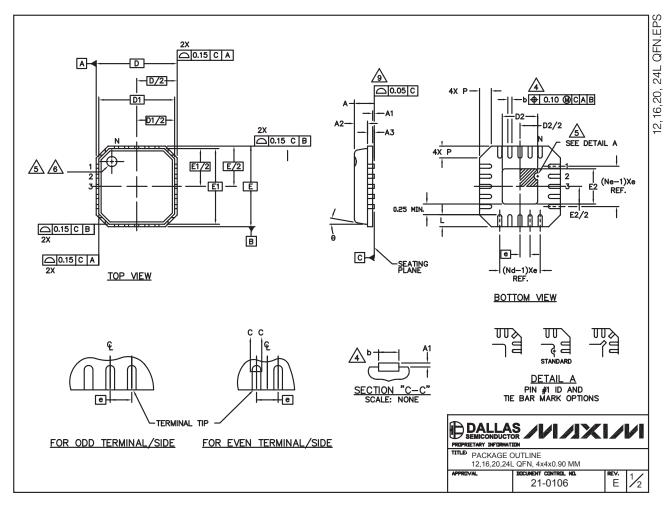

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

#### **NOTES:**

- 1. DIE THICKNESS ALLOWABLE IS 0.305mm MAXIMUM (.012 INCHES MAXIMUM).

- 2. DIMENSIONING & TOLERANCES CONFORM MUST TO ASME Y14.5M. 1994.

- 3. N IS THE NUMBER OF TERMINALS.

Nd IS THE NUMBER OF TERMINALS IN X-DIRECTION &

Ne IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

- A DIMENSION & APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

- THE PIN #1 IDENTIFIER MUST BE EXISTED ON THE TOP SURFACE OF THE PACKAGE BY USING INDENTATION MARK OR INK/LASER MARKED. DETAILS OF PIN #1 IDENTIFIER IS OPTIONAL, BUT MUST BE LOCATED WITHIN ZONE INDICATED.

- 6 EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

- 7. ALL DIMENSIONS ARE IN MILLIMETERS.

- 8. PACKAGE WARPAGE MAX 0.05mm.

- APPLIED FOR EXPOSED PAD AND TERMINALS.

EXCLUDE EMBEDDING PART OF EXPOSED PAD FROM MEASURING.

- 10. MEETS JEDEC MO220; EXCEPT DIMENSION "b".

- 11. THIS PACKAGE OUTLINE APPLIES TO PUNCHED QFN (STEPPED SIDES).

| ş       | COMMON     |                |      |                |  |  |  |  |  |

|---------|------------|----------------|------|----------------|--|--|--|--|--|

| S M BO. | DIMENSIONS |                |      |                |  |  |  |  |  |

| િ ૧     | MIN.       | NOM.           | MAX. | T <sub>E</sub> |  |  |  |  |  |

| Α       | 0.80       | 0.90           | 1.00 |                |  |  |  |  |  |

| A1      | 0.00       | 0.01           | 0.05 |                |  |  |  |  |  |

| A2      | 0.00       | 0.00 0.65 0.80 |      |                |  |  |  |  |  |

| A3      | 0.20 REF.  |                |      |                |  |  |  |  |  |

| D<br>D1 |            | 4.00 BSC       |      |                |  |  |  |  |  |

| D1      |            | 3.75 BSC       |      |                |  |  |  |  |  |

| E       |            | 4.00 BSC       |      |                |  |  |  |  |  |

| E1      | 3.75 BSC   |                |      |                |  |  |  |  |  |

| Φ       | 0,         | _              | 12°  |                |  |  |  |  |  |

| Р       | 0.24       | 0.42           | 0.60 |                |  |  |  |  |  |

| Y  | PITCH | ******** |      | H <sub>0</sub> _ | Ž,         | PITCH |          |      | No_            | Y H       | PITCH |          |      | No_ | V III     | PITCH | VARIA1   | TON D | No_ |

|----|-------|----------|------|------------------|------------|-------|----------|------|----------------|-----------|-------|----------|------|-----|-----------|-------|----------|-------|-----|

| ા  | MIN.  | NOM.     | MAX. | T <sub>E</sub>   | <u>  입</u> | MIN.  | I NOM.   | MAX. | T <sub>E</sub> | <u></u> ใ | MIN.  | I NOM. I | MAX. | TΕ  | <u> 입</u> | MIN.  | NOM.     | MAX.  | Ťε  |

| e  |       | 0.80 BSC |      |                  | e          |       | 0.65 BSC |      |                | e         |       | 0.50 BSC |      |     | e         |       | 0.50 BSC |       |     |

| N  |       | 12       |      | 3                | N          |       | 16       |      | 3              | N         |       | 20       |      | 3   | N         |       | 24       |       | 3   |

| Nd |       | 3        |      | 3                | Nd         |       | 4        |      | 3              | Nd        |       | 5        |      | 3   | Nd        |       | 6        |       | 3   |

| Ne |       | 3        |      | 3                | Ne         |       | 4        |      | 3              | Ne        |       | 5        |      | 3   | Ne        |       | 6        |       | 3   |

| L  | 0.50  | 0.60     | 0.75 |                  | L          | 0.50  | 0.60     | 0.75 |                | L         | 0.50  | 0.60     | 0.75 |     | L         | 0.30  | 0.40     | 0.50  |     |

| Ь  | 0.28  | 0.33     | 0.40 | 4                | Ь          | 0.23  | 0.28     | 0.35 | 4              | Ь         | 0.18  | 0.23     | 0.30 | 4   | Ы         | 0.18  | 0.23     | 0.30  | 4   |

|         | EXPOSED PAD VARIATION |        |      |      |        |      |  |  |  |  |

|---------|-----------------------|--------|------|------|--------|------|--|--|--|--|

| PKG.    |                       | D2     |      |      | E2     |      |  |  |  |  |

| CODE    | MIN.                  | I NOM. | MAX. | MIN. | I NOM. | MAX. |  |  |  |  |

| G1244-2 | 1.95                  | 2.10   | 2.25 | 1.95 | 2.10   | 2.25 |  |  |  |  |

| G1644-1 | 1.95                  | 2.10   | 2.25 | 1.95 | 2.10   | 2.25 |  |  |  |  |

| G2044-3 | 1.95                  | 2.10   | 2.25 | 1.95 | 2.10   | 2.25 |  |  |  |  |

| G2044-4 | 1.55                  | 1.70   | 1.85 | 1.55 | 1.70   | 1.85 |  |  |  |  |

| G2444-1 | 1.95                  | 2.10   | 2.25 | 1.95 | 2.10   | 2.25 |  |  |  |  |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.