### **General Description**

The MAX5650/MAX5651/MAX5652 parallel-input, voltage-output, 16-bit, digital-to-analog converters (DACs) provide monotonic 16-bit output voltage over the full extended operating temperature range. The MAX5650/ MAX5651 include an internal precision low drift (10ppm/°C) bandgap voltage reference, while the MAX5652 requires an external reference. The MAX5650 operates from a +5V single supply and has a +4.096V internal reference. The MAX5651 operates from either a +3V or +5V single supply and has a +2.048V internal reference. The MAX5652 operates from either a +3V or +5V single supply and accepts an input reference voltage between +2V and AVDD. TheMAX5650/MAX5651/ MAX5652 parallel inputs are double buffered and configurable as a single 16-bit wide input or a 2-byte input. The MAX5650/MAX5651/MAX5652 unbuffered DAC voltage output ranges from 0 to VREF.

The MAX5650/MAX5651/MAX5652 feature an active-low hardware clear input (CLR) that clears the registers and the output to zero-scale (0000 hex) or midscale (8000 hex), depending on the state of the MID/ZERO input. These devices include matched scaling resistors for use with a precision external op amp (such as the MAX400) to generate a bipolar output-voltage swing.

The MAX5650/MAX5651/MAX5652 are available in a 32pin, 5mm x 5mm TQFN package and are guaranteed over the extended temperature range (-40°C to +85°C).

For 14-bit, pin-compatible versions of the MAX5650/ MAX5651/MAX5652, refer to the MAX5653/MAX5654/ MAX5655 datasheet.

For 12-bit, pin-compatible versions of the MAX5650/ MAX5651/MAX5652, refer to the MAX5656/MAX5657/ MAX5658 datasheet.

#### **Applications**

Servo Loops Automatic Test Equipment

Waveform Generators

Digital Calibration

Motor Control

**Actuator Control**

**Process Control**

### Selector Guide

| PART       | SUPPLY<br>VOLTAGE (V) | REFERENCE<br>(V) | INL<br>(LSB, max) |

|------------|-----------------------|------------------|-------------------|

| MAX5650ETJ | +4.75 to +5.25        | Internal, +4.096 | ±4                |

| MAX5651ETJ | +2.7 to +5.25         | Internal, +2.048 | _                 |

| MAX5652ETJ | +2.7 to +5.25         | External         | _                 |

Pin Configuration appears at end of data sheet.

#### **Features**

- ♦ 16-Bit Resolution

- ♦ Parallel 16-Bit or 2-Byte Double Buffered Interface

- **♦** Guaranteed Monotonic

- ♦ Maximum INL: ±4 LSB

- ♦ Fast 2µs Settling Time

- ♦ Clear Input (CLR) Sets Output to Zero-Scale or Midscale

- ♦ Integrated Precision Resistors for Bipolar Operation

- ♦ Integrated Precision Bandgap Reference:

- +4.096V (MAX5650)

- +2.048V (MAX5651)

### **Ordering Information**

| PART         | PIN-PACKAGE             | PACKAGE<br>CODE |

|--------------|-------------------------|-----------------|

| MAX5650ETJ   | 32 TQFN-EP* (5mm x 5mm) | T3255-4         |

| MAX5651ETJ** | 32 TQFN-EP* (5mm x 5mm) | T3255-4         |

| MAX5652ETJ** | 32 TQFN-EP* (5mm x 5mm) | T3255-4         |

Note: All devices specified over the -40°C to +85°C temperature range.

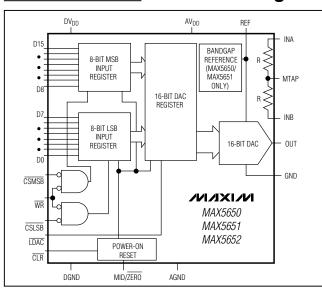

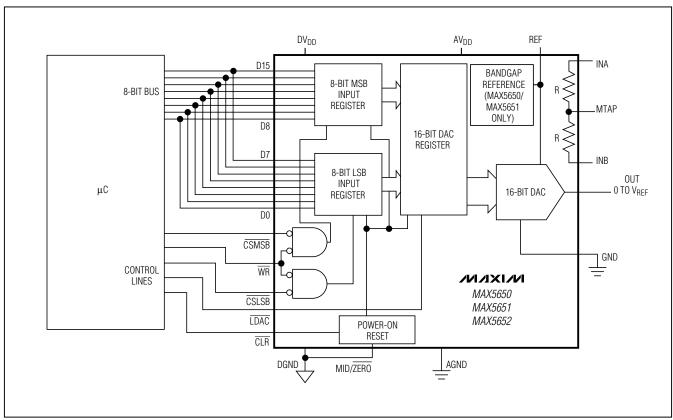

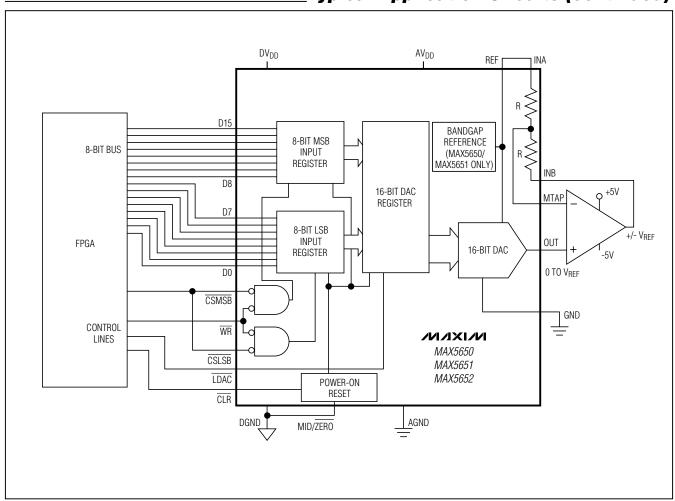

### Functional Diagram

MIXIM

Maxim Integrated Products 1

<sup>\*</sup>EP = Exposed paddle. Connect to AGND or leave unconnected. \*\*Future product—contact factory for availability.

#### **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>DD</sub> to DV <sub>DD</sub> ±6V AV <sub>DD</sub> to AGND, GND0.3V to +6V DV <sub>DD</sub> to DGND0.3V to +6V DGND to GND0.3V to +0.3V | INB to AGND6V to +6V INB to MTAP6V to +6V Maximum Current into Any Pin $\pm$ 50mA Continuous Power Dissipation (T <sub>A</sub> = $\pm$ 70°C) |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| DGND, GND to AGND                                                                                                                              | 32-Pin TQFN (derate 20.8mW/°C above +70°C)2758.6mW                                                                                           |

| D0-D15, CSLSB, CSMSB, WR, LDAC, CLR, MID/ZERO,                                                                                                 | Operating Temperature Range40°C to +85°C                                                                                                     |

| to DGND0.3V to (DV <sub>DD</sub> + 0.3V)                                                                                                       | Storage Temperature Range65°C to +150°C                                                                                                      |

| REF to AGND0.3V to (AV <sub>DD</sub> + 0.3V)                                                                                                   | Lead Temperature (soldering, 10s)+300°C                                                                                                      |

| OUT, MTAP, INA to AGND, GND0.3V to AVDD                                                                                                        |                                                                                                                                              |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS—MAX5650**

(AV<sub>DD</sub> = DV<sub>DD</sub> = +4.75V to +5.25V, AGND = DGND = GND = 0V, V<sub>REF</sub> = internal, R<sub>L</sub> = ∞, C<sub>L</sub> = 10pF, C<sub>REF</sub> = 1µF,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25$ °C.) (Note 1)

| PARAMETER                                      | SYMBOL                                 | CONDITIONS                                                      | MIN   | TYP   | MAX   | UNITS           |

|------------------------------------------------|----------------------------------------|-----------------------------------------------------------------|-------|-------|-------|-----------------|

| STATIC PERFORMANCE—ANAL                        | OG SECTIO                              | DN                                                              | •     |       |       |                 |

| Resolution                                     | N                                      |                                                                 | 16    |       |       | Bits            |

| Differential Nonlinearity                      | DNL                                    | Guaranteed monotonic                                            |       | ±0.5  | ±1    | LSB             |

| Integral Nonlinearity                          | INL                                    |                                                                 |       |       | ±4    | LSB             |

| Zero-Code Offset Error                         | ZSE                                    |                                                                 |       |       | ±80   | μV              |

| Zero-Code Temperature<br>Coefficient           | ZSTC                                   | (Note 2)                                                        |       | ±0.05 |       | ppmFS/<br>°C    |

| Gain Error                                     |                                        | (Note 3)                                                        |       |       | ±10   | LSB             |

| Gain-Error Temperature<br>Coefficient          |                                        | (Note 2)                                                        |       | ±0.1  |       | ppm/°C          |

| DAC Output Resistance                          | Rout                                   | (Note 4)                                                        |       | 6.2   |       | kΩ              |

| Bipolar Resistor Ratio                         |                                        | R <sub>INB</sub> / R <sub>INA</sub>                             |       | 1     |       | $\Omega/\Omega$ |

| Bipolar Resistor Ratio Error                   |                                        |                                                                 |       |       | ±0.05 | %               |

| Bipolar Resistor Ratio Temperature Coefficient |                                        | (Note 2)                                                        |       | ±0.5  |       | ppm/°C          |

| Bipolar Resistor Value                         |                                        | R <sub>INB</sub> and R <sub>INA</sub> (Note 4)                  |       | 12.4  |       | kΩ              |

| VOLTAGE REFERENCE (R <sub>REF</sub> =          | 10k $\Omega$ , C <sub>REF</sub>        | (MIN) = 1μF)                                                    |       |       |       |                 |

| Voltage Reference                              | V <sub>REF</sub>                       | T <sub>A</sub> = +25°C                                          | 4.081 | 4.106 | 4.111 | V               |

| Reference Voltage Temperature Coefficient      | TCV <sub>REF</sub>                     | (Note 2)                                                        |       | 10    |       | ppm/°C          |

| Reference Load Regulation                      | V <sub>OUT</sub> /<br>I <sub>OUT</sub> | $0 \le I_{OUT} \le V_{REF} / 10k\Omega$                         |       | 0.1   | 0.6   | μV/μΑ           |

| Short-Circuit Current                          |                                        |                                                                 |       | 6     |       | mA              |

| Reference Load                                 | I <sub>REF</sub>                       |                                                                 |       |       | 400   | μΑ              |

| Reference Power-Up Time                        |                                        | Settle to 0.5 LSB                                               |       | 4     |       | ms              |

| Power-Supply Rejection Ratio                   | PSRR                                   | $AV_{DD} = DV_{DD} = 4.75V \text{ to } 5.25V \text{ (FS code)}$ |       |       | 0.5   | mV/V            |

MIXIM

### **ELECTRICAL CHARACTERISTICS—MAX5650 (continued)**

$(AV_{DD} = DV_{DD} = +4.75V \text{ to } +5.25V, \text{ AGND} = \text{DGND} = \text{GND} = 0V, \text{ V}_{REF} = \text{internal}, \text{ R}_{L} = \infty, \text{ C}_{L} = 10 \text{pF}, \text{ C}_{REF} = 1 \mu\text{F}, \text{ T}_{A} = \text{T}_{MIN} \text{ to T}_{MAX}, \text{ unless otherwise noted. Typical values are at T}_{A} = +25^{\circ}\text{C}.) \text{ (Note 1)}$

| PARAMETER                          | SYMBOL              | CONDITIONS                                                                                       | MIN                    | TYP | MAX                       | UNITS             |

|------------------------------------|---------------------|--------------------------------------------------------------------------------------------------|------------------------|-----|---------------------------|-------------------|

| DYNAMIC PERFORMANCE—ANA            | ALOG SECT           | TON                                                                                              |                        |     |                           | •                 |

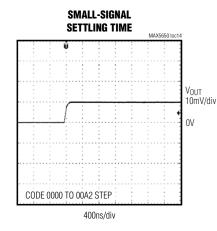

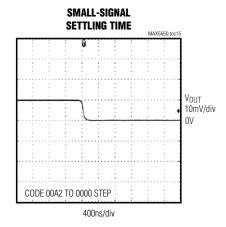

| Output Settling Time               |                     | 7F60H to 80A0H or 80A0H to 7F60H to 0.5 LSB                                                      |                        | 2   |                           | μs                |

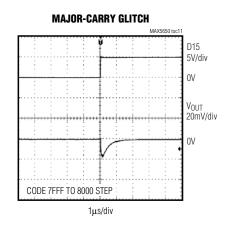

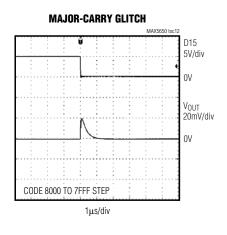

| DAC Glitch Impulse                 |                     | Major carry transition                                                                           |                        | 10  |                           | nV·s              |

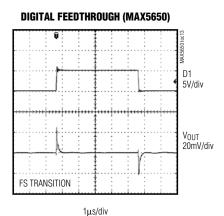

| Digital Feedthrough                |                     | Code = 0000 hex; CSLSB = CSMSB = DV <sub>DD</sub> , D0–D15 transition from 0 to DV <sub>DD</sub> |                        | 3   |                           | nV·s              |

| DYNAMIC PERFORMANCE—VOI            | LTAGE REF           | ERENCE SECTION                                                                                   |                        |     |                           |                   |

| Noise Voltage (Note 6)             |                     | Frequency = 0.1Hz to 10Hz                                                                        |                        | 15  |                           | μV <sub>P-P</sub> |

| Noise Voltage (Note 6)             |                     | Frequency = 10Hz to 1kHz                                                                         |                        | 12  |                           | μV <sub>RMS</sub> |

| V <sub>REF</sub> Glitch Impulse    |                     | For zero-scale to full-scale or full-scale to zero-scale transition                              |                        | 10  |                           | nV·s              |

| STATIC PERFORMANCE—DIGIT           | AL INPUTS           |                                                                                                  |                        |     |                           |                   |

| Input High Voltage                 | VIH                 | (Note 8)                                                                                         | 2.4                    |     |                           | V                 |

| Input Low Voltage                  | VIL                 | (Note 8)                                                                                         |                        |     | 0.8                       | V                 |

| Input Current                      | I <sub>IN</sub>     |                                                                                                  |                        |     | ±1                        | μΑ                |

| Input Capacitance                  | C <sub>IN</sub>     |                                                                                                  |                        | 5   |                           | рF                |

| POWER SUPPLY                       |                     |                                                                                                  |                        |     |                           |                   |

| Analog Supply Range                | AV <sub>DD</sub>    |                                                                                                  | 4.75                   |     | 5.25                      | V                 |

| Digital Supply Range               | DV <sub>DD</sub>    | (Note 9)                                                                                         | AV <sub>DD</sub> - 0.3 |     | AV <sub>DD</sub><br>+ 0.3 | V                 |

| Positive Supply Current            | I <sub>AVDD</sub> + | All digital inputs at DV <sub>DD</sub> or 0V, AV <sub>DD</sub> = DV <sub>DD</sub>                |                        |     | 2                         | mA                |

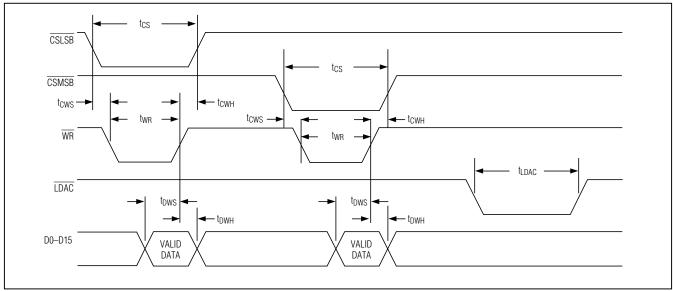

| TIMING CHARACTERISTICS (Fig        | ure 4)              |                                                                                                  |                        |     |                           |                   |

| CSMSB and CSLSB Pulse Width        | tcs                 |                                                                                                  | 40                     |     |                           | ns                |

| WR Pulse Width                     | twR                 |                                                                                                  | 40                     |     |                           | ns                |

| CSMSB or CSLSB to WR<br>Setup Time | tcws                |                                                                                                  | 0                      |     |                           | ns                |

| CSMSB or CSLSB to WR<br>Hold Time  | tcwH                |                                                                                                  | 0                      |     |                           | ns                |

| Data Valid to WR Setup Time        | tows                |                                                                                                  | 40                     |     |                           | ns                |

| Data Valid to WR Hold Time         | tDWH                |                                                                                                  | 0                      |     |                           | ns                |

| LDAC Pulse Width                   | tLDAC               |                                                                                                  | 40                     |     |                           | ns                |

| CLR Pulse Width                    | tCLR                |                                                                                                  | 40                     |     |                           | ns                |

- **Note 1:** 100% production tested at  $T_A = +25$ °C and  $T_A = +85$ °C. Guaranteed by design at  $T_A = -40$ °C.

- Note 2: Temperature coefficient is determined by the box method in which the maximum change over the temperature range is divided by  $\Delta T$ .

- Note 3: Gain error is measured at the full-scale code and is calculated with respect to the reference voltage (REF).

- Note 4: Resistor tolerance is typically ±20%.

- Note 5: Guaranteed by design, not production tested.

- Note 6: Noise is measured at the reference output.

- Note 7: Min/max range guaranteed by gain-error test. Operation outside min/max limits results in degraded performance.

- Note 8: The devices draw higher supply current when the digital inputs are driven between (DV<sub>DD</sub> 0.5V) and (DGND + 0.5V). See Digital Supply Current vs. Digital Input Voltage in the *Typical Operating Characteristics*.

- **Note 9:** For optimal performance  $AV_{DD} = DV_{DD}$ .

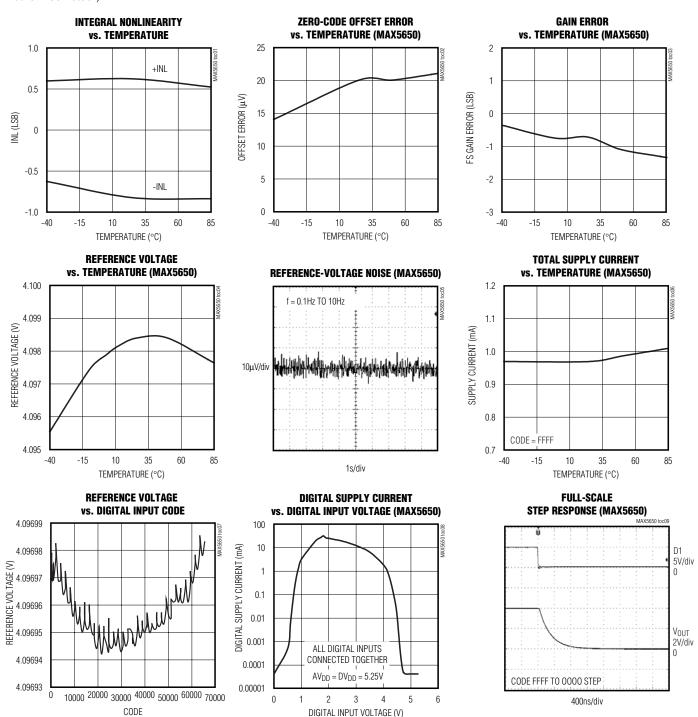

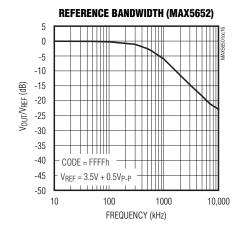

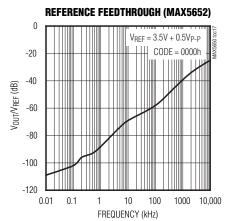

### **Typical Operating Characteristics**

$(AV_{DD} = DV_{DD} = +5V, AGND = DGND = GND = 0V, R_L = \infty, C_L = 10pF, C_{REF} = 1\mu F$  for the MAX5650/MAX5651,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

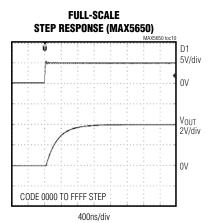

### Typical Operating Characteristics (continued)

$(AV_{DD} = DV_{DD} = +5V, AGND = DGND = GND = 0V, R_L = \infty, C_L = 10pF, C_{REF} = 1\mu F$  for the MAX5650/MAX5651,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

### **Pin Description**

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                                                                                     |

|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | D0               | Data Input Bit 0 (LSB)                                                                                                                                                                                                                                                                       |

| 2   | D1               | Data Input Bit 1                                                                                                                                                                                                                                                                             |

| 3   | D2               | Data Input Bit 2                                                                                                                                                                                                                                                                             |

| 4   | D3               | Data Input Bit 3                                                                                                                                                                                                                                                                             |

| 5   | D4               | Data Input Bit 4                                                                                                                                                                                                                                                                             |

| 6   | D5               | Data Input Bit 5                                                                                                                                                                                                                                                                             |

| 7   | D6               | Data Input Bit 6                                                                                                                                                                                                                                                                             |

| 8   | D7               | Data Input Bit 7                                                                                                                                                                                                                                                                             |

| 9   | D8               | Data Input Bit 8                                                                                                                                                                                                                                                                             |

| 10  | D9               | Data Input Bit 9                                                                                                                                                                                                                                                                             |

| 11  | D10              | Data Input Bit 10                                                                                                                                                                                                                                                                            |

| 12  | D11              | Data Input Bit 11                                                                                                                                                                                                                                                                            |

| 13  | D12              | Data Input Bit 12                                                                                                                                                                                                                                                                            |

| 14  | D13              | Data Input Bit 13                                                                                                                                                                                                                                                                            |

| 15  | D14              | Data Input Bit 14                                                                                                                                                                                                                                                                            |

| 16  | D15              | Data Input Bit 15 (MSB)                                                                                                                                                                                                                                                                      |

| 17  | DGND             | Digital Ground                                                                                                                                                                                                                                                                               |

| 18  | DV <sub>DD</sub> | Digital Supply. Bypass DV <sub>DD</sub> to DGND with a 0.1µF capacitor as close to the device as possible.                                                                                                                                                                                   |

| 19  | CSLSB            | Lower 8-Bit Active-Low Chip Select. When $\overline{\text{CSLSB}}$ is driven low the data inputs D0–D7 are loaded to the input and DAC registers depending on the state of $\overline{\text{WR}}$ and $\overline{\text{LDAC}}$ (see Table 1).                                                |

| 20  | CSMSB            | Upper 8-Bit Active-Low Chip Select. When $\overline{\text{CSMSB}}$ is driven low the data inputs D8–D15 are loaded to the input and DAC registers depending on the state of $\overline{\text{WR}}$ and $\overline{\text{LDAC}}$ (see Table 1).                                               |

| 21  | WR               | Active-Low Write Input. While chip select (CSLSB and/or CSMSB) is low, the data on D0–D7 and/or D8–D15 is presented to the input register when WR is low. A rising edge on WR then latches the data to the input register (see Table 1). Hold WR low to make the input register transparent. |

| 22  | LDAC             | Asynchronous Active-Low Load DAC Input. When LDAC is low, the data in the input register is presented to the DAC register. A rising edge on LDAC then latches the data to the DAC register (see Table 1). Hold WR and LDAC low to perform a write-through operation.                         |

| 23  | CLR              | Asynchronous Active-Low Clear DAC Input. Pull CLR low to clear the input and DAC registers and set the DAC output to midscale (8000 hex), if MID/ZERO is high, or zero scale (0000 hex), if MID/ZERO is low.                                                                                 |

| 24  | MID/ZERO         | Midscale/Zero-Scale Clear Output Value Select. Pull MID/ZERO low for zero-scale clear output (0000 hex) or high for midscale clear output (8000 hex).                                                                                                                                        |

| 25  | MTAP             | Internal Scaling Resistor Midpoint Tap. Connect to the inverting input of an external op amp.                                                                                                                                                                                                |

| 26  | INB              | Internal Resistor Input B. Free end of internal resistor (R <sub>INB</sub> ). Connect to the output of an external output buffer for bipolar operation.                                                                                                                                      |

| 27  | AV <sub>DD</sub> | Analog Supply. Bypass AVDD to AGND with a 0.1µF capacitor as close to the device as possible.                                                                                                                                                                                                |

| 28  | AGND             | Analog Ground                                                                                                                                                                                                                                                                                |

| 29  | INA              | Internal Resistor Input A. Free end of internal resistor (RINA). Connect to REF for bipolar operation.                                                                                                                                                                                       |

\_\_ /N/XI/M

### Pin Description (continued)

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                       |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30  | REF  | Internal Reference Voltage Output (MAX5650/MAX5651). Connect a $1\mu F < C_{REF} < 47\mu F$ between REF and AGND as close to the device as possible. The internal reference voltage of the MAX5650 is $+4.096V$ and $+2.048V$ for the MAX5651. |

|     |      | External Reference Voltage Input (MAX5652). Connect to an external voltage reference source between +2V and AV <sub>DD</sub> .                                                                                                                 |

| 31  | OUT  | DAC Output                                                                                                                                                                                                                                     |

| 32  | GND  | DAC Ground                                                                                                                                                                                                                                     |

| _   | EP   | Exposed paddle. Connect to AGND or leave unconnected.                                                                                                                                                                                          |

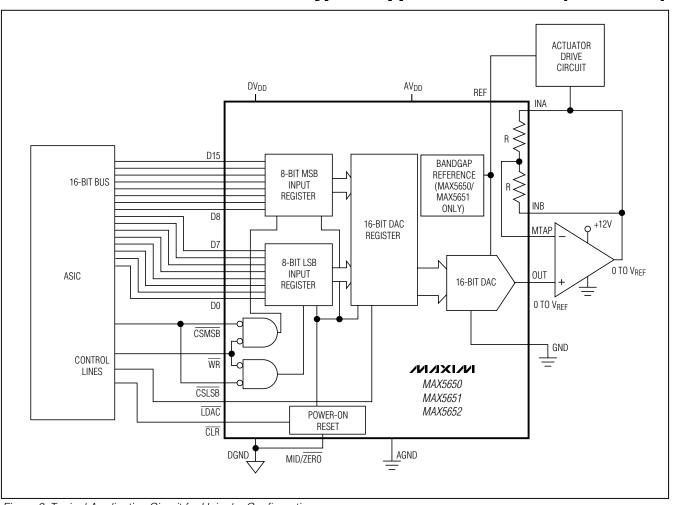

### **Typical Application Circuits**

Figure 1. Typical Application Circuit for  $\mu C$  Byte-Wide Interface

### **Typical Application Circuits (continued)**

Figure 2. Typical Application Circuit for Unipolar Configuration

### **Typical Application Circuits (continued)**

Figure 3. Typical Application Circuit for Bipolar Configuration

Figure 4. Timing Diagram

### **Detailed Description**

The MAX5650/MAX5651/MAX5652 parallel-input, voltage-output DACs offer full 16-bit performance with less than ±4 LSB integral nonlinearity and less than ±1 LSB differential nonlinearity, ensuring monotonic performance over the full operating temperature range. The DAC is composed of an inverted R2R ladder with the unbuffered output available directly at OUT, allowing 16-bit performance from the reference voltage to the DAC ground (GND). The parallel inputs are doublebuffered and configurable as a single 16-bit wide input or a 2-byte input. The MAX5650/MAX5651 include internal precision low-drift (10ppm/°C) bandgap voltage references of +4.096V and +2.048V, respectively. The MAX5652 accepts an external reference voltage between +2V and AV<sub>DD</sub>. The MAX5650 operates with a supply voltage range of +4.75V to +5.25V, while the MAX5651/MAX5652 operate with a supply voltage range of +2.7V to +5.25V.

#### Voltage Reference

The MAX5650/MAX5651 provide a 10ppm/°C (typ) internal precision bandgap voltage reference with a load regulation specification of less than  $0.6\mu V/\mu A$  (maximum) over the entire operating temperature range. The reference voltage for the MAX5650 is +4.096V, while the reference voltage for the MAX5651 is +2.048V. Connect a capacitor ranging between  $1\mu F$  and  $47\mu F$  from REF to ground as close to the device as possible. Use a low-ESR ceramic capacitor such as the GRM series from Murata.

The MAX5652 accepts an external reference with a voltage range extending from +2V to  $AV_{DD}$ . The output voltage of the DAC is determined as follows:

$$V_{OUT} = V_{REF} \times N / 65536$$

where N is the numeric value of the DAC's binary input code (0 to 65535) and  $V_{\rm RFF}$  is the reference voltage.

At a full-scale transition, the instantaneous charge demand from the external reference is about 550pC. For a reference with a 1µF load capacitor, the charge demand causes an instantaneous reference voltage drop of 550µV. A 10µF load capacitor causes a voltage drop of 55µV. This glitch recovers in a time inversely proportional to the bandwidth of the voltage reference, which should be sufficiently fast to recover before the next DAC transition to avoid accumulation of the glitch energy and a shift in the average reference voltage. For a +4.096V reference with 1µF bypass capacitor, it takes three time constants to recover to 0.5 LSB accuracy. Therefore, a 96kHz bandwidth reference recovers in 5µs while a 960kHz bandwidth reference recovers in 0.5µs.

For further voltage-reference selection assistance, visit www.maxim-ic.com/appnotes.cfm/appnote\_number/754.

10 \_\_\_\_\_\_\_/N/1XI/M

#### **Digital Interface**

The MAX5650/MAX5651/MAX5652 accept a single 16-bit wide input or an 8 plus 8-bit wide input. Data latches or transfers directly to the DAC depending on the state of the control inputs CLR, CSLSB, CSMSB, LDAC, MID/ZERO, and WR. All digital inputs are compatible with both TTL and CMOS logic.

The double buffered input consists of an input register and a DAC register (see the *Functional Diagram*). Data is loaded into the input register using CSLSB, CSMSB, and WR. The input register is transparent when WR and CSLSB and/or CSMSB are low. The rising edge of WR,

while  $\overline{\text{CSLSB}}$  is low, latches the lower byte (D0–D7) into the input register. The rising edge of WR, while  $\overline{\text{CSMSB}}$  is low, latches the upper byte (D8–D15) into the input register. The sequence of loading the MSB and LSB does not matter. See Figure 1 for byte-wide interface circuit.

The DAC register is transparent when \$\overline{LDAC}\$ is low. The rising edge of \$\overline{LDAC}\$ latches data into the DAC register. The DAC's analog output reflects the data held in the DAC register. Both the input register and DAC register are transparent when \$\overline{CSLSB}\$, \$\overline{CSMSB}\$, \$\overline{WR}\$, and \$\overline{LDAC}\$ are driven low. In this case, any change at D0–D15 appears at the output instantly. See Table 1 for the truth table.

**Table 1. Truth Table**

| CLR | CSLSB | CSMSB | WR | LDAC | FUNCTION                                                                                                                                                                                 |

|-----|-------|-------|----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 0     | 1     | 0  | 1    | Loads least significant byte into the input register. DAC output remains unchanged.                                                                                                      |

| 1   | 0     | 1     | 5  | 1    | Latches least significant byte into the input register. DAC output remains unchanged.                                                                                                    |

| 1   | 1     | 0     | 0  | 1    | Loads most significant byte into the input register. DAC output remains unchanged.                                                                                                       |

| 1   | 1     | 0     | _  | 1    | Latches most significant byte into the input register. DAC output remains unchanged.                                                                                                     |

| 1   | X     | X     | 1  | 0    | Transfers data from the input register into the DAC register and updates the DAC output.                                                                                                 |

| 1   | X     | X     | 1  | \    | Latches data from the input register into the DAC register. DAC output remains unchanged.                                                                                                |

| 1   | 1     | 0     | 0  | 0    | Most significant input and DAC registers are transparent. DAC output updates immediately with the most significant input data and least significant input register data.                 |

| 1   | Χ     | Χ     | 1  | 1    | No operation.                                                                                                                                                                            |

| 1   | 0     | 0     | 0  | 0    | Both most significant and least significant input registers and DAC register are transparent. DAC output updates immediately with the most significant and least significant input data. |

| 1   | 0     | 0     | 0  | 1    | Loads all 16 bits into the input register. DAC output remains unchanged.                                                                                                                 |

| 1   | 0     | 1     | 0  | 0    | Least significant input and DAC registers are transparent. DAC output updates immediately with the least significant input data and most significant register data.                      |

| 1   | 1     | 1     | X  | 0    | Transfers data held in the input register to the DAC register and updates the DAC output.                                                                                                |

| 1   | 1     | 1     | Χ  | 1    | No operation.                                                                                                                                                                            |

| 0   | X     | Х     | X  | X    | Sets the input and DAC registers and DAC output to midscale (if MID/ZERO = 1) or zero-scale (if MID/ZERO = 0).                                                                           |

0 = Low state.

1 = High state.

X = Don't care.

$\mathcal{I} = Rising\ edge.$

The MAX5650/MAX5651/MAX5652 provide an asynchronous clear input (CLR). Asserting CLR resets the input and DAC registers and DAC output to midscale if the MID/ZERO input is high and to zero scale when MID/ZERO is low.

#### Power-On Reset (POR)

The MAX5650/MAX5651/MAX5652 provide an internal POR circuit. On power-up, the input and DAC registers and DAC output are set to 0000 hex if MID/ $\overline{ZERO}$  is low or 8000 hex if MID/ $\overline{ZERO}$  is high. Wait 10µs after power-up before pulling  $\overline{CSMSB}$  or  $\overline{CSLSB}$  low.

#### **Internal Scaling Resistors**

The MAX5650/MAX5651/MAX5652 include two internal scaling resistors of 12.4k $\Omega$  (typ) each that are matched to 0.05% or better. Use these resistors with a precision external op amp to generate a bipolar output swing (see the *Bipolar Operation* section). The free ends of these resistors are accessible at INA and INB while the midpoint is accessible at MTAP. Connect INB to the output of the op amp and INA to REF for bipolar operation. Negative voltages are only allowed at INB (see the *Absolute Maximum Ratings* section).

### \_Applications Information

#### **Unipolar Buffered/Unbuffered Operation**

Unbuffered operation reduces power consumption as well as the offset error contributed by the external output buffer (see Figure 1). The R2R DAC output is available directly at OUT, allowing 16-bit performance from +V<sub>REF</sub> to GND without degradation at zero scale.

The typical application circuit (Figure 2) shows the MAX5650/MAX5651/MAX5652 configured for a buffered unipolar voltage-output operation. Use the integrated precision matched resisters for op-amp input impedance matching. Table 2 shows digital codes and corresponding output voltages for unipolar buffered or unbuffered operation.

#### **Bipolar Operation**

For bipolar voltage-output operation, use an external op amp (such as the MAX400) in conjunction with the internal scaling resistors (see Figure 3). Connect the free end of the internal resistor (INB) to the output of the external op amp and the free end of the other resistor (INA) to REF. Connect the midpoint of the resistors to the inverting input of the op amp. Connect the output of the DAC to the noninverting input of the external op amp. The resulting transfer function is as follows:

$V_{OUT} = V_{REF} [(2D/65,536) - 1]$

where D is the decimal value of the DACs binary input code. Table 3 shows digital codes and corresponding output voltages for bipolar operation.

**Table 2. Unipolar Code Table**

| DAC LATCH CONTENTS  | ANALOG OUTPUT, VOUT                                           |

|---------------------|---------------------------------------------------------------|

| MSB LSB             | ANALOG COTFOT, VOU                                            |

| 1111 1111 1111 1111 | V <sub>REF</sub> x (65,535 / 65,536)                          |

| 1000 0000 0000 0000 | V <sub>REF</sub> x (32,768 / 65,536)<br>= 0.5V <sub>REF</sub> |

| 0000 0000 0000 0001 | V <sub>REF</sub> x (1 / 65,536)                               |

| 0000 0000 0000 0000 | OV                                                            |

### **Table 3. Bipolar Code Table**

| DAC LATC  | H CONTENTS | ANALOG OUTPUT, V <sub>OUT</sub>                              |

|-----------|------------|--------------------------------------------------------------|

| MSB       | LSB        | ANALOG GOTFOT, VOUT                                          |

| 1111 1111 | 1111 1111  | +V <sub>REF</sub> x (32,767 / 32,768)                        |

| 1000 0000 | 0000 0001  | +V <sub>REF</sub> x (1 / 32,768)                             |

| 1000 0000 | 0000 0000  | OV                                                           |

| 0111 1111 | 1111 1111  | -V <sub>REF</sub> (1 / 32,768)                               |

| 0000 0000 | 0000 0000  | -V <sub>REF</sub> x (32,768 / 32,768)<br>= -V <sub>REF</sub> |

#### **Power-Supply and Layout Considerations**

Careful PC board layout is important for optimal system performance. Wire-wrapped boards, sockets, and breadboards are not recommended. Keep analog and digital signals separate to reduce noise injection and digital feedthrough. Connect AGND and DGND to the highest quality ground available. Star-connect all ground return paths back to AGND or use a multilayer board with a low-inductance ground plane. Connect analog and digital ground planes together at a low-impedance power-supply source. For the MAX5652, keep the trace between the reference source to the reference input short and low impedance. Bypass each supply with a 0.1µF capacitor as close as possible to the IC for optimal 16-bit performance.

Chip Information

PROCESS: BICMOS

NIXIN

### **Pin Configuration**

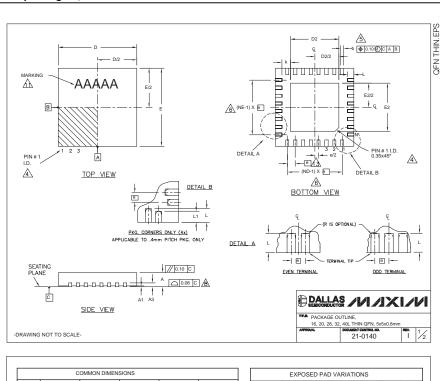

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

|                 |                                |                                             | С                              | OMMO                              | DN D                         | IMEN                            | SION         | S                                |                     |                         |                      |               |                 |           |         |          |          | EXI  | POSE  | D PAD  | VARI   | ATION  | IS      |        |                  |  |      |  |    |  |  |    |  |   |      |

|-----------------|--------------------------------|---------------------------------------------|--------------------------------|-----------------------------------|------------------------------|---------------------------------|--------------|----------------------------------|---------------------|-------------------------|----------------------|---------------|-----------------|-----------|---------|----------|----------|------|-------|--------|--------|--------|---------|--------|------------------|--|------|--|----|--|--|----|--|---|------|

| PKG.            |                                | 16L 5x                                      |                                |                                   | DL 5                         |                                 |              | 8L 5x                            |                     |                         | 12L 5>               |               |                 |           | 40L 5x5 |          |          |      |       |        |        |        |         |        |                  |  | PKG. |  | D2 |  |  | E2 |  | L | DOWN |

| SYMBOL          | MIN.                           | NOM.                                        | MAX.                           | MIN.                              | NOM.                         | MAX.                            | MIN.         | NOM.                             | MAX.                | MIN.                    | NOM.                 | MAX.          | MIN.            | IIN. NOM. | 1. M    | AX.      | CODES    | MIN. | NOM.  | MAX.   | MIN.   | NOM.   | MAX.    | ±0.15  | BONDS<br>ALLOWED |  |      |  |    |  |  |    |  |   |      |

| Α               | 0.70                           | 0.75                                        | 0.80                           | 0.70                              | 0.75                         | 0.80                            | 0.70         | 0.75                             | 0.80                | 0.70                    | 0.75                 | 0.80          | 0.70            | 0.75      | 5 0.    | 80       | T1655-2  | 3.00 | 3.10  | 3.20   | 3.00   | 3.10   | 3.20    | **     | YES              |  |      |  |    |  |  |    |  |   |      |

| A1              | 0                              | 0.02                                        | _                              | _                                 | _                            | 0.05                            | _            | 0.02                             |                     | _                       | 0.02                 |               | _               | 0.02      | -       | 05       | T1655-3  | 3.00 | 3.10  | 3.20   | 3.00   | 3.10   | 3.20    | **     | NO               |  |      |  |    |  |  |    |  |   |      |

| A3              | _                              | .20 RE                                      | _                              |                                   | 20 RE                        | _                               |              | 20 RE                            |                     | _                       | 20 RE                | _             |                 | 20 R      |         | _        | T1655N-1 | 3.00 | 3.10  | 3.20   | 3.00   | 3.10   | 3.20    | **     | NO               |  |      |  |    |  |  |    |  |   |      |

| b               |                                | 0.30                                        |                                |                                   |                              |                                 |              |                                  |                     |                         |                      |               |                 |           |         |          | T2055-3  | 3.00 | 3.10  | 3.20   | 3.00   | 3.10   | 3.20    | **     | YES              |  |      |  |    |  |  |    |  |   |      |

| D<br>E          | 4.90                           | 5.00                                        |                                |                                   | 5.00                         | 5.10                            |              | 5.00                             |                     | 4.90                    | 5.00                 |               |                 |           |         |          | T2055-4  | 3.00 | 3.10  | 3.20   | 3.00   | 3.10   | 3.20    | **     | NO               |  |      |  |    |  |  |    |  |   |      |

| e               | -                              | 5.00<br>0.80 B                              | _                              | _                                 | 5.00<br>65 B:                |                                 | -            | 50 BS                            | -                   | _                       | 50 B                 | _             | -               | 40 F      | _       | _        | T2055-5  | 3.15 | 3.25  | 3.35   | 3.15   | 3.25   | 3.35    | 0.40   | YES              |  |      |  |    |  |  |    |  |   |      |

| k               | 0.25                           |                                             | SC.                            | 0.25                              | 00 B                         | SC                              | 0.25         | .50 B3                           |                     | 0.25                    | .50 83               | -<br>-        | 0.25            |           | -       | _        | T2855-3  | 3.15 | 3.25  | 3.35   | 3.15   | 3.25   | 3.35    | **     | YES              |  |      |  |    |  |  |    |  |   |      |

| I I             | _                              | 0.40                                        | -                              | 0.45                              | 0 55                         | 0.65                            | -            | -                                | 0.65                | _                       | 0.40                 | _             | 0.40            | _         | -       | _        | T2855-4  | 2.60 | 2.70  | 2.80   | 2.60   | 2.70   | 2.80    | **     | YES              |  |      |  |    |  |  |    |  |   |      |

| 11              | 0.30                           | 0.40                                        | 0.50                           | 0.40                              | 0.55                         | 0.00                            | 0.45         | 0.55                             | 0.00                | 0.30                    | 0.40                 | 0.50          | 0.40            |           |         |          | T2855-5  | 2.60 | 2.70  | 2.80   | 2.60   | 2.70   | 2.80    | **     | NO               |  |      |  |    |  |  |    |  |   |      |

| N               | <u> </u>                       | 16                                          | _                              | - 1                               | 20                           | _                               | -            | 28                               | -                   | Ė                       | 32                   | _             | 0.50            | 40        | 0.0.    | -        | T2855-6  | 3.15 | 3.25  | 3.35   | 3.15   | 3.25   | 3.35    | **     | NO               |  |      |  |    |  |  |    |  |   |      |

| ND              |                                | 4                                           |                                | _                                 | 5                            |                                 | _            | 7                                |                     | -                       | 8                    |               | $\vdash$        | 10        |         | _        | T2855-7  | 2.60 | 2.70  | 2.80   | 2.60   | 2.70   | 2.80    | **     | YES              |  |      |  |    |  |  |    |  |   |      |

| NE              |                                | 4                                           |                                |                                   | 5                            |                                 |              | 7                                |                     |                         | 8                    |               | 10              |           |         |          | T2855-8  | 3.15 | 3.25  | 3.35   | 3.15   | 3.25   | 3.35    | 0.40   | YES              |  |      |  |    |  |  |    |  |   |      |

| JEDEC           |                                | WHH                                         | 3                              | ٧                                 | VHH                          | 0                               | ١            | VHHD                             | -1                  | V                       | VHHD                 | -2            |                 |           |         |          | T2855N-1 | 3.15 | 3.25  | 3.35   | 3.15   | 3.25   | 3.35    | **     | NO               |  |      |  |    |  |  |    |  |   |      |

|                 |                                |                                             |                                |                                   |                              |                                 |              |                                  |                     |                         |                      |               |                 |           |         |          | T3255-3  | 3.00 | 3.10  | 3.20   | 3.00   | 3.10   | 3.20    | **     | YES              |  |      |  |    |  |  |    |  |   |      |

| OTES:           |                                |                                             |                                |                                   |                              |                                 |              |                                  |                     |                         |                      |               |                 |           |         |          | T3255-4  | 3.00 | 3.10  |        | 3.00   | 3.10   | 3.20    | **     | NO               |  |      |  |    |  |  |    |  |   |      |

| 1. DIM          | ENS                            | ONING                                       | 8 T                            | DLERA                             | NCIN                         | IG CC                           | NFOF         | OT MS                            | ASM                 | E Y14                   | .5M-1                | 994.          |                 |           |         |          | T3255-5  | 3.00 | 3.10  |        | 3.00   | 3.10   | 3.20    | **     | YES              |  |      |  |    |  |  |    |  |   |      |

| 2. ALL          | DIM                            | ENSIO                                       | NS AF                          | RE IN N                           | /ILLII                       | ИЕТЕ                            | RS. A        | NGLE:                            | SARE                | IN D                    | EGRE                 | ES.           |                 |           |         |          | T3255N-1 | 3.00 | 3.10  |        | 3.00   | 3.10   | 3.20    | **     | NO               |  |      |  |    |  |  |    |  |   |      |

| 3. N IS         | THE                            | TOTA                                        | L NUI                          | MBER                              | OF T                         | ERMII                           | NALS.        |                                  |                     |                         |                      |               |                 |           |         |          | T4055-1  | 3.20 | 3.30  | 3.40   | 3.20   | 3.30   | 3.40    | **     | YES              |  |      |  |    |  |  |    |  |   |      |

| OPT<br>IDE      | NFOR<br>FION/<br>NTIFI<br>ENSI | MINAL<br>RM TO<br>AL, BU<br>ER MA<br>ON b A | JESD<br>T MU:<br>Y BE<br>APPLI | 95-1 S<br>ST BE<br>EITHE<br>ES TO | PP-0<br>LOC/<br>R A I<br>MET | 112. E<br>ATED<br>MOLD<br>ALLIZ | WITH<br>OR N | S OF<br>IN THE<br>IARKE<br>ERMIN | TERM<br>ZON<br>D FE | AINAL<br>NE INE<br>ATUR | #1 ID<br>DICAT<br>E. | ENTI<br>ED. T | FIER /<br>HE TE | RMI       | NAL     | . #1     |          |      |       |        |        | 022 00 | ,,,,,,, | DimENO | ONS TABL         |  |      |  |    |  |  |    |  |   |      |

| 6. ND           |                                |                                             |                                |                                   |                              |                                 |              |                                  | UALC                | ONE                     | лсы г                | A A NI        | ) E SII         | ne p      | E 0 E   | ECTIVI   | :I V     |      |       |        |        |        |         |        |                  |  |      |  |    |  |  |    |  |   |      |

| 7. DEF          |                                |                                             |                                |                                   |                              |                                 |              |                                  |                     |                         |                      |               | - L 011         | )_ I      |         | LUTTIVI  |          |      |       |        |        |        |         |        |                  |  |      |  |    |  |  |    |  |   |      |

| A cor           |                                |                                             |                                |                                   |                              |                                 |              |                                  |                     |                         |                      | WEL           | L AS T          | HE 1      | TER     | MINALS   |          |      |       |        |        |        |         |        |                  |  |      |  |    |  |  |    |  |   |      |

| 9. DR/          |                                | G CON                                       |                                |                                   | JEDI                         | EC M                            | D220,        | EXCE                             | PT E                | (POS                    | ED PA                | D DII         | MENS            | ON I      | FOR     |          |          | -    |       |        |        |        |         |        |                  |  |      |  |    |  |  |    |  |   |      |

| <u>∕10.</u> WAI | RPAC                           | SE SHA                                      | ALL N                          | OTEX                              | CEE                          | 0.10                            | mm.          |                                  |                     |                         |                      |               |                 |           |         |          |          | ı    | ΠAi   | ΔΙΙ    | AS     | 48.    | 411 4   |        | 8 48             |  |      |  |    |  |  |    |  |   |      |

| 11. MAI         | RKIN                           | G IS FO                                     | OR PA                          | CKAG                              | E OF                         | IENT.                           | ATION        | REFE                             | REN                 | CE O                    | NLY.                 |               |                 |           |         |          |          | Į.   | IJ#   | MICOND | UCTOR  | # W    |         |        |                  |  |      |  |    |  |  |    |  |   |      |

| 12. NU!         | ивег                           | OF L                                        | EADS                           | SHOW                              | /N AF                        | RE FO                           | R REI        | FEREN                            | NCE C               | NLY.                    |                      |               |                 |           |         | "e". ±0. |          | - 1  | mue D | VCK VC | SE OUT | TIME   |         |        |                  |  |      |  |    |  |  |    |  |   |      |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

14 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600