## 16-Bit, 5Gsps Interpolating and Modulating RF DAC

#### **General Description**

The MAX5868 high-performance interpolating and modulating 16-bit 5Gsps RF DAC can directly synthesize up to 500MHz of instantaneous bandwidth from DC to frequencies greater than 2GHz. The device is optimized for cable and digital video broadcast applications and meets spectral mask requirements for a broad set of communication standards including EPoC, DVB-T, DVB-T2, DVB-C2, ISDB-T, and DOCSIS 3.0/3.1.

The device integrates interpolation filters, a digital quadrature modulator, a numerically controlled oscillator (NCO) and a 14-bit RF DAC core. The user-configurable 4x, 5x, 6x, 8x, 10x, 12x, 16x, 20x or 24x, linear phase interpolation filters reduce the input data bandwidth required from an FPGA/ASIC. The NCO allows for fully agile modulation of the input baseband signal for direct RF synthesis.

The MAX5868 includes a source synchronous 16-bit parallel LVDS data input interface. The input baseband I and Q signals are time interleaved on a single parallel input port configured for double data rate clocking at up to 1240Mwps (620Mwps I and Q each). The device accepts data in word (16 bit), byte (8 bit), or nibble (4 bit) modes. The input data is aligned to the data clock supplied with the data. An input FIFO decouples the timing of the input interface from the DAC update clock domain. In addition, a parity input and parity flag interrupt output are available to ensure data integrity.

The MAX5868 clock input has a flexible clock interface and accepts a differential sine-wave or square-wave input clock signal. The device outputs a divided reference clock to ensure synchronization with the FPGA/ASIC driving its input port. In addition, dedicated input and output signals are provided for synchronizing multiple devices.

The MAX5868 uses a differential current-steering architecture and can produce a 0dBm full-scale output signal level with a  $50\Omega$  load. Operating from 1.8V and 1.0V power supplies, the device consumes 1.5W at 5Gsps. The device is offered in a compact 144-pin CSBGA package and is specified for the extended temperature range (-40°C to +85°C).

For related parts and recommended products to use with this part, refer to www.maximintegrated.com/MAX5868.related.

#### **Features and Benefits**

- Direct RF Synthesis Solution for Communications

- · 4.96Gsps DAC Output Update Rate

- · High-Performance 14-Bit RF DAC Core

- Digital Quadrature Modulator and NCO with 1Hz/10Hz/100Hz/1kHz/10kHz Resolution

- 4x/5x/6x/8x/10x/12x/16x/20x/24x Interpolation

- 16-Bit 1240Mwps DDR Parallel LVDS Data Bus

- Highly Flexible and Configurable

- · Data Bus with Word, Byte and Nibble Modes

- · Reference Clock Output for FPGA Interface

- Multiple DAC Synchronization

- · SPI Interface for Device Configuration

- · Low Power, Compact Solution

- 1.5W at f<sub>CLK</sub> = 5Gsps

- 10mm x 10mm, 144-Pin CSBGA

#### **Applications**

- Ethernet PON over Coax (EPoC)

- Downstream DOCSIS CMTS Modulators

- Digital Video Broadcast

DVB-T / DVB-T2 / DVB-C2 / ISDB-T Modulators

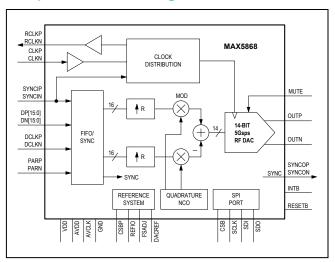

## **Simplified Block Diagram**

Ordering Information appears at end of data sheet.

## 16-Bit, 5Gsps Interpolating and Modulating RF DAC

### **Absolute Maximum Ratings**

| AVDD2, AVCLK2, V <sub>DD2</sub> 0.3V to +2.1V             | AVDD, AVCLK, V <sub>DD</sub> 0.3V to +1.2V               |

|-----------------------------------------------------------|----------------------------------------------------------|

| OUTP, OUTN0.3V to (V <sub>AVDD2</sub> + 0.5V)             | REFIO, DACREF,                                           |

| MUTE, RESETB, CSB, SCLK,                                  | FSADJ, CSBP0.3V to (V <sub>AVDD2</sub> + 0.3V, MAX 2.1V) |

| SDO, SDI, INTB0.3V to (V <sub>DD2</sub> + 0.3V, 2.1V Max) | CLKP, CLKN0.3V to (V <sub>AVCLK2</sub> + 0.3V, MAX 2.1V) |

| SINCIP, SYNCIN, SYNCOP, SYNCON, DCLKP, DCLKN,             | Continuous Power Dissipation (T <sub>A</sub> = +70°C)    |

| RCLKP, RCLKN0.3V to (V <sub>DD2</sub> + 0.3V, 2.1V Max)   | CSBGA (derate 38.8mW/°C above +70°C)3101mW               |

| DP0, DN0, DP1, DN1, DP2, DN2, DP3, DN3,                   | SDO, INTB Maximum Continuous Current8mA                  |

| DP4, DN40.3V to (V <sub>DD2</sub> + 0.3V, 2.1V Max)       | Operating Temperature Range                              |

| DP5, DN5, DP6, DN6, DP7, DN7, DP8, DN8,                   | T <sub>A</sub> 40°C to +85°C                             |

| DP9, DN90.3V to (V <sub>DD2</sub> + 0.3V, 2.1V Max)       | T <sub>J</sub> 40°C to +125°C                            |

| DP10, DN10, DP11, DN11, DP12, DN12, DP13,                 | Junction Temperature+150°C                               |

| DN130.3V to (V <sub>DD2</sub> + 0.3V, 2.1V Max)           | Storage Temperature Range60°C to +150°C                  |

| DP14, DN14, DP15, DN15,                                   | Soldering Temperature (reflow)+260°C                     |

| PARP, PARN0.3V to (V <sub>DD2</sub> + 0.3V, 2.1V Max)     |                                                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Thermal Characteristics (Note 1)**

**CSBGA**

Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )..........12.9°C/W Junction-to-Board Thermal Resistance ( $\theta_{JB}$ )........6.23°C/W Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )......25.8°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

$(V_{AVDD} = V_{AVCLK} = V_{DD} = 1.0V, V_{AVDD2} = V_{AVCLK2} = V_{DD2} = 1.8V, P_{CLK} = 0dBm, 10x interpolation, 16-bit word mode, <math>I_{OUTFS} = 29.5385mA$ , output is  $50\Omega$  double-terminated and transformer coupled, external reference at 1.20V,  $R_{SET} = 1.3k\Omega$  between FSADJ and DACREF.  $T_{A(MIN)} = -40^{\circ}C$ ,  $T_{J(MAX)} = +115^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{J} = +60^{\circ}C$ .) (Note 2)

| PARAMETER                       | SYMBOL             | CONDITIONS                                            | MIN | TYP                    | MAX | UNITS |

|---------------------------------|--------------------|-------------------------------------------------------|-----|------------------------|-----|-------|

| STATIC PERFORMANCE              |                    |                                                       |     |                        |     |       |

| Input Data Word Width           |                    |                                                       |     | 16                     |     | Bits  |

| DAC Resolution                  |                    |                                                       |     | 14                     |     | Bits  |

| Differential Nonlinearity       | DNL                | Figure 4                                              |     | ±1.5                   |     | LSB   |

| Integral Nonlinearity           | INL                | Figure 4                                              |     | ±3                     |     | LSB   |

| Offset Voltage Error            | os                 |                                                       |     | 0.003                  |     | %FS   |

| Full-Scale Output Current Range | I <sub>OUTFS</sub> |                                                       | 10  |                        | 30  | mA    |

| Output Voltage Gain Error       | GE <sub>FS</sub>   | f <sub>OUT</sub> = DC, <u>Figure 4</u>                |     | ±3                     |     | %FS   |

| Output Power                    | Pout               | f <sub>OUT</sub> = 100MHz, f <sub>CLK</sub> = 4.96GHz |     | 0                      |     | dBm   |

| Maximum Output Compliance       |                    | Typical maximum single-ended output voltage           | V   | ' <sub>AVDD2</sub> + 0 | .4  | V     |

| Minimum Output Compliance       |                    | Typical minimum single-ended output voltage           | \   | / <sub>AVDD2</sub> - 0 | 4   | V     |

| Output Resistance               | R <sub>OUT</sub>   | Differential DAC output resistance                    |     | 50                     |     | Ω     |

$(V_{AVDD} = V_{AVCLK} = V_{DD} = 1.0V, V_{AVDD2} = V_{AVCLK2} = V_{DD2} = 1.8V, P_{CLK} = 0 dBm, 10x interpolation, 16-bit word mode, I_{OUTFS} = 29.5385mA, output is <math>50\Omega$  double-terminated and transformer coupled, external reference at 1.20V,  $R_{SET} = 1.3k\Omega$  between FSADJ and DACREF.  $T_{A(MIN)} = -40^{\circ}C$ ,  $T_{J(MAX)} = +115^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{J} = +60^{\circ}C$ .) (Note 2)

| PARAMETER                                               | SYMBOL             | COND                                                                                                   | MIN                                                                              | TYP | MAX  | UNITS |       |

|---------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----|------|-------|-------|

| DYNAMIC PERFORMANCE                                     | J.                 |                                                                                                        |                                                                                  |     |      |       |       |

| DAC Clock Frequency                                     | f <sub>CLK</sub>   | (Note 3)                                                                                               |                                                                                  |     |      | 4960  | MHz   |

| Adjusted DAC Update Rate                                | AUR <sub>DAC</sub> | (Note 4)                                                                                               |                                                                                  |     |      | 1240  | Msps  |

| Maximum Data Clock Frequency                            | fDATACLK           | (Note 5)                                                                                               |                                                                                  |     | 620  |       | MHz   |

| Maximum Input Data Rate                                 | f <sub>DATA</sub>  | DDR interleaved dat                                                                                    | a                                                                                |     | 1240 |       | Mwps  |

|                                                         |                    | Adjacent channel<br>(750kHz from chan-<br>nel block edge to<br>6MHz from channel<br>block edge)        |                                                                                  |     | -67  |       |       |

|                                                         |                    | Next-adjacent<br>channel (6MHz from<br>channel block edge<br>to 12MHz from<br>channel block edge)      | 8x interpolation,<br>f <sub>OUT</sub> = 575MHz,<br>f <sub>DATA</sub> = 1152Mwps, |     | -69  |       |       |

|                                                         | ACPR -             | Third-adjacent<br>channel (12MHz<br>from channel block<br>edge to 18MHz<br>from channel block<br>edge) | 8x interpolation, fOUT = 975MHz, fDATA = 1152Mwps,                               | -69 |      |       |       |

| Out-of-Band Noise and Spurious                          |                    | Noise in any other channel                                                                             |                                                                                  |     | -67  |       | alD a |

| Eight 6MHz QAM Carriers<br>Average Total Power = -15dBm |                    | Adjacent channel<br>(750kHz from chan-<br>nel block edge to<br>6MHz from channel<br>block edge)        |                                                                                  |     | -65  |       | dBc   |

|                                                         |                    | Next-adjacent<br>channel (6MHz from<br>channel block edge<br>to 12MHz from<br>channel block edge)      |                                                                                  |     | -68  |       |       |

|                                                         |                    | Third-adjacent<br>channel (12MHz<br>from channel block<br>edge to 18MHz<br>from channel block<br>edge) | f <sub>CLK</sub> = 4608MHz                                                       |     | -67  |       |       |

|                                                         |                    | Noise in any other channel                                                                             |                                                                                  |     | -64  |       |       |

$(V_{AVDD} = V_{AVCLK} = V_{DD} = 1.0V, V_{AVDD2} = V_{AVCLK2} = V_{DD2} = 1.8V, P_{CLK} = 0 dBm, 10x interpolation, 16-bit word mode, I_{OUTFS} = 29.5385mA, output is 50Ω double-terminated and transformer coupled, external reference at 1.20V, R_{SET} = 1.3kΩ between FSADJ and DACREF. <math>T_{A(MIN)} = -40$ °C,  $T_{J(MAX)} = +115$ °C, unless otherwise noted. Typical values are at  $T_{J} = +60$ °C.) (Note 2)

| PARAMETER                                                                                                                 | SYMBOL                                                                                        | COND                                                                                                    | MIN                                                         | TYP | MAX  | UNITS |     |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-----|------|-------|-----|

|                                                                                                                           |                                                                                               | Adjacent chan-<br>nel (from channel<br>block edge to<br>192MHz from chan-<br>nel block edge)            | f <sub>OUT</sub> = 1100MHz,                                 |     | -59  |       |     |

| Adjacent Channel Power Ratio<br>Thirty-Two 6MHz QAM Carriers<br>192MHz Wideband<br>Average Total Output<br>Power = -17dBm |                                                                                               | Next-adjacent<br>channel (192MHz<br>from channel block<br>edge to 384MHz<br>from channel block<br>edge) | f <sub>DATA</sub> = 1152Mwps,<br>f <sub>CLK</sub> = 4608MHz |     | -59  |       |     |

|                                                                                                                           | channel block<br>edge)  Next-adjacent<br>channel (192MH<br>from channel blo<br>edge to 384MHz | nel (from chan-<br>nel block edge<br>to 192MHz from<br>channel block                                    | f <sub>OUT</sub> = 1600MHz,                                 |     | -57  |       | dBc |

|                                                                                                                           |                                                                                               | channel (192MHz<br>from channel block<br>edge to 384MHz<br>from channel block                           | f <sub>DATA</sub> = 1152Mwps,<br>f <sub>CLK</sub> = 4608MHz |     |      |       |     |

| Harmonic Distortion                                                                                                       |                                                                                               | Second harmonic distortion                                                                              | f <sub>OUT</sub> = 400MHz,<br>f <sub>DATA</sub> = 1152Mwps, |     | -66  |       |     |

| Eight 6MHz QAM Carriers<br>Average Total Power = -15dBFS                                                                  | HD                                                                                            | Third harmonic distortion                                                                               | f <sub>CLK</sub> = 4608MHz,<br>8x interpolation             |     | -67  |       | dBc |

| Output Settling Time for Full-                                                                                            |                                                                                               | To ±0.024% of output full-scale, 4x interpolation                                                       | f <sub>CLK</sub> = 2460MHz                                  |     | 32   |       |     |

| Scale Input Step (Note 6)                                                                                                 |                                                                                               | To ±0.024% of output full-scale, 10x interpolation                                                      | f <sub>CLK</sub> = 4915.2MHz                                |     | 41   |       | ns  |

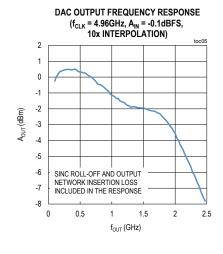

| Output Bandwidth                                                                                                          |                                                                                               | f <sub>DAC</sub> = 4915.2MHz,<br>(Note 7)                                                               | -1dB bandwidth                                              |     | 2250 |       | MHz |

$(V_{AVDD} = V_{AVCLK} = V_{DD} = 1.0V, V_{AVDD2} = V_{AVCLK2} = V_{DD2} = 1.8V, P_{CLK} = 0 dBm, 10x interpolation, 16-bit word mode, I_{OUTFS} = 29.5385mA, output is 50Ω double-terminated and transformer coupled, external reference at 1.20V, R_{SET} = 1.3kΩ between FSADJ and DACREF. <math>T_{A(MIN)} = -40$ °C,  $T_{J(MAX)} = +115$ °C, unless otherwise noted. Typical values are at  $T_{J} = +60$ °C.) (Note 2)

| PARAMETER                         | SYMBOL             | CONDITIONS                | MIN  | TYP                                              | MAX                 | UNITS           |

|-----------------------------------|--------------------|---------------------------|------|--------------------------------------------------|---------------------|-----------------|

| INTERPOLATION FILTERS             | <u> </u>           |                           | •    |                                                  |                     |                 |

| Interpolation Rates               | R                  |                           |      | 4,<br>5,<br>6,<br>8,<br>10,<br>12,<br>16,<br>20, |                     |                 |

|                                   |                    |                           |      | 20,<br>24                                        |                     |                 |

| Passband Width                    | PBW                | Ripple < 0.01dB           | 0.4  | 07 x f <sub>DA</sub>                             | <br><sub>C</sub> /R |                 |

| Stopband Rejection                |                    | 0.5 x f <sub>DAC</sub> /R |      | 90                                               |                     | dB              |

|                                   |                    | 4x interpolation          |      | 288                                              |                     |                 |

|                                   |                    | 5x interpolation          |      | 382                                              |                     | 1               |

|                                   |                    | 6x interpolation          |      | 420                                              |                     | 1               |

|                                   |                    | 8x interpolation          |      | 496                                              |                     | ]               |

| Data Latency                      |                    | 10x interpolation         |      | 673                                              |                     | Clock<br>Cycles |

|                                   |                    | 12x interpolation         |      | 764                                              |                     | Joyoloo         |

|                                   |                    | 16x interpolation         |      | 864                                              |                     |                 |

|                                   |                    | 20x interpolation         |      | 1137                                             |                     |                 |

|                                   |                    | 24x interpolation         |      | 1317                                             |                     |                 |

| NCO                               |                    |                           |      |                                                  |                     |                 |

| Maximum Frequency                 |                    |                           |      | f <sub>CLK</sub> /2                              |                     | Hz              |

| Frequency Control Word Resolution |                    |                           |      | 32                                               |                     | Bits            |

| SNR                               |                    |                           |      | 86.5                                             |                     | dB              |

| SFDR                              |                    |                           |      | 92.4                                             |                     | dBc             |

| REFERENCE                         |                    |                           |      |                                                  |                     |                 |

| Reference Input Range             |                    |                           | 1.10 |                                                  | 1.30                | V               |

| Reference Output Voltage          | V <sub>REFIO</sub> | Internal reference        | 1.10 | 1.20                                             | 1.30                | V               |

| Reference Input Resistance        | R <sub>REFIO</sub> |                           |      | 10                                               |                     | kΩ              |

| Reference Voltage Drift           |                    |                           |      | ±65                                              |                     | ppm/°C          |

$(V_{AVDD} = V_{AVCLK} = V_{DD} = 1.0V, V_{AVDD2} = V_{AVCLK2} = V_{DD2} = 1.8V, P_{CLK} = 0dBm, 10x interpolation, 16-bit word mode, I_{OUTFS} = 29.5385mA, output is 50Ω double-terminated and transformer coupled, external reference at 1.20V, R_{SET} = 1.3kΩ between FSADJ and DACREF. <math>T_{A(MIN)} = -40^{\circ}C$ ,  $T_{J(MAX)} = +115^{\circ}C$ , unless otherwise noted. Typical values are at  $T_{J} = +60^{\circ}C$ .) (Note 2)

| PARAMETER                                    | SYMBOL            | CON                                                                        | MIN                                | TYP                  | MAX      | UNITS                 |                  |

|----------------------------------------------|-------------------|----------------------------------------------------------------------------|------------------------------------|----------------------|----------|-----------------------|------------------|

| CMOS LOGIC INPUTS/OUTPUT                     | S (INTB, RES      | ETB, MUTE, CSB, S                                                          | SCLK, SDI, SDO)                    |                      |          |                       |                  |

| Input High Voltage                           | V <sub>IH</sub>   |                                                                            |                                    | 0.7 x V <sub>D</sub> | D2       |                       | V                |

| Input Low Voltage                            | V <sub>IL</sub>   |                                                                            |                                    |                      | 0        | .3 x V <sub>DD2</sub> | V                |

| Input Current                                | I <sub>IN</sub>   | Excluding RESETE                                                           | 3                                  | -10                  | ±0.1     | +10                   | μΑ               |

| RESETB Input Current                         | I <sub>INRB</sub> |                                                                            |                                    | -10                  |          | +55                   | μΑ               |

| Input Capacitance                            | C <sub>IN</sub>   |                                                                            |                                    |                      | 3        |                       | pF               |

| Output High Voltage                          | V <sub>OH</sub>   | I <sub>LOAD</sub> = 200μA, IN resistor to V <sub>DD2</sub>                 | TB has a 1kΩ pullup                | 0.8 x V <sub>D</sub> | D2       |                       | V                |

| Output Low Voltage                           | V <sub>OL</sub>   | I <sub>SINK</sub> = 200µA, IN <sup>-</sup><br>resistor to V <sub>DD2</sub> | ΓB has a 1kΩ pullup                |                      | 0        | .2 x V <sub>DD2</sub> | V                |

| Output Leakage Current                       |                   | Three-state                                                                |                                    |                      | ±2.5     |                       | μA               |

| Rise/Fall Time                               |                   | C <sub>LOAD</sub> = 10pF, 20                                               | % to 80%                           |                      | 0.5      |                       | ns               |

| LVDS LOGIC INPUT/OUTPUT (DRCLKN, PARP, PARN) | P15–D0P, DN       | I15–DN0, SYNCIP, S                                                         | SYNCIN, SYNCOP, SYN                | ICON, DC             | LKP, DCL | KN, RCLK              | P,               |

| Differential Input Logic High                | V <sub>IH</sub>   |                                                                            |                                    |                      |          | 100                   | mV               |

| Differential Input Logic Low                 | V <sub>IL</sub>   |                                                                            |                                    | -100                 |          |                       | mV               |

| Input Common Mode Voltage                    | V <sub>ICM</sub>  |                                                                            |                                    | 0.675                |          | 1.375                 | V                |

| Differential Input Resistance                | R <sub>IN</sub>   |                                                                            |                                    | 87.5                 | 100      | 132.5                 | Ω                |

| Differential Output Logic High               | V <sub>OH</sub>   | $R_{LOAD}$ = 100Ω diff                                                     | ferential                          | 275                  |          | 450                   | mV               |

| Differential Output Logic Low                | V <sub>OL</sub>   | $R_{LOAD}$ = 100Ω diff                                                     | ferential                          | -450                 |          | -275                  | mV               |

| Output Common Mode Voltage                   | V <sub>OCM</sub>  |                                                                            |                                    | 1.125                | 1.25     | 1.375                 | V                |

| Output Maximum Frequency                     | f <sub>RCLK</sub> | $R_{LOAD} = 100\Omega$ diff                                                | ferential, C <sub>LOAD</sub> = 8pF |                      | 620      |                       | MHz              |

| CLOCK INPUT (CLKP, CLKN)                     | •                 |                                                                            |                                    | •                    |          |                       |                  |

| Differential Input Voltage Swing             | V <sub>DIFF</sub> | Sine-wave input                                                            |                                    |                      | > 0.5    |                       | V <sub>P-P</sub> |

| Common Mode Voltage                          | V <sub>COM</sub>  | AC-coupled, intern                                                         | ally biased                        |                      | 0.5      |                       | V                |

| Differential Input Resistance                | R <sub>CLK</sub>  |                                                                            |                                    |                      | 100      |                       | Ω                |

| DATA CLOCK TIMING (8x INTER                  | RPOLATION,        | f <sub>CLK</sub> = 4.9152GHz)                                              | (Note 8)                           |                      |          |                       |                  |

| Data Setup Time                              |                   | DATACLK rising edge                                                        | 1405°0 × T × 105°0                 | -680                 |          |                       |                  |

| (DATACLK to DATA)                            | ts                | DATACLK falling edge                                                       | +125°C > T <sub>J</sub> > +65°C    | -680                 |          |                       | ps               |

| Data Hold Time                               |                   | DATACLK rising edge                                                        | 1125°C > T > 165°C                 | 420                  |          |                       |                  |

| (DATACLK to DATA)                            | t <sub>H</sub>    | DATACLK falling edge                                                       | - +125°C > T <sub>J</sub> > +65°C  | 420                  |          |                       | ps               |

$(V_{AVDD} = V_{AVCLK} = V_{DD} = 1.0V, V_{AVDD2} = V_{AVCLK2} = V_{DD2} = 1.8V, P_{CLK} = 0dBm, 10x interpolation, 16-bit word mode, I_{OUTFS} = 29.5385mA, output is 50Ω double-terminated and transformer coupled, external reference at 1.20V, R<sub>SET</sub> = 1.3kΩ between FSADJ and DACREF. <math>T_{A(MIN)} = -40$ °C,  $T_{J(MAX)} = +115$ °C, unless otherwise noted. Typical values are at  $T_{J} = +60$ °C.) (Note 2)

| PARAMETER                   | SYMBOL                                                            | CONDITIONS                                      | MIN  | TYP  | MAX  | UNITS |

|-----------------------------|-------------------------------------------------------------------|-------------------------------------------------|------|------|------|-------|

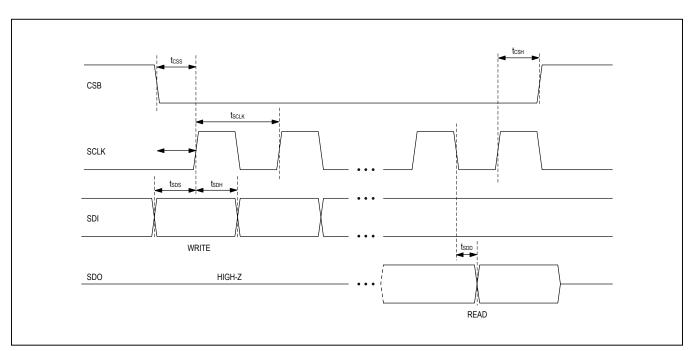

| SERIAL PORT INTERFACE TIM   | ING                                                               |                                                 |      |      |      |       |

| SCLK Frequency              | f <sub>SCLK</sub>                                                 | 1/t <sub>SCLK</sub>                             |      |      | 50   | MHz   |

| SCLK to CSB Setup Time      | t <sub>CSS</sub>                                                  |                                                 |      | 10   |      | ns    |

| SCLK to CSB Hold Time       | tcsH                                                              |                                                 |      | 1    |      | ns    |

| SDI to SCLK Hold Time       | t <sub>SDH</sub>                                                  | Data-read                                       |      | 1    |      | ns    |

| SDI to SCLK Setup Time      | t <sub>SDS</sub>                                                  | Data-read                                       |      | 10   |      | ns    |

| SCLK to SDO Data Delay      | t <sub>SDD</sub>                                                  | Data-write                                      |      | 15   |      | ns    |

| POWER SUPPLY                |                                                                   |                                                 |      |      |      |       |

| 1.0V Supply Voltage Range   | V <sub>DD</sub> ,<br>V <sub>AVCLK</sub> ,<br>V <sub>AVDD</sub>    |                                                 | 0.95 | 1.0  | 1.05 | V     |

| 1.8V Supply Voltage Range   | V <sub>DD2</sub> ,<br>V <sub>AVCLK2</sub> ,<br>V <sub>AVDD2</sub> |                                                 | 1.71 | 1.8  | 1.89 | V     |

| 1.0V Digital Supply Current | I <sub>VDD</sub>                                                  |                                                 |      | 520  | 680  | mA    |

| 1.8V Digital Supply Current | I <sub>VDD2</sub>                                                 |                                                 |      | 16   | 23.5 | mA    |

| 1.0V Clock Supply Current   | I <sub>AVCLK</sub>                                                | f <sub>CLK</sub> = 4915.2MHz, -1dBFS peak input |      | 300  | 442  | mA    |

| 1.8V Clock Supply Current   | I <sub>AVCLK2</sub>                                               | power, 10x interpolation,                       |      | 20   | 22   | mA    |

| 1.0V Analog Supply Current  | I <sub>AVDD</sub>                                                 | f <sub>CENTER</sub> = 2140MHz                   |      | 192  | 280  | mA    |

| 1.8V Analog Supply Current  | I <sub>AVDD2</sub>                                                |                                                 |      | 244  | 290  | mA    |

| Total Power Dissipation     | P <sub>TOTAL</sub>                                                |                                                 |      | 1516 | 2006 | mW    |

- Note 2: All specifications are guaranteed via test at T<sub>J</sub> = +60°C and T<sub>J</sub> = +115°C to an accuracy of ±10°C, unless otherwise noted. Specifications at T<sub>J</sub> < +60°C are guaranteed by design and characterization. Timing specifications are guaranteed by design and characterization.

- **Note 3:**  $f_{DAC}$  (DAC update rate) =  $f_{CLK}$ .

- Note 4: Adjusted DAC update rate is defined as the maximum DAC update rate divided by the smallest interpolating factor. For the MAX5868, the maximum DAC update rate is 4960Msps and the smallest interpolating factor is 4. Adjusted DAC update rate = 4960Msps/4 = 1240Msps. Note this is a mathematically derived specification and is not production tested.

- Note 5: f<sub>DATACLK</sub> = f<sub>DCLK</sub> = Data Clock Frequency.

- **Note 6:** Settling time is dominated by the interpolation filter step response.

- Note 7: Excludes  $\sin(x)/x$  rolloff.

- Note 8: Specification guaranteed by design and characterization, not production tested.

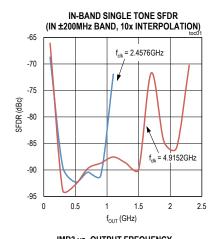

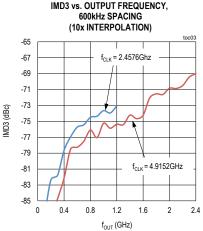

## **Typical Operating Characteristics**

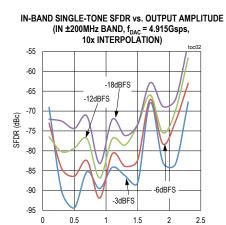

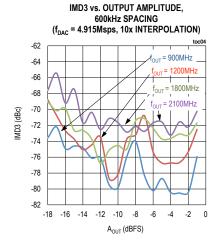

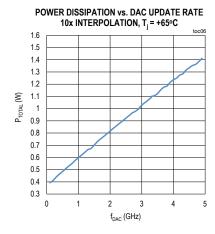

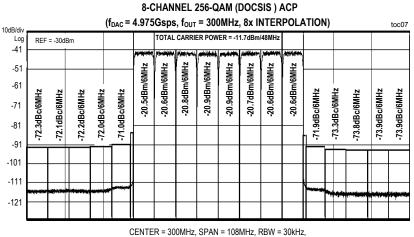

$(V_{AVDD} = V_{AVCLK} = V_{DD} = 1.0V, V_{AVDD2} = V_{AVCLK2} = V_{DD2} = 1.8V, P_{CLK} = 0dBm, 16-bit word mode, I_{OUTFS} = 29.5385mA, output is <math>50\Omega$  double-terminated and transformer coupled, external reference at 1.20V,  $R_{SET} = 1.3k\Omega$  between FSADJ and DACREF,  $T_A = +25^{\circ}C$ ,  $T_J = +65^{\circ}C$ , unless otherwise noted.)

$f_{OUT}\left(GHz\right)$

$(V_{AVDD} = V_{AVCLK} = V_{DD} = 1.0V, V_{AVDD2} = V_{AVCLK2} = V_{DD2} = 1.8V, P_{CLK} = 0dBm, 16-bit word mode, I_{OUTFS} = 29.5385mA, output is <math>50\Omega$  double-terminated and transformer coupled, external reference at 1.20V,  $R_{SET} = 1.3k\Omega$  between FSADJ and DACREF,  $T_A = +25^{\circ}C$ ,  $T_J = +65^{\circ}C$ , unless otherwise noted.)

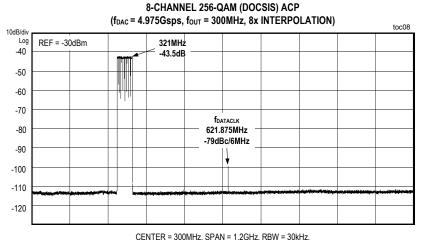

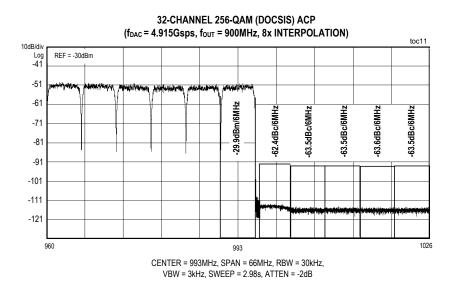

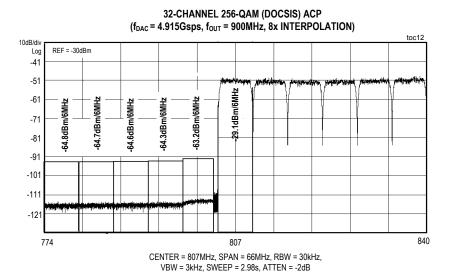

VBW = 3kHz, SWEEP = 2.98s, ATTEN = -2dB

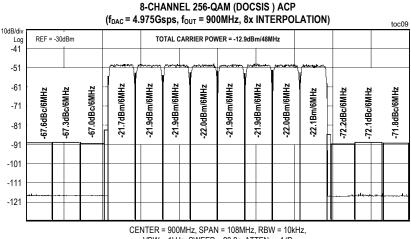

VBW = 3kHz, SWEEP = 13.4s, ATTEN = -6dB

$(V_{AVDD} = V_{AVCLK} = V_{DD} = 1.0V, V_{AVDD2} = V_{AVCLK2} = V_{DD2} = 1.8V, P_{CLK} = 0 dBm, 16-bit word mode, I_{OUTFS} = 29.5385 mA,$ output is  $50\Omega$  double-terminated and transformer coupled, external reference at 1.20V,  $R_{SET}$  = 1.3k $\Omega$  between FSADJ and DACREF,  $T_A = +25$ °C,  $T_J = +65$ °C, unless otherwise noted.)

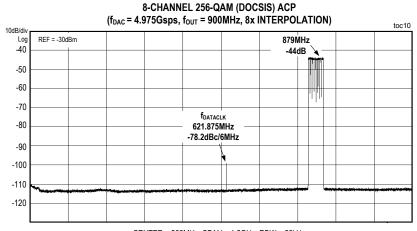

VBW = 1kHz, SWEEP = 20.9s, ATTEN = -4dB

\*SETUP OPTIMIZED FOR GAIN FLATNESS. ADDITIONAL REDUCTION IN NOISE FLOOR POSSIBLE BY DECREASING ATTENUATION.

CENTER = 900MHz, SPAN = 1.2GHz, RBW = 30kHz, VBW = 3kHz. SWEEP = 13.4s. ATTEN = -6dB

Maxim Integrated | 10 www.maximintegrated.com

$(V_{AVDD} = V_{AVCLK} = V_{DD} = 1.0V, V_{AVDD2} = V_{AVCLK2} = V_{DD2} = 1.8V, P_{CLK} = 0dBm, 16-bit word mode, I_{OUTFS} = 29.5385mA, output is <math>50\Omega$  double-terminated and transformer coupled, external reference at 1.20V,  $R_{SET} = 1.3k\Omega$  between FSADJ and DACREF,  $T_A = +25^{\circ}C$ ,  $T_J = +65^{\circ}C$ , unless otherwise noted.)

\*SETUP OPTIMIZED FOR NOISE FLOOR. GAIN FLATNESS IS IMPROVED BY INCREASING ATTENUATION.

\*SETUP OPTIMIZED FOR NOISE FLOOR. GAIN FLATNESS IS IMPROVED BY INCREASING ATTENUATION.

$(V_{AVDD} = V_{AVCLK} = V_{DD} = 1.0V, V_{AVDD2} = V_{AVCLK2} = V_{DD2} = 1.8V, P_{CLK} = 0dBm, 16-bit word mode, I_{OUTFS} = 29.5385mA, output is <math>50\Omega$  double-terminated and transformer coupled, external reference at 1.20V,  $R_{SET} = 1.3k\Omega$  between FSADJ and DACREF,  $T_A = +25^{\circ}C$ ,  $T_J = +65^{\circ}C$ , unless otherwise noted.)

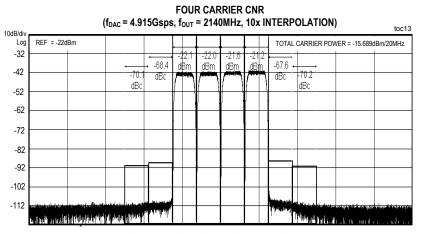

CENTER = 2140MHz, SPAN = 80MHz, RBW = 30kHz, VBW = 3kHz, SWEEP = 1.104s, ATTEN = 0dB

FOUR CARRIER CNR

#### (fDAC = 4.915Gsps, fout = 2140MHz, 10x INTERPOLATION) RFF = -20dBm Log $f_{OUT} = 2140MHz$ f<sub>DAC</sub> - f<sub>OUT</sub> = 2775MHz -30 $f_{DAC} = 4915MHz$ -40 -50 -60 -70 fdac - fdataclk f<sub>DAC</sub>/2 Folded HD2 -80 -90 -100 -110

CENTER = 2700MHz, SPAN = 5GHz, RBW = 1MHz, VBW = 1MHz, SWEEP = 21.3ms, ATTEN= -2dB

# 16-Bit, 5Gsps Interpolating and Modulating RF DAC

## **Ball Configuration**

| TOP VI     | EW           |              |            |             | MAX                   | 5868        |                   |           |             |             |             |

|------------|--------------|--------------|------------|-------------|-----------------------|-------------|-------------------|-----------|-------------|-------------|-------------|

| REFIO A1   | CSBP A2      | AVCLK A3     | AVDD2      | AVDD2       | OUTP A6               | OUTN A7     | AVDD2             | AVDD2     | AVCLK       | AVCLK2      | AVCLK2      |

| DACREF B1  | FSADJ<br>B2  | GND<br>B3    | AVDD2      | AVDD2       | OUTP<br>B6            | OUTN B7     | AVDD2             | AVDD2     | GND<br>B10  | GND<br>B11  | GND<br>B12  |

| GND<br>C1  | AVDD2        | AVDD2        | GND<br>C4  | GND<br>C5   | GND<br>C6             | GND<br>C7   | GND<br>C8         | GND<br>C9 | GND<br>C10  | CLKP<br>C11 | CLKP<br>C12 |

| GND D1     | GND D2       | GND D3       | GND D4     | GND D5      | GND D6                | GND D7      | GND D8            | GND D9    | GND D10     | CLKN D11    | CLKN D12    |

| SCLK<br>E1 | CSB<br>E2    | GND<br>E3    | GND<br>E4  | GND<br>E5   | GND<br>E6             | GND<br>E7   | GND<br>E8         | GND<br>E9 | GND<br>E10  | GND<br>E11  | GND<br>E12  |

| SDI<br>F1  | RESETB F2    | GND<br>F3    | AVDD F4    | GND<br>F5   | GND F6                | GND F7      | GND<br>F8         | AVDD F9   | GND<br>F10  | GND<br>F11  | GND<br>F12  |

| SDO<br>G1  | INTB G2      | MUTE<br>G3   | GND<br>G4  | GND<br>G5   | GND<br>G6             | GND<br>G7   | GND<br>G8         | GND<br>G9 | GND<br>G10  | GND<br>G11  | GND<br>G12  |

| PARP<br>H1 | SYNCIP<br>H2 | SYNCOP<br>H3 | GND<br>H4  | VDD<br>H5   | VDD<br>H6             | VDD<br>H7   | VDD<br>H8         | VDD<br>H9 | GND<br>H10  | GND<br>H11  | GND<br>H12  |

| PARN J1    | SYNCIN J2    | SYNCON<br>J3 | VDD2       | VDD2        | VDD J6                | VDD J7      | VDD J8            | VDD2      | VDD2        | TDC J11     | TDA  J12    |

| DP14<br>K1 | DN14<br>K2   | DP15<br>K3   | DN15       | DCLKP<br>K5 | DCLKN<br>K6           | RCLKP<br>K7 | RCLKN<br>K8       | DP0       | DN0<br>(K10 | DP1 (K11)   | DN1<br>K12  |

| DP13       | DP12         | DP11         | DP10       | DP9         | DP8                   | DP7         | DP6               | DP5       | DP4         | DP3         | DP2         |

| DN13 M1    | DN12         | DN11 M3      | DN10<br>M4 | DN9 M5      | DN8                   | DN7         | DN6 M8            | DN5<br>M9 | DN4<br>M10  | DN3<br>M11  | DN2<br>M12  |

|            | GND          | s            | UPPLIES    |             | ITICAL RF<br>D ANALOG |             | DATA,<br>CLOCK IO |           |             |             |             |

## **Ball Description**

| BALL                                                                                                | NAME   | FUNCTION                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1                                                                                                  | REFIO  | Reference Voltage Input/Output. REFIO outputs an internal 1.2V bandgap reference voltage. REFIO has a $10k\Omega$ series resistance and can be driven using an external 1.2V reference voltage. Connect a $1\mu\text{F}$ capacitor between REFIO and DACREF.                                        |

| A2                                                                                                  | CSBP   | DAC Current Source Bypass. Connect a 1µF capacitor between CSBP and DACREF.                                                                                                                                                                                                                         |

| A3, A10                                                                                             | AVCLK  | 1.0V Supply Input for Clock                                                                                                                                                                                                                                                                         |

| A4, A5, A8, A9, B4,<br>B5, B8, B9, C2, C3                                                           | AVDD2  | Analog 1.8V Supply Input                                                                                                                                                                                                                                                                            |

| A6, B6                                                                                              | OUTP   | Positive Terminal of Differential DAC Output                                                                                                                                                                                                                                                        |

| A7, B7                                                                                              | OUTN   | Negative Terminal of Differential DAC Output                                                                                                                                                                                                                                                        |

| A11, A12                                                                                            | AVCLK2 | 1.8V Supply Input for Clock                                                                                                                                                                                                                                                                         |

| B1                                                                                                  | DACREF | DAC Reference Ground. Do not connect to ground (GND).                                                                                                                                                                                                                                               |

| B2                                                                                                  | FSADJ  | Analog Input for DAC Full-Scale Output Current Adjustment. A resistor from FSADJ to DACREF sets the full-scale output current of the DAC. To obtain a 29.5385mA full-scale output current using the internal reference voltage, connect a $1.3 \mathrm{k}\Omega$ resistor between FSADJ and DACREF. |

| B3, B10, B11,<br>B12, C4–C10,<br>D4–D10, E3–E12,<br>F3, F5–F8, F10,<br>F11, F12,<br>G4–G10, H4, H10 | GND    | Ground                                                                                                                                                                                                                                                                                              |

| C1, D1, D2,<br>D3, G11, G12,<br>H11, H12                                                            | GND    | Must be grounded for normal operation.                                                                                                                                                                                                                                                              |

| C11, C12                                                                                            | CLKP   | DAC Clock Positive Input. An internal $100\Omega$ termination resistor connects CLKP to CLKN.                                                                                                                                                                                                       |

| D11, D12                                                                                            | CLKN   | DAC Clock Negative Input                                                                                                                                                                                                                                                                            |

| E1                                                                                                  | SCLK   | Digital CMOS Input for Serial Port Interface Clock                                                                                                                                                                                                                                                  |

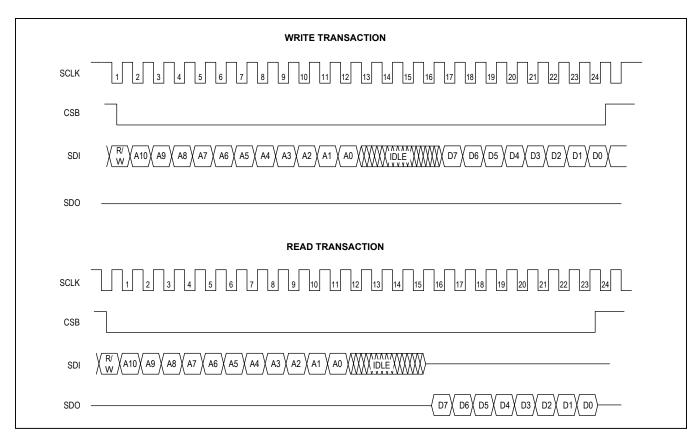

| E2                                                                                                  | CSB    | Digital CMOS Input for Serial Port Interface Chip Selection Bar. MAX5868 is selected when CSB = low.                                                                                                                                                                                                |

| F1                                                                                                  | SDI    | Digital CMOS Input for Serial Port Interface Data Input. Serial port data is latched on the rising edge of SCLK.                                                                                                                                                                                    |

| F2                                                                                                  | RESETB | Digital CMOS Input with Internal Pulldown to Ground. Device is reset when RESETB = low. Set RESETB low during device startup. RESETB must be set high for normal operation after startup.                                                                                                           |

| F4, F9                                                                                              | AVDD   | Analog 1.0V Supply Input                                                                                                                                                                                                                                                                            |

| G1                                                                                                  | SDO    | Digital CMOS Output for Serial Port Interface Data Output. Serial port data is clocked out from MAX5868 on the falling edge of SCLK.                                                                                                                                                                |

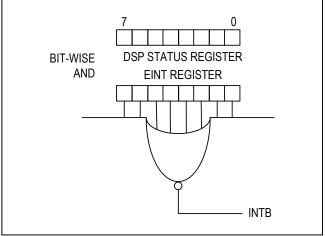

| G2                                                                                                  | INTB   | Digital CMOS Output for Interrupt. Types of interrupts are defined by the EINT SPI register. The cause of the interrupt is determined by reading the STATUS SPI register.                                                                                                                           |

| BALL                                                                                                | NAME   | FUNCTION                                                                                                                                                                                                                                                                                            |

## **Ball Description (continued)**

| Dan Descriptio              | 11 (00111111111111111111111111111111111 | ,                                                                                                                                                                                   |

|-----------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

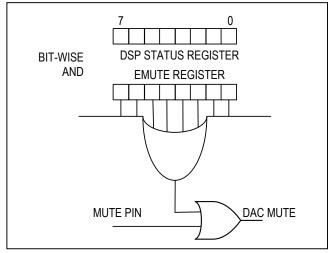

| G3                          | MUTE                                    | Digital CMOS Input MUTE = high puts the device into mute mode. MUTE = low puts the device into normal operation mode.                                                               |

| H1                          | PARP                                    | LVDS Positive Input for Parity Bit. A differential $100\Omega$ termination resistor is on-chip between PARP and PARN.                                                               |

| H2                          | SYNCIP                                  | LVDS Positive Input for Synchronization. A differential $100\Omega$ termination resistor is on-chip between SYNCIP and SYNCIN.                                                      |

| H3                          | SYNCOP                                  | LVDS Positive Output for Synchronization                                                                                                                                            |

| H5–H9, J6, J7, J8           | $V_{DD}$                                | 1.0V Supply Input for Digital Core                                                                                                                                                  |

| J1                          | PARN                                    | LVDS Negative Input for Parity Bit                                                                                                                                                  |

| J2                          | SYNCIN                                  | LVDS Negative Input for Synchronization                                                                                                                                             |

| J3                          | SYNCON                                  | LVDS Negative Output for Synchronization                                                                                                                                            |

| J4, J5, J9, J10             | V <sub>DD2</sub>                        | 1.8V Supply Input for Digital I/O                                                                                                                                                   |

| J11                         | TDC                                     | Temperature Sensor Diode Cathode. Connect TDC and TDA to ground if not used.                                                                                                        |

| J12                         | TDA                                     | Temperature Sensor Diode Anode. Connect TDC and TDA to ground if not used.                                                                                                          |

| K1, K3, K9, K11,<br>L1–L12, | DP15-DP0                                | LVDS Positive Data Input for DAC Data. DP15 is MSB. Offset binary format is default. A differential $100\Omega$ termination resistor is on chip between each data pair DPx and DNx. |

| K2, K4, K10, K12,<br>M1–M12 | DN15-DN0                                | LVDS Negative Inputs for DAC Data. DN15 is MSB. Offset binary format is default.                                                                                                    |

| K5                          | DCLKP                                   | LVDS Positive Input for DAC Data Clock. A differential $100\Omega$ termination resistor is on-chip between DCLKP and DCLKN.                                                         |

| K6                          | DCLKN                                   | LVDS Negative Input for DAC Data Clock                                                                                                                                              |

| K7                          | RCLKP                                   | LVDS Positive Output for Reference Data Clock Equal to 1/2 the Expected Input Data Rate (f <sub>DATA</sub> ) Operating in Double Data Rate (DDR)                                    |

| K8                          | RCLKN                                   | LVDS Negative Output for Reference Data Clock Equal to 1/2 the Expected Input Data Rate (f <sub>DATA</sub> ) Operating in Double Data Rate (DDR)                                    |

### **Functional Diagram**

#### **Detailed Description**

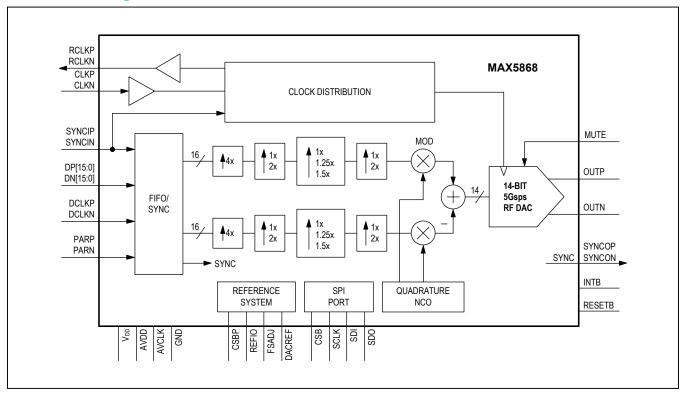

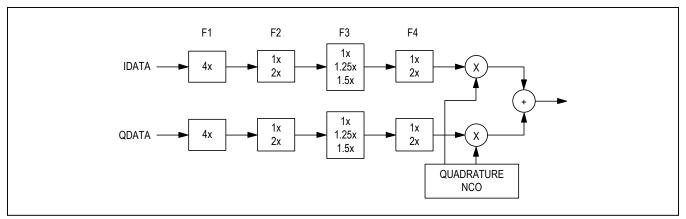

The MAX5868 is a high-performance interpolating and modulating 16-bit 5Gsps RF DAC designed for EPoC, digital video broadcast, and downstream DOCSIS CMTS modulators. The device can synthesize up to 500MHz of instantaneous bandwidth at frequencies up to the Nyquist bandwidth (f<sub>CLK</sub>/2) of the DAC. The major functional blocks of the device include a 16-bit parallel LVDS interface, a cascade of interpolation filters, a digital quadrature modulator and NCO, and a 14-bit, 5Gsps RF DAC. The supporting functional blocks include the clock distribution system, reference system, and SPI interface. See detailed *Functional Diagram*.

Input baseband data is supplied to the device in quadrature via a 16-bit parallel LVDS interface (DP[15:0]/DN[15:0]). The data streams for I and Q channels are time interleaved, therefore the data rate through the input port is twice the input data rate to the I and Q channels. Data can be fed to the device in nibble (4 bit), byte (8 bit) or word (16 bit) modes, allowing for flexibility to optimize the number and speed of the LVDS data pairs driving the DAC.

Before entering the DSP portion of the signal path, the data timing is realigned in the input FIFO buffer to ensure accurate data capture. The FIFO buffer allows the input data port to be synchronized with an external data clock (DCKLP/DCKLN). The input data clock needs to be frequency locked with the DAC clock (CLKP/CLKN) but there are no restrictions on its phase. The device expects even parity and can be configured to produce an interrupt when parity errors are detected. 16-bit input data enhances the accuracy of the interpolation and modulation functions and ensures true 14-bit data is presented to the RF DAC core.

The DSP path consists of a chain of configurable interpolation filters. Interpolation rates of 4x, 5x, 6x, 8x, 10x, 12x, 16x, 20x or 24x can be selected by bypassing one or more of the interpolation filters. Interpolation reduces the required input data rate to the device relaxing the requirements on the FPGA or ASIC. In addition, interpolation increases the separation between the desired signal and its aliased image easing filter design requirements.

After passing through the interpolation stages, the signal is modulated using the LO signal generated by the NCO

and the digital quadrature modulator. The NCO allows for fully agile modulation of the input baseband signal for direct RF synthesis with 32 bits of frequency setting resolution. Placing the modulator at the output of the interpolator chain allows for fully agile placement of the output carrier frequency within the Nyquist bandwidth of the DAC. The quadrature modulator produces a real signal at its output, which is in turn fed into the 14-bit DAC core where it is converted to an analog RF signal. The analog output produces a full-scale current between 10mA and 30mA driving loads up to  $50\Omega$  differential.

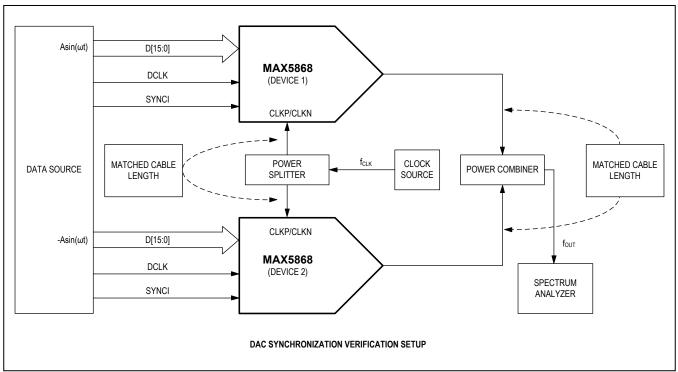

The clock distribution system provides a low noise differential input buffer for the external master DAC clock (CLKP/CLKN) and delivers all necessary clocks to all the DAC blocks. The DAC clock input accepts a differential sine-wave or square-wave signal. The device outputs a divided reference clock (RCLKP/RCLKN) that is equal to 1/2 the expected input data rate (fDATA) operating in Double Data Rate (DDR) to facilitate synchronization with the FPGA or ASIC driving its data port. Two additional signals, SYNCI and SYNCO, are provided to facilitate synchronizing multiple MAX5868 devices.

The reference system delivers the reference current to the DAC current source array and all bias currents necessary for the circuit operation. The reference system also includes a band-gap reference, which can be used as a reference for the DAC full scale current.

The SPI port is a bidirectional interface and is used for configuring the device and reading/writing status and control registers.

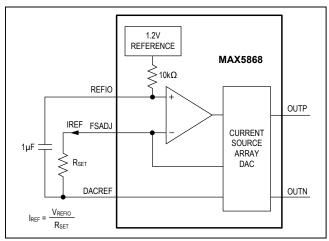

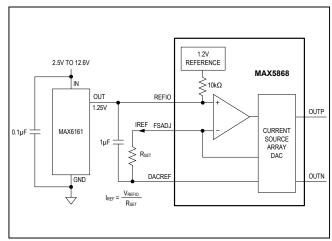

Figure 1. Reference Architecture, Internal Reference Configuration

The device operates from 1.8V and 1.0V power supply voltages and consumes 1.5W at 5Gsps.

#### Reference Interface

The device operates with either the on-chip 1.2V bandgap reference or an external reference voltage source as shown in Figure 1 and Figure 2. REFIO serves as the input for an external, low-impedance reference source. or as the reference output when the internal reference is used. REFIO must be decoupled to DACREF with a 1µF capacitor when using the internal reference. REFIO must be buffered with an external amplifier if heavier loading is required, due to the  $10k\Omega$  series resistance.

The reference circuit employs a control amplifier designed to regulate the full-scale, differential output current, IOUTES. The output current is calculated as follows:

$$I_{OUTFS} = 32 \times I_{REF}$$

where  $I_{RFF}$  is the reference output current ( $I_{RFF}$  = V<sub>REFIO</sub>/R<sub>SET</sub>) and I<sub>OUTFS</sub> is the full-scale output current of the DAC. Using the 1.2V (typical) internal reference and  $R_{SFT}$  of 1.28k $\Omega$  results in a full-scale output current of 30mA. In general, the dynamic performance of the DAC improves with increasing full-scale current.

#### **Analog Output**

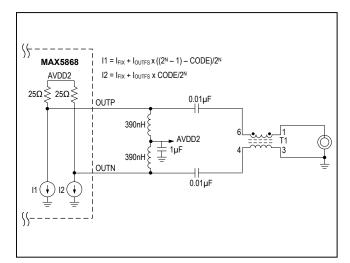

The device is a differential current-steering DAC with built-in output termination resistors. The outputs are terminated to AVDD2 providing a 50Ω differential output resistance. In addition to the signal current, a constant current sink (IFIX) equal to one half IOUTFS is connected to each differential DAC output. N = 14 and is the number

Figure 2. Reference Architecture, External Reference Configuration

of bits of resolution of the DAC core. Figure 3 shows an equivalent circuit for the internal output structure of the device. The circuit has some resistive, capacitive and inductive elements. These elements have been minimized by design in order to achieve the highest possible output bandwidth (2250MHz typical).

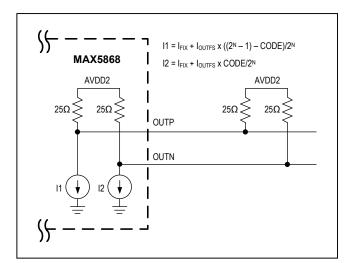

In addition, the device requires a differential external termination (i.e. double termination). This external termination can be accomplished with a differential  $50\Omega$  load or a single-ended  $50\Omega$  load interfaced through a transformer. RF chokes to the AVDD2 supply should be used with the transformer coupled output. A typical transformer coupled configuration for high-frequency operation is shown in Figure 3.

For applications where the DC information is important, the output configuration in Figure 4 can be used.  $25\Omega$ resistors to AVDD2 are required for DC coupling. The DC configuration will lower the output common-mode which may reduce performance slightly. The device is not compatible with an unterminated output when using the upper portion of the full-scale current range. Lowering the fullscale current to 20mA or less may allow use of the outputs without external terminations, though performance will be impacted in this configuration.

#### **Clock Interface**

The MAX5868 DAC is updated on the rising edge of the clock supplied to the differential high frequency clock input (CLKP/CLKN) and supports a maximum frequency of 4.96GHz. The high-frequency clock should be a balanced fully differential signal with a 50%, or near 50%, duty cycle. The clock input has internal (on-chip)  $100\Omega$

Figure 3. Typical DAC Output Configuration

differential termination. The clock inputs requires a minimum of 0dBm input power. The clock inputs must be AC-coupled to the clock source as they are self biased internally.

#### **Data Interface**

The LVDS data interface includes a 16-bit wide interleaved I/Q data input (DP[15:0]/DN[15:0]), a parity bit input (PARP/PARN), a data clock input (DCLKP/DCLKN), a synchronization input (SYNCIP/SYNCIN) and a synchronization output (SYNCOP/SYNCON). Each LVDS input is terminated internally with a differential  $100\Omega$ resistor. DC coupling is required and the logic levels must meet the requirements specified in the Electrical Characteristics table.

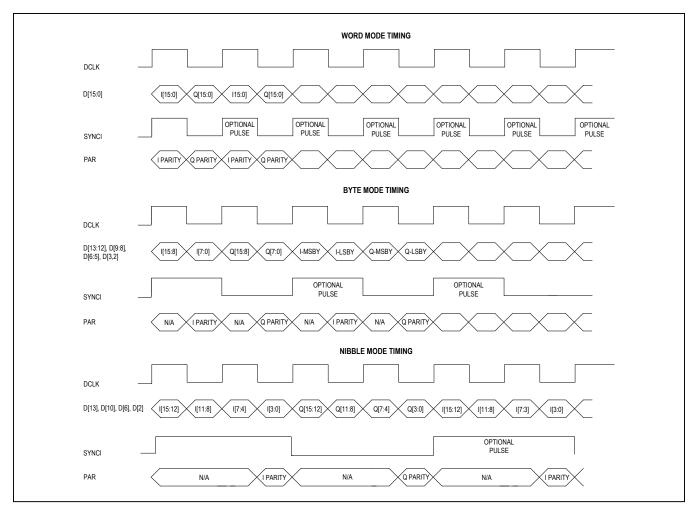

The complex, interleaved data (I and Q) is latched into the device in one of three interface configuration modes using either offset binary or two's complement data format. The three interface configuration modes are Word (16 bit), Byte (8 bit) and Nibble (4 bit) modes. Both the interface configuration modes and data format are set by programming the CfgChipOM register accessible through the SPI interface. The default is Word mode for interface configuration and offset binary for data format. Data inversion can also be user programmed for the Q-data (default is no inversion).

The data interface operates in Double Date Rate (DDR) for all interface configurations. The input data clock DCLK must be frequency locked with the DAC clock. The device outputs a LVDS divided reference clock (RCLKP/RCLKN) which is equal to 1/2 the expected input data rate (fDATA) operating in DDR. DCLK must be frequency locked to

Figure 4. Output Configuration for Low-Frequency Operation

## 16-Bit, 5Gsps Interpolating and Modulating RF DAC

RCLK; however, there are no restrictions to the relative phase of these two clock signals.

In 16-bit Word mode, each rising DCLK edge marks an I and Q interleaved data pair, which are demultiplexed into an I and Q data stream inside the chip, where a FIFO buffer allows the input data to be synchronized with the data clock DCLK.

The 8-bit Byte and 4-bit Nibble modes are provided to reduce active I/O pin count and are typically used when higher interpolation rates are used. In Byte and Nibble modes, only 8 bits or 4 bits of the input data LVDS pairs (instead of 16 LVDS pairs) are used along with the SYNCI signal, which is used to carry framing alignment information.

In all data interface configuration modes, the DCLK, DP[15:0]/DN[15:0], SYNCI, and PAR signals need to be time aligned. In Word mode, I-data is associated with the rising edge of DCLK, and Q-data is associated with the falling edge of DCLK. See Data Setup Time and Data Hold Time requirements in *Electrical Characteristics* table. The interface supports DCLK frequencies up to 620MHz. With the DDR mode, a maximum input rate 1240Mwps can be achieved for the data (I + Q). Once the data is clocked into MAX5868, the FIFO is used to match the external clock domain (DCLK) with the internal clock domain (RCLK). As stated above, DCLK must be frequency locked to RCLK. A FIFO overflow and underflow will activate interrupt register bits: one for overflow and one for underflow.

The device expects even parity and can be programmed to generate an interrupt on the INTB pin when parity errors are detected. In all modes, the parity is calculated and compared over the 16-bit data width plus the additional parity bit supplied to the PARP/PARN input. For example, an even parity means the XOR of the 16-bit data and the parity bit (17 bits total) results in a '0'. In Word mode, the SYNCI signal is not required for data frame alignment. If parity is not used, the PARP/PARN input should be a valid LVDS logic

'1' or '0' at all times. The device can also be configured to mute the DAC output when parity errors are detected.

Relative timing diagrams for the LVDS interface in Word, Byte, and Nibble modes are shown in Figure 5.

#### **Word Mode Operation**

Word mode is the default input interface. All 16 bits are used in this mode where D[15] is the MSB and D[0] is the LSB.

SYNCI is not required for framing alignment in this mode. See the <u>SYNC Functionality</u> section for further details on synchronizing multiple devices.

Parity is applied coincident with the word input, I parity with I data and Q parity with Q data.

The rising edge of DCLK captures the I-data and the falling edge of DCLK captures the Q-data. In terms of timing, the parity bit should be treated as a data bit, as it is routed the same as the data bits inside the chip.

#### **Byte Mode Operation**

Operating in the Byte mode, data is input 8 bits at a time. The data input sequence for Byte mode is: I[15-8], I[7-0], Q[15-8], Q[7-0], I[15-8], etc. The active data pins for Byte mode are: D[13] (MSB byte), D[12], D[9], D[8], D[6], D[5], D[3] and D[2] (LSB byte).

An internal counter is used to demux the input data into two separate 16-bit data busses. The internal counter is reset when a rising edge is detected on the SYNCI input. A rising edge, '0' to '1' transition should be applied to SYNCI with the first byte of the first I data word. SYNCI may be pulsed high with each new I data word, but is not required once the system is synchronized. See the <u>SYNC Functionality</u> section for further details on synchronizing multiple devices.

Parity, PARP/PARN, is captured along with the least significant byte (LSB byte). However, it may be applied with the entire word.

Figure 5. LVDS Timing

#### **Nibble Mode Operation**

Operating in the Nibble mode, data is input 4 bits at a time. The data sequence at the input pins is: I[15:12], I[11:8], I[7:4], I[3:0], Q[15:12], Q[11:8], Q[7:4], Q[3:0], I[15:12], I[11:8], etc. The active data pins for the Nibble mode are: D[13] (MSB nibble), D[10], D[6] and D[2] (LSB nibble). One nibble is captured on each edge of the DCLK signal.

An internal counter is used to demux the input data into two separate 16 bit data busses. The rising edge of the SYNCI signal is used to set the initial phase of a frame tracking counter. This counter output is used to control the data frame assembler. The counter rollover value is determined by the state of the byte and nibble mode controls. A rising edge, '0' to '1' transition should be applied to SYNCI with the first nibble of the first I data word. SYNCI may be pulsed high with each new I data word, but is not

required once the system is synchronized. See the <u>SYNC</u> <u>Functionality</u> section for further details on synchronizing multiple devices.

Parity, PARP/PARN, is captured along with the least significant nibble (LSB nibble). However, it may be applied with the entire word.

#### Interpolation Filters

Interpolation rates of 4x, 5x, 6x, 8x, 10x, 12x, 16x, 20x, and 24x are supported and are user selectable. The default rate is 10x interpolation. The interpolation filters support a maximum I+Q signal bandwidth of 504.68MHz in 16-bit Word mode when using a 4x interpolation rate ( $f_{DAC}$  = 2480Msps) or 8x interpolation rate ( $f_{DAC}$  = 4960Msps). The typical passband ripple is less than 0.1dB for all interpolation modes. The block diagram for the interpolation filter signal path is shown in Figure 6.

Figure 6. Interpolator/Modulator Block Diagram

The interpolation filters for the desired interpolation rate are programmed in the CfgDSP register accessible through the serial control interface. The DAC update rate equals the input sample rate ( $f_{S_N}$ ) multiplied by the interpolation rate. The input data rate ( $f_{DATA}$ ) is determined by the input sample rate and data format (nibble, byte, or word). The MAX5868 outputs a reference clock for use in the data generation system. The RCLKP/RCLKN outputs are LVDS signals at a frequency equal to 1/2 the expected input data rate ( $f_{DATA}$ ) operating in DDR. The RCLKP/RCLKN frequency is calculated as follows:

$$f_{RCLK} = \begin{pmatrix} f_{DAC} \\ R \end{pmatrix} \times DMode$$

where:

fRCLK = Reference clock frequency

f<sub>DAC</sub> = DAC update rate = DAC clock frequency (f<sub>CLK</sub>)

R = Programmed interpolation rate

DMode = Input data format mode

= 1 for word mode

= 2 for byte mode

= 4 for nibble mode

The data clock in the FPGA or ASIC,  $f_{DATACLK}$ , can be derived from the reference clock output of the DAC,  $f_{RCLK}$ . The relationship between the various clocks and data rates are as follows:

- f<sub>DAC</sub> = R x f<sub>S\_IN</sub> where f<sub>S\_IN</sub> = input sample rate for the interleaved complex I/Q data set

- f<sub>DATA</sub> = 2 x f<sub>S IN</sub> x DMode

• f<sub>DATACLK</sub> = f<sub>DATA</sub>/2 (DDR data) = f<sub>RCLK</sub>

There are some constraints with respect to interpolation rate, data input rates and the DAC clock frequency. These are:

- The input data rate, f<sub>DATA</sub>, must not exceed the maximum data rate frequency (1240Mwps) specified in the *Electrical Characteristics* table

- The DAC clock frequency, f<sub>CLK</sub>, must not exceed the maximum clock frequency (4960MHz) specified in the *Electrical Characteristics* table, and

- The reference clock output, f<sub>RCLK</sub>, or the data clock, f<sub>DATACLK</sub>, must not exceed the maximum frequency (620MHz) specified in the *Electrical Characteristics* table. Higher interpolation rates may be required when using byte or nibble input modes to ensure f<sub>DATACLK</sub> does not exceed 620MHz.

#### **Frequency Planning**

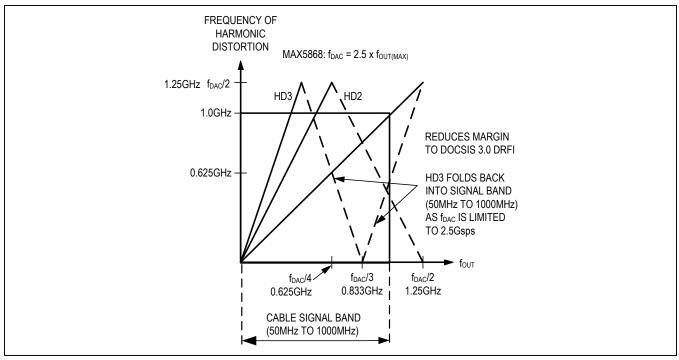

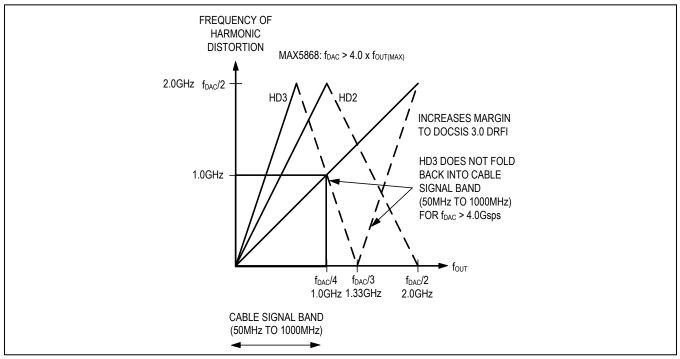

Using a DAC to generate communication transmit signals requires consideration of aliased harmonics and internally generated divided clocks. To ensure the dominant second and third order harmonics do not fold back into the signal band, the DAC update rate needs to be greater than four times the highest frequency in the band of interest.

<u>Figure 7</u> and 8 show the location of the 2nd and 3rd harmonic distortion products for the case of the DAC being updated at 2.5 times and 4 times the maximum desired frequency in the band of interest (e.g. 1000MHz for DOCSIS 3.0 DRFI).

Figure 7. Example of Incorrect Frequency Planning

Figure 8. Example of Correct Frequency Planning

#### Signal Bandwidth

The MAX5868 can generate a maximum I/Q complex signal bandwidth of 504.68MHz when operating in 16-bit Word mode at  $f_{DAC}$  = 4960Msps and 8x interpolation (or  $f_{DAC}$  = 2480Msps and 4x interpolation) for output frequencies ranging from DC to Nyquist.

The actual signal bandwidth is dependent on the input sample rate ( $f_{S\_IN}$ ), or the DAC update rate ( $f_{DAC}$ ) divided by the interpolation setting (R), and the interpolation filter passband width (PBW = 0.407, expressed as a percentage of the input sample rate). The I/Q complex DAC signal bandwidth is calculated as:

DAC Signal Bandwidth =

$$2 \times (f_{DAC}/R) \times (PBW)$$

The complex I/Q signals are converted to a real signal using a digital quadrature modulator and quadrature NCO. The real bandwidth is centered around the NCO frequency.

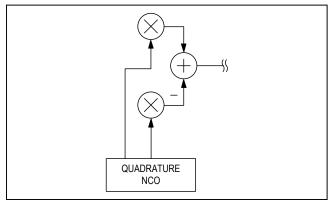

#### **Complex Modulator and NCO**

The device includes a complex modulator comprised of a complex NCO driving two multipliers followed by an adder Figure 9). The complex modulator produces the result:

$$I(n) \times COS(\omega n) - Q(n) \times SIN(\omega n)$$

where I and Q are filtered and interpolated versions of the input I-data and Q-data.

The complex NCO can synthesize a frequency in the range from 0Hz to  $f_{DAC}/2$  using a 33-bit phase accumulator. The synthesized frequency is calculated as follows:

$$f_{NCO} = \frac{FCW\_full}{2^{33}} \times f_{DAC}$$

Figure 9. Complex NCO and Modulator

FCW\_full is the rational value of the frequency control word. A unique feature of the MAX5868 NCO is that the frequency can be programmed with either an integer or with rational values that provide increased NCO resolution. The value of FCW\_full is stored in three variables as shown here.

$$FCW_full = FCW + \frac{NFW}{DFW}$$

where:

FCW\_full is the full resolution frequency control word FCW is the integer portion of FCW full

NFW is the numerator of the rational portion of FCW\_full DFW is the denominator of the rational portion of FCW\_full FCW\_full is calculated as:

$$FCW_full = f_{NCO} \times \frac{2^{33}}{f_{DAC}}$$

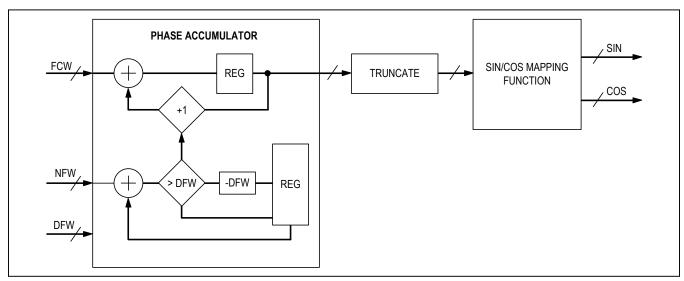

The default values for NFW (0) and DFW (1) allow the NCO to work like a standard integer NCO with frequency control word FCW. The NCO block diagram is shown in Figure 10.

For general usage, FCW, NFW, and DFW are calculated as follows:

- 1) Compute FCW full as shown above

- 2) Set FCW = the integer portion of FCW full

- 3) Set FCW Remain = FCW full FCW

- 4) Calculate NFW = round(FCW Remainder x 2<sup>18</sup> -1)

- 5) Calculate DFW = round(NFW/FCW\_Remainder)

- If desired, NFW and DFW can be reduced at this point

#### Example:

Assume  $f_{DAC}$  = 4960MHz,  $f_{NCO}$  = 1023MHz, then

1) FCW\_full =

$$1023MHz \times \frac{2^{33}}{4960MHz} = 1771674009.6$$

- 2) FCW = floor(FCW full) = 1771674009

- 3) FCW\_Remainder = FCW\_full FCW = 0.6

- 4) NFW =  $0.6 \times (2^{18} 1) = \text{round} (157285.8) = 157286$

- 5) DFW = NFW/FCW\_Remainder = 157286/0.6 = round(262143.3333) = 262143

Figure 10. NCO Block Diagram

#### Verify:

- 1) FCW\_full = FCW + NFW/DFW = 1771674009 + 157286/262143 = 1771674009.6000008

- 2)  $f_{NCO}$ =FCW\_full/2<sup>33</sup>xf<sub>DAC</sub>=1771674009.6000008/2<sup>33</sup> x 4960MHz = 1023.000MHz

In many communication applications the DAC is updated at a frequency which is a multiple of 10.24MHz allowing the NCO frequency to be set on an exact 1Hz, 10Hz, 10Hz, 1kHz, or 10kHz grid. To determine the required FCW, NFW, and DFW values to accomplish this, use the following procedure: