#### **General Description**

The MAX5882 14-bit, 4.6Gsps digital-to-analog converter (DAC) is designed for direct RF synthesis of multicarrier quadrature amplitude modulation (QAM) signals in cable modem termination systems (CMTS) and edge QAM (EQAM) devices. The DAC features excellent spurious, noise, and adjacent-channel power (ACP) performance, and directly synthesizes multiple carriers in the 47MHz to 1003MHz cable downstream band, as defined by the Data-Over-Cable Service Interface Specification (DOCSISM). The 4.6Gsps update rate allows digital generation of signals with more than 2GHz bandwidth.

The device has four 14-bit, multiplexed, low-voltage differential signaling (LVDS) input ports that each operate at up to 1150Mwps in double data rate (DDR) or single data rate (SDR) mode. The inputs also accept differential high-speed transceiver logic (DHSTL) input levels. The device accepts a clock at 1/2 the DAC update rate, as conversion is triggered on both rising and falling clock edges. The input data rate on each port is 1/4 the DAC update rate or 1/2 of the clock rate. The device contains a delay-locked loop (DLL) that simplifies the interface to FPGA or ASIC devices. Using the DLL, the phase of the output clock (DATACLK) is adjusted to ensure that the input LVDS data bus has the proper timing relationship to the on-chip clock used to latch the data.

The device is a current-steering DAC with an integrated 50I differential output termination to ensure optimum dynamic performance. Operating from 3.3V and 1.8V power supplies, the device consumes 2.3W at 4.6Gsps. The device is specified over the extended temperature range (-40NC to +85NC) and is offered in a 256 CSBGA lead(Pb)-free/RoHS-compliant package.

#### **Applications**

- DOCSIS-Compliant Edge QAM Devices

- Cable Modem Termination Systems (CMTS)

- Broadcast Video Modulators

- Video-On-Demand (VOD)

- Coax Media Converters

- Remote PHY

DOCSIS is a registered trademark of Cable Television Laboratories, Inc. (CableLabs $^{\ensuremath{\$}}$ )

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

#### **Features**

- 4.6Gsps Output Update Rate

- Direct RF Synthesis from 47MHz to 1003MHz

- No Aliasing of HD3 into Cable Band

- Industry-Leading DOCSIS 3.0 Performance Noise

Floor

- -70dBc at four = 900MHz, 8 Channel (256 QAM)

- -66dBc at four = 900MHz, 16 Channel (256 QAM)

- -62dBc at four = 900MHz, 32 Channel (256 QAM)

- -57dBc at four = 500MHz, 128 Channel (256 QAM)

- High Output Power 9dBm (CW)

Enables Low Solution Power

- 4:1 Multiplexed LVDS Inputs

- Up to 1150Mwps Each Port

- Double Data Rate (DDR) Mode

- On-Chip DLL for Input Data Synchronization

- Parity Error Flag

- Internal 50Ω Differential Output Termination

- Input Register Scan Mode

- Compact 17mm x 17mm, 256 CSBGA Package

- Evaluation Kit Available (Order MAX5882EVKIT+)

#### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX5882EXF+D | -40°C to +85°C | 256 CSBGA   |

+Denotes a lead(Pb)-free/RoHS-compliant package. D = Dry pack.

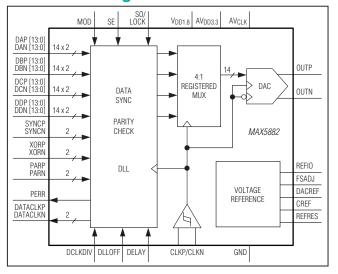

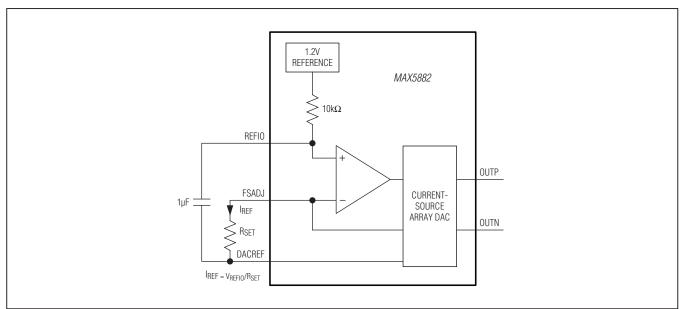

#### **Functional Diagram**

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

#### **Absolute Maximum Ratings**

| $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                |

|---------------------------------------------------------------------------------------------------------------------|

| OUTP, OUTN to GND, DACREF0.3V to AV <sub>DD3.3</sub> + 1.0V<br>CREF to GND, DACREF0.3V to V <sub>DD1.8</sub> + 0.3V |

| SE, DCLKDIV, DLLOFF, MOD, DELAY,                                                                                    |

| REFRES TO GND, DACREF0.3V to AV <sub>DD3.3</sub> + 0.3V                                                             |

| CLKP, CLKN to GND, DACREF0.3V to AV <sub>CLK</sub> + 0.3V                                                           |

| DAP0–DAP13, DBP0–DBP13, DCP0–DCP13 to GND,                                                                          |

| DACREF0.3V to V <sub>DD1.8</sub> + 0.3V                                                                             |

| DDP0–DDP13, XORP, SYNCP, PARP to GND,                                                                               |

| DACREF0.3V to V <sub>DD1.8</sub> + 0.3V                                                                             |

| DAN0–DAN13, DBN0–DBN13, DCN0–DCN13 to GND,                                                                          |

| DACREF0.3V to V <sub>DD1.8</sub> + 0.3V                                                                             |

DDN0-DDN13, XORN, SYNCN, PARN to GND,

| DACREF0.3V to V <sub>DD1.8</sub> + 0.3V                       |

|---------------------------------------------------------------|

| DATACLKP, DATACLKN to GND,                                    |

| DACREF0.3V to V <sub>DD1.8</sub> + 0.3V                       |

| SO/LOCK, PERR to GND, DACREF0.3V to V <sub>DD1.8</sub> + 0.3V |

| SO/LOCK, PERR Continuous Current                              |

| DATACLKP, DATACLKN Continuous Current8mA                      |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )         |

| 256 CSBGA (derate 38.6mW/°C above +70°C)3088.8mW              |

| Operating Temperature Range40°C to +85°C                      |

| Junction Temperature+150°C                                    |

| Storage Temperature Range65°C to +150°C                       |

| Soldering Temperature (reflow)+260°C                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

| PARAMETER                           | SYMBOL           | CONDITIONS                                                                                | MIN     | ТҮР    | MAX  | UNITS |  |

|-------------------------------------|------------------|-------------------------------------------------------------------------------------------|---------|--------|------|-------|--|

| STATIC PERFORMANCE                  |                  |                                                                                           |         |        |      |       |  |

| Resolution                          |                  |                                                                                           |         | 14     |      | Bits  |  |

| Full-Scale Output Current Range     | IOUT             | (Note 2)                                                                                  | 10      |        | 80   | mA    |  |

| Output-Power Gain Error             | GE               |                                                                                           | -0.7    |        | +0.7 | dB    |  |

| Output Down Drift                   |                  | Internal reference                                                                        |         | -0.003 |      |       |  |

| Output-Power Drift                  |                  | External reference                                                                        | -0.0025 |        |      | dB/°C |  |

| Full-Scale Output Power             | Pout             | Differential, into 50Ω load,<br>f <sub>OUT</sub> = 103.5MHz, f <sub>DAC</sub> = 4.608Gsps |         | 9      |      | dBm   |  |

| Output Resistance                   | R <sub>OUT</sub> | Differential                                                                              |         | 50     |      | Ω     |  |

| DYNAMIC PERFORMANCE (Note 3         | ·                | ·                                                                                         |         |        |      |       |  |

| Minimum Clock Rate f <sub>CLK</sub> |                  |                                                                                           |         |        | 10   | MHz   |  |

| Maximum Clock Rate                  | fCLK             | 2304                                                                                      |         |        | MHz  |       |  |

| Minimum Output Update Rate          | fDAC             | 20                                                                                        |         |        |      | Msps  |  |

| Maximum Output Update Rate          | fDAC             |                                                                                           | 4608    |        |      | Msps  |  |

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

### **Electrical Characteristics (continued)**

| PARAMETER                                                                      | SYMBOL             |                                                                 | MIN                                                                                              | TYP | MAX     | UNITS |     |  |

|--------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----|---------|-------|-----|--|

|                                                                                |                    |                                                                 | Adjacent channel (750kHz from<br>channel block edge to 6MHz<br>from channel block edge)          |     | -71 -64 |       |     |  |

|                                                                                |                    | f <sub>OUT</sub> =<br>400MHz,<br>f <sub>DAC</sub> =             | Next-adjacent channel (6MHz<br>from channel block edge to<br>12MHz from channel block<br>edge)   |     | -73     | -66   |     |  |

|                                                                                |                    | 4608Msps                                                        | Third-adjacent channel<br>(12MHz from channel block<br>edge to 18MHz from channel<br>block edge) |     | -73     | -66   |     |  |

|                                                                                |                    |                                                                 | Noise in any other channel (Note 4)                                                              |     | -73     |       |     |  |

|                                                                                |                    | f <sub>OUT</sub> =<br>860MHz,<br>f <sub>DAC</sub> =<br>4608Msps | Adjacent channel (750kHz from<br>channel block edge to 6MHz<br>from channel block edge)          |     | -67     |       |     |  |

| Out-of-Band Noise and<br>Spurious, Eight 6MHz QAM Chan-<br>nels, Average Total |                    |                                                                 | Next-adjacent channel (6MHz<br>from channel block edge to<br>12MHz from channel block<br>edge)   |     | -66     |       | dBc |  |

| Power = -10dBFS                                                                |                    |                                                                 | Third-adjacent channel<br>(12MHz from channel block<br>edge to 18MHz from channel<br>block edge) |     | -66     |       |     |  |

|                                                                                |                    |                                                                 | Noise in any other channel (Note 4)                                                              |     | -65     |       |     |  |

|                                                                                |                    |                                                                 | Adjacent channel (750kHz from<br>channel block edge to 6MHz<br>from channel block edge)          |     | -67     |       |     |  |

|                                                                                | f <sub>DAC</sub> = | 1000MHz,                                                        | Next-adjacent channel (6MHz<br>from channel block edge to<br>12MHz from channel block<br>edge)   |     | -67     |       |     |  |

|                                                                                |                    | 4608Msps                                                        | Third-adjacent channel<br>(12MHz from channel block<br>edge to 18MHz from channel<br>block edge) |     | -67     |       |     |  |

|                                                                                |                    |                                                                 | Noise in any other channel (Note 4)                                                              |     | -66     |       |     |  |

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

### **Electrical Characteristics (continued)**

| PARAMETER                                        | SYMBOL              |                                        | MIN                                                        | ТҮР                                                  | MAX              | UNITS       |      |        |

|--------------------------------------------------|---------------------|----------------------------------------|------------------------------------------------------------|------------------------------------------------------|------------------|-------------|------|--------|

| Harmonic Distortion, Block<br>of Four 6MHz QAM   |                     | f <sub>OUT</sub> =<br>300MHz,          | nels coincio                                               | eight 6MHz chan-<br>ling with<br>nic components      |                  | -72         | -64  | dPo    |

| Channels, Average Total<br>Power = -10dBFS       |                     | f <sub>DAC</sub> =<br>4.6Gsps          |                                                            | welve 6MHz chan-<br>ling with 3rd-har-<br>ponents    |                  | -72         | -65  | - dBc  |

| Gain Flatness                                    | GF                  | Over any                               | single 6MHz ch                                             | annel                                                |                  | 0.05        |      | dB     |

| Gailt Flattless                                  | Gi                  | Within 47                              | MHz to 1003MH                                              | Iz band                                              |                  | 1.6         |      | ub .   |

| Clock Spurs                                      |                     | f <sub>DAC</sub> = 4.0<br>QAM cha      | 6Gsps, eight<br>nnels                                      | f <sub>DAC</sub> /4 spur<br>f <sub>DAC</sub> /8 spur |                  | -80<br>-100 |      | dBm    |

| f <sub>DAC</sub> /2 - f <sub>OUT</sub> Image     |                     |                                        | 6Gsps, eight QA<br>from 952MHz to                          | M channels covering<br>1000MHz                       |                  | -40         |      | dBc    |

| f <sub>DAC</sub> /2 - 2f <sub>OUT</sub> Spurious |                     |                                        | 6Gsps, eight QA<br>from 952MHz to                          | M channels covering<br>1000MHz                       |                  | -64         |      | dBc    |

| REFERENCE                                        |                     |                                        |                                                            |                                                      |                  |             |      |        |

| Internal Reference Voltage Range                 | V <sub>REFIO</sub>  |                                        |                                                            |                                                      | 1.1              | 1.2         | 1.3  | V      |

| Reference Input-Voltage Compli-<br>ance Range    | V <sub>REFIOR</sub> |                                        |                                                            |                                                      | 0.5              |             | 1.8  | V      |

| Reference Input Resistance                       | R <sub>REFIO</sub>  |                                        |                                                            |                                                      |                  | 10          |      | kΩ     |

| Reference Voltage Drift                          | TCO <sub>REF</sub>  |                                        |                                                            |                                                      |                  | 50          |      | ppm/°C |

| ANALOG OUTPUT TIMING                             |                     |                                        |                                                            |                                                      |                  |             |      |        |

| Output Fall Time                                 | t <sub>FALL</sub>   | 90% to 10% (Note 5)                    |                                                            |                                                      |                  | 300         |      | ps     |

| Output Rise Time                                 | t <sub>RISE</sub>   | 10% to 90                              | 0% (Note 5)                                                |                                                      |                  | 300         |      | ps     |

| Settling Time                                    | t <sub>S</sub>      | Settling to<br>Settling to             |                                                            |                                                      |                  | 1<br>2.5    |      | - ns   |

| Output Bandwidth                                 | BW                  | (Note 6)                               |                                                            |                                                      |                  | 2.0         |      | GHz    |

| Output Propagation Delay                         | t <sub>PD</sub>     | (Note 7)                               |                                                            |                                                      |                  | 1.5         |      | ns     |

|                                                  |                     | , ,                                    | ]/DAN[13:0] to (                                           | output                                               |                  | 11.5        |      |        |

|                                                  |                     |                                        | /DBN[13:0] to (                                            |                                                      | 12<br>12.5<br>13 |             |      | Clock  |

| Output Data Latency                              | t <sub>DL</sub>     | -                                      | ]/DCN[13:0] to                                             |                                                      |                  |             |      | Cycles |

|                                                  |                     |                                        | )/DDN[13:0] to                                             |                                                      |                  |             |      | 1      |

| TIMING CHARACTERISTICS                           |                     |                                        |                                                            | ·                                                    |                  |             |      |        |

|                                                  |                     |                                        | DLLOFF = Low                                               | , DELAY = High                                       | 1075             |             | 1152 |        |

|                                                  |                     | I –                                    |                                                            | LLOFF = Low, DELAY = Open                            |                  |             | 1075 | 1      |

|                                                  |                     |                                        | DLLOFF = Low, DELAY = Open950DLLOFF = Open, DELAY = Low825 |                                                      | 825              |             | 950  | 1      |

|                                                  | £                   | f <sub>DLL</sub> =                     | f <sub>DLL</sub> = DLLOFF = Open, DELAY = High 700         |                                                      |                  |             | 825  |        |

| DLL Frequency Range                              | fDLL                | f <sub>CLK</sub> /2 DLLOFF = Open, DEL |                                                            | n, DELAY = Open                                      | 625              |             | 700  | - MHz  |

|                                                  |                     |                                        | DLLOFF = Res                                               | , DELAY = Low                                        | 550              |             | 625  | 1      |

|                                                  |                     | DLLOFF = Res, DELAY = High             |                                                            |                                                      | 475              |             | 550  | 1      |

|                                                  |                     |                                        | DLLOFF = Res,                                              | DELAY = Open                                         | 400              |             | 475  | 1      |

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

#### **Electrical Characteristics (continued)**

| PARAMETER                      | SYMBOL                       | CONDITION                                                                                                                                     | IS                                                                 | MIN   | TYP | MAX                     | UNITS                   |

|--------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------|-----|-------------------------|-------------------------|

| Input Data Skew vs. SYNC       |                              | Allowed skew of any<br>LVDS inputs (DAP[13:0]/<br>DAN[13:0], DBP[13:0]/<br>DBN[13:0], DCP[13:0]/<br>DCN[13:0], DDP[13:0]/<br>DDN[13:0], XORP/ | T <sub>A(MIN)</sub> = 0°C,<br>T <sub>J(MAX)</sub> =<br>+110°C      | -324  |     | +307                    |                         |

|                                | <sup>t</sup> skew            | XORN, and PARP/<br>PARN), with respect to<br>the SYNC input; this<br>parameter only applies<br>when DLLOFF is not<br>driven high (Note 8)     | T <sub>A(MIN)</sub> =<br>-40°C,<br>T <sub>J(MAX)</sub> =<br>+110°C | -300  |     | +300                    | ps                      |

|                                |                              | DLLOFF = 1.8V; data<br>on the LVDS input<br>pins must be stable for<br>tSETUP before the next                                                 | T <sub>A(MIN)</sub> = 0°C,<br>T <sub>J(MAX)</sub> =<br>+110°C      | 1.52  |     |                         |                         |

| Input Data to Clock Setup Time | <sup>t</sup> SETUP           | edge of DATACLKP/<br>DATACLKN; this param-<br>eter only applies when<br>DLLOFF is driven high<br>(Note 8)                                     | T <sub>A(MIN)</sub> =<br>-40°C,<br>T <sub>J(MAX)</sub> =<br>+110°C | 1.53  |     |                         | ns                      |

|                                |                              | DLLOFF = 1.8V; data on<br>the LVDS input pins must<br>remain stable for t <sub>HOLD</sub>                                                     | T <sub>A(MIN)</sub> = 0°C,<br>T <sub>J(MAX)</sub> =<br>+110°C      | -0.85 |     |                         |                         |

| Input Data to Clock Hold Time  | <sup>t</sup> HOLD            | after an edge of DATA-<br>CLKP/DATACLKN; this<br>parameter only applies<br>when DLLOFF is driven<br>high (Note 8)                             | T <sub>A(MIN)</sub> =<br>-40°C,<br>T <sub>J(MAX)</sub> =<br>+110°C | -0.9  |     |                         | ns                      |

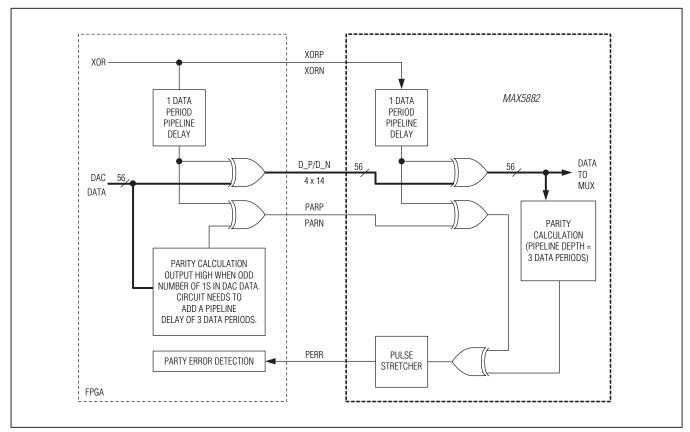

| Parity Error Pulse Width       | terr                         | Pulse width of PERR when is detected                                                                                                          | n a parity error                                                   |       | 48  |                         | Data<br>Clock<br>Cycles |

| Parity Pipeline Delay          | <sup>t</sup> PIPE,<br>PARITY | Pipeline delay in the internal parity calcu-<br>lation; delay the incoming PARP/PARN bit<br>by this amount                                    |                                                                    | 3     |     | 3                       | Data<br>Clock<br>Cycles |

| XOR Pipeline Delay             | <sup>t</sup> PIPE,<br>XOR    | Pipeline delay in the XOR incoming XORP/XORN bit                                                                                              | 1                                                                  |       | 1   | Data<br>Clock<br>Cycles |                         |

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

### **Electrical Characteristics (continued)**

| PARAMETER                          | SYMBOL              | CONDITIONS                                                                        | MIN                                     | TYP     | MAX                                     | UNITS      |

|------------------------------------|---------------------|-----------------------------------------------------------------------------------|-----------------------------------------|---------|-----------------------------------------|------------|

|                                    |                     | N[13:0], DBP[13:0], DBN[13:0], DCP[13:0],                                         | DCN[13:0                                | ], DDP[ | 13:0], DDI                              | N[13:0],   |

| XORP, XORN, PARP, PARN, S          |                     | SPECIFIED FOR LVDS INPUT                                                          | 1                                       |         |                                         |            |

| Differential Input Logic-High      | VIH                 |                                                                                   | 100                                     |         |                                         | mV         |

| Differential Input Logic-Low       | VIL                 |                                                                                   |                                         |         | -100                                    | mV         |

| Input Common-Mode Voltage<br>Range | V <sub>COM</sub>    |                                                                                   | 1.125                                   |         | 1.375                                   | V          |

| Differential Input Resistance      | R <sub>IN</sub>     |                                                                                   | 85                                      | 107     | 125                                     | Ω          |

| Input Capacitance                  | C <sub>IN</sub>     |                                                                                   |                                         | 1.5     |                                         | pF         |

|                                    |                     | N[13:0], DBP[13:0], DBN[13:0], DCP[13:0],<br>SPECIFIED FOR DIFFERENTIAL-HSTL INPU |                                         | ], DDP[ | 13:0], DDI                              | N[13:0],   |

| Differential Input Logic-High      | V <sub>IH(DC)</sub> |                                                                                   | 160                                     |         |                                         | mV         |

| Differential Input Logic-Low       | V <sub>IL(DC)</sub> |                                                                                   |                                         |         | -160                                    | mV         |

| Input Common-Mode Voltage<br>Range | V <sub>COM</sub>    |                                                                                   | 0.456                                   |         | 1.0                                     | V          |

| Differential Input Resistance      | R <sub>IN</sub>     |                                                                                   | 85                                      | 107     | 125                                     | Ω          |

| Input Capacitance                  | C <sub>IN</sub>     |                                                                                   |                                         | 1.5     |                                         | pF         |

| 1.8V CMOS LOGIC INPUTS (D          | CLKDIV, SE, MO      | D)                                                                                |                                         |         |                                         |            |

| Input Logic-High                   | V <sub>IH1.8</sub>  |                                                                                   | 0.7 x<br>V <sub>DD1.8</sub>             |         |                                         | V          |

| Input Logic-Low                    | V <sub>IL1.8</sub>  |                                                                                   |                                         |         | 0.3 x<br>V <sub>DD1.8</sub>             | V          |

| Input Leakage Current              | I <sub>IN1.8</sub>  |                                                                                   | -5                                      |         | +5                                      | μ <b>A</b> |

| Input Capacitance                  | C <sub>IN1.8</sub>  |                                                                                   |                                         | 3       |                                         | pF         |

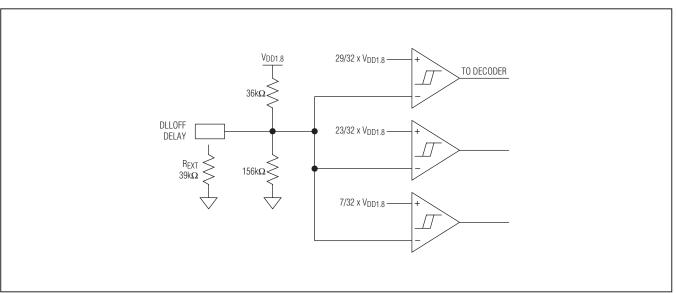

| <b>1.8V 4-LEVEL LOGIC INPUTS</b>   | (DLLOFF, DELA)      | Y)                                                                                |                                         |         |                                         |            |

| Input 4-Level Logic-Open           | V <sub>OC4</sub>    |                                                                                   | 23/32 x<br>V <sub>DD1.8</sub><br>+ 50mV |         | 29/32 x<br>V <sub>DD1.8</sub><br>- 50mV | V          |

| Input 4-Level Logic-Res            | V <sub>RC4</sub>    |                                                                                   | 7/32 x<br>V <sub>DD1.8</sub><br>+ 50mV  |         | 23/32 x<br>V <sub>DD1.8</sub><br>- 50mV | V          |

| Input 4-Level Logic-High           | V <sub>IH4</sub>    |                                                                                   | 29/32 x<br>V <sub>DD1.8</sub><br>+ 50mV |         | V <sub>DD1.8</sub>                      | V          |

| Input 4-Level Logic-Low            | V <sub>IL4</sub>    |                                                                                   | 0                                       |         | 7/32 x<br>V <sub>DD1.8</sub><br>- 50mV  | V          |

| Input Pullup Current               | I <sub>PU4</sub>    |                                                                                   | 8                                       | 11.3    | 15                                      | μ <b>A</b> |

| Input Pulldown Current             | I <sub>PD4</sub>    |                                                                                   | 32                                      |         | 64                                      | μ <b>A</b> |

| Input Capacitance                  | C <sub>IN4</sub>    |                                                                                   |                                         | 3       |                                         | pF         |

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

#### **Electrical Characteristics (continued)**

| PARAMETER                                             | PARAMETER SYMBOL CONDITIONS     |                                                                                                         |                             |                      |       | UNITS |

|-------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------|----------------------|-------|-------|

| 1.8V CMOS LOGIC OUTPUTS                               | (SO/LOCK, PER                   | R)                                                                                                      |                             |                      |       |       |

| Output Logic-High                                     | V <sub>OH1.8</sub>              | I <sub>SOURCE</sub> = 200µA                                                                             | V <sub>DD1.8</sub> -<br>0.2 |                      |       | V     |

| Output Logic-Low                                      | V <sub>OL1.8</sub>              | I <sub>SINK</sub> = 200μA                                                                               |                             |                      | 0.2   | V     |

| 1.8V LVDS OUTPUTS (DATAC                              | LKP, DATACLK                    | N)                                                                                                      |                             |                      |       |       |

| Differential Swing                                    | V <sub>DIFF, LVDS</sub>         | $V_{DIFF,LVDS} = V_{DATACLKP} - V_{DATACLKN}$ with 100 $\Omega$ differential termination                | ±250                        | ±350                 | ±450  | mV    |

| Output Rise and Fall Time                             | t <sub>R</sub> , t <sub>F</sub> | With $100\Omega$ differential termination                                                               |                             | 0.3                  |       | ns    |

| Common-Mode Voltage                                   | V <sub>COM, LVDS</sub>          |                                                                                                         | 1.125                       | 1.28                 | 1.375 | V     |

| CLOCK INPUTS (CLKP, CLKN                              | )                               |                                                                                                         |                             |                      |       |       |

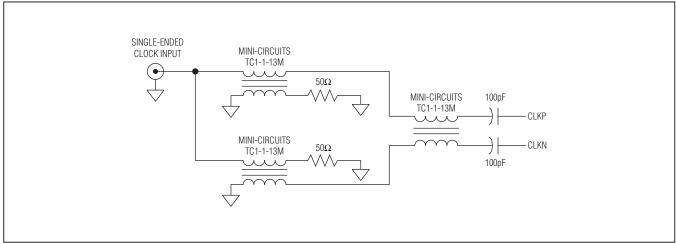

| Minimum Clock Input Power                             | P <sub>CLK</sub> , MIN          | (Note 9)                                                                                                |                             | 6                    |       | dBm   |

| Maximum Clock Input Power P <sub>CLK, MAX</sub> Power |                                 | Power measured into the MAX5882 clock input with $100\Omega$ external differential termination resistor | 12                          |                      |       | dBm   |

| Common-Mode Voltage                                   | VCOMCLK                         | Input is self-biased                                                                                    |                             | AV <sub>CLK</sub> /3 |       | V     |

| Input Resistance                                      | R <sub>CLK</sub>                | Differential                                                                                            |                             | 100                  |       | Ω     |

| Input Capacitance                                     | C <sub>CLK</sub>                |                                                                                                         |                             | 2                    |       | pF    |

| POWER SUPPLIES                                        |                                 |                                                                                                         |                             |                      |       |       |

| Analog Supply Voltage Range                           | AV <sub>DD3.3</sub>             |                                                                                                         | 3.2                         | 3.3                  | 3.5   | V     |

| 1.8V Supply Voltage Range                             | V <sub>DD1.8</sub>              |                                                                                                         | 1.7                         | 1.8                  | 1.9   | V     |

| Clock Supply Voltage Range                            | AV <sub>CLK</sub>               |                                                                                                         | 1.7                         | 1.8                  | 1.9   | V     |

| Analog Supply Current                                 | I <sub>AVDD3.3</sub>            | f <sub>DAC</sub> = 4608Msps, f <sub>OUT</sub> = 400MHz,<br>8-channel QAM (Note 3)                       |                             | 335                  | 360   | mA    |

| 1.8V Supply Current                                   | I <sub>VDD1.8</sub>             | f <sub>DAC</sub> = 4608Msps, f <sub>OUT</sub> = 400MHz,<br>8-channel QAM (Note 3)                       |                             | 250                  | 290   | mA    |

| Clock Supply Current                                  | IAVCLK                          | f <sub>DAC</sub> = 4608Msps, f <sub>OUT</sub> = 400MHz,<br>8-channel QAM (Note 3)                       |                             | 440                  | 500   | mA    |

| Power Dissipation                                     | P <sub>DISS</sub>               | f <sub>DAC</sub> = 4608Msps, f <sub>OUT</sub> = 400MHz,<br>8-channel QAM (Note 3)                       |                             | 2.3                  | 2.6   | W     |

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

#### **Electrical Characteristics (continued)**

$(V_{AVDD3.3} = 3.3V, V_{DD1.8} = V_{AVCLK} = 1.8V, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, V_{MOD} = V_{DCLKDIV} = V_{DLLOFF} = 0V, V_{DELAY} = 1.8V, R_{REFRES} = 500\Omega$ , transformer-coupled differential output,  $T_{A(MIN)} = -40^{\circ}$ C,  $T_{J(MAX)} = +110^{\circ}$ C, unless otherwise noted. Typical values are at  $T_{J} = +65^{\circ}$ C.) (Note 1)

- Note 1: All specifications are guaranteed via test at T<sub>J</sub> = +65°C and T<sub>J</sub> = +110°C to an accuracy of ±15°C, unless otherwise noted. Specifications at T<sub>J</sub> < +65°C are guaranteed by design and characterization. Timing specifications are guaranteed by design and characterization.

- Note 2: Nominal full-scale current I<sub>OUT</sub> = 128 x I<sub>REF</sub>.

- **Note 3:** CLK input = +9dBm, AC-coupled sine wave.

- Note 4: Excludes clock, clock images, f<sub>DAC</sub>/2 f<sub>OUT</sub>, and f<sub>DAC</sub>/2 2f<sub>OUT</sub> spurs, which are specified separately.

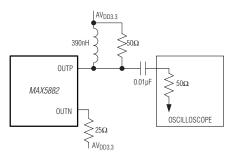

- **Note 5:** Measured single-ended into a double-terminated  $50\Omega$  load.

- Note 6: Excludes impulse-response dependent rolloff inherent in the DAC.

- Note 7: Referenced to rising edge of DAC update clock-excludes data latency.

- Note 8: Guaranteed by design and characterization.

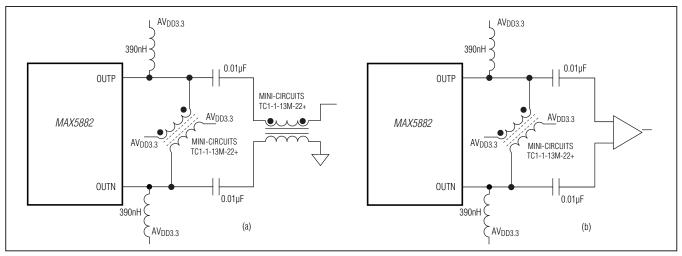

- **Note 9:** Transformer-coupled clock input (Figure 4).

#### **Thermal Characteristics**

| PARAMETER                                 | SYMBOL         | CONDITIONS    | MIN  | ТҮР  | MAX  | UNITS |  |

|-------------------------------------------|----------------|---------------|------|------|------|-------|--|

| Ambient Temperature                       | T <sub>A</sub> | (Note 10)     | -40  |      | +85  | °C    |  |

| Junction Temperature                      | ТJ             |               | -40  |      | +110 | °C    |  |

| Thermal Resistance, Junction-             | 0              | Air flow 0m/s |      | 31.9 |      | °C/M  |  |

| to-Ambient (Note 10)                      | $\theta_{JA}$  | Air flow 1m/s |      | 27.7 |      | °C/W  |  |

| Thermal Resistance, Junction-<br>to-Case  | θJC            |               |      | 3.4  |      | °C/W  |  |

| Thermal Resistance, Junction-<br>to-Board | $\theta_{JB}$  |               |      | 24   |      | °C/W  |  |

| Thermal Characterization                  |                | Air flow 0m/s |      | 25.5 |      | °C/M  |  |

| Parameter, Junction-to-Board              | ΨJB            | Air flow 1m/s | 23.7 |      |      | °C/W  |  |

| Thermal Characterization                  | ))( .=         | Air flow 0m/s |      | 8.1  |      | °C/W  |  |

| Parameter, Junction-to-Top                |                | Air flow 1m/s |      | 1.7  | /W   |       |  |

Note 10: The package is mounted on a four-layer JEDEC-standard test board, dissipating maximum power.

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

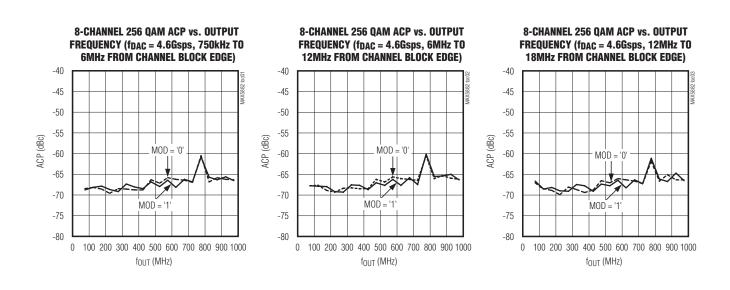

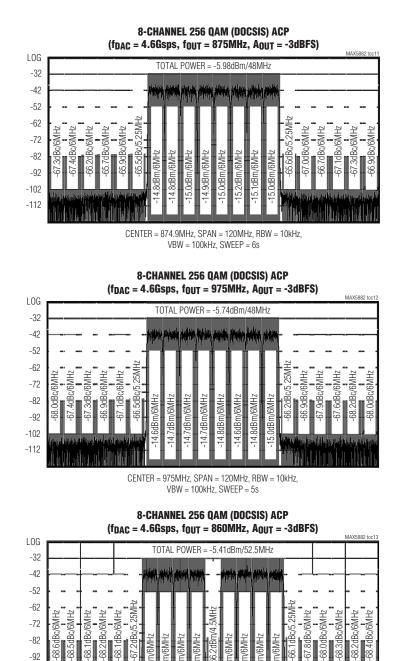

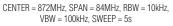

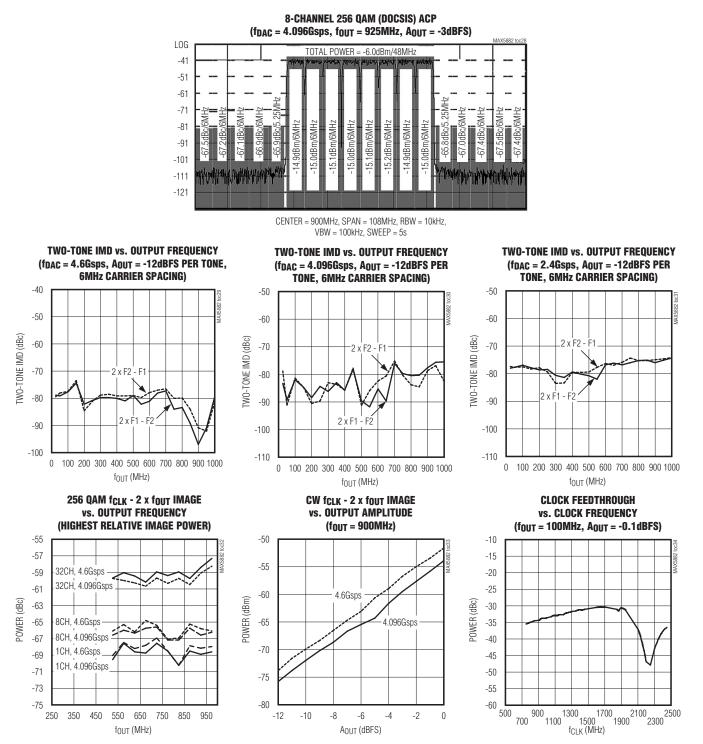

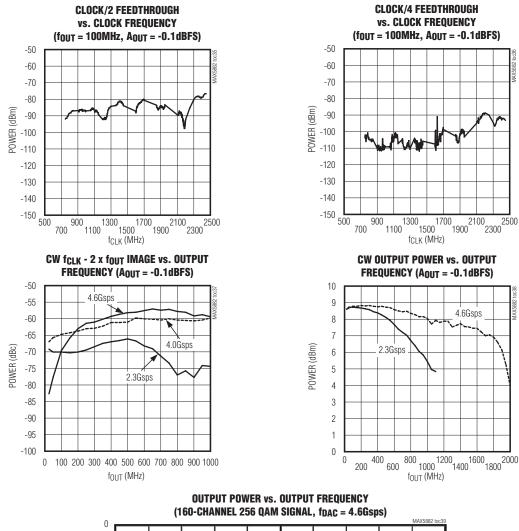

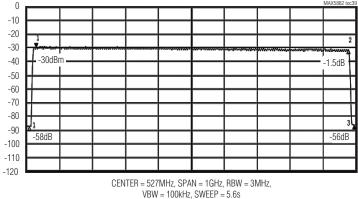

#### **Typical Operating Characteristics**

$(V_{AVDD3.3} = 3.3V, V_{DD1.8} = V_{AVCLK} = 1.8V, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, V_{MOD} = V_{DCLKDIV} = V_{DLLOFF} = 0V, V_{DELAY} = 1.8V, R_{REFRES} = 500\Omega$ , transformer-coupled differential output, tested at T<sub>J</sub> = +60°C, unless otherwise noted.)

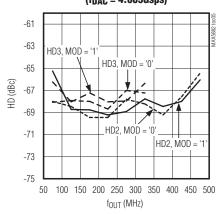

#### 8-CHANNEL 256 QAM HARMONIC DISTORTION vs. OUTPUT FREQUENCY (fdac = 4.605Gsps)

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

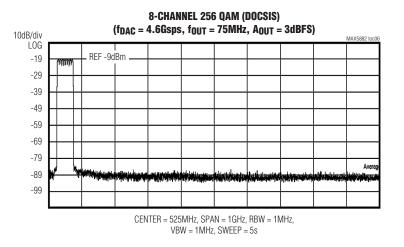

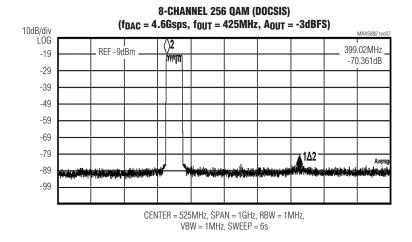

### **Typical Operating Characteristics (continued)**

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

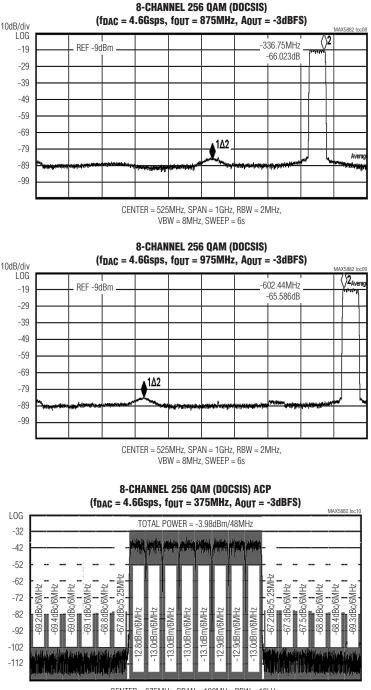

### **Typical Operating Characteristics (continued)**

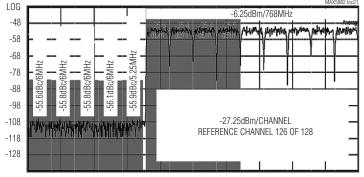

CENTER = 375MHz, SPAN = 120MHz, RBW = 10kHz, VBW = 100kHz, SWEEP = 5s

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

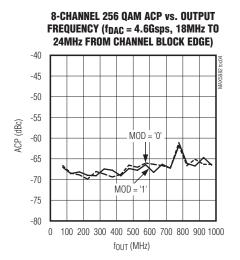

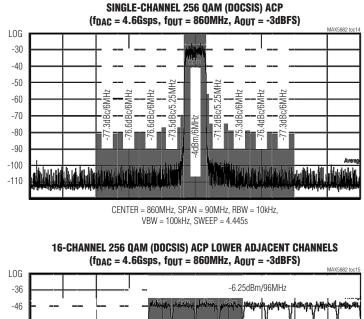

#### **Typical Operating Characteristics (continued)**

$(V_{AVDD3.3} = 3.3V, V_{DD1.8} = V_{AVCLK} = 1.8V, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, V_{MOD} = V_{DCLKDIV} = V_{DLLOFF} = 0V, V_{DELAY} = 1.8V, R_{REFRES} = 500\Omega$ , transformer-coupled differential output, tested at T<sub>J</sub> = +60°C, unless otherwise noted.)

CENTER = 860MHz, SPAN = 126MHz, RBW = 10kHz,

VBW = 100kHz, SWEEP = 5s

-102 -112

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

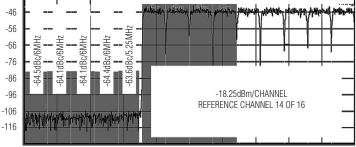

#### **Typical Operating Characteristics (continued)**

$(V_{AVDD3.3} = 3.3V, V_{DD1.8} = V_{AVCLK} = 1.8V, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, V_{MOD} = V_{DCLKDIV} = V_{DLLOFF} = 0V, V_{DELAY} = 1.8V, R_{REFRES} = 500\Omega$ , transformer-coupled differential output, tested at T<sub>J</sub> = +60°C, unless otherwise noted.)

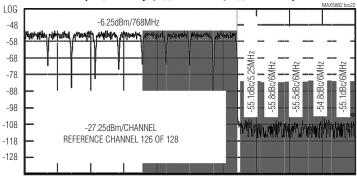

CENTER = 824MHz, SPAN = 84MHz, RBW = 10kHz, VBW = 100kHz, SWEEP = 5s

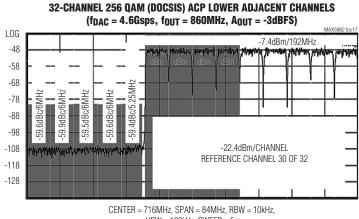

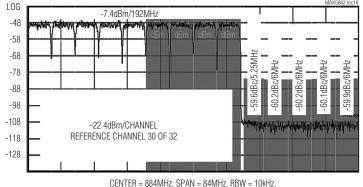

16-CHANNEL 256 QAM (DOCSIS) ACP UPPER ADJACENT CHANNELS (fdac = 4.6Gsps, fout = 860MHz, Aout = -3dBFS)

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

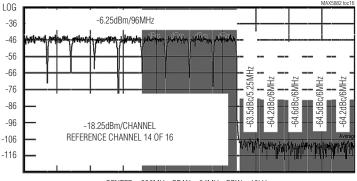

#### **Typical Operating Characteristics (continued)**

VBW = 100 kHz, SWEEP = 5s

32-CHANNEL 256 QAM (DOCSIS) ACP UPPER ADJACENT CHANNELS (fdac = 4.6Gsps, fout = 860MHz, Aout = -3dBFS)

VBW = 100kHz, SWEEP = 5s

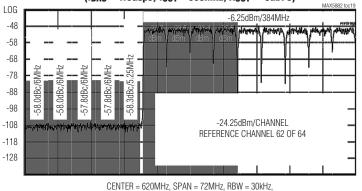

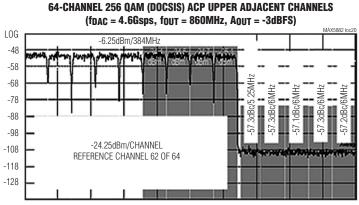

64-CHANNEL 256 QAM (DOCSIS) ACP LOWER ADJACENT CHANNELS (fdac = 4.6Gsps, fout = 860MHz, Aout = -3dBFS)

R = 620WHZ, SPAN = 72WHZ, RBW = 30Kr VBW = 300kHz, SWEEP = 5s

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

### **Typical Operating Characteristics (continued)**

$(V_{AVDD3.3} = 3.3V, V_{DD1.8} = V_{AVCLK} = 1.8V, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, V_{MOD} = V_{DCLKDIV} = V_{DLLOFF} = 0V, V_{DELAY} = 1.8V, R_{REFRES} = 500\Omega$ , transformer-coupled differential output, tested at T<sub>J</sub> = +60°C, unless otherwise noted.)

CENTER = 980MHz, SPAN = 84MHz, RBW = 10kHz, VBW = 100kHz, SWEEP = 5s

128-CHANNEL 256 QAM (DOCSIS) ACP LOWER ADJACENT CHANNELS (fdac = 4.6Gsps, fout = 860MHz, Aout = -3dBFS)

CENTER = 128MHz, SPAN = 84MHz, RBW = 10kHz, VBW = 100kHz, SWEEP = 5s

128-CHANNEL 256 QAM (DOCSIS) ACP UPPER ADJACENT CHANNELS (fdac = 4.6Gsps, fout = 860MHz, Aout = -3dBFS)

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

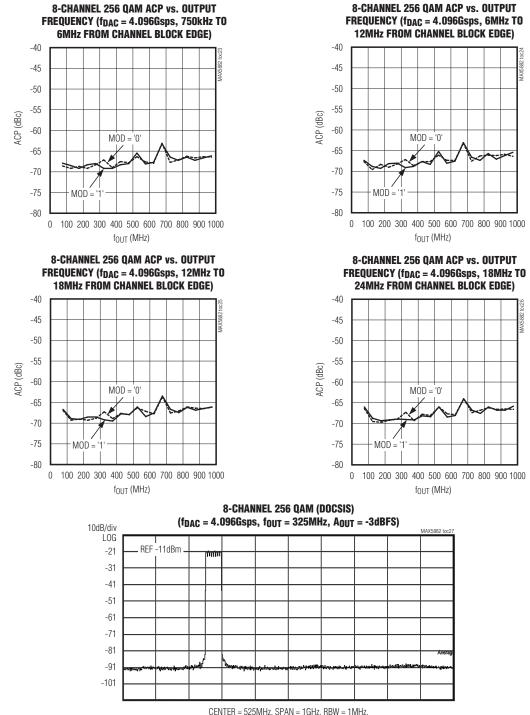

### **Typical Operating Characteristics (continued)**

R = 525MHz, SPAN = 1GHz, RBW = 1M VBW = 1MHz, SWEEP = 5s

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

### **Typical Operating Characteristics (continued)**

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

#### **Typical Operating Characteristics (continued)**

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

### **Typical Operating Characteristics (continued)**

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

### **Ball Configuration**

| OP VIEW |                    |                    |                    |                    |                    |          |       |                     |                     |       |       |                     |                     |        |                   |                   |

|---------|--------------------|--------------------|--------------------|--------------------|--------------------|----------|-------|---------------------|---------------------|-------|-------|---------------------|---------------------|--------|-------------------|-------------------|

|         |                    |                    |                    |                    |                    |          |       | MAXS                | 5882                |       |       |                     |                     |        |                   |                   |

|         | CREF               | DACREF             | REFIO              | FSADJ              | REFRES             | AVDD3.3  | GND   | AVDD3.3             | AVDD3.3             | OUTN  | OUTP  | AVDD3.3             | AVDD3.3             | GND    | GND               | GND               |

|         | (A1)               | (A2)               | (A3)               | (A4)               | (A5)               | (A6)     | (A7)  | (A8)                | (A9)                | (A10) | (A11) | (A12)               | (A13)               | (A14)  | (A15)             | (A16)             |

|         | GND                | GND                | GND                | GND                | GND                | GND      | GND   | AV <sub>DD3.3</sub> | AV <sub>DD3.3</sub> | OUTN  | OUTP  | AV <sub>DD3.3</sub> | AV <sub>DD3.3</sub> | GND    | AVCLK             | AVCLK             |

|         | (B1)               | (B2)               | (B3)               | (B4)               | (B5)               | (B6)     | (B7)  | (B8)                | (B9)                | (B10) | (B11) | (B12)               | (B13)               | (B14)  | (B15)             | (B16)             |

|         | V <sub>DD1.8</sub> | GND      | GND   | GND                 | GND                 | GND   | GND   | GND                 | GND                 | GND    | AV <sub>CLK</sub> | CLKN              |

|         | (01)               | (C2)               | (C3)               | (C4)               | (C5)               | (C6)     | (07)  | (08)                | (09)                | (C10) | (011) | (C12)               | (C13)               | (C14)  | (C15)             | (C16)             |

|         | SE                 | SO/LOCK            | PERR               | GND                | DELAY              | GND      | GND   | GND                 | GND                 | GND   | GND   | GND                 | GND                 | GND    | AVCLK             | CLKP              |

|         | (D1)               | (D2)               | (D3)               | (D4)               | (D5)               | (D6)     | (D7)  | (D8)                | (D9)                | (D10) | (D11) | (D12)               | (D13)               | (D14)  | (D15)             | (D16)             |

|         | GND                | DCLKDIV            | GND                | DLLOFF             | MOD                | GND      | GND   | GND                 | GND                 | GND   | GND   | GND                 | GND                 | GND    | AV <sub>CLK</sub> | AV <sub>CLK</sub> |

|         | (E1)               | (E2)               | (E3)               | (E4)               | (E5)               | (E6)     | (E7)  | (E8)                | (E9)                | (E10) | (E11) | (E12)               | (E13)               | (E14)  | (E15)             | (E16)             |

|         | GND                | GND                | GND                | GND                | GND                | GND      | GND   | GND                 | GND                 | GND   | GND   | GND                 | GND                 | GND    | GND               | GND               |

|         | (F1)               | (F2)               | (F3)               | (F4)               | (F5)               | (F6)     | (F7)  | (F8)                | (F9)                | (F10) | (F11) | (F12)               | (F13)               | (F14)  | (F15)             | (F16)             |

|         | V <sub>DD1.8</sub> | V <sub>DD1.8</sub> | V <sub>DD1.8</sub> | V <sub>DD1.8</sub> | GND                | GND      | GND   | GND                 | GND                 | GND   | GND   | GND                 | GND                 | GND    | GND               | GND               |

|         | (G1)               | (G2)               | (G3)               | (G4)               | (G5)               | (G6)     | (G7)  | (G8)                | (G9)                | (G10) | (G11) | (G12)               | (G13)               | (G14)  | (G15)             | (G16)             |

|         | DAP13              | DAN13              | DAP12              | DAN12              | DAP11              | DAN11    | DAP10 | DAN10               | GND                 | GND   | GND   | GND                 | VDD1.8              | VDD1.8 | VDD1.8            | VDD1.8            |

|         | (H1)               | (H2)               | (H3)               | (H4)               | (H5)               | (H6)     | (H7)  | (H8)                | (H9)                | (H10) | (H11) | (H12)               | (H13)               | (H14)  | (H15)             | (H16)             |

|         | DAP9               | DAN9               | DAP8               | DAN8               | DAP7               | DAN7     | DAP6  | DAN6                | DDP13               | DDN13 | DDP12 | DDN12               | DDP11               | DDN11  | DDP10             | DDN10             |

|         | (J1)               | (J2)               | (J3)               | (J4)               | (J5)               | (J6)     | (J7)  | (J8)                | (J9)                | (J10) | (J11) | (J12)               | (J13)               | (J14)  | (J15)             | (J16)             |

|         | DAP5               | DAN5               | DAP4               | DAN4               | DAP3               | DAN3     | DAP2  | DAN2                | DDP9                | DDN9  | DDP8  | DDN8                | DDP7                | DDN7   | DDP6              | DDN6              |

|         | (K1)               | (K2)               | (K3)               | (K4)               | (K5)               | (K6)     | (K7)  | (K8)                | (K9)                | (K10) | (K11) | (K12)               | (K13)               | (K14)  | (K15)             | (K16)             |

|         | DAP1               | DAN1               | DAPO               | DANO               | GND                | GND      | GND   | GND                 | DDP5                | DDN5  | DDP4  | DDN4                | DDP3                | DDN3   | DDP2              | DDN2              |

|         | (L1)               | (L2)               | (L3)               | (L4)               | (L5)               | (L6)     | (L7)  | (L8)                | (L9)                | (L10) | (L11) | (L12)               | (L13)               | (L14)  | (L15)             | (L16)             |

|         | DBP13              | DBN13              | DBP12              | DBN12              | DBP11              | DBN11    | DBP10 | DBN10               | DDP1                | DDN1  | DDP0  | DDNO                | GND                 | GND    | GND               | GND               |

|         | (M1)               | (M2)               | (M3)               | (M4)               | (M5)               | (M6)     | (M7)  | (M8)                | (M9)                | (M10) | (M11) | (M12)               | (M13)               | (M14)  | (M15)             | (M16)             |

|         | DBP9               | DBN9               | DBP8               | DBN8               | DBP7               | DBN7     | DBP6  | DBN6                | DCP13               | DCN13 | DCP12 | DCN12               | DCP11               | DCN11  | DCP10             | DCN10             |

|         | (N1)               | (N2)               | (N3)               | (N4)               | (N5)               | (N6)     | (N7)  | (N8)                | (N9)                | (N10) | (N11) | (N12)               | (N13)               | (N14)  | (N15)             | (N16)             |

|         | DBP5               | DBN5               | DBP4               | DBN4               | DBP3               | DBN3     | DBP2  | DBN2                | DCP9                | DCN9  | DCP8  | DCN8                | DCP7                | DCN7   | DCP6              | DCN6              |

|         | (P1)               | (P2)               | (P3)               | (P4)               | (P5)               | (P6)     | (P7)  | (P8)                | (P9)                | (P10) | (P11) | (P12)               | (P13)               | (P14)  | (P15)             | (P16)             |

|         | DBP1               | DBN1               | DBP0               | DBN0               | PARP               | PARN     | SYNCP | SYNCN               | DCP5                | DCN5  | DCP4  | DCN4                | DCP3                | DCN3   | DCP2              | DCN2              |

|         | (R1)               | (R2)               | (R3)               | (R4)               | (R5)               | (R6)     | (R7)  | (R8)                | (R9)                | (R10) | (R11) | (R12)               | (R13)               | (R14)  | (R15)             | (R16)             |

|         | GND                | GND                | GND                | GND                | DATACLKP           | DATACLKN | XORP  | XORN                | DCP1                | DCN1  | DCP0  | DCNO                | GND                 | GND    | GND               | GND               |

|         | (T1)               | (T2)               | (T3)               | (T4)               | (T5)               | (T6)     | (T7)  | (T8)                | (T9)                | (T10) | (T11) | (T12)               | (T13)               | (T14)  | (T15)             | (T16)             |

### Ball Description

| BALL | NAME   | FUNCTION                                                                                                                                                                                                              |

|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1   | CREF   | Noise Bypass Pin. A $1\mu F$ capacitor between CREF and DACREF band limits the phase noise of the device.                                                                                                             |

| A2   | DACREF | Current-Set Resistor Return Path. For 80mA full-scale output current, connect a $2k\Omega$ resistor between FSADJ and DACREF. DACREF is internally connected to GND. <b>Do not connect DACREF to external ground.</b> |

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

### **Ball Description (continued)**

| BALL                                                                                                                                                    | NAME                | FUNCTION                                                                                                                                                                                                                                                                                                                     |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A3                                                                                                                                                      | REFIO               | Reference Input/Output. Output pin for the internal 1.2V bandgap reference. REFIO has a $10k\Omega$ series resistance and can be driven using an external reference. Connect a $1\mu$ F capacit between REFIO and DACREF.                                                                                                    |  |

| A4                                                                                                                                                      | FSADJ               | Full-Scale Adjust Input. Sets the full-scale output current of the DAC. For 80mA full-scale output current, connect a $2k\Omega$ resistor between FSADJ and DACREF.                                                                                                                                                          |  |

| A5                                                                                                                                                      | REFRES              | Connect a 500 $\Omega$ resistor between REFRES and AV <sub>DD3.3</sub> .                                                                                                                                                                                                                                                     |  |

| A6, A8, A9,<br>A12, A13, B8,<br>B9, B12, B13                                                                                                            | AV <sub>DD3.3</sub> | Analog 3.3V Supply Voltage. Connect 47nF bypass capacitors between each AV <sub>DD3.3</sub> pin and GND.                                                                                                                                                                                                                     |  |

| A7, A14, A15,<br>A16, B1–B7,<br>B14, C6–C14,<br>D4, D6–D14,<br>E1, E3, E6–<br>E14, F1–F16,<br>G5–G16, H9–<br>H12, L5–L8,<br>M13–M16, T1–<br>T4, T13–T16 | GND                 | Analog Ground. Connect to ground plane with minimum inductance.                                                                                                                                                                                                                                                              |  |

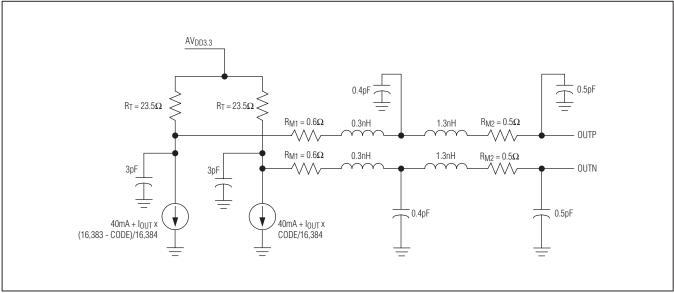

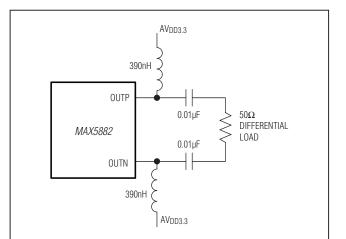

| A10, B10                                                                                                                                                | OUTN                | Negative Terminal of Differential DAC Output. OUTN has an internal 25 $\Omega$ resistor to AV <sub>DD3.3</sub> .                                                                                                                                                                                                             |  |

| A11, B11                                                                                                                                                | OUTP                | Positive Terminal of Differential DAC Output. OUTP has an internal $25\Omega$ resistor to AV <sub>DD3.3</sub> .                                                                                                                                                                                                              |  |

| B15, B16, C15,<br>D15, E15, E16                                                                                                                         | AV <sub>CLK</sub>   | Clock 1.8V Supply Voltage. Connect 47nF bypass capacitors between AV <sub>CLK</sub> and GND.                                                                                                                                                                                                                                 |  |

| C1–C5, G1–<br>G4, H13–H16                                                                                                                               | V <sub>DD1.8</sub>  | 1.8V Supply Voltage. Connect 47nF bypass capacitors between each $V_{DD1.8}$ pin and GND.                                                                                                                                                                                                                                    |  |

| D16                                                                                                                                                     | CLKP                | Positive Converter Clock Input. There is an internal $100\Omega$ termination resistor between CLKP and CLKN.                                                                                                                                                                                                                 |  |

| C16                                                                                                                                                     | CLKN                | Negative Converter Clock Input. There is an internal $100\Omega$ termination resistor between CLKP and CLKN.                                                                                                                                                                                                                 |  |

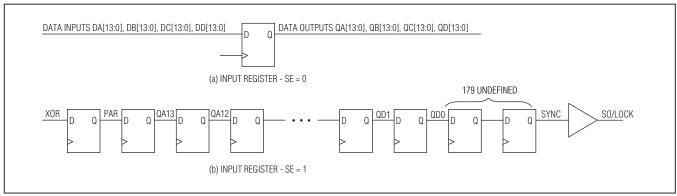

| D1                                                                                                                                                      | SE                  | Scan Enable. 1.8V CMOS logic input. During normal operation, SE should be connected to GND, and this makes the SO/LOCK pin a DLL LOCK indicator output. When SE is high (1.8V), the parallel input register is configured as a shift register, allowing the contents of the input register to be shifted out on SO/LOCK.     |  |

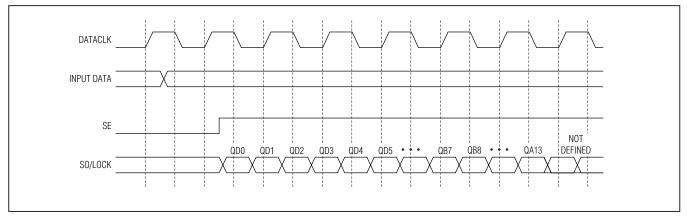

| D2                                                                                                                                                      | SO/LOCK             | 1.8V CMOS Logic Output<br>SE = high: SO/LOCK is a scan data output<br>SE = low: SO/LOCK is a DLL locking indicator output, and logic high indicates DLL is<br>locked                                                                                                                                                         |  |

| D3                                                                                                                                                      | PERR                | 1.8V CMOS Logic Level Parity Error Output. When a parity error is detected in the DAC input data, this pin is set high for a minimum of 48 LVDS data periods. This can be used to provide failure monitoring for the system. Note that this pin can pulse high when power is initially applied and before the DLL is locked. |  |

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

### **Ball Description (continued)**

| BALL                                                                         | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                    |  |

|------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D5                                                                           | DELAY     | Data Clock Mode Control      DELAY = 0: No clock delay when DLLOFF = 1      DELAY = 1: One f <sub>CLK</sub> period delay added to DATACLKP/DATACLKN when DLLOFF = 1      DLLOFF ≠ 1: DELAY is a 4-level input pin used along with DLLOFF (see Table 1 for details)      DELAY is a 1.8V, 3.3V tolerant, 4-level logic input |  |

| E2                                                                           | DCLKDIV   | Data Clock Divider Mode Input<br>DCLKDIV = 1: DATACLKP/DATACKLN is f <sub>DAC</sub> /8<br>DCLKDIV = 0: DATACLKP/DATACKLN is f <sub>DAC</sub> /4<br>DCLKDIV is a 1.8V, 3.3V tolerant, CMOS input with an internal pulldown resistor                                                                                          |  |

| E4                                                                           | DLLOFF    | Data Clock Mode Control      DLLOFF ≠ 1: DLL is enabled as a 4-level logic input pin used along with the DELAY pin      (see Table 1 for details)      DLLOFF = 1: DLL is disabled      DLLOFF is a 1.8V, 3.3V tolerant, 4-level logic input                                                                                |  |

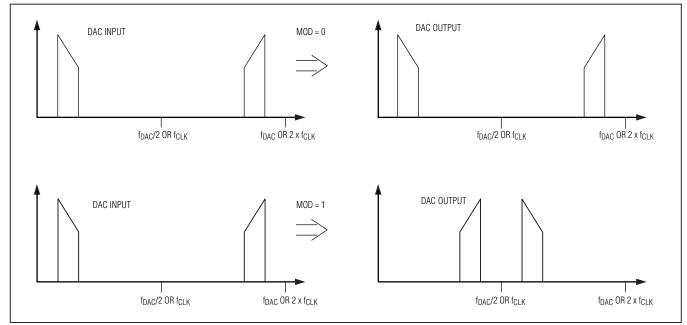

| E5                                                                           | MOD       | f <sub>DAC</sub> /2 (f <sub>CLK</sub> ) Modulation Control Input<br>MOD = 0: Modulation off<br>MOD = 1: Modulation on<br>MOD is a 1.8V, 3.3V tolerant, CMOS input with an internal pulldown resistor                                                                                                                        |  |

| H1, H3, H5,<br>H7, J1, J3, J5,<br>J7, K1, K3, K5,<br>K7, L1, L3              | DAP[13:0] | Positive Terminals of the A-Channel LVDS Data Inputs (Offset Binary Format). DAP13 is the MSB.                                                                                                                                                                                                                              |  |

| H2, H4, H6,<br>H8, J2, J4, J6,<br>J8, K2, K4, K6,<br>K8, L2, L4              | DAN[13:0] | Negative Terminals of the A-Channel LVDS Data Inputs                                                                                                                                                                                                                                                                        |  |

| M1, M3, M5,<br>M7, N1, N3,<br>N5, N7, P1, P3,<br>P5, P7, R1, R3              | DBP[13:0] | Positive Terminals of the B-Channel LVDS Data Inputs (Offset Binary Format). DBP13 is the MSB.                                                                                                                                                                                                                              |  |

| M2, M4, M6,<br>M8, N2, N4,<br>N6, N8, P2, P4,<br>P6, P8, R2, R4              | DBN[13:0] | Negative Terminals of the B-Channel LVDS Data Inputs                                                                                                                                                                                                                                                                        |  |

| N9, N11, N13,<br>N15, P9, P11,<br>P13, P15, R9,<br>R11, R13, R15,<br>T9, T11 | DCP[13:0] | Positive Terminals of the C-Channel LVDS Data Inputs (Offset Binary Format). DCP13 is the MSB.                                                                                                                                                                                                                              |  |

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

### **Ball Description (continued)**

| BALL                                                                             | NAME      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| N10, N12, N14,<br>N16, P10, P12,<br>P14, P16, R10,<br>R12, R14, R16,<br>T10, T12 | DCN[13:0] | Negative Terminals of the C-Channel LVDS Data Inputs                                                                                                                                                                                                                                                                                                                                                               |  |

| J9, J11, J13,<br>J15, K9, K11,<br>K13, K15, L9,<br>L11, L13, L15,<br>M9, M11     | DDP[13:0] | Positive Terminals of the D-Channel LVDS Data Inputs (Offset Binary Format). DDP13 is the MSB.                                                                                                                                                                                                                                                                                                                     |  |

| J10, J12, J14,<br>J16, K10, K12,<br>K14, K16, L10,<br>L12, L14, L16,<br>M10, M12 | DDN[13:0] | Negative Terminals of the D-Channel LVDS Data Inputs                                                                                                                                                                                                                                                                                                                                                               |  |

| R5                                                                               | PARP      | Positive Terminal of the Parity LVDS Data Input. The parity input data is used internally to pro-<br>vide detection of bit errors between the data source and the DAC and can be used for system<br>monitoring. PARP/PARN should be delayed three DATACLKP/DATACLKN cycles.                                                                                                                                        |  |

| R6                                                                               | PARN      | Negative Terminal of parity LVDS Data Input                                                                                                                                                                                                                                                                                                                                                                        |  |

| R7                                                                               | SYNCP     | Positive Terminal of the Synchronization LVDS Data Input. The SYNCP/SYNCN pair should be driven synchronously with the DAC data input pairs and should be a pseudo-random sequence.                                                                                                                                                                                                                                |  |

| R8                                                                               | SYNCN     | Negative Terminal of the Synchronization LVDS Data Input                                                                                                                                                                                                                                                                                                                                                           |  |

| T5                                                                               | DATACLKP  | Positive Terminal of the LVDS Data Clock Output                                                                                                                                                                                                                                                                                                                                                                    |  |

| Т6                                                                               | DATACLKN  | Negative Terminal of the LVDS Data Clock Output                                                                                                                                                                                                                                                                                                                                                                    |  |

| Τ7                                                                               | XORP      | Positive Terminal of the XOR LVDS Data Input. The A-, B-, C-, and D-channel data bits are logi-<br>cally exclusive ORed by the data on the XORP/XORN pin internally. This function can be used<br>for whitening spurious signals that can be present in the input data. XORP/XORN should be<br>delayed one DATACLKP/DATACLKN cycle. To disable the XOR function, drive a logic 0 into the<br>XORP/XORN input pair. |  |

|                                                                                  | XORN      | Negative Terminal of XOR LVDS Data Input                                                                                                                                                                                                                                                                                                                                                                           |  |

### 14-Bit, 4.6Gsps Cable Downstream Direct RF Synthesis DAC

#### **Detailed Description**

The MAX5882 is a high-performance, high-speed, 14-bit current-steering DAC with an integrated 50 $\Omega$  differential output termination to the 3.3V supply. The DAC operates with a clock rate (f<sub>CLK</sub>) up to 2.3GHz. The DAC output is updated on each edge of the input clock resulting in a DAC update rate (f<sub>DAC</sub>) of 4.6Gsps.

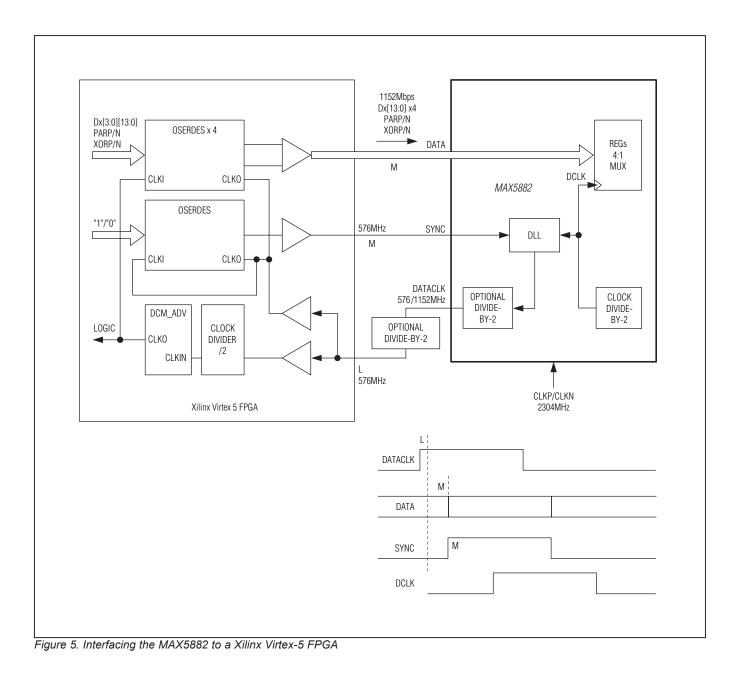

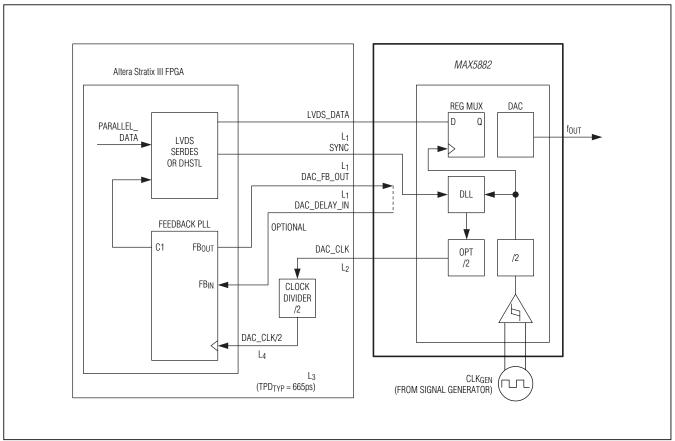

The device employs an edge-triggered 4:1 input data multiplexer and a delay-locked loop (DLL) to ease the interface requirements to FPGA or ASIC data sources. The SYNCP/SYNCN signal provides timing information to the internal DLL. The XORP/XORN signal allows whitening the spectral content of the input data stream. The data interface also provides parity validation for verification of the data transmission.

The analog output is a current-steering circuit capable of generating differential full-scale currents in the 10mA to 80mA range. An integrated 1.2V bandgap reference, control amplifier, and user-selectable external resistor determine the data converter's full-scale range.