#### MAX77597

## 36V, 300mA, Buck Converter with 1.1µA IQ

### **General Description**

The MAX77597 is a small, synchronous buck converter with integrated switches. The device is designed to deliver up to 300mA with input voltages from 3.5V to 36V, while using only 1.1 $\mu$ A quiescent current at no load (fixed-output version). Voltage quality can be monitored by observing the  $\overline{\text{RESET}}$  signal. The device can operate near dropout by running at 98% duty cycle, making it ideal for battery-powered applications.

The device offers fixed 3.3V. Frequency is fixed at 1.7 MHz, which allows for small external components and reduced output ripple. The device offers both forced-PWM and skip modes of operation, with ultra-low quiescent current of  $1.1 \mu A$  in skip mode.

The MAX77597 is available in a small (2mm x 2.5mm) 10-pin TDFN package and operates across the -40°C to +85°C temperature range.

### **Applications**

- Portable Devices Powered from 2s, 3s, or 4s Li+ Batteries

- USB Type-C Devices

- Point-of-Load Applications

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- Flexible Power for Systems That Require a Wide Input Voltage Range

- V<sub>IN</sub> Range: 3.5V to 36V

- Up to 300mA Output Current

- · Fixed 3.3V, Output Voltage

- 98% (Max) Duty Cycle Operation with Low Dropout

- Operates from 5V, 12V, or 20V USB Type-C Input Power

- · Operates from 2S, 3S, or 4S Li-Ion Battery

- Minimizes Power Consumption and Extends Battery Life

- 1.1µA Quiescent Current (3.3V Fixed Output Voltage)

- 86% Peak Efficiency at 12V<sub>IN</sub>, 3.3 V<sub>OUT</sub>

- Minimizes Solution Size

- 1.7MHz Operating Frequency

- Small 2.0mm x 2.5mm x 0.75mm 10-Pin TDFN Package

- Robust Solution

- · Short-Circuit, Thermal Protections

- · 6.67ms Internal Soft-Start Minimizes Inrush Current

- Current-Mode Control Architecture

- Up to 42V Input Voltage Tolerance

# **Absolute Maximum Ratings**

| (Voltages Referenced to PGNE | 0)                                         |

|------------------------------|--------------------------------------------|

| SUP                          | 0.3V to +42V                               |

| EN                           | 0.3V to MIN (24V, V <sub>SUP</sub> + 0.3V) |

| BST to LX                    | +6V                                        |

| BST                          | 0.3V to +47V                               |

| MODE, OUT/FB, RESET          | 0.3V to V <sub>BIAS</sub> + 0.3V           |

| AGND                         | 0.3V to +0.3V                              |

| BIAS                         | 0.3V to +6.0V                              |

| OUT/FB Short-Circuit Duration                         | Continuous     |

|-------------------------------------------------------|----------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

| (derate 9.8mW/°C above +70°C)                         | 784mV          |

| Operating Temperature Range                           | 40°C to +85°C  |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | 300°C          |

| Soldering Temperature (reflow)                        | +260°C         |

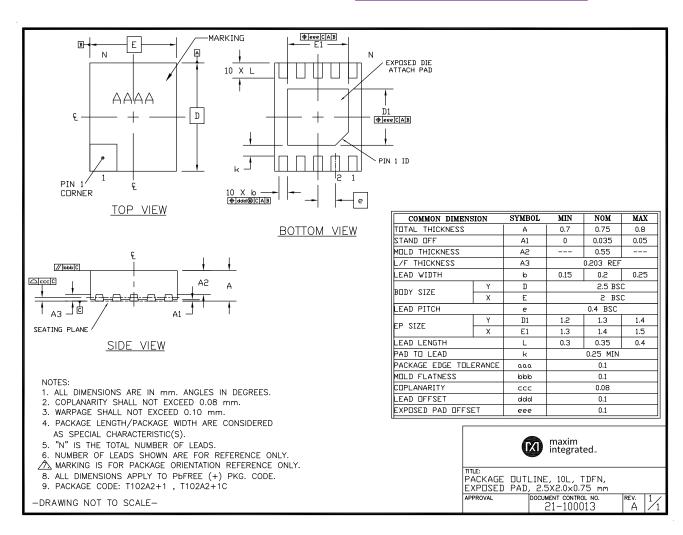

### **Package Information**

#### **20-TDFN**

| PACKAGE CODE                           | T102A2+1C |  |  |  |

|----------------------------------------|-----------|--|--|--|

| Outline Number                         | 21-100013 |  |  |  |

| Land Pattern Number                    | _         |  |  |  |

| Thermal Resistance:                    |           |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 102°C/W   |  |  |  |

| Junction to Case (θ <sub>JC</sub> )    | 2.9°C/W   |  |  |  |

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

### **Electrical Characteristics**

$(V_{SUP} = V_{EN} = 14V, V_{MODE} = 0V, T_A = T_J = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                                          | SYMBOL                | CONDITIONS                                                                           | MIN  | TYP  | MAX  | UNITS             |

|----------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------|------|------|------|-------------------|

| Supply Voltage                                     | V <sub>SUP</sub>      |                                                                                      | 3.5  |      | 36   | V                 |

| Supply Voltage                                     | V <sub>SUP</sub>      | t < 500ms (Note 2)                                                                   |      |      | 42   | V                 |

|                                                    |                       | Shutdown (V <sub>EN</sub> = 0V)                                                      |      | 0.75 | 3.0  |                   |

| Supply Current                                     | I <sub>SUP</sub>      | No load, fixed 3.3V V <sub>OUT</sub>                                                 |      | 1.1  | 3.0  | μA                |

| опри оптен                                         | ISUP                  | V <sub>MODE</sub> = V <sub>BIAS</sub> , no load, FPWM, no switching                  | 0.5  | 1    | 1.5  | mA                |

| IN/I I I                                           | .,,                   | V <sub>BIAS</sub> rising                                                             | 3.0  | 3.2  | 3.4  | V                 |

| UV Lockout                                         | V <sub>UVLO</sub>     | Hysteresis                                                                           |      | 0.4  |      |                   |

| BIAS Regulator Voltage                             | V <sub>BIAS</sub>     | V <sub>SUP</sub> = 5.5V to 36V                                                       |      | 5    |      | V                 |

| BIAS Current Limit                                 |                       |                                                                                      | 10   |      |      | mA                |

| BUCK CONVERTER                                     |                       | 1                                                                                    |      |      |      |                   |

| Voltage Accuracy                                   | V <sub>OUT,3.3V</sub> | $V_{OUT} = 3.3V, 6V \le V_{SUP} \le 36V,$<br>$I_{LOAD} = 0 \text{ to } 300\text{mA}$ | 3.1  | 3.3  | 3.4  | V                 |

| High-Side DMOS R <sub>DSON</sub>                   | R <sub>ON,HS</sub>    | V <sub>BIAS</sub> = 5V, I <sub>LX</sub> = 200mA                                      |      | 1000 | 2200 | mΩ                |

| Low-Side DMOS R <sub>DSON</sub>                    | R <sub>ON,LS</sub>    | V <sub>BIAS</sub> = 5V, I <sub>LX</sub> = 200mA                                      |      | 500  | 1200 | mΩ                |

| DMOS High-Side Current-Limit<br>Threshold          | I <sub>MAX</sub>      |                                                                                      | 425  | 500  | 575  | mA                |

| DMOS High-Side Skip-Mode<br>Peak-Current Threshold | I <sub>SKIP</sub>     |                                                                                      | 70   | 100  | 130  | mA                |

| DMOS Low-Side Zero-Crossing<br>Threshold           | I <sub>ZX</sub>       |                                                                                      |      | 40   |      | mA                |

| DMOS Low-Side Negative<br>Current-Limit Threshold  | I <sub>NEG</sub>      | FPWM mode                                                                            |      | -320 |      | mA                |

| Soft-Start Ramp Time                               | t <sub>SS</sub>       |                                                                                      |      | 6.67 |      | ms                |

| LX Rise Time                                       | t <sub>RISE,LX</sub>  | (Note 2)                                                                             |      | 6    |      | ns                |

| Minimum On-Time                                    | t <sub>ON_MIN</sub>   |                                                                                      |      | 34   |      | ns                |

| Maximum Duty Cycle                                 | DC <sub>MAX</sub>     |                                                                                      |      | 98   |      | %                 |

| PWM Switching Frequency                            | f <sub>SW</sub>       |                                                                                      | 1.58 | 1.7  | 1.82 | MHz               |

| RESET OUTPUT (RESET)                               |                       |                                                                                      |      |      |      |                   |

| RESET Threshold                                    | V <sub>THR_RES</sub>  | V <sub>OUT</sub> rising                                                              | 88   | 92   | 96   | %V <sub>OUT</sub> |

|                                                    | V <sub>THF_RES</sub>  | V <sub>OUT</sub> falling                                                             | 86   | 90   | 94   |                   |

| RESET Debounce                                     | t <sub>DEB</sub>      |                                                                                      |      | 12   |      | μs                |

| RESET High Leakage Current                         | I <sub>LEAK,RES</sub> | T <sub>A</sub> = +25°C                                                               |      |      | 1    | μA                |

| RESET Low Level                                    | V <sub>OUT,RES</sub>  | Sinking 1mA                                                                          |      |      | 0.4  | V                 |

## **Electrical Characteristics (continued)**

$(V_{SUP} = V_{EN} = 14V, V_{MODE} = 0V, T_A = T_J = -40^{\circ}C$  to +85°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 1)

| PARAMETER                   | SYMBOL                | CONDITIONS | MIN | TYP  | MAX | UNITS |  |  |

|-----------------------------|-----------------------|------------|-----|------|-----|-------|--|--|

| LOGIC LEVELS                | LOGIC LEVELS          |            |     |      |     |       |  |  |

| EN Input High Threshold     | V <sub>IH,EN</sub>    |            | 2.4 |      |     | V     |  |  |

| EN Input Low Threshold      | V <sub>IL,EN</sub>    |            |     |      | 0.4 | V     |  |  |

| EN Input Current            | I <sub>IN,EN</sub>    |            |     | 0.1  |     | μA    |  |  |

| MODE Input High Threshold   | V <sub>IH,MODE</sub>  |            | 1.4 |      |     | V     |  |  |

| MODE Input Low Threshold    | V <sub>IL,MODE</sub>  |            |     |      | 0.4 | V     |  |  |

| MODE Internal Pulldown      | R <sub>PD,MODE</sub>  |            |     | 1000 |     | kΩ    |  |  |

| THERMAL PROTECTION          |                       |            |     |      |     |       |  |  |

| Thermal Shutdown            | T <sub>SHDN</sub>     | (Note 2)   |     | +175 |     | °C    |  |  |

| Thermal-Shutdown Hysteresis | T <sub>SHDN,HYS</sub> | (Note 2)   |     | +15  |     | °C    |  |  |

Note 1: Limits are 100% tested at  $T_A$  = +25°C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

Note 2: Guaranteed by design; not production tested.

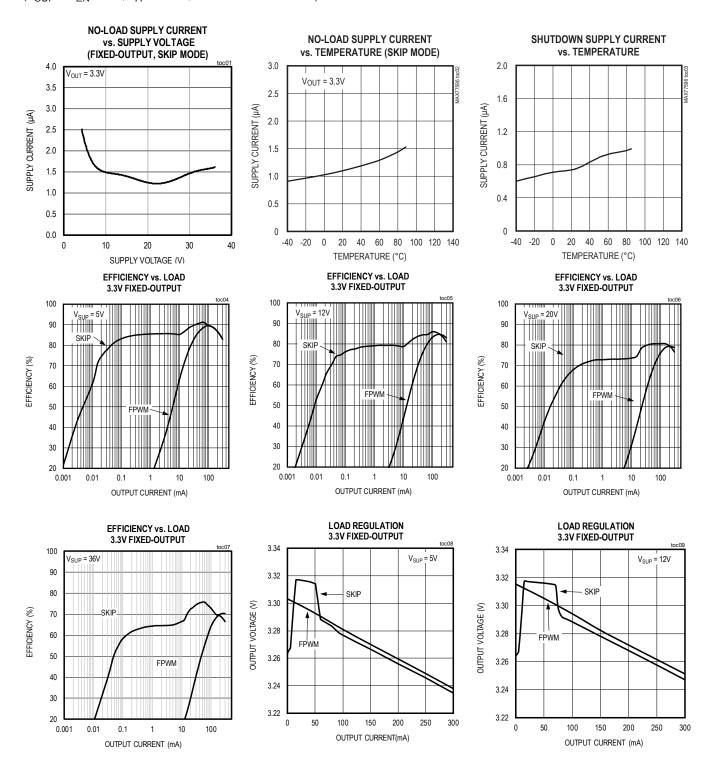

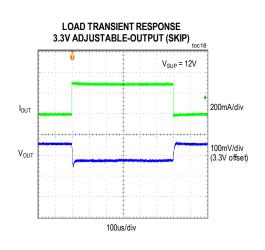

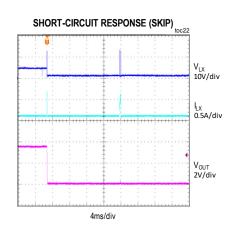

# **Typical Operating Characteristics**

$(V_{SUP} = V_{EN} = 12V, T_A = +25^{\circ}C, unless otherwise noted.)$

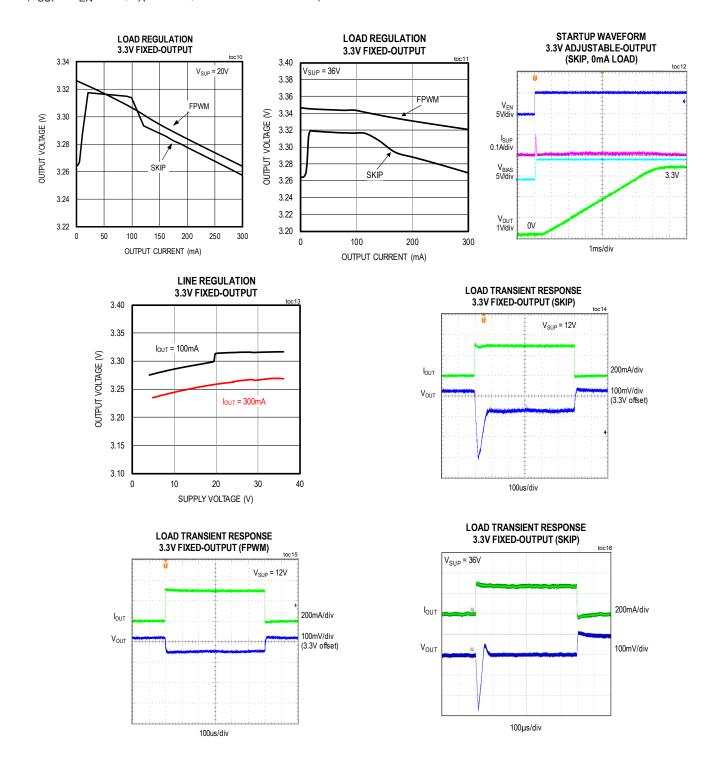

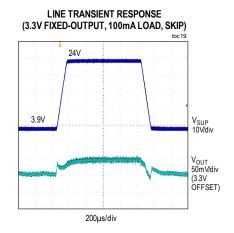

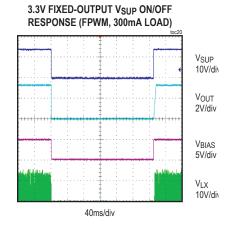

## **Typical Operating Characteristics (continued)**

$(V_{SUP} = V_{EN} = 12V, T_A = +25^{\circ}C, unless otherwise noted.)$

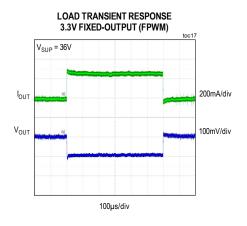

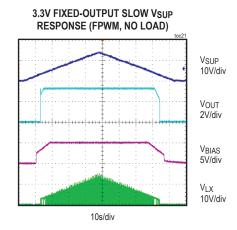

## **Typical Operating Characteristics (continued)**

$(V_{SUP} = V_{EN} = 12V, T_A = +25^{\circ}C, unless otherwise noted.)$

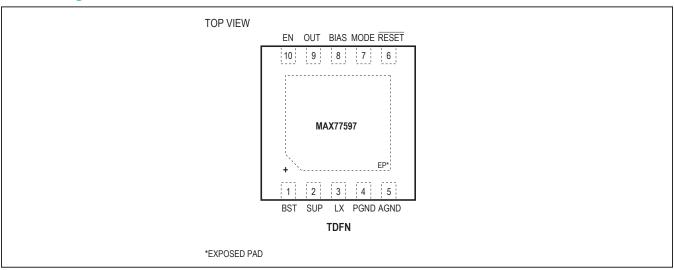

# **Pin Configuration**

## **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                                                 |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

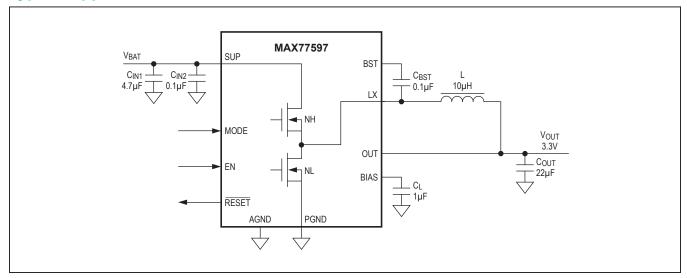

| 1   | BST   | High-Side Driver Supply. Connect a 0.1µF bootstrap capacitor between LX and BST.                                                                                                         |

| 2   | SUP   | IC Supply Input. Connect a minimum of 4.7μF ceramic capacitor from SUP to PGND.                                                                                                          |

| 3   | LX    | Buck Switching Node. LX is high impedance when the device is off.                                                                                                                        |

| 4   | PGND  | Power Ground. Connect to AGND under the device in a star configuration.                                                                                                                  |

| 5   | AGND  | Analog Ground. Connect to PGND under the device in a star configuration.                                                                                                                 |

| 6   | RESET | Open-Drain Reset Output. An external pullup resistor is required.                                                                                                                        |

| 7   | MODE  | Mode Switch-Control Input. Connect to ground or leave open to enable skip-mode operation under light loads. Connect to BIAS to enable forced-PWM mode. MODE has a 1MΩ internal pulldown. |

| 8   | BIAS  | 5V Internal Logic Supply. Connect a 1μF ceramic capacitor to AGND. Do not load this pin externally.                                                                                      |

| 9   | OUT   | MAX77597ETBB+ (Fixed Output): Buck Regulator Voltage-Sense Input. Bypass OUT to PGND with a minimum 22μF X5R ceramic capacitor.                                                          |

| 10  | EN    | Enable Input. Drive EN low to disable the device. Drive EN high to enable the device.                                                                                                    |

| _   | EP    | Exposed Pad. Connect EP to a large copper ground plane for effective power dissipation. Do not use EP as the only IC ground connection. EP must be connected to PGND.                    |

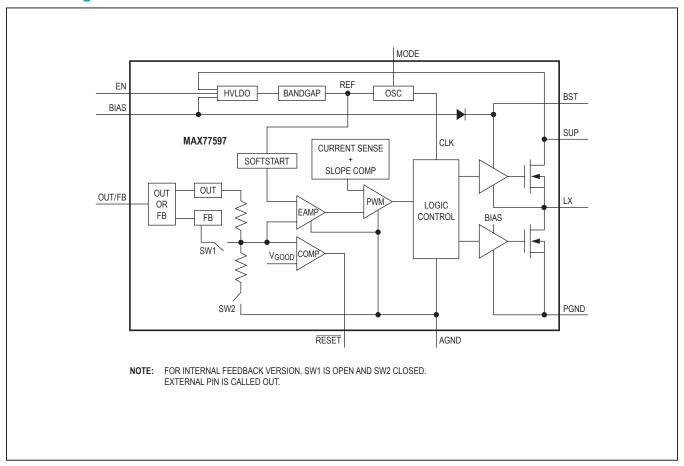

# **Block Diagram**

### **Detailed Description**

The MAX77597 is a small, current-mode buck converter that features synchronous rectification and requires no external compensation network. The device operates from a 3.5V to 36V supply voltage and can deliver up to 300mA output current. Frequency is fixed at 1.7MHz, which allows for small external components and reduced output ripple.

The device offers fixed 3.3V output Voltage quality can be monitored by observing the  $\overline{\text{RESET}}$  signal. The device offers both forced-PWM and skip mode, with ultra-low-quiescent current of 1.1µA in skip mode.

#### **DC-DC Converter Control Architecture**

The step-down converter uses a PWM peak current-mode control scheme with a load-line architecture. Peak current-mode control provides several advantages over voltage-mode control, including precise control of the inductor current on a cycle-by-cycle basis, simpler compensation, and inherent compensation for line voltage variation.

An internal transconductance amplifier establishes an integrated error voltage. The heart of the PWM controller is an open-loop comparator: one input is the integrated voltage-feedback signal; the other consists of the amplified current-sense signal plus slope-compensation ramp. Integrated high-side current sensing is used, which reduces component count and layout risk by eliminating the need to carefully route sensitive external signals. Error-amplifier compensation is also integrated, once again simplifying the power-supply designer's task while eliminating external components.

The controller features a load-line architecture. The output voltage is positioned slightly above nominal regulation at no load and slightly below nominal regulation at full load. As output load changes, a small but controlled amount of load regulation ("load-line") error occurs on the output voltage. This voltage positioning architecture allows the output voltage to respond to sudden load transients in a critically damped manner, and effectively reduces the amount of output capacitance needed when compared to classical integrating controllers. See the *Typical Operating Characteristics* section of the data sheet for information about the converter's typical voltage regulation behavior versus load.

The device can operate in either forced-PWM or skip mode. In forced-PWM mode, the converter maintains a constant switching frequency, regardless of load, to allow for easier filtering of the switching noise. The device includes proprietary circuitry that dramatically reduces quiescent current consumption in skip mode, improving light-load efficiency. See the <u>Forced PWM/Skip Modes</u> section for further details.

#### System Enable (EN)

An enable control input (EN) activates the device from its low-power shutdown mode. EN is compatible with inputs from levels down to 2.4V. EN can be connected directly to SUP for voltage level up to 24V. For self-enable operations with SUP voltages above 24V, connect EN using an external resistor divider to maintain EN below 24V.

#### **Linear Regulator Output (BIAS)**

The device includes a 5V linear regulator output (BIAS) that provides power to the internal circuit blocks. Connect a  $1\mu F$  ceramic capacitor from BIAS to AGND. Do not load this pin externally.

### **Undervoltage Lockout**

When  $V_{BIAS}$  drops below the undervoltage-lockout (UVLO) level of  $V_{UVLO}$  = 2.8V (typ), the device assumes that the supply voltage is too low for proper operation, so the UVLO circuitry inhibits switching. When  $V_{BIAS}$  rises above the UVLO rising threshold, the controller enters the startup sequence and then resumes normal operation.

#### **Startup and Soft-Start**

The device features an internal soft-start timer. The output-voltage soft-start ramp time is 6.67ms (typ). If a short circuit or undervoltage is encountered after the soft-start timer has expired, the device is disabled for 16.5ms (typ) and then reattempts soft-start again. This pattern repeats until the short circuit has been removed.

#### **RESET Output**

The device features an open-drain RESET output to monitor the output voltage. The RESET output requires an external pullup resistor. RESET goes high (high impedance) after the regulator output increases above 92% of the nominal regulated voltage. RESET goes low when the regulator output drops to below 90% of the nominal regulated voltage.

#### Forced PWM/Skip Modes

The device features a logic-level input (MODE) to switch between forced-PWM and skip modes. Connecting MODE to BIAS enables the forced-PWM operation. Connecting MODE to ground, or leaving unconnected, enables skipmode operation with ultra-low-quiescent current of 1.1µA. In skip-mode operation, the converter's switching frequency is load dependent until the output load reaches the skip threshold. At higher load current, the switching frequency does not change and the operating mode is similar to the forced-PWM mode. Skip mode helps improve efficiency in light-load applications by allowing the converter to turn on the high-side switch only when the output voltage falls below a set threshold. As such, the converter does not switch the MOSFETs on and off as often as is the case in the forced-PWM mode. Consequently, the gate charge and switching losses are much lower in skip mode.

#### **Current Limit/Short-Circuit Protection**

The device has fault protection designed to protect itself from abnormal conditions. If the output is soft shorted (meaning the output is overloaded but over 25% of regulation), cycle-by-cycle current limit limits how high the inductor current goes for any cycle. If the output is hard shorted to ground and the output falls to less than 25% of regulation, the part goes into a mode where it switches until 15 cycles are ended by current limit, then waits for 16.5ms before trying to soft-start again. This mode of operation limits the amount of power dissipated by the device under these conditions. The device also has overtemperature protection. If the die temperature exceeds approximately 175°C, the device stops switching until the die temperature drops by approximately 15°C and then resumes operation, including going through soft-start again.

### **Applications Information**

#### **Inductor Selection**

Three key inductor parameters must be specified for operation with the device: inductance value (L), inductor saturation current ( $I_{SAT}$ ), and DC resistance ( $R_{DCR}$ ). To select inductance value, the ratio of inductor peak-to-peak AC current to DC average current (LIR) must be selected first. A good compromise between size and loss is a 30% peak-to-peak ripple current to average current ratio (LIR = 0.3). The switching frequency, input voltage,

output voltage, and selected LIR then determines the inductor value as follows:

$$L = \frac{V_{OUT} \times (V_{SUP} - V_{OUT})}{V_{SUP} \times f_{SW} \times I_{OUT} \times LIR}$$

where  $V_{SUP}$ ,  $V_{OUT}$ , and  $I_{OUT}$  are typical values (so that efficiency is optimum for typical conditions). The switching frequency is 1.7MHz. <u>Table 1</u> lists some of the inductor values for 300mA output current and several output voltages.

Table 1. Inductor Values for 300mA Output Current

| V <sub>SUP</sub> /V <sub>OUT</sub> (V)  | 14V/3.3V                 |

|-----------------------------------------|--------------------------|

| INDUCTOR (μH) I <sub>LOAD</sub> = 300mA | 10μΗ (typ)<br>22μΗ (max) |

#### **Input Capacitor**

The input filter capacitor reduces peak currents drawn from the power source and reduces noise and voltage ripple on the input caused by the circuit's switching. The input capacitor RMS current requirement (I<sub>RMS</sub>) is defined by the following equation:

$$I_{RMS} = I_{LOAD(MAX)} \frac{\sqrt{V_{OUT} \times (V_{SUP} - V_{OUT})}}{V_{SUP}}$$

I<sub>RMS</sub> has a maximum value when the input voltage equals twice the output voltage ( $V_{SUP} = 2V_{OUT}$ ), so  $I_{RMS(MAX)} = I_{LOAD(MAX)}/2$ .

Choose an input capacitor that exhibits less than +10°C self-heating temperature rise at the RMS input current for optimal long-term reliability.

The input voltage ripple is composed of  $\Delta V_Q$  (caused by the capacitor discharge) and  $\Delta V_{ESR}$  (caused by the ESR of the capacitor). Use low-ESR ceramic capacitors with high ripple current capability at the input. Assume the contribution from the ESR and capacitor discharge equal to 50%. Calculate the input capacitance and ESR required for a specified input voltage ripple using the following equations:

$$ESR_{IN} = \frac{\Delta V_{ESR}}{I_{OUT} + \frac{\Delta I_{L}}{2}}$$

where:

$$\Delta I_{L} = \frac{(V_{SUP} - V_{OUT}) \times V_{OUT}}{V_{SUP} \times f_{SW} \times L}$$

and:

$$C_{IN} = \frac{I_{OUT} \times D(1-D)}{\Delta V_O \times f_{SW}}$$

and  $D = \frac{V_{OUT}}{V_{SUP}}$

where  $I_{\mbox{OUT}}$  is the maximum output current and D is the duty cycle.

#### **Output Capacitor**

The output filter capacitor must have low enough ESR to meet output ripple and load transient requirements. The output capacitance must be high enough to absorb the inductor energy while transitioning from full-load to noload conditions. When using high-capacitance, low-ESR capacitors, the filter capacitor's ESR dominates the output voltage ripple. Therefore, the size of the output capacitor depends on the maximum ESR required to meet the output voltage ripple (V<sub>RIPPI F(P-P)</sub>) specifications:

$$V_{RIPPLE(P-P)} = ESR \times I_{LOAD(MAX)} \times LIR$$

The actual capacitance value required relates to the physical size needed to achieve low ESR, as well as to the chemistry of the capacitor technology. Therefore, the capacitor is usually selected by ESR and voltage rating rather than by capacitance value.

When using low-capacity filter capacitors, such as ceramic capacitors, size is usually determined by the capacity needed to prevent voltage droop and voltage rise from causing problems during load transients. Generally, once enough capacitance is added to meet the overshoot requirement, undershoot at the rising-load edge is no longer a problem.

#### **PCB Layout Guidelines**

Careful PCB layout is critical to achieve low-switching power losses and clean, stable operation. Use a multi-layer board whenever possible for better noise immunity and power dissipation. Follow these guidelines for good PCB layout:

- The input capacitor (4.7μF, see Figures 3 and 4) should be placed immediately next to the SUP pin of the device. Since the device operates at 1.7MHz switching frequency, this placement is critical for effective decoupling of high-frequency noise from the SUP pin.

- 2) Solder the exposed pad to a large copper plane area under the device. To effectively use this copper area as heat exchanger between the PCB and ambient, expose the copper area on the top and bottom sides. Add a few small vias or one large via on the copper pad for efficient heat transfer. Connect the exposed pad to PGND, ideally at the return terminal of the output capacitor.

- Isolate the power components and high-current path from the sensitive analog circuitry. Doing so is essential to prevent any noise coupling into the analog signals.

- 4) Keep the high-current paths short, especially at the ground terminals. This practice is essential for stable, jitter-free operation.

- 5) Connect PGND and AGND together at the return terminal of the output capacitor. Do not connect them anywhere else.

- 6) Keep the power traces and load connections short. This practice is essential for high efficiency.

- 7) Place the BIAS capacitor ground next to the AGND pin and connect with a short and wide trace.

# **Typical Application Circuits**

Figure 1. MAX77597ETBB+, Fixed Output Voltage (3.3V), 10-Pin TDFN

## **Ordering Information**

| PART          | V <sub>OUT</sub> | PIN-PACKAGE |  |

|---------------|------------------|-------------|--|

| MAX77597ETBB+ | Fixed 3.3V       | 10 TDFN-EP* |  |

<sup>\*</sup>EP = Exposed pad.

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                              | PAGES<br>CHANGED |  |

|--------------------|---------------|------------------------------------------|------------------|--|

| 0                  | 4/20          | Initial release                          | _                |  |

| 1                  | 4/20          | Updated the Detailed Description section | 11               |  |

For information on other Maxim Integrated products, visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.