## USB Type-C, 3A Switch-Mode Buck Charger with Integrated CC Detection, Reverse Boost, and ADC

#### **General Description**

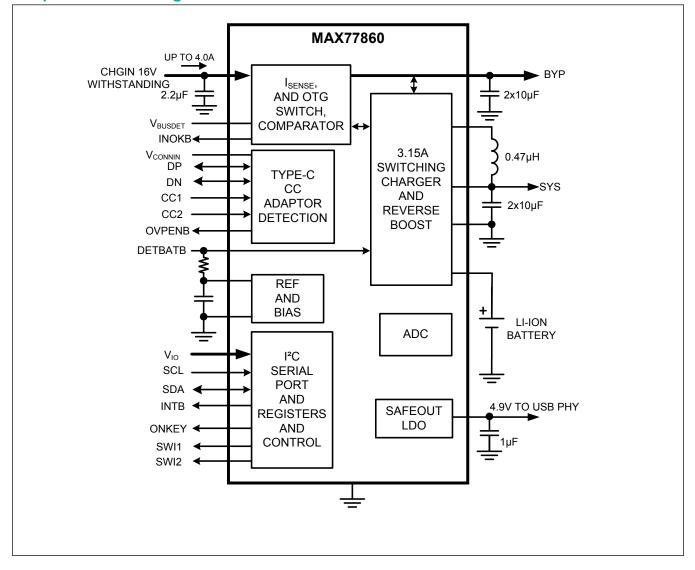

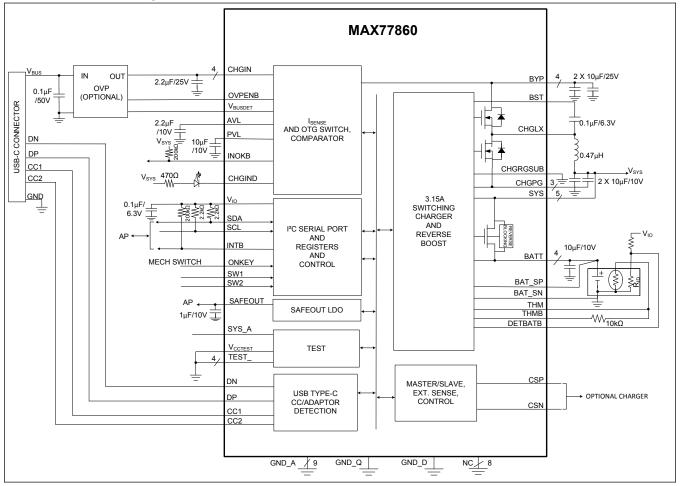

The MAX77860 is a high-performance single input switch mode charger that features USB Type-C CC detection capability in addition to reverse boost capability and a Safeout LDO.

This switched-mode battery charger with two integrated switches, provides small inductor and capacitor sizes, programmable battery charging current, and is ideally suited for portable devices such as smartphones, IoT devices, and other Li-ion battery powered electronics. The charger features a single input, which works for both USB and high voltage adapters. It supports USB Type-C CC detection under BC 1.2 specification, and the power-path switch is integrated in the chip. All MAX77860 blocks connected to the adapter/USB pin are protected from input overvoltage events up to 14V. The USB-OTG output provides trueload disconnect and is protected by an adjustable output current limit. It has an input current limit up to 4.0A and can charge a single-cell battery up to 3.15A. When configured in reverse-boost mode, the IC requires no additional inductors to power USB-OTG accessories. The switching charger is designed with a special CC, CV, and die temperature regulation algorithm, as well as I<sup>2</sup>C programmable settings to accommodate a wide range of battery sizes and system loads. The on-chip ADC can help monitor the charging input voltage/current, battery voltage, charging/ discharging current, and the battery temperature.

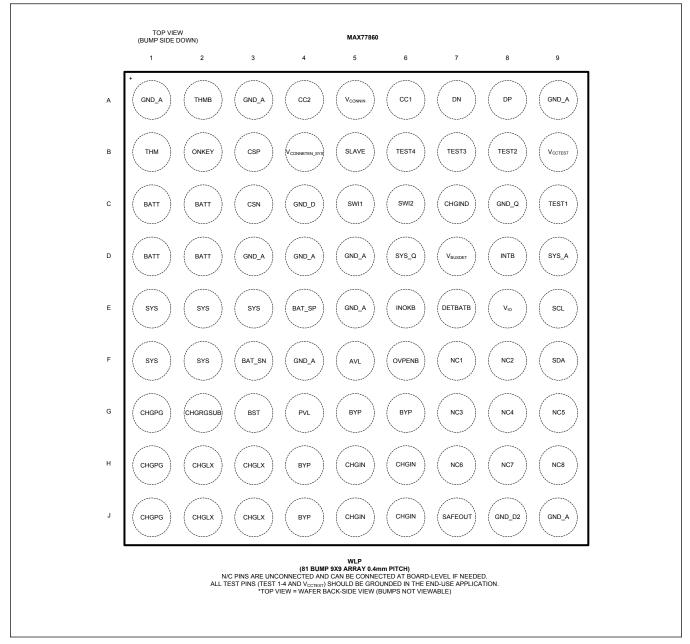

The MAX77860 communicates through an  $I^2C$  3.0 compatible serial interface consisting of a bidirectional serial data line (SDA) and a serial clock line (SCL). The IC is available in a 3.9mm x 4.0mm, 81-bump (9 x 9 array), 0.4mm pitch, wafer-level package (WLP).

#### **Applications**

- USB Type-C Charging for 1S Li-ion Applications

- Mobile Point-of-Sale Devices

- Portable Medical Equipment

- Portable Industrial Equipment

#### **Benefits and Features**

- Single-Cell Switch Mode Charger

- Up to 14V Protection

- 4.0V to 13.5V Input Operating Range

- Switching Charger with D+/D- Charger Detection

Up to 4.0A Input Current Limit with Adaptive Input Current Limit (AICL)

- Up to 3.15A Battery Charging Current Limit

- Optional External Sense Resistor

- CC, CV, and Die Temperature Control

- Supports USB-OTG Reverse Boost, up to 1.5A Current Limit

- Master-Slave Charging Capability, up to 6A Charge

Current

- Integrated Battery True-Disconnect FET

- Rated up to 9A<sub>RMS</sub>, Discharge Current Limit (Programmable)

- USB Type-C Detection

- Integrated V<sub>CONN</sub> Switch

- CC Pin

- D+/D- Detection for USB HVDCP

- BC 1.2 Support

- One Safeout LDO

- I<sup>2</sup>C-Compatible Interface

Ordering Information appears at end of data sheet.

# USB Type-C, 3A Switch-Mode Buck Charger with Integrated CC Detection, Reverse Boost, and ADC

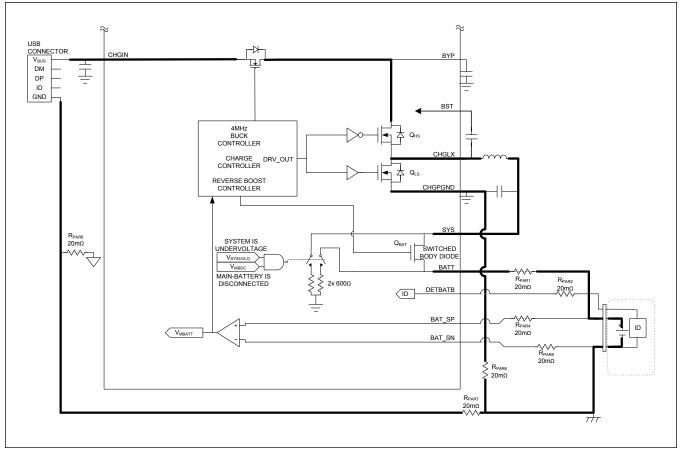

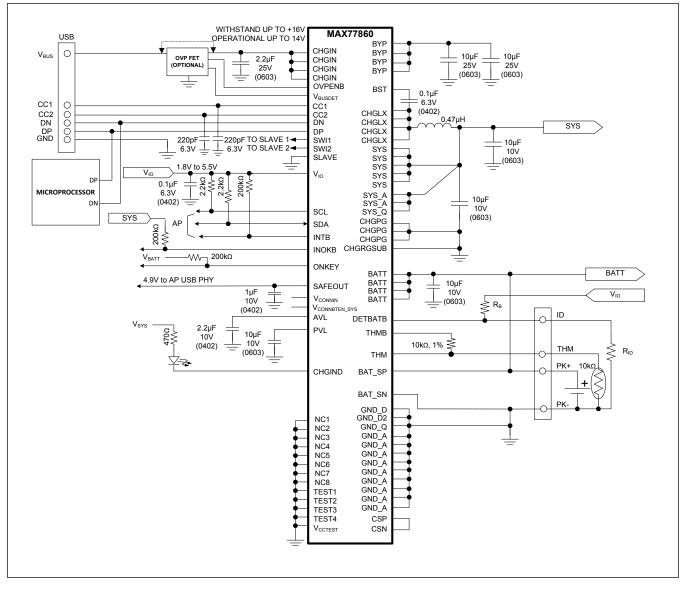

#### **Simplified Block Diagram**

USB Type-C, 3A Switch-Mode Buck Charger with Integrated CC Detection, Reverse Boost, and ADC

#### TABLE OF CONTENTS

| General Description                                                   |   |

|-----------------------------------------------------------------------|---|

| Applications                                                          |   |

| Benefits and Features                                                 |   |

| Simplified Block Diagram                                              |   |

| Absolute Maximum Ratings                                              | i |

| Package Information                                                   | i |

| 81-WLP                                                                | i |

| Electrical Characteristics                                            | ł |

| Electrical Characteristics—Charger                                    |   |

| Electrical Characteristics—SAFEOUT LDO 21                             |   |

| Electrical Characteristics—SAR ADC 21                                 |   |

| Electrical Characteristics—USB Type-C 22                              |   |

| Typical Operating Characteristics    27                               | • |

| Pin Configuration                                                     | i |

| MAX77860                                                              | i |

| Pin Description                                                       | I |

| Functional Diagrams                                                   |   |

| Functional Block Diagram    32                                        |   |

| Detailed Description                                                  | j |

| Switching Charger                                                     | , |

| Features                                                              | j |

| USB Data Contact Detection                                            |   |

| DP and DN                                                             |   |

| Adapter Detection                                                     |   |

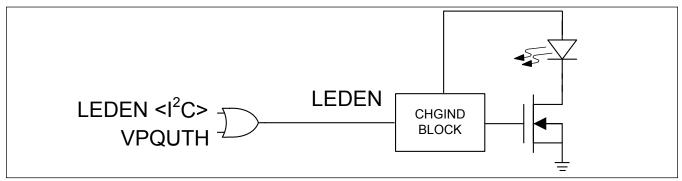

| Charging Status Indicator                                             | ì |

| External Input OVP Driver                                             | ì |

| Input Current Limit                                                   | ì |

| Input-Voltage Regulation Loop and Adaptive Input Current Limit (AICL) | i |

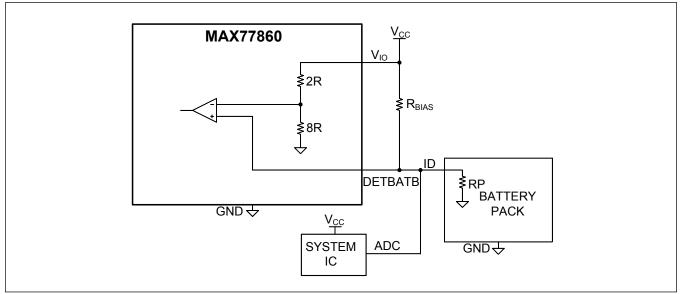

| Battery Detect Input Pin (MDETBATB) 36                                | i |

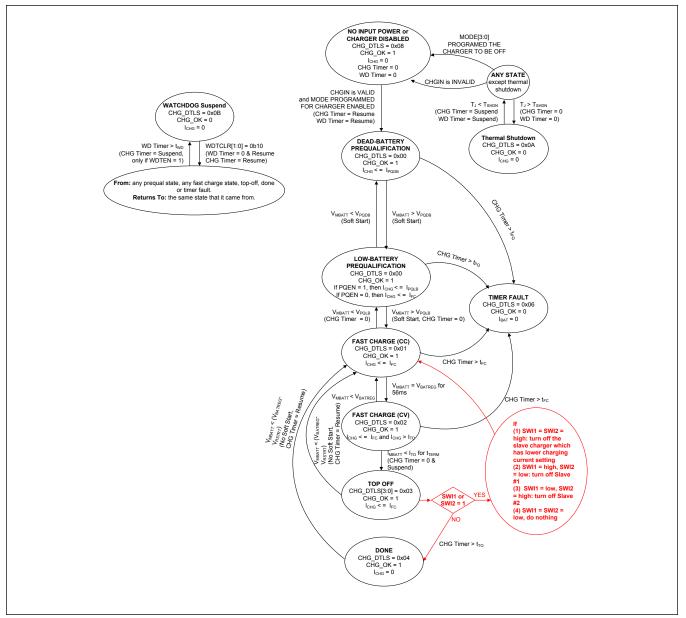

| Charge States                                                         | • |

| Dead-Battery Prequalification State 39                                | I |

| Fast-Charge Constant Current State                                    | I |

| Topoff State                                                          | I |

| Done State                                                            | I |

| Timer Fault State                                                     | I |

| Watchdog Timer                                                        |   |

| Thermal Shutdown State                                                | , |

| Main Battery Differential Voltage Sense    45                         | , |

USB Type-C, 3A Switch-Mode Buck Charger with Integrated CC Detection, Reverse Boost, and ADC

### **TABLE OF CONTENTS (CONTINUED)**

USB Type-C, 3A Switch-Mode Buck Charger with Integrated CC Detection, Reverse Boost, and ADC

#### LIST OF FIGURES

| Figure 1. Charging Status Indicator.                    | 35 |

|---------------------------------------------------------|----|

| Figure 2. DETBATB Internal Circuitry and System Diagram | 36 |

| Figure 3. Charger State Diagram                         | 37 |

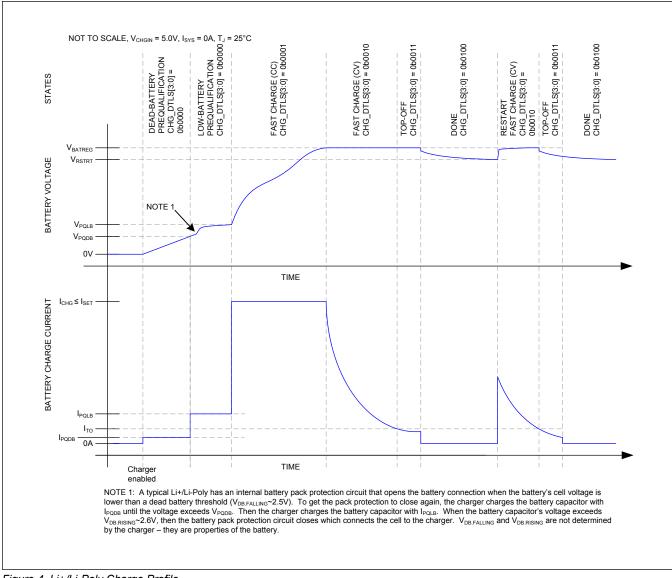

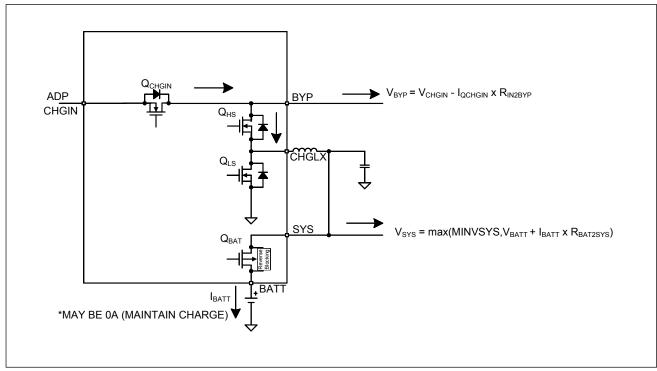

| Figure 4. Li+/Li-Poly Charge Profile                    | 38 |

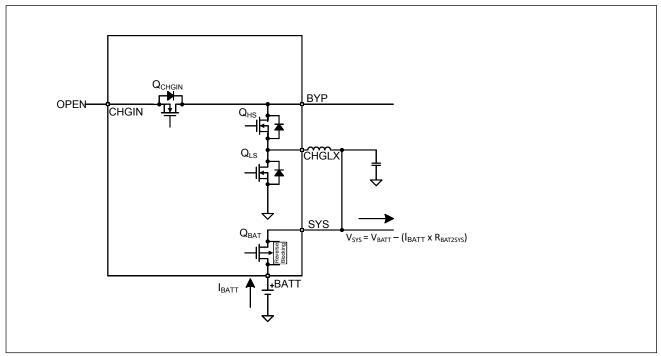

| Figure 5. Battery Only                                  | 41 |

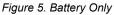

| Figure 6. Battery-Boost                                 | 42 |

| Figure 7. Battery-Boost (OTG)                           | 42 |

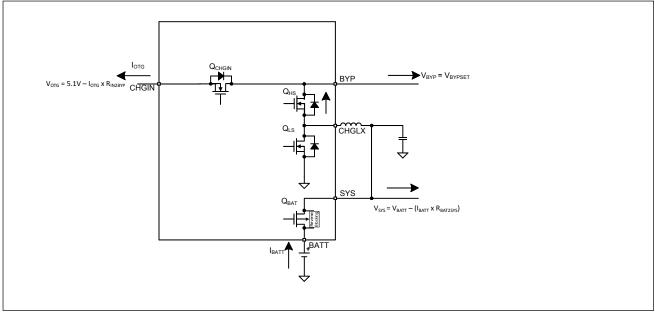

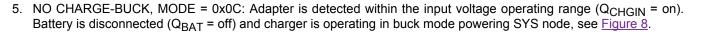

| Figure 8. No Charge-Buck                                | 43 |

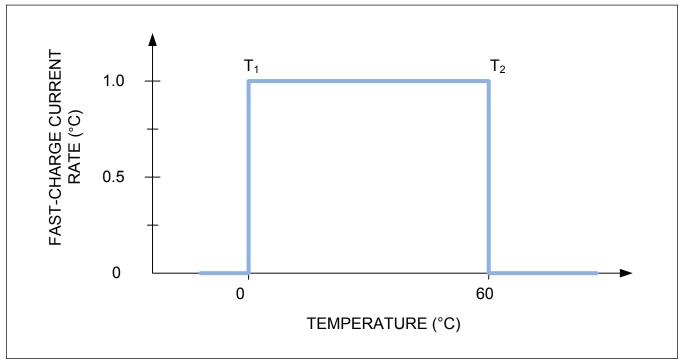

| Figure 9. Charge-Buck                                   | 44 |

| Figure 10. Thermal Shutdown Regions                     | 45 |

| Figure 11. Schematic with Parasitic Capacitances        | 46 |

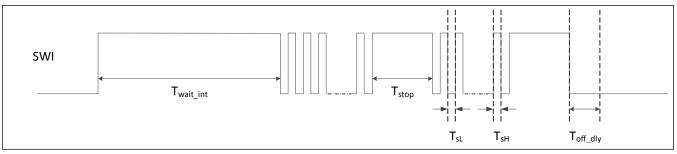

| Figure 12. S-Wire Timing Diagram                        | 48 |

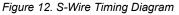

| Figure 13. SW1 and SW2 Transmission                     | 48 |

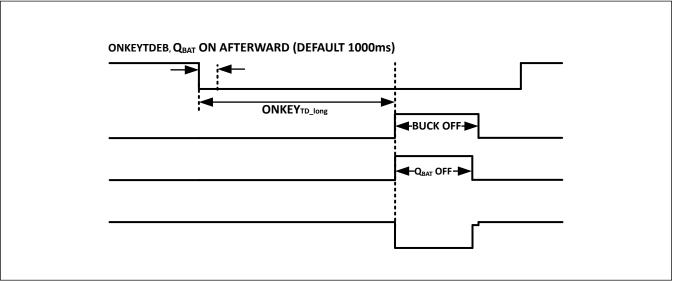

| Figure 14. ONKEY Timing Diagram                         | 49 |

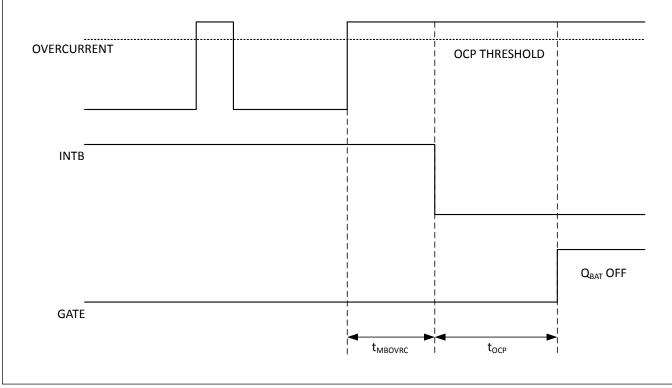

| Figure 15. Overcurrent Protection Timing Diagram.       | 50 |

USB Type-C, 3A Switch-Mode Buck Charger with Integrated CC Detection, Reverse Boost, and ADC

#### LIST OF TABLES

| Table 1. Supported Adapter Types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2. Top Level Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48 |

| Table 3. Functional Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48 |

| Table 4. PMIC Register (0x20)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53 |

| Table 5. Interrupt Source (0x22)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 53 |

| Table 6. Interrupt Source Mask (0x23)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53 |

| Table 7. SYSTEM Interrupt (0x24)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 54 |

| Table 8. SYSTEM Interrupt Source Mask (0x26)         Control         Contro         Control <thcontrol< th=""></thcontrol<> | 54 |

| Table 9. SAFEOUT Control Register (0xC6).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55 |

| Table 10. Charger Interrupt (0xB0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 56 |

| Table 11. Charger Interrupt Mask (0xB1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57 |

| Table 12. Charger Status (0xB2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 58 |

| Table 13. Charger Details 00 (0xB3).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59 |

| Table 14. Charger Details 01 (0xB4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60 |

| Table 15. Charger Details 02 (0xB5).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 62 |

| Table 16. Charger Configuration 00 (0xB7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 63 |

| Table 17. Charger Configuration 01 (0xB8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64 |

| Table 18. Charger Configuration 02 (0xB9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65 |

| Table 19. Charger Configuration 03 (0xBA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65 |

| Table 20. Charger Configuration 04 (0xBB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66 |

| Table 21. Charger Configuration 05 (0xBC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 66 |

| Table 22. Charger Configuration 06 (0xBD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67 |

| Table 23. Charger Configuration 07 (0xBE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67 |

| Table 24. Charger Configuration 09 (0xC0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 69 |

| Table 25. Charger Configuration 10 (0xC1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 70 |

| Table 26. Charger Configuration 11 (0xC2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71 |

| Table 27. Charger Configuration 12 (0xC3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 72 |

| Table 28. BC_INT (0x00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72 |

| Table 29. CC_INT (0x01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73 |

| Table 30. BC_INTMASK (0x02)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73 |

| Table 31. CC_INTMASK (0x03)         Output         Output <td>73</td>                                        | 73 |

| Table 32. BC_STATUS1 (0x04)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 74 |

| Table 33. BC_STATUS2 (0x05)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 74 |

| Table 34. CC_STATUS1 (0x06)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 74 |

| Table 35. CC_STATUS2 (0x07)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 75 |

| Table 36. BC_CTRL1 (0x08)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 75 |

| Table 37. BC_CTRL2 (0x09)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 75 |

| Table 38. CC_CTRL1 (0x0A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 76 |

USB Type-C, 3A Switch-Mode Buck Charger with Integrated CC Detection, Reverse Boost, and ADC

#### LIST OF TABLES (CONTINUED)

| Table 39. CC_CTRL2 (0x0B)              | 77   |

|----------------------------------------|------|

| Table 40. CC_CTRL3 (0x0C)              | 77   |

| Table 41. CHGIN_ILIM1 (0x0D)           | 77   |

| Table 42. CHGIN_ILIM2 (0x0E)           | 78   |

| Table 43. S-Wire Interrupt (0x80)      | 78   |

| Table 44. S-Wire Interrupt Mask (0x81) | 79   |

| Table 45. Slave Charger 1 CC (0x82)    | 79   |

| Table 46. Slave Charger 2 CC (0x83)    | 80   |

| Table 47. S-Wire 1 Readback (0x84)     | 80   |

| Table 48. S-Wire 2 Readback (0x85)     | 81   |

| Table 49. S-Wire Status (0x86)         | 81   |

| Table 50. ADC_CONFIG1 (0x50)           | 81   |

| Table 51. ADC_CONFIG2 (0x51)           | 82   |

| Table 52. ADC_CONFIG3 (0x52)           | 82   |

| Table 53. ADC_DATA_CH0 (0x53)          | 83   |

| Table 54. ADC_DATA_CH1 (0x54)          | 83   |

| Table 55. ADC_DATA_CH2 (0x55)          | 83   |

| Table 56. ADC_DATA_CH3 (0x56)          | . 84 |

| Table 57. ADC_DATA_CH4 (0x57)          | . 84 |

| Table 58. ADC_DATA_CH5 (0x58)          | . 84 |

| Table 59. ADC_DATA_CH6 (0x59)          | . 84 |

| Table 60. ADC_DATA_CH7 (0x5A)          | . 84 |

| Table 61. ADC_OFFSET_CH1 (0x5B)        | 85   |

| Table 62. ADC_OFFSET_CH3 (0x5C)        | 85   |

| Table 63. ADC_OFFSET_CH4 (0X5D)        | 86   |

|                                        |      |

# USB Type-C, 3A Switch-Mode Buck Charger with Integrated CC Detection, Reverse Boost, and ADC

#### **Absolute Maximum Ratings**

| Operating Junction Temperature (T <sub>J</sub> ) Range40°C to +85° | °C BYF             |

|--------------------------------------------------------------------|--------------------|

| Junction Temperature (T <sub>J</sub> ) Range40°C to +150°          |                    |

| Storage Temperature Range40°C to +150°                             |                    |

| Soldering Temperature (reflow)+260°                                |                    |

| Switching Charger                                                  | ON                 |

| CHGIN to GND0.3V to 16                                             | SV SW              |

| BYP to GND0.3V to 16                                               | SV SW              |

| PVL to GND0.3V to 6                                                | SV CHO             |

| AVL to GND0.3V to 6                                                |                    |

| BAT_SP to GND0.3V, BATT - 0.3V to 6V, BATT + 0.3                   | BV SAF             |

| BATT to GND0.3V to 6                                               |                    |

| SYS to GND0.3V to 6                                                | SV DP,             |

| DETBATB to GND0.3V to V <sub>IO</sub> + 0.3                        |                    |

| V <sub>BUSDET</sub> to GND0.3V to 20                               | V V <sub>CC</sub>  |

| OVPENB to GND0.3V to AVL + 0.3                                     | BV V <sub>CC</sub> |

| BST to PVL0.3V to 16                                               | SV ADC             |

| BST to CHGLX0.3V to 6                                              | SV THN             |

| INOKB to GND0.3V to SYS + 0.3                                      |                    |

| BAT_SN to GND0.3V to 0.3                                           | BV V <sub>IO</sub> |

| CHGPG to GND0.3V to 0.3                                            |                    |

| CHGLX Continuous Current                                           |                    |

| CHGPG Continuous Current                                           |                    |

| SYS Continuous Current4.5A <sub>RN</sub>                           |                    |

| BATT Continuous Current4.5A <sub>RN</sub>                          |                    |

| CHGIN Continuous Current 3A <sub>RN</sub>                          | /IS                |

|                                                                    |                    |

| BYP Continuous Current       3A <sub>RMS</sub> CSP to GND       -0.3V, BATT - 0.3V to 6V, BATT + 0.3V         CSN to GND       -0.3V, BATT - 0.3V to 6V, BATT + 0.3V         SLAVE to GND       -0.3V to SYS_A + 0.3V         ONKEY to GND       -0.3V to BATT + 0.3V         SWI1 to GND       -0.3V to SYS_A + 0.3V         SWI2 to GND       -0.3V to SYS_A + 0.3V |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CHGIND to GND0.3V to AVL + 0.3V                                                                                                                                                                                                                                                                                                                                       |  |

| Safeout LDO                                                                                                                                                                                                                                                                                                                                                           |  |

| SAFEOUT to GND0.3V to 6V, CHGIN + 0.3V                                                                                                                                                                                                                                                                                                                                |  |

| JSB Type-C                                                                                                                                                                                                                                                                                                                                                            |  |

| DP, DN to GND0.3V to $V_{CCINT}$ + 0.3V                                                                                                                                                                                                                                                                                                                               |  |

| CC1, CC2 to GND0.3V to V <sub>CCINT</sub> + 0.3V                                                                                                                                                                                                                                                                                                                      |  |

| V <sub>CONNIN</sub> to GND0.3V to V <sub>CCINT</sub> + 0.3V                                                                                                                                                                                                                                                                                                           |  |

| V <sub>CONNBTEN SYS</sub> to GND0.3V to 6V                                                                                                                                                                                                                                                                                                                            |  |

| ADC –                                                                                                                                                                                                                                                                                                                                                                 |  |

| THMB, THM to GND0.3V to BATT + 0.3V                                                                                                                                                                                                                                                                                                                                   |  |

| <sup>2</sup> C and Interface Logic                                                                                                                                                                                                                                                                                                                                    |  |

| V <sub>IO</sub> to GND0.3V to 6V                                                                                                                                                                                                                                                                                                                                      |  |

| SDA, SCL to GND0.3V to $V_{IO}$ + 0.3V                                                                                                                                                                                                                                                                                                                                |  |

| SYS_A, SYS_Q to GND0.3V to 6V                                                                                                                                                                                                                                                                                                                                         |  |

| INTB0.3V to SYS_A + 0.3V                                                                                                                                                                                                                                                                                                                                              |  |

| TEST_, V <sub>CCTEST</sub> to GND                                                                                                                                                                                                                                                                                                                                     |  |

| GND_ to GND0.3V to 0.3V                                                                                                                                                                                                                                                                                                                                               |  |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 81-WLP

| Package Code                           | W813C3+1                       |  |  |  |

|----------------------------------------|--------------------------------|--|--|--|

| Outline Number                         | <u>21-0775</u>                 |  |  |  |

| Land Pattern Number                    | Refer to Application Note 1891 |  |  |  |

| Thermal Resistance, Four-Layer Board:  |                                |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 49°C/W                         |  |  |  |

| Junction to Case $(\theta_{JC})$       | N/A                            |  |  |  |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

# USB Type-C, 3A Switch-Mode Buck Charger with Integrated CC Detection, Reverse Boost, and ADC

### **Electrical Characteristics**

$(V_{SYS} = +3.6V, V_{CHGIN} = 0V, V_{IO} = 1.8V, T_A = -40^{\circ}C$  to +85°C, typical value for  $T_A$  is +25°C. Limits are 100% tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Typical values are not guaranteed.)

| PARAMETER                             | SYMBOL                | CONDITIONS                                                                                       | MIN                   | TYP                       | MAX                   | UNITS |

|---------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------|-----------------------|---------------------------|-----------------------|-------|

| SUPPLY CURRENT                        |                       |                                                                                                  | •                     |                           |                       |       |

| Shutdown Supply<br>Current (BATT)     | ISHDN                 | All circuits off, BATT = 3.6V                                                                    |                       | 25                        | 50                    | μA    |

| No Load Supply Current<br>(BATT)      | I <sub>NL</sub>       | USB Type-C on, all other circuits off,<br>BATT = 3.6V                                            |                       | 90                        | 150                   | μA    |

| SYS INPUT RANGE                       |                       | ·                                                                                                | •                     |                           |                       |       |

| SYS Undervoltage<br>Lockout Threshold | VSYS_UVLO             | V <sub>BATT</sub> falling, 200mV hysteresis                                                      | 2.4                   | 2.5                       | 2.6                   | V     |

| SYS Overvoltage<br>Lockout Threshold  | V <sub>SYS_OVLO</sub> | V <sub>BATT</sub> rising, 200mV hysteresis                                                       | 5.2                   | 5.36                      | 5.52                  | V     |

| Low SYS Thresholds                    |                       | Range programmable through LSDAC register, $V_{SYS}$ falling, production tested at 3.60V setting |                       | 3.6                       |                       | V     |

| Low SYS Hysteresis                    |                       | Range programmable through LSHYST register, production tested at 100mV setting                   |                       | 100                       |                       | mV    |

| THERMAL SHUTDOWN                      |                       |                                                                                                  |                       |                           |                       |       |

| Thermal Shutdown<br>Threshold         | T <sub>SHDN</sub>     | T <sub>J</sub> rising                                                                            |                       | 165                       |                       | °C    |

| Thermal Shutdown<br>Hysteresis        |                       |                                                                                                  |                       | 15                        |                       | °C    |

| Thermal Interrupt 1                   |                       |                                                                                                  |                       | 120                       |                       | °C    |

| Thermal Interrupt 2                   |                       |                                                                                                  |                       | 140                       |                       | °C    |

| LOGIC AND CONTROL I                   | NPUTS                 |                                                                                                  |                       |                           |                       |       |

| SCL, SDA Input Low<br>Level           |                       | T <sub>A</sub> = +25°C                                                                           |                       |                           | 0.3 x V <sub>IO</sub> | V     |

| SCL, SDA Input High<br>Level          |                       | T <sub>A</sub> = +25°C                                                                           | 0.7 x V <sub>IO</sub> |                           |                       | V     |

| SCL, SDA Input<br>Hysteresis          |                       | T <sub>A</sub> = +25°C                                                                           |                       | 0.05 x<br>V <sub>IO</sub> |                       | V     |

| SCL, SDA Logic Input<br>Current       |                       | V <sub>IO</sub> = 3.6V                                                                           | -10                   |                           | +10                   | μA    |

| SCL, SDA Input<br>Capacitance         |                       | (Note 1)                                                                                         |                       | 10                        |                       | pF    |

| SDA Output Low<br>Voltage             |                       | Sinking 20mA                                                                                     |                       |                           | 0.4                   | V     |

| Output Low Voltage<br>(INTB)          |                       | I <sub>SINK</sub> = 1mA                                                                          |                       |                           | 0.4                   | V     |

| Output High Leakage                   |                       | V <sub>SYS</sub> = 5.5V, T <sub>A</sub> = +25°C                                                  | -1                    | 0                         | +1                    |       |

| (INTB)                                |                       | V <sub>SYS</sub> = 5.5V, T <sub>A</sub> = +85°C                                                  |                       | 0.1                       |                       | μA    |

| Interrupt Debounce<br>Filter Timer    |                       | LOWSYS                                                                                           |                       | 16                        |                       | ms    |

# USB Type-C, 3A Switch-Mode Buck Charger with Integrated CC Detection, Reverse Boost, and ADC

### **Electrical Characteristics (continued)**

$(V_{SYS} = +3.6V, V_{CHGIN} = 0V, V_{IO} = 1.8V, T_A = -40^{\circ}C$  to +85°C, typical value for  $T_A$  is +25°C. Limits are 100% tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Typical values are not guaranteed.)

| PARAMETER                                                                  | SYMBOL              | CONDITIONS                        | MIN          | TYP   | MAX  | UNITS |

|----------------------------------------------------------------------------|---------------------|-----------------------------------|--------------|-------|------|-------|

| I <sup>2</sup> C-COMPATIBLE INTER                                          | FACE TIMING         | FOR STANDARD, FAST, AND FAST-MO   | DDE PLUS (No | te 1) |      | 1     |

| Clock Frequency                                                            | f <sub>SCL</sub>    |                                   |              |       | 1000 | kHz   |

| Hold Time (Repeated)<br>START Condition                                    | <sup>t</sup> HD;STA |                                   | 0.26         |       |      | μs    |

| CLK Low Period                                                             | tLOW                |                                   | 0.5          |       |      | μs    |

| CLK High Period                                                            | thigh               |                                   | 0.26         |       |      | μs    |

| Setup Time Repeated<br>START Condition                                     | <sup>t</sup> SU;STA |                                   | 0.26         |       |      | μs    |