#

# MAX9530

### Quad NTSC/PAL Decoder and Quad Audio Codec

#### **General Description**

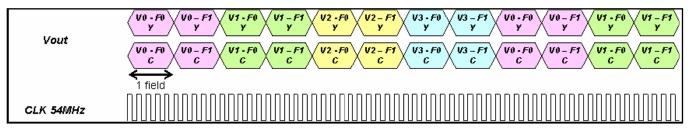

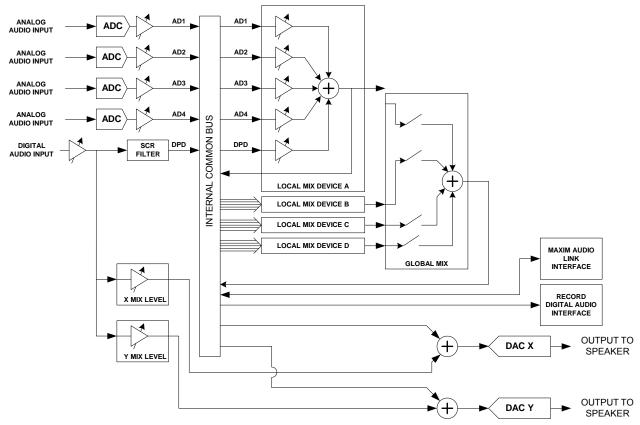

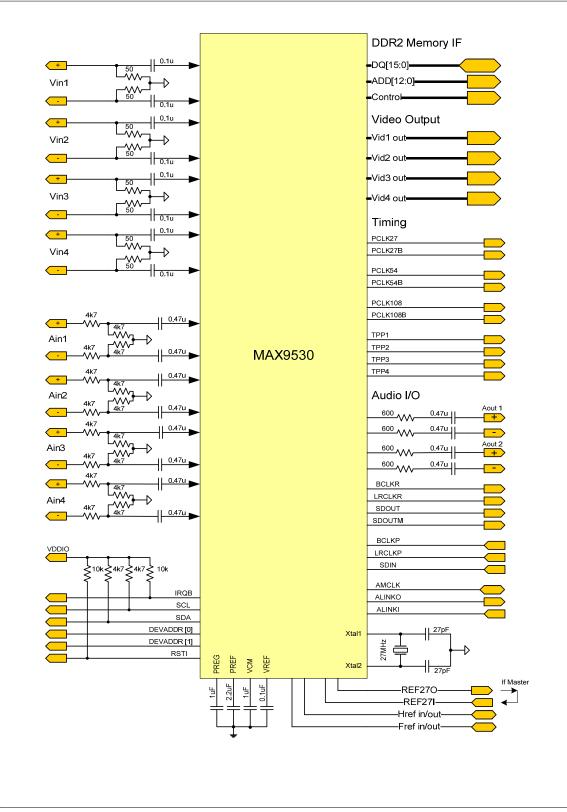

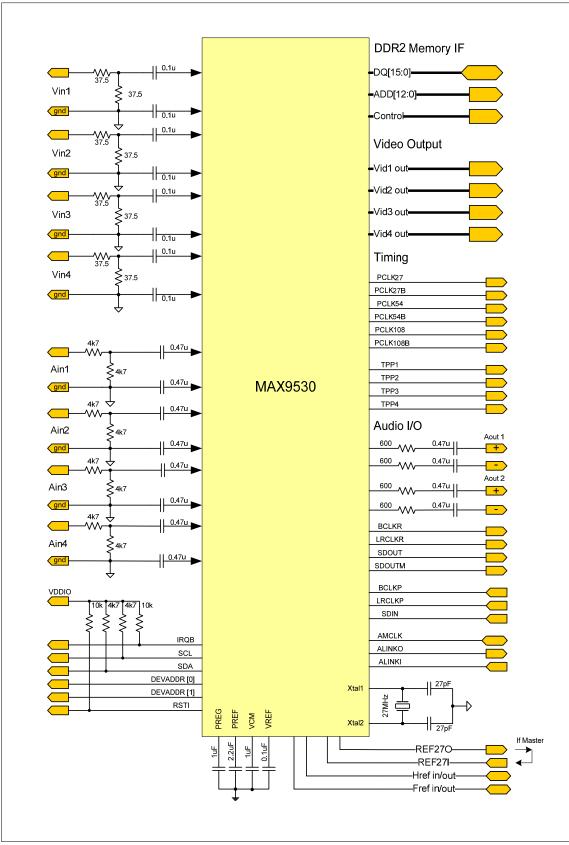

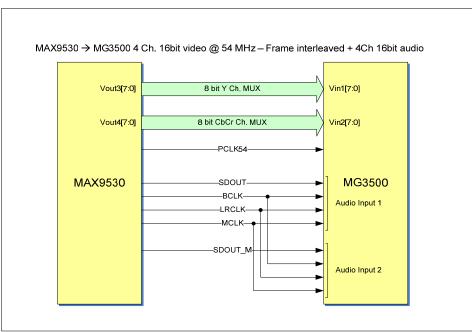

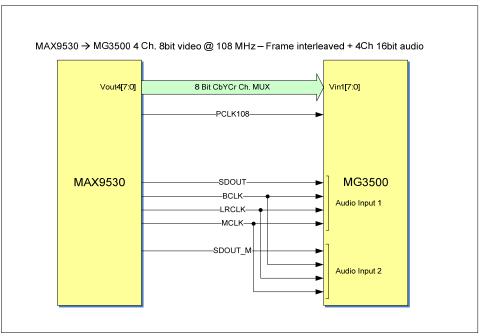

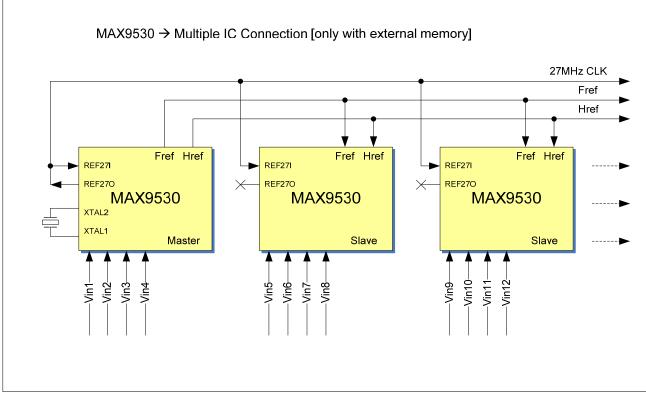

The MAX9530 is a quad-channel video decoder and audio codec for security & surveillance applications. The part is specially designed to serve as the front-end in multi-channel DVR (Digital Video Recorder) and DVS (Digital Video Streamer) systems. The architecture supports byte- or frame-interleaved digital video output for direct connection to a wide selection of multi-channel A/V media processors including Maxim's own H.264 codec family (i.e. MG3500 and later generations). The on-chip DDR2 memory controller enables output of frame-synchronized digital video from up to four asynchronous analog video inputs. Multiple devices can be configured to support an unlimited number of synchronized video streams. The use of external memory is optional. A memory bypass mode provides for output of up to four-channels of asynchronous video data in BT.656 digital component format.

The video signal path produces excellent video quality derived from four 54MHz/10-bit ADCs and a 5L comb filter bank. Differential or single-ended video and audio inputs are supported. The video input path includes a DC restore circuit, analog gain control, and anti-aliasing filter for each channel with no additional external components. Long cable connections are supported with the use of an adaptive equalizer block that automatically adjusts and compensates for high-frequency video signal losses in each channel independently. Each video channel can also be downscaled in high-quality for recording in lower resolution formats. All video capture operates from a unique "PLL-less" design, to ensure instant lock, and no loss of video content waiting for lock to occur with the incoming video.

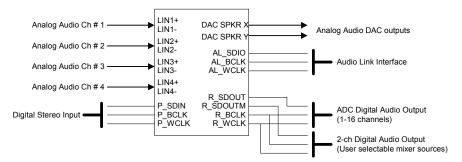

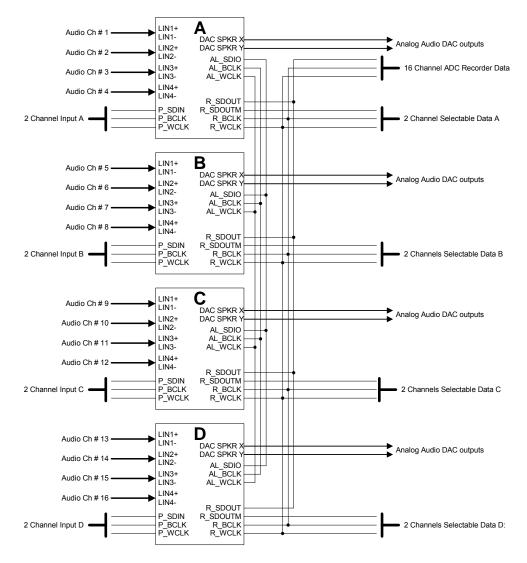

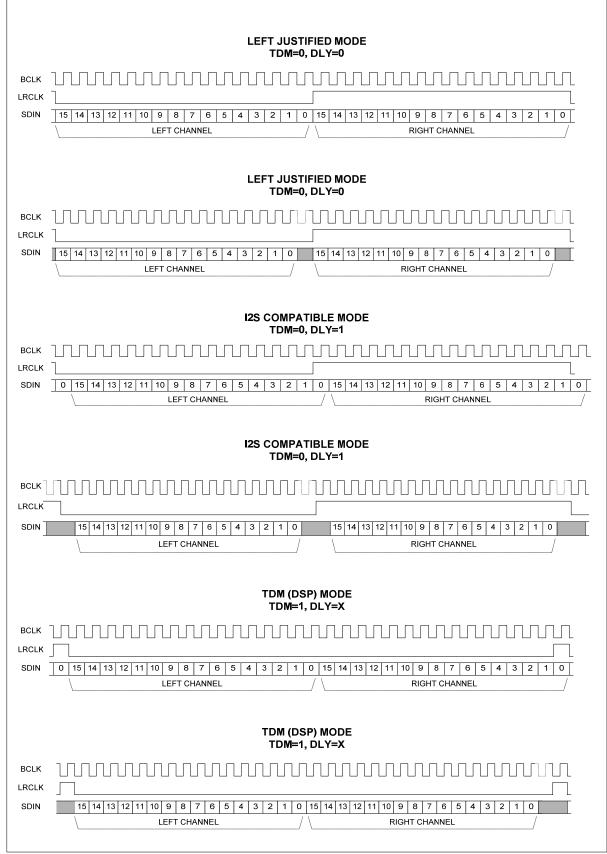

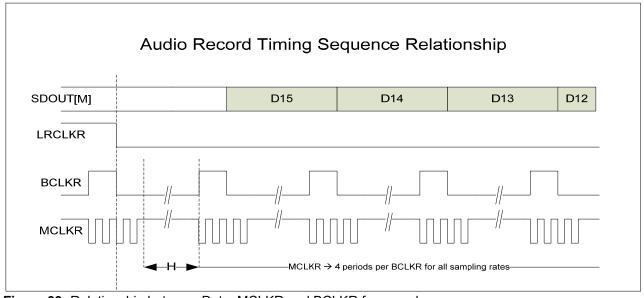

In addition, four mono audio channels are captured in 16-bit precision with programmable sample rates from 16 to 48kHz. Three independent I2S interfaces provide digital audio input/output for record, playback, and mixing operations. A separate inter-chip Audio Link bus allows cascaded operation for multi-channel systems with 8/16/etc. channel inputs. Two analog audio outputs are also provided.

The digital I/Os can operate from 1.7 to 3.6V.

#### Applications

Security Surveillance/CCTV Systems Digital Video Recorders (DVRs) Digital Video Streamers (IP Streaming)

#### Features

- Video Features:

- 4-ch Analog Video Decoder NTSC (M,J,4.43) or PAL(B,G,H,I,D,N,M,60)

- 4-ch Frame-Interleaved Output Synchronizer (optional with external DDR2 memory).

- Programmable 2D Video Scalers

- Independent Auto Cable EQ per Video Channel

- Instant Lock System for Video Capture

- Multi-Line Adaptive Comb Filters.

- 4x Oversampled 54MHz/10-bit Video ADC

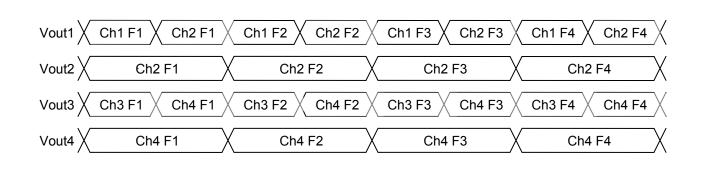

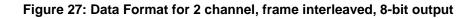

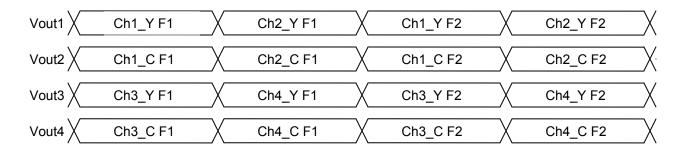

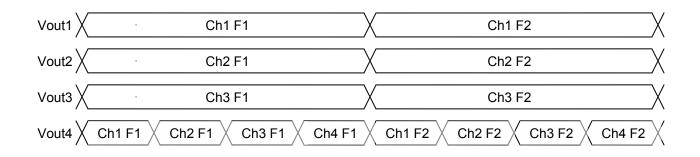

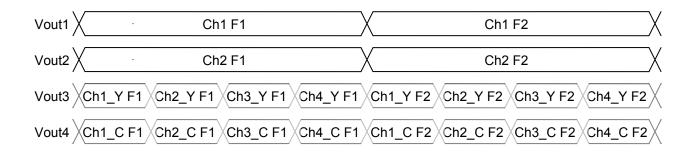

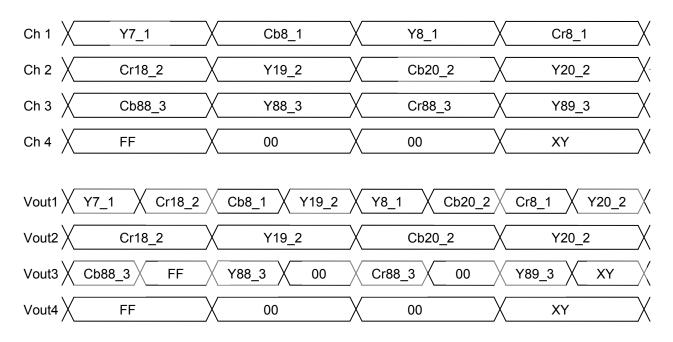

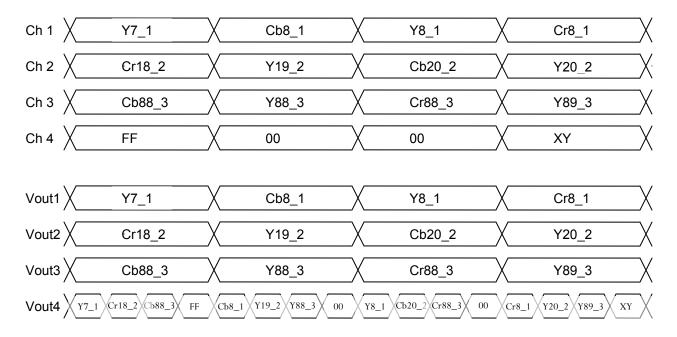

- Output formats Video - 4x8-bit non-interleaved or 2x2x8-bit / 1x4x8-bit interleaved

- DVR Multiplex Output: With DDR2 – Pixel or Frame Interleaved Without DDR2 – BT.656 Pixel Multiplex

- Audio Features:

- 4-ch Analog Audio Input (Mono)

- 48KHz/16 bit Audio ADC.

- 2-ch Analog Audio Output

- Differential or Single-Ended Analog Inputs

- I<sup>2</sup>C Interface

- 1400mW Typical Power Dissipation (w. DDR)

- ♦ 1.8V Analog Supply Voltage

- ♦ 1.8V Digital Core Supply Voltage

- 1.8V to 3.3V Digital I/O Voltage

- JTAG Support

#### Ordering Information

| PART        | INPUTS | PIN-PACKAGE |

|-------------|--------|-------------|

| MAX9530CXV+ | 4 + 4  | CSBGA 196   |

|             |        |             |

All devices specified over the 0°C to +70°C operating temperature range.

+ Denotes lead(Pb)-free/RoHS-compliant package.

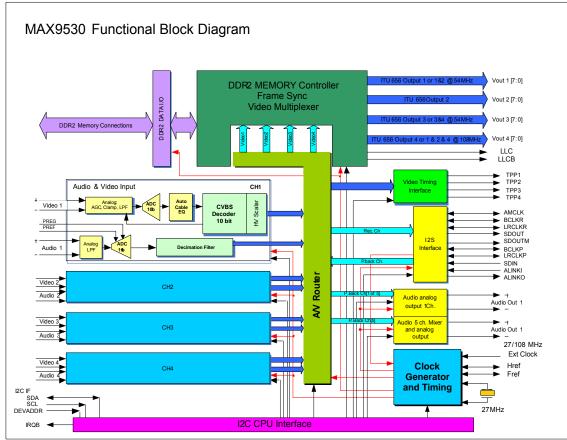

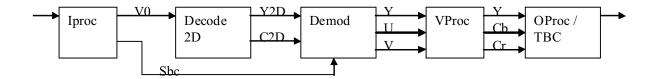

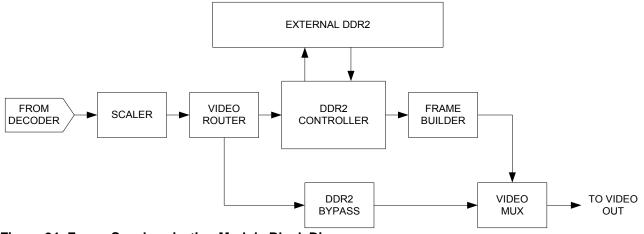

# 1. BLOCK DIAGRAM

Figure 1: MAX9530 Block Diagram

# 2. TABLE OF CONTENTS

# 3. ABSOLUTE MAXIMUM RATINGS

| Supply Voltages                                 |                      |

|-------------------------------------------------|----------------------|

| VDDA to GND                                     | 0.3V to +2V          |

| VDDD to GND                                     | 0.3V to +2V          |

| VDDIO to GND                                    | 0.3V to +3.6V        |

| Outputs                                         |                      |

| VOUT_<7:0>, PCLK_, TPP                          | 0.3V to (VDDIO+0.3V) |

| AOUT                                            | 0.3V to (VDDA+0.3V)  |

| PREG, REF, VCM                                  |                      |

| IRQB, SDA, TDO                                  | 0.3V to +3.6V        |

| Inputs                                          |                      |

| · VIN_, AIN                                     | 0.3V to (VDDA+0.3V)  |

| XTAL1, XTAL2                                    | 0.3V to (VDDA+0.3V)  |

| SDIN                                            |                      |

| SDA, SCL, DEVADDR<1:0>, TMS, TDI, TCK, JTAG_RST | 0.3V to +3.6V        |

| Input/Outputs                                   |                      |

| LRCLK_, BCLK_, SDOUT                            | 0.3V to (VDDIO+0.3V) |

| A<12:0>, DQ<15:0>, _DQS, RASB,                  |                      |

| CASB, WEB, CSB, _DM, CKE, CK_, ODT              | 0.3V to (VDDD+0.3V)  |

| Continuous Current                              |                      |

| All Pins                                                                 | . +/-50mA |

|--------------------------------------------------------------------------|-----------|

|                                                                          |           |

| Continuous Power Dissipation (TA = +70°C) 196 pin CSBGA Multilayer Board |           |

| (derate 20.8mW/C above +70C)                                             | 1860mW    |

| Operating Temperature Range         |        |

|-------------------------------------|--------|

| Junction Temperature                | +150°C |

| Storage Temperature Range           |        |

| Lead Temperature (soldering, 10sec) | +260°C |

**Note A**: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a 4-layer board. For detailed information on package thermal considerations see <u>www.maxim-ic.com/thermal-tutorial</u>

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# 4. ELECTRICAL CHARACTERISTICS: EC TABLE

(VDDA = VDDD = +1.8V, VDDIO = +3.3V, GND = 0V,  $T_A = 0^{\circ}C$  to 70°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                         | SYMBOL           | CONDITIONS                                                                                           |      | EC Table |      | UNITS |

|-----------------------------------|------------------|------------------------------------------------------------------------------------------------------|------|----------|------|-------|

|                                   |                  |                                                                                                      | MIN  | TYP      | MAX  |       |

| SUPPLIES                          |                  |                                                                                                      |      |          |      |       |

| Analog Supply Voltage Range       | VDDA             |                                                                                                      | 1.7  | 1.8      | 1.9  | V     |

| Digital Supply Voltage Range      | VDDD             |                                                                                                      | 1.7  | 1.8      | 1.9  | V     |

| Digital I/O Supply Voltage Range  | VDDIO            |                                                                                                      | 1.7  | 3.3      | 3.45 | V     |

| Analog Supply Current             |                  | Normal Operation (Note 2)                                                                            |      | 152      | 250  | mA    |

|                                   | IVDDA            | Shutdown (XTAL=0Hz)                                                                                  |      | 2        | 200  | μA    |

| Digital Supply Current            |                  | Normal Operation (Note 2)                                                                            |      | 344      | 490  | mA    |

|                                   | IVDDD            | Shutdown (XTAL=0Hz)                                                                                  |      | 50       | 1000 | μA    |

| Digital I/O Supply Current        |                  | Normal Operation (Note 2). VDDIO=1.8V                                                                |      | 52       |      | mA    |

|                                   |                  | Normal Operation (Note 2). VDDIO=3.3V                                                                |      | 150      |      | mA    |

|                                   |                  | Shutdown. DVDD_IO=3.3V (T <sub>A</sub> = 25°C)                                                       |      | 10       |      | μΑ    |

| ANALOG VIDEO INPUT                | •                | •                                                                                                    |      |          | •    |       |

| Video Input Reference (VREF)      | VREF             |                                                                                                      |      | 775      |      | mV    |

| Video Input Resistance            | RIN              |                                                                                                      |      | 2        |      | MΩ    |

| Video Input Capacitance           | CIN              |                                                                                                      |      | 8        |      | pF    |

| Diff. Video Input CMRR            | CMRRv            | Freq. range 0 $\rightarrow$ 5MHz                                                                     |      | 80       |      | dBFS  |

| Video Sync Level Adjust           |                  | Slow                                                                                                 | 2.1  | 3        | 3.9  |       |

| (Source and Sink Values)          |                  | Medium                                                                                               | 4.2  | 6        | 7.8  |       |

| (Note 6)                          |                  | Medium-Fast (default)                                                                                | 8    | 12       | 16   | μA    |

| DC Restore Current DAC Full Scale |                  | Fast                                                                                                 | 16.4 | 24       | 32   |       |

| Range (Source and Sink)           |                  | 1 431                                                                                                | 10.4 | 24       | 52   |       |

| ANALOG INPUT FILTER AND ADC (No   |                  | 1                                                                                                    |      |          | 1    |       |

| Video Passband Cutoff (3dB)       | F <sub>3dB</sub> |                                                                                                      |      | 13       |      | MHz   |

| Video Passband Flatness           |                  | f < F <sub>PB</sub> , V <sub>AIN</sub> = 0.65V <sub>P-P</sub><br>reference level is measured at 1MHz |      | 0.25     |      | dB    |

| Video Stopband Cutoff             | Fsb              |                                                                                                      |      | 53       |      | MHz   |

| Video Stopband Attenuation        |                  | $f > F_{SB}, V_{AIN} = 0.65V_{P-P}$<br>reference level is measured at 1MHz                           |      | 36       |      | dB    |

| PARAMETER                                              | SYMBOL                            | CONDITIO                                                        | ONS              |                                                                                 |      | EC Table |      | UNITS             |

|--------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------|------------------|---------------------------------------------------------------------------------|------|----------|------|-------------------|

|                                                        |                                   |                                                                 |                  | F                                                                               | MIN  | TYP      | MAX  |                   |

| Video Full-Scale Conversion                            |                                   | AGC Disabled, Gain<br>Programmed                                |                  | ADCGAIN=0x0                                                                     | 680  |          | 840  | mV <sub>pp</sub>  |

| Single End Input                                       |                                   | via I <sup>2</sup> C,Referenced to VINx<br>Gain Error=5%        |                  | ADCGAIN=0xF                                                                     | 280  |          | 340  | $mV_{pp}$         |

| Video Full-Scale Conversion<br>Differential Input      |                                   | AGC Disabled,<br>Gain Programmed<br>via I²C, Referenced to VINx |                  | ADCGAIN=0x0                                                                     | 1370 |          | 1690 | mV <sub>pp</sub>  |

|                                                        |                                   | Gain Error=5%                                                   |                  | ADCGAIN=0xF                                                                     | 550  |          | 670  | $mV_{pp}$         |

| Video AGC Step Size                                    |                                   |                                                                 |                  |                                                                                 |      | 0.150    |      | V/V               |

| ADC Clock Rate                                         | Fadc                              |                                                                 |                  |                                                                                 |      | 54       |      | MHz               |

| ADC Resolution                                         | ADCR                              |                                                                 |                  |                                                                                 |      | 10       |      | Bits              |

| Video DC differential nonlinearity                     | DNL                               |                                                                 |                  |                                                                                 |      | ±0.5     |      | LSB               |

| Video DC integral nonlinearity                         | INL                               |                                                                 |                  |                                                                                 |      | ±1       |      | LSB               |

| Video Signal-to-RMS noise ratio                        |                                   |                                                                 |                  |                                                                                 |      |          |      |                   |

| (Includes filter + ADC + digital anti-aliasing filter) | SNR                               | Luminance Flat Field -50%                                       | • •              |                                                                                 |      | 56       |      | dB                |

| Video Power Supply Rejection                           | PSRV                              | ADCGAIN[3:0]=0x0 1<br>$T_A = +25^{\circ}C$ 1                    | 1.7V<\<br>1.7V<\ | / <sub>VDDA</sub> <1.9V<br>/ <sub>VDDD</sub> <1.9V<br>/ <sub>VDDIO</sub> <3.45V | 33   |          |      | dBFS              |

| Video Differential Phase                               | DP                                | 5 step Modulated Staircase,<br>f =3.58MHz or 4.43MHz            |                  |                                                                                 | 1.0  |          | Deg. |                   |

| Video Differential Gain                                | DG                                | 5 step Modulated Staircase,<br>f =3.58MHz or 4.43MHz            |                  |                                                                                 | 1    |          | %    |                   |

| Video 2T Pulse Response                                |                                   | 2T = 200ns<br>2T = 250ns                                        |                  |                                                                                 | 0.2  |          | K%   |                   |

| Crosstalk                                              |                                   | Between video channels<br>Between audio input chann             | nels             |                                                                                 |      | 70<br>90 |      | dB                |

| DECODED LUMINANCE and CHROMINAN                        | ICE                               |                                                                 |                  |                                                                                 |      |          |      |                   |

| Video Chrominance Bandwidth                            | BWc                               |                                                                 |                  |                                                                                 |      | 1.0      |      | MHz               |

| Video Luminance Bandwidth                              | BW∟                               |                                                                 |                  |                                                                                 |      | 5.5      |      | MHz               |

| Video Luminance Non-Linearity                          |                                   | 5-step staircase                                                |                  |                                                                                 |      | 1.0      |      | %                 |

| Chroma Amplitude error                                 |                                   |                                                                 |                  |                                                                                 |      | 1        |      | %                 |

| Chroma Phase Error                                     |                                   |                                                                 |                  |                                                                                 |      | +/- 1    |      | deg               |

| Video Horizontal Line Time Static Variation            |                                   |                                                                 |                  |                                                                                 |      | 1.5      |      | %                 |

| Video Maximum Horizontal Line Time Jitter              |                                   |                                                                 |                  |                                                                                 |      | 8        |      | μs                |

| Video Input Signal<br>Minimum Peak Signal to RMS Noise |                                   |                                                                 | 3&W S<br>Color S |                                                                                 |      | 12<br>18 |      | dB                |

| CLOCK GENERATOR                                        |                                   |                                                                 |                  |                                                                                 |      |          |      |                   |

| Video Clock Jitter                                     |                                   |                                                                 |                  |                                                                                 |      | 400      |      | ps <sub>p-p</sub> |

| CRYSTAL OSCILLATOR (XTAL1, XTAL2)                      |                                   |                                                                 |                  |                                                                                 |      |          |      |                   |

| Frequency                                              |                                   | Fundamental Mode Only                                           |                  |                                                                                 |      | 27.0000  |      | MHz               |

| XTAL1, XTAL2 Input Capacitance                         | Cxtal1,<br>Cxtal2                 |                                                                 |                  |                                                                                 | 4    |          | pF   |                   |

| Maximum Load Capacitor                                 | C <sub>L1</sub> , C <sub>L2</sub> |                                                                 |                  |                                                                                 |      | 45       |      | pF                |

| Frequency Accuracy                                     | ·                                 |                                                                 |                  |                                                                                 |      | ±50      |      | ppm               |

| Maximum Input Clock Jitter                             |                                   | External Clock                                                  |                  |                                                                                 |      | 600      |      | pspp              |

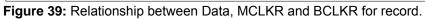

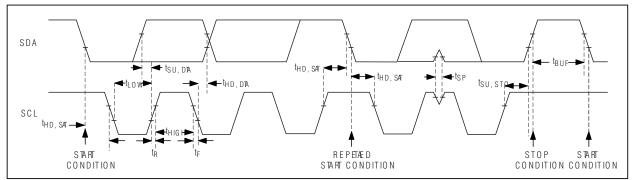

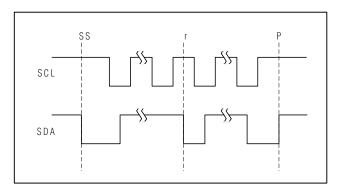

| I <sup>2</sup> C SERIAL INTERFACE (SDA, SCL)           | 1                                 |                                                                 |                  |                                                                                 |      |          |      | 1 1 44            |

| Serial Clock Frequency                                 | f <sub>SCL</sub>                  |                                                                 |                  |                                                                                 | 0    |          | 400  | kHz               |

| Bus Free Time Between STOP and                         | tBUF                              |                                                                 |                  |                                                                                 |      |          | 100  |                   |

| START Conditions                                       | UUF                               |                                                                 |                  |                                                                                 | 1.3  |          |      | μs                |

| PARAMETER                             | PARAMETER SYMBOL CONDITIONS      |                                                                                                                                                                        |                      | EC Table    |                  | UNITS |  |

|---------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------|------------------|-------|--|

|                                       |                                  |                                                                                                                                                                        | MIN                  | TYP         | MAX              |       |  |

| Hold Time (repeated) START Condition. | thd,sta                          |                                                                                                                                                                        | 0.6                  |             |                  | μs    |  |

| SCL Pulse Width Low                   | tLOW                             |                                                                                                                                                                        | 1.3                  |             |                  | μs    |  |

| SCL Pulse Width High                  | thigh                            |                                                                                                                                                                        | 0.6                  |             |                  | μs    |  |

| Setup Time for a Repeated START       | t <sub>SU,STA</sub>              |                                                                                                                                                                        |                      |             |                  |       |  |

| Condition                             | 100,017                          |                                                                                                                                                                        | 0.6                  |             |                  | μs    |  |

| Data Hold Time                        | thd,dat                          |                                                                                                                                                                        | 0                    |             | 900              | ns    |  |

| Data Setup Time                       | tsu,dat                          |                                                                                                                                                                        | 100                  |             |                  | ns    |  |

| SDA and SCL Receiving Rise Time       | tr                               | Note 3                                                                                                                                                                 | 20+0.1C <sub>B</sub> |             | 300              | ns    |  |

| SDA and SCL Receiving Fall Time       | tr                               | Note 3                                                                                                                                                                 | 20+0.1C <sub>B</sub> |             | 300              | ns    |  |

| SDA Transmitting Fall Time            | tr                               |                                                                                                                                                                        | 20+0.1C <sub>B</sub> |             | 500              | ns    |  |

| Setup Time for STOP Condition         | t <sub>SU,STO</sub>              |                                                                                                                                                                        | 0.6                  |             | 000              | μs    |  |

| Bus Capacitance                       | CB                               |                                                                                                                                                                        | 0.0                  |             | 400              | pF    |  |

| Pulse Width of Suppressed Spike       | t <sub>SP</sub>                  |                                                                                                                                                                        | 0                    |             | 50               |       |  |

|                                       | -                                |                                                                                                                                                                        | -                    |             | 50               | ns    |  |

|                                       |                                  |                                                                                                                                                                        | JIO_AL)              |             | 0.4              | V     |  |

| Output Low Voltage                    | Vol                              | $I_{OL} = 2mA, ODS = 01$                                                                                                                                               |                      |             | 0.4              | V     |  |

| Output High Voltage                   | Vон                              | I <sub>OH</sub> = 2mA, ODS = 01                                                                                                                                        | VDDIO –<br>0.4V      |             |                  | V     |  |

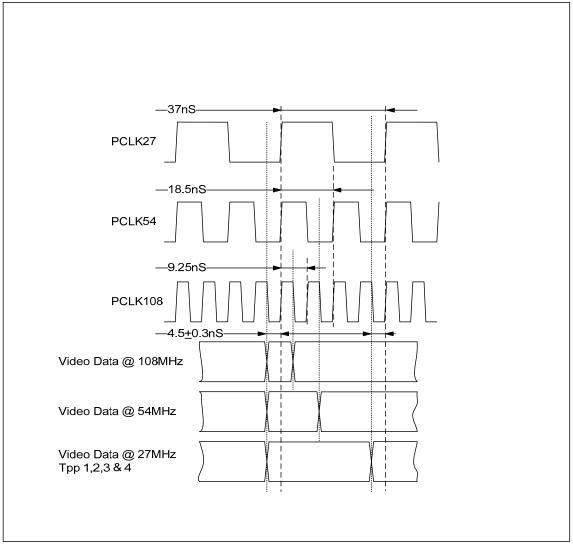

| Data to Clock Rising Edge Hold Time   |                                  | VID_<7:0> to PCLK27, ODS = 01                                                                                                                                          |                      | 32.41       |                  |       |  |

|                                       | tнD                              | VID_<7:0> to PCLK54, ODS = 01                                                                                                                                          |                      | 13.89       |                  | ns    |  |

|                                       |                                  | VID_<7:0> to PCLK108, ODS = 01                                                                                                                                         |                      | 4.63        |                  |       |  |

| Data to Clock Rising Edge Setup Time  |                                  | VID_<7:0> to PCLK27, ODS = 01                                                                                                                                          |                      | 4.63        |                  |       |  |

|                                       | tsu                              | VID_<7:0> to PCLK54, ODS = 01                                                                                                                                          |                      | 4.63        |                  | ns    |  |

|                                       |                                  | VID_<7:0> to PCLK108, ODS = 01                                                                                                                                         |                      | 4.63        |                  |       |  |

| Rise and Fall Time                    | T <sub>r</sub> , T <sub>f</sub>  | CL=10pF, DVDD_IO=1.8V                                                                                                                                                  |                      | 3           |                  |       |  |

| (20% to 80%)                          | 1, 11                            | CL=25pF, DVDD_IO=3.3V                                                                                                                                                  |                      | 3           |                  | ns    |  |

| Output Leakage                        | IOH, IOL                         | Outputs in High-Z Mode                                                                                                                                                 | -3                   | ±0.01       | 3                | μA    |  |

| OPEN-DRAIN LOGIC OUTPUT (SDA)         | TOH, TOL                         |                                                                                                                                                                        | -5                   | ±0.01       | 5                | μΑ    |  |

| Output Low Voltage                    | Vol                              |                                                                                                                                                                        |                      |             | 0.2 x            |       |  |

| Oulput Low Voltage                    | V OL                             | I <sub>OL</sub> = 3mA, VDDIO = 1.8V                                                                                                                                    |                      |             | VDDIO            |       |  |

|                                       |                                  | I <sub>OL</sub> = 3mA, VDDIO = 3.3V                                                                                                                                    |                      |             | 0.4              | V     |  |

| Output High Current                   | L                                | $V_{\text{OUT}} = 3.3V$                                                                                                                                                |                      | ±0.01       | 3                |       |  |

|                                       |                                  | , LRCLK, SDIN, SDIO, FREF, HREF, TCK, TMI,                                                                                                                             |                      |             | -                | μA    |  |

|                                       |                                  | , LRGEN, SDIN, SDIO, FREF, FIREF, TGN, TIVII,                                                                                                                          | TDS, JTAG            | KST, KEFZ/I |                  |       |  |

| Logic Low Threshold                   | VIL                              |                                                                                                                                                                        |                      |             | 0.3 x<br>DVDD_IO | V     |  |

| Logic High Threshold                  | VIH                              |                                                                                                                                                                        | 0.7 x                |             |                  | V     |  |

|                                       |                                  |                                                                                                                                                                        | VDDIO                |             |                  | v     |  |

| Input Leakage Current                 | I <sub>IH,</sub> I <sub>IL</sub> | (T <sub>A</sub> = 25°C)                                                                                                                                                | -3                   | ±0.01       | 3                | μA    |  |

| SDA/SCL Off Leakage                   | I <sub>IHI2C</sub>               | VDDA=VDDD=VDDIO=0V, SDA=SCL=3.6V                                                                                                                                       | -3                   | ±0.01       | 3                | μA    |  |

| AUDIO LINE OUT                        |                                  |                                                                                                                                                                        |                      |             |                  |       |  |

| Audia Output Cain E                   |                                  | Single ended output                                                                                                                                                    | -10                  | ±1          | 10               | 0/    |  |

| Audio Output Gain Error               | AOGE                             | Differential output                                                                                                                                                    | -10                  | ±1          | 10               | %     |  |

|                                       | 1050                             | 0dB gain, single ended output                                                                                                                                          | -                    | 1           | ž                |       |  |

| Audio Output Full Scale               | AOFS                             | 0dB gain, differential output                                                                                                                                          |                      | 2           |                  | Vpp   |  |

|                                       |                                  | Single ended output, Fs = 48kHz                                                                                                                                        | 80                   | 90          |                  |       |  |

| Audio Output Dynamic Range            | DR                               | Differential output, Fs = 48kHz                                                                                                                                        | 80                   | 90          |                  | dB    |  |

| Audio Output THD+N                    | THDN                             | Differential output, Fs = 48kHz                                                                                                                                        | 66                   | 75          |                  | dB    |  |

|                                       |                                  | 1.7V <v<sub>VDDA&lt;1.9V, 1.7V<v<sub>VDDD&lt;1.9V,</v<sub></v<sub>                                                                                                     |                      |             |                  |       |  |

| Audio Output Power Supply Rejection   |                                  | $1.7V < V_{VDDA} < 1.5V$ , $1.7V < V_{VDDD} < 1.5V$ ,<br>$1.7V < V_{VDDIO} < 3.45V$ , single ended output                                                              |                      | 74 [80]     |                  |       |  |

| Ratio                                 | PSRA                             | $1.7V < V_{VDDA} < 1.9V$ , $3.17V < V_{VDDD} < 1.9V$ , $1.7V < V_{VDDD} < 1.9V$ ,                                                                                      |                      |             |                  | dB    |  |

|                                       |                                  | 1.7V <vvdda<1.9v, 1.7v<vvddd<1.9v,<br="">1.7V<vvddio<3.45v, differential="" output<="" td=""><td></td><td>74 [80]</td><td></td><td></td></vvddio<3.45v,></vvdda<1.9v,> |                      | 74 [80]     |                  |       |  |

| Audio Output Capacitivo Drivo         |                                  | $R_{L}=10k\Omega$ , no sustained oscillations                                                                                                                          |                      | 100         |                  | pF    |  |

|                                       |                                  |                                                                                                                                                                        |                      | 100         |                  | μг    |  |

| AUDIO DAC HIGHPASS DIGITAL FILTE      |                                  |                                                                                                                                                                        |                      |             | 000              | 11-   |  |

| Audio Output Cutoff Frequency         | <b>f</b> DHPPB                   | DACxHPF = 00                                                                                                                                                           |                      |             | 200              | Hz    |  |

| ,                                     |                                  | DACxHPF = 01                                                                                                                                                           |                      |             | 100              | 1     |  |

| PARAMETER                             | SYMBOL              | CONDITIONS                                                                                      |                         | EC Table           |                             | UNITS   |  |

|---------------------------------------|---------------------|-------------------------------------------------------------------------------------------------|-------------------------|--------------------|-----------------------------|---------|--|

|                                       |                     |                                                                                                 | MIN                     | TYP                | MAX                         |         |  |

|                                       |                     | DACxHPF = 10                                                                                    |                         |                    | 50                          |         |  |

|                                       |                     | DACxHPF = 11                                                                                    |                         |                    | disabled                    | -       |  |

| AUDIO LINE IN                         |                     |                                                                                                 |                         |                    |                             |         |  |

|                                       | 4105                | Single ended input                                                                              | -10                     | ±1                 | 10                          | 0/      |  |

| Audio Input Gain Error                | AIGE                | Differential input                                                                              | -10                     | ±1                 | 10                          | %       |  |

|                                       | 4150                | Single ended Input                                                                              |                         | 1.4                |                             |         |  |

| Audio Input Full Scale                | AIFS                | Differential Input                                                                              |                         | 2.8                |                             | Vpp     |  |

|                                       | <b>D</b> D          | Single ended input, Fs = 48kHz                                                                  | 66                      | 80                 |                             |         |  |

| Audio Input Dynamic Range             | DR                  | Differential input, Fs = 48 kHz                                                                 | 66.9                    | 81                 |                             | dB      |  |

| Audio Input THD+N                     | THD+N               | Differential input, Fs = 48kHz                                                                  | 58                      | 69                 |                             | dB      |  |

| Audio Input Gain                      | GAIN                | Differential input, ADCLEV from 0000 to 1111                                                    | -12                     |                    | +3                          | dB      |  |

| Diff. Input CMRR                      | CMRRa               | Freq. Range 0 → 20KHz                                                                           |                         | 90                 |                             | dBFS    |  |

| Audio Input Power Supply Rejection    |                     | 1.7V <vvdda<1.9v, 1.7v<vvddd<1.9v,<="" td=""><td></td><td></td><td></td><td></td></vvdda<1.9v,> |                         |                    |                             |         |  |

| Ratio                                 |                     | 1.7V <v<sub>VDDIO&lt;3.45V, input referred, single</v<sub>                                      |                         | 70                 |                             |         |  |

|                                       |                     | ended input                                                                                     |                         |                    |                             |         |  |

|                                       | PSRD                | 1.7V <v<sub>VDDA&lt;1.9V, 1.7V<v<sub>VDDD&lt;1.9V,</v<sub></v<sub>                              |                         |                    |                             | – dB    |  |

|                                       |                     | 1.7V <v<sub>VDDIO&lt;3.45V, input referred, differential</v<sub>                                |                         | 70                 |                             |         |  |

|                                       |                     | input                                                                                           |                         |                    |                             |         |  |

| Audio Input Total Harmonic Distortion | TUD                 | 1kHz, 0dBFS, single ended input                                                                 |                         | -80                |                             |         |  |

| ·                                     | THD                 | 1kHz, 0dBFS, differential input                                                                 |                         | -80                |                             | dB      |  |

| Audio Input Signal to Noise Ratio     |                     | 1kHz 0dBFS, single ended input                                                                  |                         | 83                 |                             |         |  |

|                                       | SNR                 | 1kHz 0dBFS, differential input                                                                  |                         | 83                 |                             | dB      |  |

| Audio Input Resistance                | RINA                | Single-ended input                                                                              | 35                      |                    |                             |         |  |

| ·                                     |                     | Differential input                                                                              | 35                      |                    |                             | kΩ      |  |

| AUDIO ADC DIGITAL HIGHPASS FILTER     | 2                   |                                                                                                 | •                       |                    |                             |         |  |

|                                       |                     | ADCHPF = 00                                                                                     |                         |                    | 200                         |         |  |

|                                       |                     | ADCHPF = 01                                                                                     |                         |                    | 100                         | Hz<br>d |  |

| Audio Input Cutoff Frequency          | <b>f</b> ahpsb      | ADCHPF = 10                                                                                     |                         |                    | 50                          |         |  |

|                                       |                     | ADCHPF = 11                                                                                     |                         |                    | disabled                    |         |  |

| DDR2 Interface ( DQS,DQ<15:0>, DM, V  | VEB, RASB           | CASB, ODT, CKE, CK_, CSB, A<12:0>) Note                                                         | 7                       |                    |                             | 1       |  |

| Memory Clock Period                   | tск                 |                                                                                                 |                         | 6.2                |                             | ns      |  |

| SSTL18 Reference Voltage              | VrefDC              |                                                                                                 |                         | 0.5*VDDD           |                             | V       |  |

| SSTL18 Input High                     | VihDC               | T <sub>A</sub> = +25°C                                                                          | V <sub>refDC</sub> +125 |                    |                             | mV      |  |

| 1 5                                   |                     | $T_A = 0^{\circ}C$ to $70^{\circ}C$                                                             | V <sub>refDC</sub> +200 |                    |                             |         |  |

|                                       |                     | ~                                                                                               | V refDC +200            |                    |                             |         |  |

| SSTL18 Input Low                      | VilDC               | $T_A = +25^{\circ}C$                                                                            |                         |                    | V <sub>refDC</sub> –<br>125 | mV      |  |

|                                       |                     | T <sub>A</sub> = 0°C to 70°C                                                                    | 1                       |                    | V <sub>refDC</sub> – 250    | 1       |  |

| SSTL18 Output High                    | VOHDDR2             | Load = 13.4mA; VDDD=1.7V                                                                        | 1.2                     | 1.5                | 200                         | V       |  |

| SSTL18 Output Low                     | VOLDDR2             | Load = 13.4mA; VDDD=1.7V                                                                        |                         | 0.18               | 0.3                         | V       |  |

| SSTL18 Input cross-point              | VIXDDR2             | Differential inputs                                                                             |                         | VrefDC             |                             | mV      |  |

| SSTL18 Output cross-point             | VOXDDR2             | Differential outputs                                                                            |                         | V <sub>refDC</sub> |                             | mV      |  |

| SSTL18 CM Output Voltage              | VCM <sub>DDR2</sub> | Differential outputs, differential termination                                                  |                         | VrefDC             |                             | mV      |  |

| SSTL18 Output slew rate               | OS <sub>DDR2</sub>  |                                                                                                 |                         | 3                  |                             | V/ns    |  |

| DQS/DQ write skew                     | tDDR2DLY            | Write mode (DQS/DQ are outputs)                                                                 | 1                       | 1.55               |                             | ns      |  |

#### Table 1: EC Table

**Note 1:** All devices are 100% production tested at TA=+25°C. Specifications over temperature limits are guaranteed by design. **Note 2:** NTSC 75% Color Bar signal applied to analog input.  $C_L = 10$ pF on logic output pins (D7-D0 and PCLK27).

C<sub>B</sub> is in pF. Note 3:

Note 4: Filter and ADC performance measured using ADC outputs prior to composite digital demodulation (decoding).

Note 5: Decoded Luminance and Chrominance specifications measured using entire signal path from analog input to digital component outputs.

Note 6: Internal test only. Digital core controls sync level adjust current to adjust offset in analog signal path. Adjust level is based on value of sync level as converted by ADC. Digital core switches sourcing or sinking current into AIN1 and AIN2 nodes. Speed of correction (value of current) is controlled through I<sup>2</sup>C.

Note 7: SSTL18 differential signals are UDQS/B, LDQS/B, and CK/B. All others are single ended. See reference JEDEC Std. 8-15A for detailed test information.

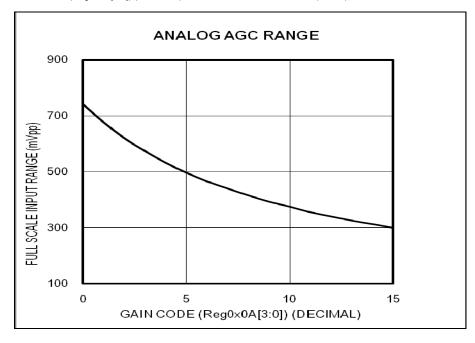

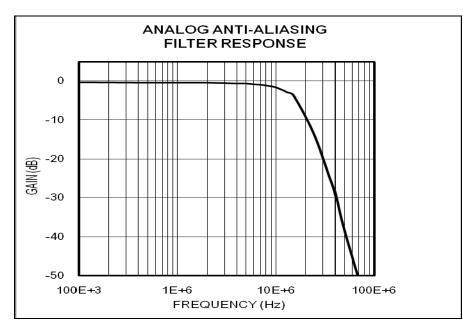

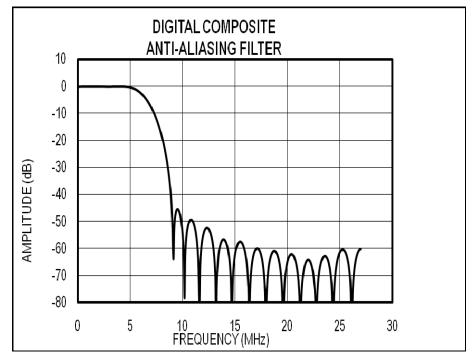

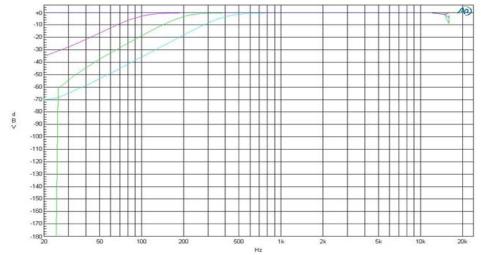

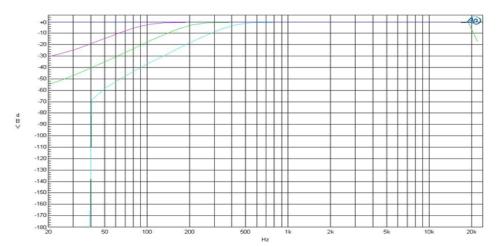

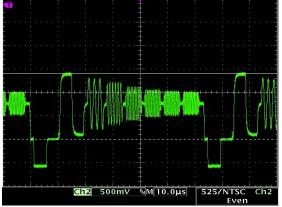

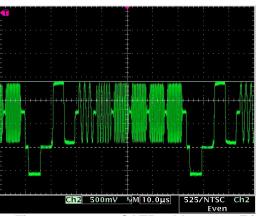

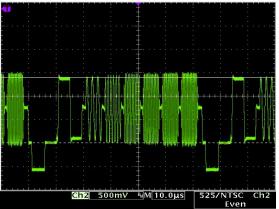

**5.** Typical Operating Characteristics (VAVDD = VDVDD = +1.8V, VDVDDIO = 3.3V, VAGND = VDGND = 0V, TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA =  $+25^{\circ}C.$ )

#### VIDEO ADC FULL-SCALE **CONVERSION RANGE**

GAIN CODE (Reg0x0A[3:0]) (DECIMAL) / FULL-SCALE INPUT RANGE (mVP-P)

Figure 2: VIDEO ANALOG AGC RANGE

VIDEO ANALOG INPUT FILTER RESPONSE FREQUENCY (MHz) / AMPLITUDE (dB)

Figure 3: VIDEO ANALOG INPUT FILTER RESPONSE

Figure 4: VIDEO DIGITAL COMPOSITE ANTI-ALIASING FILTER

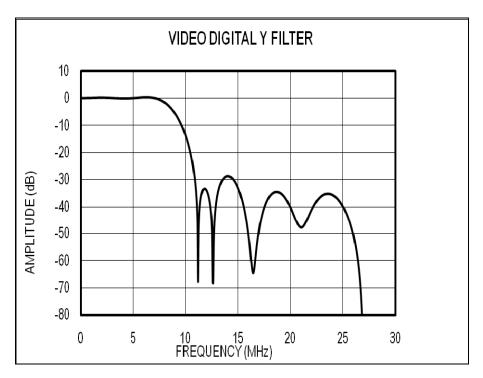

VIDEO DIGITAL Y FILTER FREQUENCY (MHz) / AMPLITUDE (dB)

Figure 5: VIDEO DIGITAL Y FILTER

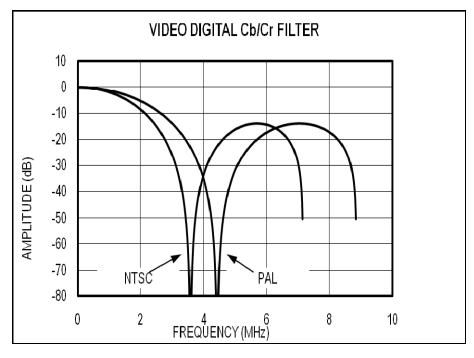

VIDEO DIGITAL Cb/Cr FILTER FREQUENCY (MHz) / AMPLITUDE (dB)

Figure 6: VIDEO DIGITAL Cb/Cr FILTER

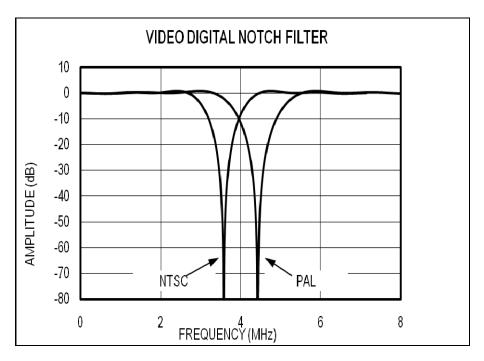

VIDEO DIGITAL NOTCH FILTER FREQUENCY (MHz) / AMPLITUDE (dB)

Figure 7: VIDEO DIGITAL NOTCH FILTER

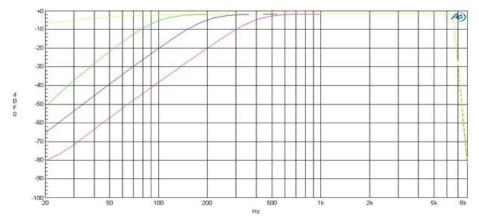

VIDEO POWER SUPPLY REJECTION VS. FREQUENCY GAIN (dB) / FREQUENCY (Hz)

Figure 8: PWER SUPPLY REJECTION vs. FREQUENCY

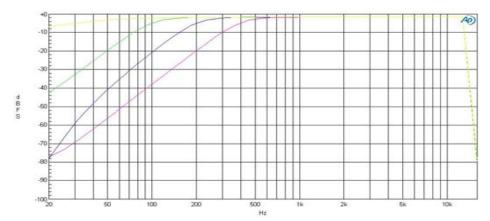

#### Figure 9:

| Sweep | Trace | Color   | Comment                |

|-------|-------|---------|------------------------|

| 1     | 1     | Magenta | AFRQ=16KHz, HPF=400Hz  |

| 2     | 1     | Blue    | AFRQ=16KHz, HPF=200Hz  |

| 3     | 1     | Green   | AFRQ=16KHz, HPF=100Hz  |

| 4     | 1     | Yellow  | AFRQ=16KHz, HPF=bypass |

#### Figure 10:

| Sweep | Trace | Color   | Comment                |

|-------|-------|---------|------------------------|

| 1     | 1     | Magenta | AFRQ=32KHz, HPF=400Hz  |

| 2     | 1     | Blue    | AFRQ=32KHz, HPF=200Hz  |

| 3     | 1     | Green   | AFRQ=32KHz, HPF=100Hz  |

| 4     | 1     | Yellow  | AFRQ=32KHz, HPF=bypass |

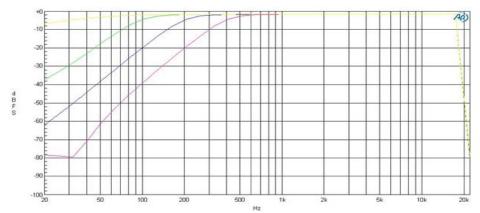

#### Figure 11:

| Sweep | Trace | Color   | Comment                  |

|-------|-------|---------|--------------------------|

| 1     | 1     | Magenta | AFRQ=44.1KHz, HPF=400Hz  |

| 2     | 1     | Blue    | AFRQ=44.1KHz, HPF=200Hz  |

| 3     | 1     | Green   | AFRQ=44.1KHz, HPF=100Hz  |

| 4     | 1     | Yellow  | AFRQ=44.1KHz, HPF=bypass |

#### Figure 12:

| Sweep | Trace | Color   | Comment                |

|-------|-------|---------|------------------------|

| 1     | 1     | Magenta | AFRQ=48KHz, HPF=400Hz  |

| 2     | 1     | Blue    | AFRQ=48KHz, HPF=200Hz  |

| 3     | 1     | Green   | AFRQ=48KHz, HPF=100Hz  |

| 4     | 1     | Yellow  | AFRQ=48KHz, HPF=bypass |

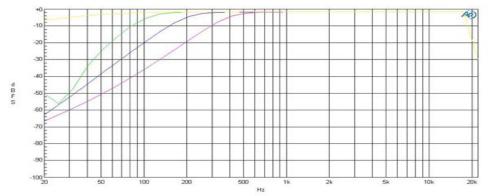

AUDIO DIGITAL HIGH PASS FILTER [IHPF] vs. INPUT FREQUENCY GAIN(dBV) / Frequency (Khz)

#### Figure 13:

| Sweep | Trace | Color   | Comment                |

|-------|-------|---------|------------------------|

| 1     | 1     | Cyan    | AFRQ=16KHz, HPF=400Hz  |

| 2     | 1     | Green   | AFRQ=16KHz, HPF=200Hz  |

| 3     | 1     | Magenta | AFRQ=16KHz, HPF=100Hz  |

| 4     | 1     | Blue    | AFRQ=16KHz, HPF=bypass |

#### Figure 14:

| Sweep | Trace | Color   | Comment                |

|-------|-------|---------|------------------------|

| 1     | 1     | Cyan    | AFRQ=32KHz, HPF=400Hz  |

| 2     | 1     | Green   | AFRQ=32KHz, HPF=200Hz  |

| 3     | 1     | Magenta | AFRQ=32KHz, HPF=100Hz  |

| 4     | 1     | Blue    | AFRQ=32KHz, HPF=bypass |

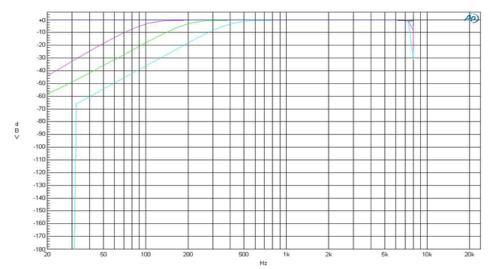

#### Figure 15:

| Sweep | Trace | Color   | Comment                  |

|-------|-------|---------|--------------------------|

| 1     | 1     | Cyan    | AFRQ=44.1KHz, HPF=400Hz  |

| 2     | 1     | Green   | AFRQ=44.1KHz, HPF=200Hz  |

| 3     | 1     | Magenta | AFRQ=44.1KHz, HPF=100Hz  |

| 4     | 1     | Blue    | AFRQ=44.1KHz, HPF=bypass |

#### Figure 16:

| Sweep | Trace | Color   | Comment                |

|-------|-------|---------|------------------------|

| 1     | 1     | Cyan    | AFRQ=48KHz, HPF=400Hz  |

| 2     | 1     | Green   | AFRQ=48KHz, HPF=200Hz  |

| 3     | 1     | Magenta | AFRQ=48KHz, HPF=100Hz  |

| 4     | 1     | Blue    | AFRQ=48KHz, HPF=bypass |

# 6. Pin Configuration

| L |             |            |            |              |             |             |            |              |              |            |            |            |            | R          |

|---|-------------|------------|------------|--------------|-------------|-------------|------------|--------------|--------------|------------|------------|------------|------------|------------|

|   | 1           | 2          | 3          | 4            | 5           | 6           | 7          | 8            | 9            | 10         | 11         | 12         | 13         | 14         |

| Α | SDIOA<br>L  | BCLK<br>P  | BCLK<br>R  | PCLK<br>108  | PCLK<br>27  | TPP1        | VOUT<br>37 | VOUT<br>36   | VOUT<br>35   | VOUT<br>34 | VOUT<br>17 | VOUT<br>16 | VOUT<br>15 | VOUT<br>14 |

| В | BCLKA<br>L  | LRCLK<br>P | LRCLK<br>R | PCLK<br>108B | PCLK<br>27B | TPP2        | VOUT<br>33 | VOUT<br>32   | VOUT<br>31   | VOUT<br>30 | VOUT<br>13 | VOUT<br>12 | VOUT<br>11 | VOUT<br>10 |

| С | LRCLK<br>AL | SDIN       | SDOUT      | HREF         | PCLK<br>54  | TPP3        | VOUT<br>47 | VOUT<br>46   | VOUT<br>45   | VOUT<br>44 | VOUT<br>27 | VOUT<br>26 | VOUT<br>25 | VOUT<br>24 |

| D | XTAL<br>1   | SDOUT<br>M | MCLK<br>R  | FREF         | PCLK<br>54B | TPP4        | VOUT<br>43 | VOUT<br>42   | VOUT<br>41   | VOUT<br>40 | VOUT<br>23 | VOUT<br>22 | VOUT<br>21 | VOUT<br>20 |

| Е | XTAL<br>2   | REF<br>27O | REF<br>27I | GND          | VDDA        | GND         | GND        | VDD          | VDD          | VDDIO      | A12        | A11        | A10        | A9         |

| F | GND         | VIN1P      | VIN1N      | GND          | VDDA        | GND         | GND        | VDD          | VDD          | VDDIO      | A8         | A7         | A6         | A5         |

| G | GND         | GND        | GND        | GND          | VDDA        | GND         | GND        | VDD          | VDD          | VDDIO      | A4         | A3         | A2         | A1         |

| н | GND         | VIN2P      | VIN2N      | GND          | VDDA        | GND         | GND        | VDD          | VDD          | VDDIO      | A0         | BA1        | BA0        | CSB        |

| J | GND         | GND        | GND        | GND          | VDDA        | GND         | GND        | VDD          | VDD          | VDDIO      | DQ15       | DQ14       | DQ13       | DQ12       |

| к | GND         | VIN3P      | VIN3N      | GND          | VDDA        | GND         | GND        | VDD          | VDD          | VDDIO      | DQ11       | DQ10       | DQ9        | DQ8        |

| L | GND         | GND        | GND        | AUD<br>GND   | PREF        | PREG        | TMS        | IRQB         | CKE          | RASB       | UDM        | UDQS       | UDQSB      | VREF       |

| М | GND         | VIN4P      | VIN4N      | VCM          | AOUT<br>2P  | AOUT<br>2N  | тск        | SDA          | СК           | CASB       | DQ7        | DQ6        | DQ5        | DQ4        |

| N | AIN1P       | AIN1N      | AIN2P      | AIN2N        | AOUT<br>1P  | AOUT<br>1N  | TDO        | SCL          | СКВ          | WEB        | DQ3        | DQ2        | DQ1        | DQ0        |

| Р | AIN3P       | AIN3N      | AIN4P      | AIN4N        | GND         | JTAG<br>RST | TDI        | DEV<br>ADDR1 | DEV<br>ADDR0 | RSTB       | LDM        | LDQS       | LDQSB      | ODT        |

# Top View (Through Package)

Figure 17: MAX9530 pin configuration

# 7. Pin Description

Table 2:

| Table 2:                     |                                           | -    |                                                  |

|------------------------------|-------------------------------------------|------|--------------------------------------------------|

| Ball                         | Ball Name                                 | Туре | Pin Description                                  |

|                              |                                           |      | Audio I/O                                        |

| BCLKR                        | A3                                        | I/O  | Audio serial clock input/output of record.       |

| LRCLKR                       | B3                                        | I/O  | Audio serial sync input/output of record.        |

| MCLKR                        | D3                                        | 0    | Audio master clock output of record.             |

| SDOUT                        | C3                                        | 0    | Audio serial data output of record.              |

| SDOUTM                       | D2                                        | 0    | Audio serial data output of mixing.              |

| BCLKP                        | A2                                        | I/O  | Audio serial clock input/output of playback.     |

| LRCLKP                       | B2                                        | I/O  | Audio serial sync input/output of playback.      |

| SDIN                         | C2                                        | I    | Audio serial data input of playback.             |

| BCLKAL                       | B1                                        | I/O  | Audio Multi-chip operation serial bit clock I/O  |

| LRCLKAL                      | C1                                        | I/O  | Audio Multi-chip operation serial word clock I/O |

| SDIOAL                       | A1                                        | I/O  | Audio Multi-chip operation serial input/output   |

| AIN1P, AIN1N                 | N1, N2                                    | I    | Audio input of channel 1.                        |

| AIN2P, AIN2N                 | N3, N4                                    | I    | Audio input of channel 2.                        |

| AIN3P, AIN3N                 | P1, P2                                    | I    | Audio input of channel 3.                        |

| AIN4P, AIN4N                 | P3, P4                                    | 1    | Audio input of channel 4.                        |

| AUDGND                       | L4                                        | А    | Audio reference ground return.                   |

| AOUT1P,N                     | N5, N6                                    | 0    | Analog audio output 1.                           |

| AOUT2P,N                     | M5, M6                                    | 0    | Analog audio output 2.                           |

| PREG                         | L6                                        | A    | Audio regulator output.                          |

| PREF                         | L5                                        | A    | Audio reference output.                          |

| VCM                          | M4                                        | A    | Audio common mode reference.                     |

|                              | 1014                                      | ~~~~ | Video I/O                                        |

| VIN1P, VIN1N                 | F2, F3                                    | 1    | Composite video input of channel 1.              |

| VIN2P, VIN2N                 | H2, H3                                    | 1    | Composite video input of channel 2.              |

| VIN3P, VIN3N                 | K2, K3                                    | 1    | Composite video input of channel 3.              |

| VIN3P, VIN3N<br>VIN4P, VIN4N | M2, M3                                    |      | Composite video input of channel 4.              |

| VIIN4F, VIIN4IN              | B14, B13, B12, B11,                       | 0    |                                                  |

| VOUT1[0:7]                   | A14, A13, A12, A11                        |      | Video data output of channel 1.                  |

| VOUT2[0:7]                   | D14, D13, D12, D11,<br>C14, C13, C12, C11 | 0    | Video data output of channel 2.                  |

| VOUT3[0:7]                   | B10, B9, B8, B7,<br>A10, A9, A8, A7       | 0    | Video data output of channel 3.                  |

| VOUT4[0:7]                   | D10, D9, D8, D7,<br>C10, C9, C8, C7       | 0    | Video data output of channel 4.                  |

|                              | ,,, _                                     |      | I2C Interface                                    |

| SDA                          | M8                                        | IO   | Serial control data line.                        |

| SCL                          | N8                                        | I    | Serial control clock line.                       |

| DEVADDR[1:0]                 | P8, P9                                    | I    | Serial control address.                          |

|                              |                                           |      | JTAG                                             |

| JTAGRST                      | P6                                        | I    | Active low                                       |

| TMS                          | L7                                        | I    |                                                  |

| ТСК                          | M7                                        |      | 6MHz max                                         |

| TDO                          | N7                                        | 0    |                                                  |

| TDI                          | P7                                        | -    |                                                  |

|                              |                                           | •    | DDR2 Memory Interface                            |

| CKE                          | L9                                        | 0    | Clock enable                                     |

|                              |                                           | 5    |                                                  |

| RASB, CASB,<br>WEB        | L10, M10, N10                                                                              | 0   | Command inputs                                                                                                                                                        |

|---------------------------|--------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, CKB                   | M9, N9                                                                                     | 0   | CK and nCK are differential clock inputs.                                                                                                                             |

| -                         |                                                                                            |     | 162 MHz, differential 100 ohm                                                                                                                                         |

| DQ[0:15]                  | N14, N13, N12, N11,<br>M14, M13, M12,<br>M11, K14, K13, K12,<br>K11, J14, J13, J12,<br>J11 | I/O | Data input/output - 50 Ohm                                                                                                                                            |

| LDQS, LDQSB               | P12, P13                                                                                   | I/O | Data strobe for lower byte                                                                                                                                            |

|                           |                                                                                            |     | 162 MHz, differential 100 ohm                                                                                                                                         |

| LDM, UDM                  | P11, L11                                                                                   | 0   | Input data mask                                                                                                                                                       |

| UDQS, UDQSB               | L12, L13                                                                                   | I/O | Data strobe for upper byte                                                                                                                                            |

|                           |                                                                                            |     | 162 MHz, differential 100 ohm                                                                                                                                         |

| ODT                       | P14                                                                                        | 0   | On-die termination                                                                                                                                                    |

| CSB                       | H14                                                                                        | 0   | Chip select                                                                                                                                                           |

| VREF                      | L14                                                                                        |     | Vref                                                                                                                                                                  |

| BA0, BA1                  | H13, H12                                                                                   | 0   | Bank address inputs                                                                                                                                                   |

| A[0:12]                   | H11, G14, G13, G12,<br>G11, F14, F13, F12,<br>F11, E14, E13, E12,<br>E11                   | 0   | Address inputs                                                                                                                                                        |

|                           |                                                                                            |     | Timing/IRQ/Reset                                                                                                                                                      |

| RSTB                      | P10                                                                                        |     | System reset.                                                                                                                                                         |

| IRQB                      | L8                                                                                         | 0   | Interrupt request output.<br>This signal has positive logic and cannot be connected<br>directly with other IRQs in the system. Pull-up resistor is still<br>required. |

| XTAL1, XTAL2              | D1, E1                                                                                     | I   | 27MHz Xtal or External 27                                                                                                                                             |

| TPP1, TPP2,<br>TPP3, TPP4 | A6, B6, C6, D6                                                                             | 0   | HS/VS/FLD/ACTIVE/NOVID of channel 1,2,3 & 4                                                                                                                           |

| PCLK27,<br>PCLK27B        | A5, B5                                                                                     | 0   | 27 MHz clock output.                                                                                                                                                  |

| PCLK54,<br>PCLK54B        | C5, D5                                                                                     | 0   | 54 MHz clock output.                                                                                                                                                  |

| PCLK108,<br>PCLK108B      | A4, B4                                                                                     | 0   | 108 MHz clock output.                                                                                                                                                 |

| HREF, FREF                | C4, D4                                                                                     | IO  | External H and F Reference Input /Output                                                                                                                              |

| REF27O                    | E2                                                                                         | 0   | Reference Clock Output.                                                                                                                                               |

| REF27I                    | E3                                                                                         | I   | Reference Clock Input.                                                                                                                                                |

|                           |                                                                                            |     | Power and Ground Pins                                                                                                                                                 |

| VDDD                      |                                                                                            | Р   | 1.8V Power for internal logic.                                                                                                                                        |