## **General Description**

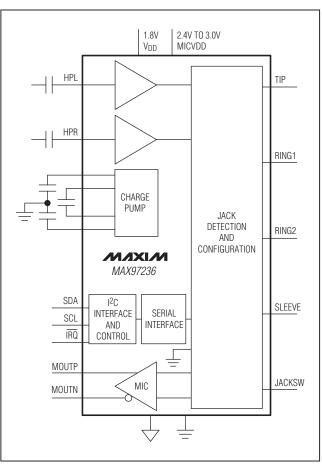

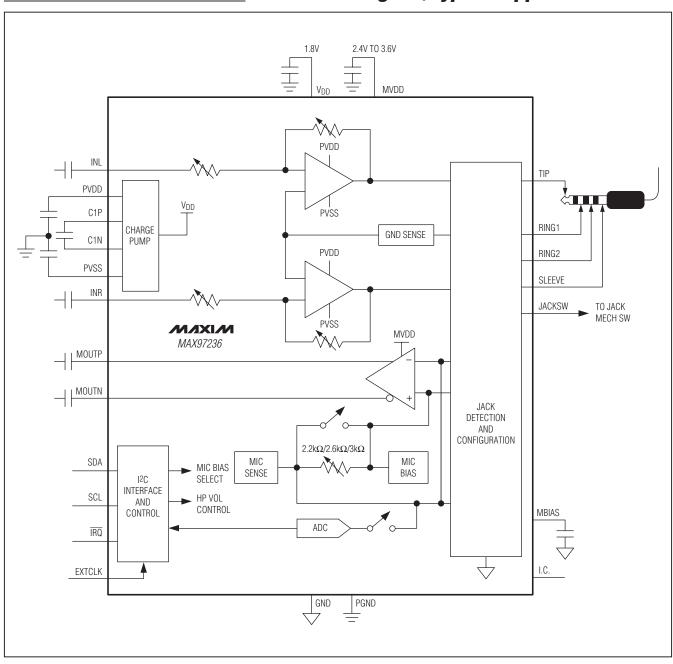

The MAX97236 is an audio amplifier with volume control and microphone preamplifier intended for use in portable audio systems employing a headphone jack. The audio circuit is powered from a single, dual-mode charge pump, allowing the output signals to be ground referenced, and eliminating the need for large and expensive DC-blocking capacitors. The configuration of a 3.5mm jack is determined by autoconfigure circuitry. The IC's functional blocks are auto-enabled after the configuration of the jack is determined.

The audio amplifier is powered from a single 1.8V power supply that reduces overall power consumption. The microphone preamplifier and bias are powered from a separate power-supply input accommodating bias voltages that are greater than 2.4V.

The automatic jack detection determines when a 3.5mm plug is inserted into the system jack and determines the configuration of the installed load. The configuration of the load is then reported to the system through the I2C interface. Multiple popular jack and load configurations are detectable with this scheme. The IC detects headsets, headphones, and A/V cables.

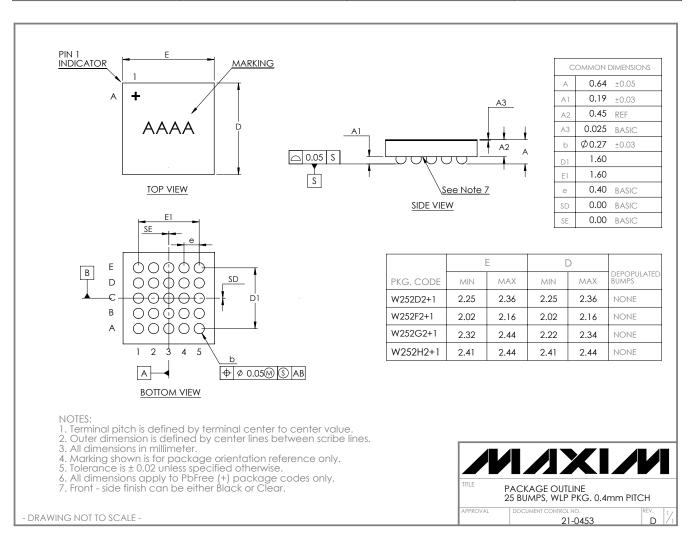

The headphone amplifier is capable of over 35mW into 16 $\Omega$ . The device is available in a small. 25-bump WLP package with a 0.4mm pitch and is specified over the extended -40°C to +85°C temperature range.

## **Applications**

**Smartphones**

Mobile Handsets

Notebooks

Portable Gaming Devices

**Tablets**

## **Ordering Information**

| PART         | TEMP           | PIN-    | I <sup>2</sup> C |

|--------------|----------------|---------|------------------|

|              | RANGE          | PACKAGE | ADDRESS          |

| MAX97236EWA+ | -40°C to +85°C | 25 WLP  | 0x80             |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

Functional Diagram/Typical Application Circuit appears at end of data sheet

### **Features**

- ♦ 30mW Headphone Amplifier Employs Second-Generation DirectDrive® with Dual-Mode Charge-**Pump Architecture**

- **♦ Automatic Jack Detection Circuitry**

- **♦ Microphone Amplifier and Bias**

- ♦ 1.8V Power Supply

- ♦ 2.4V to 3.6V Microphone Power Supply

- **♦ Headphone Amplifier Volume Control**

- ♦ Decodes Data from a Passive Multibutton Headset **Remote Control**

- ♦ 25-Bump, 2.4mm x 2.3mm, 0.4mm Pitch WLP

DirectDrive is a registered trademark of Maxim Integrated Products, Inc.

## Simplified Block Diagram

/U/IXI/U

Maxim Integrated Products 1

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to PGND0.3V to +2V MICVDD to PGND0.3V to +5.5V          | MOUT+ and MOUT- to PGND0.3V to (VMICVDD + 0.3V) C1P to PGND0.3V to (VPVDD + 0.3V)  |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| PVDD to PGND0.3V to (V <sub>DD</sub> + 0.3V)<br>PVSS to PGND2V to +0.3V | C1N to PGND(VPVSS - 0.3V) to +0.3V<br>SDA, SCL, EXTCLK, and IRQ to PGND0.3V to +6V |

| GND to PGND0.1V to +0.1V                                                | Output Short-Circuit Duration                                                      |

| TIP, RING1, IN_ to PGND(VPVSS - 0.3V)                                   | Continuous Power Dissipation (Mulitlayer Board, TA = +70°C)                        |

| to $(VPVDD + 0.3V)$                                                     | 25-Bump WLP (derate 19.2mW/°C above +70°C)1536mW                                   |

| RING2, SLEEVE to PGND(GND - 0.3V)                                       | Junction Temperature+150°C                                                         |

| to $(V_{MICVDD} + 0.3V)$                                                | Operating Temperature Range40°C to +85°C                                           |

| JACKSW to PGND(VPVSS - 0.3V) to (VMICVDD + 0.3V)                        | Storage Temperature Range65°C to +150°C                                            |

| MBIAS to PGND0.3V to (VDD + 0.3V)                                       | Soldering Temperature (reflow)+260°C                                               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## PACKAGE THERMAL CHARACTERISTICS (Note 1)

Junction-to-Ambient Thermal Resistance (θ<sub>JA</sub>)......52°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 1.8V, V_{MICVDD} = 3.0V, V_{GND} = V_{PGND} = 0V, C_{FLY} = C_{PVDD} = C_{PVSS} = 1\mu F.$  Typical values tested at T<sub>A</sub> = +25°C, unless otherwise noted. See the *Functional Diagram/Typical Application Circuit.*) (Note 2)

| PARAMETER                                      | SYMBOL               | CONDITIONS                                                                             | MIN  | TYP                      | MAX                       | UNITS |

|------------------------------------------------|----------------------|----------------------------------------------------------------------------------------|------|--------------------------|---------------------------|-------|

| GENERAL                                        | •                    |                                                                                        |      |                          |                           |       |

| Supply Voltage Range                           | V <sub>DD</sub>      | Guaranteed by PSRR test                                                                | 1.62 | 1.8                      | 1.98                      | V     |

| Undervoltage Lockout                           | UVLO                 | Rising $V_{DD}$ , $T_A = +25^{\circ}C$                                                 |      |                          | 1.6                       | V     |

| Chutdown Cupply Current                        | I <sub>VDD_SDF</sub> | In jack detect mode, T <sub>A</sub> = +25°C, fast detect mode, external clock disabled |      | 14                       | 25                        |       |

| Shutdown Supply Current                        | I <sub>VDD_SDS</sub> | In jack detect mode, T <sub>A</sub> = +25°C, slow detect mode, external clock disabled |      | 14                       | 25                        | μΑ    |

| Sleep Supply Current                           | I <sub>VDD_SL</sub>  | T <sub>A</sub> = +25°C, external clock disabled                                        |      |                          | 25                        | μΑ    |

| Quiescent Supply Current                       | I <sub>VDD</sub>     | T <sub>A</sub> = +25°C, state = LRGM                                                   |      | 2.3                      | 3.9                       | mA    |

| SDA, SCL Input Logic-High                      | V <sub>IH</sub>      | 1.8V logic compliant                                                                   | 1.4  |                          |                           | V     |

| SDA, SCL Input Logic-Low                       | V <sub>IL</sub>      | 1.8V logic compliant                                                                   |      |                          | 0.4                       | V     |

| SDA, SCL, EXTCLK Input<br>Leakage Current High | I <sub>IH</sub>      | $T_A = +25^{\circ}C$                                                                   | -1   |                          | +1                        | μΑ    |

| SDA, SCL, EXTCLK Input<br>Leakage Current Low  | I <sub>IL</sub>      | T <sub>A</sub> = +25°C                                                                 | -1   |                          | +1                        | μΑ    |

| SDA, SCL Output Logic-Low                      | V <sub>OLI2C</sub>   | I <sub>OLI2C</sub> = 2.3mA                                                             |      | 0.2 x<br>V <sub>DD</sub> |                           | V     |

| IRQ Output High Current                        | ГОН                  | $V_{IRQ_OUT} = 3.3V, T_A = +25^{\circ}C$                                               |      |                          | 1                         | μΑ    |

| IRQ Output Logic-Low                           | V <sub>OL</sub>      | I <sub>OL</sub> = 3mA                                                                  |      |                          | 0.25 x<br>V <sub>DD</sub> | V     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 1.8V, V_{MICVDD} = 3.0V, V_{GND} = V_{PGND} = 0V, C_{FLY} = C_{PVDD} = C_{PVSS} = 1\mu F.$  Typical values tested at TA = +25°C, unless otherwise noted. See the *Functional Diagram/Typical Application Circuit.*) (Note 2)

| PARAMETER                            |                     |                                                                                                                         | MIN  | TYP  | MAX  | UNITS             |

|--------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------|------|------|------|-------------------|

| EXTCLK Input High Voltage            |                     |                                                                                                                         | 1.4  |      |      | V                 |

| EXTCLK Input Low Voltage             |                     |                                                                                                                         |      |      | 0.4  | V                 |

| EXTCLK Frequency Range               | f <sub>EXTCLK</sub> | $T_A = +25^{\circ}C$                                                                                                    | 1    | 19.2 | 26   | MHz               |

| EXTCLK Duty Cycle                    | D_EXTCLK            | $T_A = +25^{\circ}C$                                                                                                    | 45   |      | 55   | %                 |

| Maximum EVTCL // Clay Bata           |                     | f <sub>EXTCLK</sub> = 1MHz, 0.4V to 1.4V                                                                                |      | 50   |      | 20                |

| Maximum EXTCLK Slew Rate             |                     | f <sub>EXTCLK</sub> = 10MHz, 0.4V to 1.4V                                                                               |      | 5    |      | ns                |

| Turn-On Time                         | t <sub>ON</sub>     | (Note 3)                                                                                                                |      | 1    | 10   | ms                |

| JACK DETECTION                       |                     |                                                                                                                         |      |      |      |                   |

| Turn-On Time                         | <sup>t</sup> ONTIME | Jack detect time from insertion to interrupt (Note 4)                                                                   |      | 500  |      | ms                |

| AUDIO AMPLIFIER (Gain = 0dB,         | Unless Otherw       | ise Noted)                                                                                                              |      |      |      |                   |

| Output Offset Voltage                | V <sub>OS</sub>     | $T_A = +25$ °C, state = LRGM                                                                                            | -500 |      | +500 | μV                |

| Output Power                         | D                   | $R_L = 32\Omega$ , $THD+N = 1\%$ , $f_{IN} = 1$ kHz                                                                     |      | 30   |      | m\//              |

| Output Power                         | P <sub>OUT</sub>    | $R_L = 16\Omega$ , $THD+N = 1\%$ , $f_{IN} = 1$ kHz                                                                     |      | 35   |      | mW                |

| Line Output Voltage                  | V <sub>O_LINE</sub> | $R_L = 10k\Omega$                                                                                                       |      | 1    |      | V <sub>RMS</sub>  |

| T                                    |                     | $R_L = 16\Omega$ , $P_{OUT} = 10$ mW, $f_{IN} = 1$ kHz                                                                  |      | 0.05 |      |                   |

| Total Harmonic Distortion Plus Noise | THD+N               | $R_L = 16\Omega$ , $P_{OUT} = 0.1$ mW, $f_{IN} = 1$ kHz                                                                 |      | 0.04 |      | %                 |

| T lus Noise                          |                     | $R_L = 10k\Omega$ , $V_{OUT} = 1V_{RMS}$ , $f_{IN} = 1kHz$                                                              |      | 0.03 |      |                   |

|                                      | ONE                 | Referenced to $32\Omega$ load, $1V_{RMS}$ input signal, A-weighted                                                      | 103  |      |      |                   |

| Signal-to-Noise Ratio                | SNR                 | Referenced to $32\Omega$ load, $1V_{RMS}$ input signal, A-weighted (gain = -30dB)                                       | 85   |      |      | dB                |

|                                      |                     | DC 1.62V to 1.98V, gain = 0dB,<br>T <sub>A</sub> = +25°C                                                                |      | 87   |      |                   |

| Power-Supply Rejection Ratio         | PSRR                | f <sub>IN</sub> = 217Hz, 100mV <sub>P-P</sub> ripple,<br>gain = 0dB                                                     | 78   |      |      | dB                |

|                                      |                     | f <sub>IN</sub> = 10kHz, 100mV <sub>P-P</sub> ripple,<br>gain = 0dB                                                     | 74   |      |      |                   |

|                                      |                     | A-weighted                                                                                                              |      | 6    |      |                   |

| Output Noise                         | V <sub>N</sub>      | A-weighted, gain = -30dB                                                                                                |      | 1.7  |      | μV <sub>RMS</sub> |

|                                      |                     | A-weighted, gain = -60dB                                                                                                |      | 1.4  |      |                   |

| Peak Output Current                  | lout                | Peak current needed to output the rated typical power                                                                   |      | 40   |      | mA                |

| Minimum Headphone Impedance          | Z <sub>OUT</sub>    |                                                                                                                         |      | 12   |      | Ω                 |

|                                      |                     | $R_L = 16\Omega$ , $f_{IN} = 1$ kHz, $P_{OUT} = 5$ mW, crosstalk between audio channels, gain = 0dB, with ground sense  | -51  |      |      | dB                |

| Crosstalk                            | XTALK               | $R_L = 32\Omega$ , $f_{IN} = 1$ kHz, $P_{OUT} = 25$ mW, crosstalk between audio channels, gain = 0dB, with ground sense | -56  |      |      | dB                |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 1.8V, V_{MICVDD} = 3.0V, V_{GND} = V_{PGND} = 0V, C_{FLY} = C_{PVDD} = C_{PVSS} = 1\mu F.$  Typical values tested at T<sub>A</sub> = +25°C, unless otherwise noted. See the *Functional Diagram/Typical Application Circuit.*) (Note 2)

| PARAMETER                           | SYMBOL                | CONDITIONS                                       |                                              |                             | MIN   | TYP  | MAX   | UNITS             |

|-------------------------------------|-----------------------|--------------------------------------------------|----------------------------------------------|-----------------------------|-------|------|-------|-------------------|

|                                     |                       | $R_L = 10k\Omega$ ,                              | gain ≥ 0dB                                   |                             |       | 470  |       |                   |

| Maximum Capacitive Load Drive       | $C_L$                 | $R_L = 10k\Omega$ ,                              | gain < 0dB                                   |                             |       | 200  |       | рF                |

|                                     |                       | $R_L = 32\Omega$                                 |                                              |                             |       | 200  |       |                   |

|                                     |                       |                                                  | $P_{OUT} = 0.$                               | 5mW, $R_L = 32\Omega$       |       | 4.5  |       |                   |

| Power Consumption                   |                       | Pout = $4.5r$<br>Per channel (Note 5)            |                                              | 5mW, $R_L = 32\Omega$ ,     |       | 6.8  |       | mW                |

| ·                                   |                       |                                                  | P <sub>OUT</sub> = 20<br>(Note 6)            | OmW, $R_L = 32\Omega$ ,     |       | 23   |       |                   |

|                                     |                       | Output voltage needed THSH = 0                   |                                              | THSH = 0                    |       | 0.4  |       |                   |

| Charge-Pump Switch Threshold        |                       | to toggle the                                    | charge-                                      | THSH = 1                    |       | 0.55 |       | V                 |

| Click-and-Pop Level                 | KCP                   | $R_L = 32\Omega$ , p                             | $R_L = 32\Omega$ , peak voltage, A-weighted, |                             |       | -74  |       | dBV               |

| olicit and 1 op 20vol               | ROI                   | 32 samples/                                      |                                              | Out of shutdown             |       | -74  |       | GBV               |

| Input Capacitance                   | C <sub>IN</sub>       | Gain = 6dB                                       |                                              |                             |       | 150  |       | рF                |

| Input Impedance                     | Z <sub>IN</sub>       |                                                  |                                              |                             | 16    |      | 75    | kΩ                |

| AUDIO AMPLIFIER VOLUME CON          |                       |                                                  | -                                            |                             |       |      |       |                   |

| Gain Range                          |                       | From min to                                      | max volum                                    | e setting                   | -60   |      | +6    | dB                |

| Maximum Volume Setting              |                       |                                                  |                                              |                             | 5.5   | 6    | 6.5   | dB                |

| Minimum Volume Setting              |                       |                                                  |                                              |                             | -60.5 | -60  | -59.5 | dB                |

| Mute Attenuation                    |                       |                                                  |                                              |                             |       | 80   |       | dB                |

| Channel-to-Channel Gain<br>Matching |                       |                                                  |                                              |                             | -0.5  |      | +0.5  | dB                |

|                                     |                       | Volume setti                                     | na -54dB <                                   | _VOL ≤ 6dB                  |       | 1    |       |                   |

| Gain Change per Step                |                       |                                                  |                                              | <br>VOL ≤ -54dB             |       | 2    |       | dB                |

| MICROPHONE BIAS                     |                       | 1                                                |                                              |                             |       |      |       |                   |

| MIC Bias Supply Voltage             | V <sub>MICVDD</sub>   | Guaranteed                                       | by MIC bia                                   | s PSRR test                 | 2.4   |      | 3.6   | V                 |

|                                     |                       | High output                                      |                                              |                             | 2.4   | 2.6  | 2.8   |                   |

| Bias Output Voltage                 | $V_{BIAS}$            | Low output v                                     |                                              |                             | 1.84  | 2    | 2.16  | V                 |

| Bias Output Current                 | I <sub>BIAS_OUT</sub> | R <sub>MICBIAS</sub> = voltage, T <sub>A</sub> : |                                              | (2.6V) output               | 1.2   |      |       | mA                |

| MIC Supply Current Consumption      | I <sub>MBIAS</sub>    |                                                  |                                              |                             |       | 150  | 400   | μΑ                |

|                                     |                       | $MICR = 0b0$ $T_A = +25^{\circ}C$                | 0, V <sub>MBIAS</sub> =                      | = 2.6V,                     | 2.02  | 2.2  | 2.38  |                   |

| Di O I I D I I                      | 0                     | $MICR = 0b0$ $T_A = +25^{\circ}C$                | 2.39                                         | 2.6                         | 2.81  | 1.0  |       |                   |

| Bias Output Resistance              | R <sub>MBIAS</sub>    | $MICR = 0b1$ $T_A = +25^{\circ}C$                | MICR = 0b10, V <sub>MBIAS</sub> = 2.6V,      |                             |       |      | 3.24  | kΩ                |

|                                     |                       | $MICR = 0b1$ $T_A = +25^{\circ}C$                | 1, V <sub>MBIAS</sub> =                      | = 2.6V,                     |       | 0.07 |       |                   |

| Bias Output Noise                   | V <sub>N_BIAS</sub>   | With externa                                     | l capacitor                                  | , V <sub>MBIAS</sub> = 2.6V |       | 2.8  |       | μV <sub>RMS</sub> |

|                                     |                       |                                                  |                                              |                             |       |      |       |                   |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 1.8V, V_{MICVDD} = 3.0V, V_{GND} = V_{PGND} = 0V, C_{FLY} = C_{PVDD} = C_{PVSS} = 1\mu F.$  Typical values tested at TA = +25°C, unless otherwise noted. See the *Functional Diagram/Typical Application Circuit.*) (Note 2)

| PARAMETER                                  | SYMBOL                  | CONDITIONS                                |                                                                                                                                           |     | TYP   | MAX | UNITS |

|--------------------------------------------|-------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| Bias Power-Supply Rejection                | PSRR <sub>MBIAS</sub>   | D                                         | $V_{MICVDD} = 2.4V \text{ to}$<br>3.6V, $T_A = +25^{\circ}C$                                                                              | 74  | 90    |     | dB    |

| Bias i ower-supply riejection              | 1 SHIMBIAS              | $R_{MBIAS} = 2.2k\Omega$                  | $f_{IN} = 2kHz$ , $100mV_{P-P}$ ripple                                                                                                    |     | 75    |     | QD.   |

| MICROPHONE PREAMPLIFIER                    |                         |                                           |                                                                                                                                           |     |       |     |       |

| MIC Prooms Coin                            | A                       | Gain = high, f <sub>IN</sub> =            | 997Hz                                                                                                                                     | 23  | 24    | 25  | dB    |

| MIC Preamp Gain                            | Аміс                    | Gain = low, f <sub>IN</sub> =             | 997Hz                                                                                                                                     | 11  | 12    | 13  | ub    |

| Supply Current Consumption                 | I <sub>DD_MAMP</sub>    |                                           |                                                                                                                                           |     | 200   | 300 | μA    |

| MIC Preamp Noise                           | V <sub>N_MAMP</sub>     | Input referred (No<br>A-weighted 0.1kH    | ote 7), gain = 24dB,<br>Iz to 7kHz                                                                                                        |     | 3     |     | μV    |

| Total Harmonic Distortion Plus Noise       | THD+N <sub>MICPRE</sub> | f <sub>IN</sub> = 1kHz, V <sub>IN</sub> = | 1V <sub>RMS</sub>                                                                                                                         |     |       | 3   | %     |

| Low Corner Frequency Response              | f <sub>-3dB</sub>       | Relative to 997Hz                         |                                                                                                                                           |     | 15    |     | Hz    |

| High Corner Frequency Response             | f-3dB                   | Relative to 997Hz                         | _                                                                                                                                         |     | > 300 |     | kHz   |

| MIC Preamplifier Power-Supply<br>Rejection | PSR <sub>MAMP</sub>     |                                           | $V_{\text{MICVDD}} = 2.4 \text{V to } 3.6 \text{V}, T_{\text{A}} = +25 ^{\circ} \text{C},$<br>gain = +24dB, $R_{\text{MIC}} = 500 \Omega$ |     | 90    |     | dB    |

| The jection                                |                         | $f_{IN} = 2kHz$ , 100m                    |                                                                                                                                           | 58  |       |     |       |

| Output Common-Mode Voltage                 | V <sub>CM_MIC</sub>     | Voltage measured MOUTN to GND             | d from MOUTP or                                                                                                                           |     | 0.8   |     | V     |

| Input Capacitance                          | C <sub>MAMP</sub>       | AC-coupling capa                          | acitance                                                                                                                                  |     | 85    |     | pF    |

| Input Resistance                           | R <sub>MAMP</sub>       | Input resistance                          |                                                                                                                                           |     | 100   |     | МΩ    |

| Output Impedance                           | Z <sub>OUT</sub>        |                                           |                                                                                                                                           |     | 10    |     | Ω     |

| 6-BIT KEY ENCODER ADC                      |                         |                                           |                                                                                                                                           |     |       |     |       |

| ADC Trip Level                             |                         | Level at which the trigger a conversi     | e mic bias must drop to ion                                                                                                               |     | 0.64  |     | V     |

| Minimum ADC Course Range                   |                         | LSB 10mV                                  |                                                                                                                                           |     | 0.128 |     | V     |

| Maximum ADC Course Range                   |                         | LSB 10mV                                  |                                                                                                                                           |     | 0.64  |     | V     |

| Minimum ADC Fine Range                     |                         | LSB 2mV                                   |                                                                                                                                           | 0   |       | V   |       |

| Maximum ADC Fine Range                     |                         | LSB 2mV                                   |                                                                                                                                           |     | 0.128 |     | V     |

| CHARGE PUMP                                |                         |                                           |                                                                                                                                           |     |       |     |       |

| Oscillator Frequency                       | fosc1                   | $V_{OUT} = 0V, R_L =$                     | open, T <sub>A</sub> = +25°C                                                                                                              | 78  | 83    | 88  | kHz   |

| Osomator Frequency                         | f <sub>OSC2</sub>       | $V_{OUT} = 0.2V, R_L$                     | = open                                                                                                                                    | 665 |       |     | I II  |

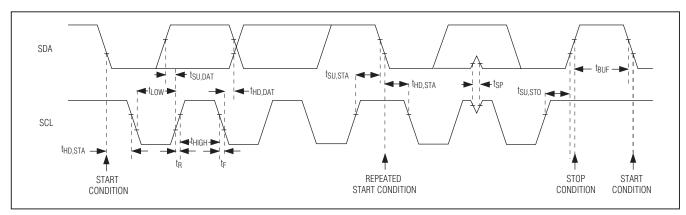

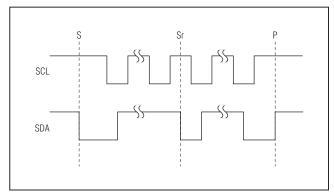

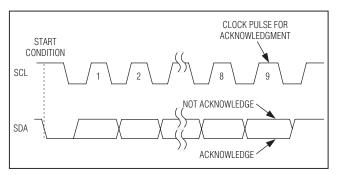

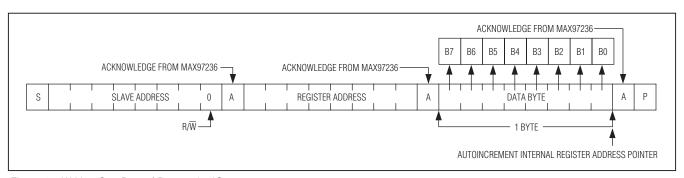

## **I<sup>2</sup>C TIMING CHARACTERISTICS**

(TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25°C.) (Note 2)

| PARAMETER                                       | SYMBOL              | CONDITIONS | MIN                       | TYP | MAX | UNITS |

|-------------------------------------------------|---------------------|------------|---------------------------|-----|-----|-------|

| Serial-Clock Frequency                          | f <sub>SCL</sub>    |            | 0                         |     | 400 | kHz   |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>    |            | 1.3                       |     |     | μs    |

| Hold Time (REPEATED) START Condition            | t <sub>HD,STA</sub> |            | 0.6                       |     |     | μs    |

| SCL Pulse-Width Low                             | t <sub>LOW</sub>    |            | 1.3                       |     |     | μs    |

| SCL Pulse-Width High                            | <sup>t</sup> HIGH   |            | 0.6                       |     |     | μs    |

| Setup Time for a REPEATED START Condition       | t <sub>SU,STA</sub> |            | 0.6                       |     |     | μs    |

| Data Hold Time                                  | t <sub>HD,DAT</sub> |            | 0                         |     | 900 | ns    |

| Data Setup Time                                 | t <sub>SU,DAT</sub> |            | 100                       |     |     | ns    |

| SDA and SCL Receiving Rise Time                 | t <sub>R</sub>      |            | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA and SCL Receiving Fall Time                 | t <sub>F</sub>      |            | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |

| SDA Transmitting Fall Time                      | t <sub>F</sub>      |            | 20 +<br>0.1C <sub>B</sub> |     | 250 | ns    |

| Setup Time for STOP Condition                   | t <sub>SU,STO</sub> |            | 0.6                       |     |     | μs    |

| Bus Capacitance                                 | C <sub>B</sub>      |            |                           |     | 400 | pF    |

| Pulse Width of Suppressed Spike                 | t <sub>SP</sub>     |            | 0                         |     | 50  | ns    |

- Note 2: All specifications are 100% tested at T<sub>A</sub> = +25°C. Temperature limits are guaranteed by design.

- **Note 3:** The current listed toN is the time from the system sending the enable signal, after receiving the DDONE signal, to when the amplifier outputs turn on.

- Note 4: Total turn-on time from jack insert to output enable is dependent upon the search algorithm.

- Note 5: Power consumption numbers taken with the THRH bit set high, fixing the power-supply switchover threshold at its highest value.

- **Note 6:** Power consumption numbers taken with the high efficiency bit set low, fixing the power-supply switchover threshold at its lowest value, providing the least amount of dynamic distortion.

- **Note 7:** Tested with R<sub>MIC</sub> =  $6k\Omega$  in parallel with 5pF connected from SLEEVE to RING2.

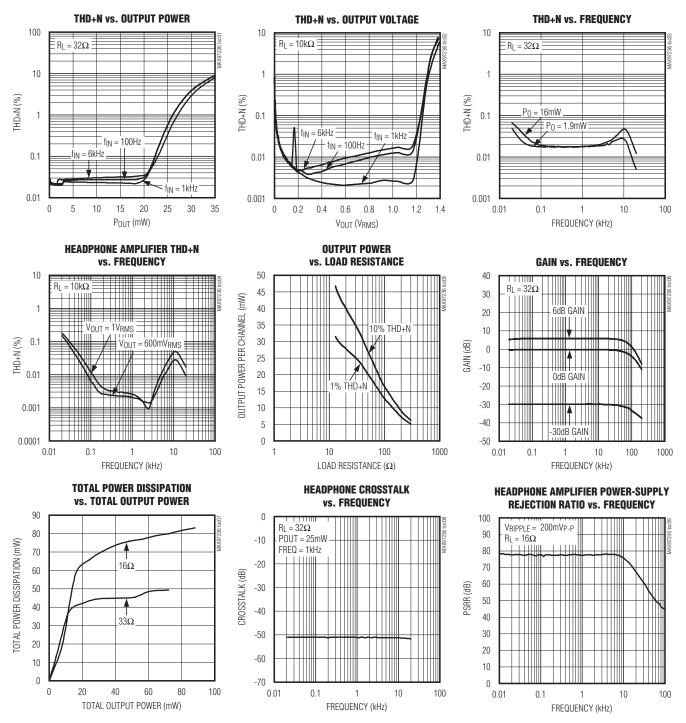

## Typical Operating Characteristics

(VDD = 1.8V, VMICVDD = 3.0V, VGND = VPGND = 0V, CFLY = CPVDD = CPVSS = 1µF.)

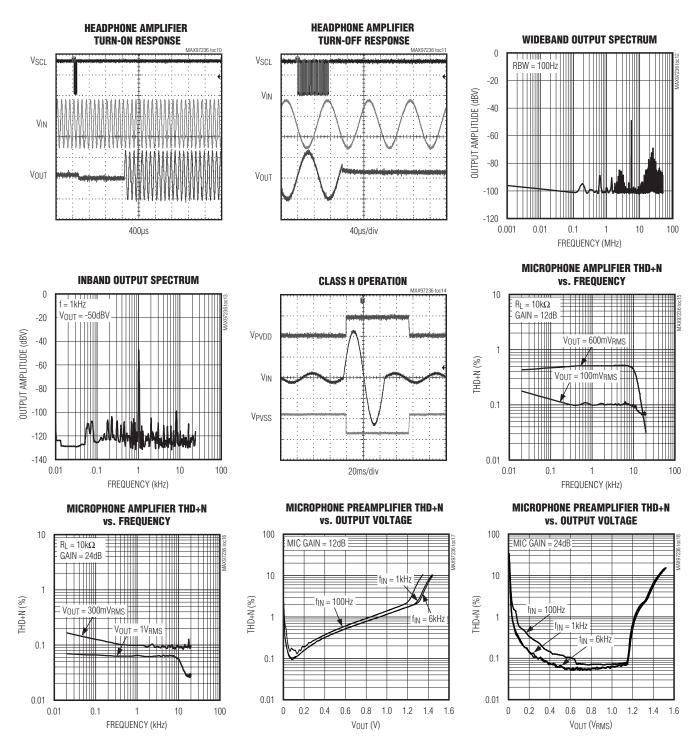

## Typical Operating Characteristics (continued)

$(V_{DD} = 1.8V, V_{MICVDD} = 3.0V, V_{GND} = V_{PGND} = 0V, C_{FLY} = C_{PVDD} = C_{PVSS} = 1\mu F.)$

## **Typical Operating Characteristics (continued)**

$(V_{DD} = 1.8V, V_{MICVDD} = 3.0V, V_{GND} = V_{PGND} = 0V, C_{FLY} = C_{PVDD} = C_{PVSS} = 1\mu F.)$

# MICROPHONE PREAMPLIFIER POWER-SUPPLY REJECTION RATIO vs. FREQUENCY

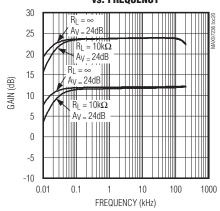

## MICROPHONE AMPLIFIER GAIN vs. FREQUENCY

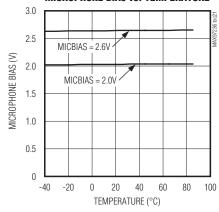

#### **MICROPHONE BIAS vs. TEMPERATURE**

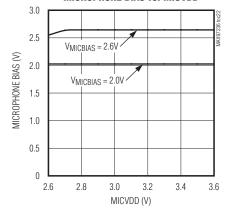

### **MICROPHONE BIAS vs. MICVDD**

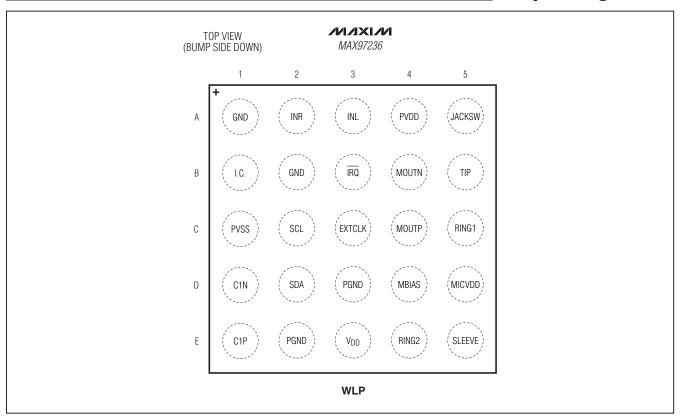

## **Bump Configuration**

## **Bump Description**

| BUMP   | NAME   | FUNCTION                                                                                                        |

|--------|--------|-----------------------------------------------------------------------------------------------------------------|

| A1, B2 | GND    | Analog Ground                                                                                                   |

| A2     | INR    | Right Audio Input                                                                                               |

| А3     | INL    | Left Audio Input                                                                                                |

| A4     | PVDD   | Charge-Pump Positive Output. Bypass to PGND with 1µF.                                                           |

| A5     | JACKSW | Jack Switch. Connect to the mechanical switch.                                                                  |

| B1     | I.C.   | Internally Connected. Leave unconnected.                                                                        |

| В3     | ĪRQ    | Interrupt Request Flag. Open-drain, active-low digital output. Pullup with $10k\Omega$ to system logic voltage. |

| B4     | MOUTN  | Negative Microphone Output                                                                                      |

| B5     | TIP    | Left Headphone Output. Connect to the tip of the four-pole jack.                                                |

| C1     | PVSS   | Charge-Pump Negative Output. Bypass to PGND with 1µF.                                                           |

| C2     | SCL    | I <sup>2</sup> C Serial-Clock Input                                                                             |

| C3     | EXTCLK | External System Clock Input. All internal digital clocks are derived from EXTCLK.                               |

## Pin Description (continued)

| BUMP   | NAME            | FUNCTION                                                                              |

|--------|-----------------|---------------------------------------------------------------------------------------|

| C4     | MOUTP           | Positive Microphone Output                                                            |

| C5     | RING1           | Jack Input 2/Right Headphone Output. Connect to the first ring of the four-pole jack. |

| D1     | C1N             | Charge-Pump Flying Capacitor Negative Connection. Connect 1µF between C1N and C1P.    |

| D2     | SDA             | Serial-Data I/O                                                                       |

| D3, E2 | PGND            | Power Ground. Ground Return for the charge pump.                                      |

| D4     | MBIAS           | Microphone Bias Capacitor Connection. Connect 1µF to GND.                             |

| D5     | MICVDD          | Microphone Power-Supply Input. Bypass to GND with 1µF.                                |

| E1     | C1P             | Charge-Pump Flying Capacitor Positive Connection. Connect 1µF between C1N and C1P.    |

| E3     | V <sub>DD</sub> | Main Power-Supply Input. Connect to 1.8V and bypass to GND with 1µF.                  |

| E4     | RING2           | Microphone Input Headset GND. Connect to the second ring of the four-pole jack.       |

| E5     | SLEEVE          | Microphone Input Headset GND. Connect to the sleeve of the four-pole jack.            |

## **Detailed Description**

# Class H DirectDrive Headphone Amplifier with Dual-Mode Charge Pump

The headphone amplifier is optimized for low-power consumption and low noise. A charge pump generates a negative and positive supply voltage that powers the headphone amplifier and eliminates the need for a large output coupling capacitor.

The headphone amplifier has volume control from -60dB to +6dB. A single-pole filter,  $f_{-3dB} = 85 \text{kHz}$ , attenuates signals outside the audio band.

#### **Dual-Mode Charge Pump**

The charge pump powers the headphone amplifier. When a headphone load is connected and the audio output signal is small, the charge pump outputs a  $\pm 0.9$ V negative and positive supply voltage. When a large audio signal is applied, the output rails of the charge pump switch to a higher voltage mode,  $\pm 1.8$ V. The higher voltage rails accommodate the higher voltage swing necessary to amplify line level audio signals. The lower voltage rails reduce the power consumption of the headphone amplifier when higher rails are not needed.

#### Class H Operation

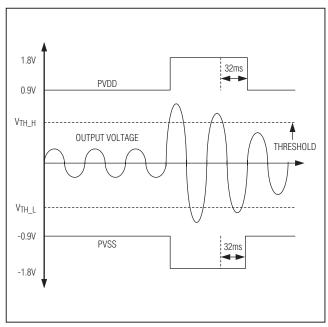

The Class H amplifier employs a class AB output stage with power-supply voltages that shift based on the output signal needs (Figure 1). The lower power supply rails are

used when the output voltage requirements are below the 0.5V threshold. The higher supply rails are used when the output voltage is above the 0.5V threshold, maximizing output power and voltage swing. The switch between available power-supply voltages occurs on a cycle-by-cycle basis.

Figure 1. Class H Power-Supply Operation

#### **Audio Short-Circuit Protection**

A short on the right audio output does not shut down the left audio channel. A short on the left audio output does not shut down the right audio channel. This ensures that a mono audio plug does not damage the chip, but allows audio to be heard through the other channel output. A short is considered anything below  $4\Omega$  for a time period of 100ms.

#### **Ground Sense**

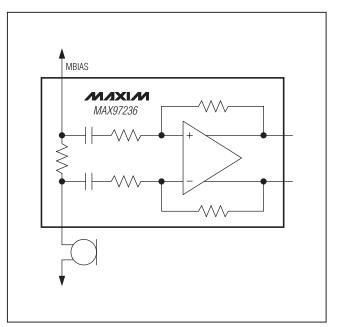

The headphone amplifier features output ground sensing for improved crosstalk performance. Crosstalk is improved by at least 20dB, between the audio channels, which all share a common jack ground. Figure 2 shows the audio signal path from the filter through the amplifier with volume control and the ground sense.

### **Headphone Amplifier Input Filter**

The headphone amplifiers employ a lowpass filter to remove out-of-band noise from the audio DAC driving the headphone inputs. The filter attenuates frequencies above 85kHz.

### **Headphone Amplifier Volume Control**

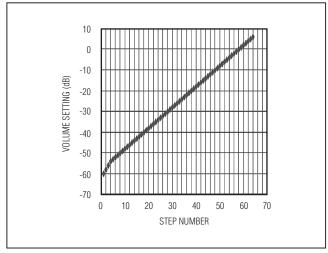

The IC features a 64-step volume control with a resolution of 1dB/step from +6dB down to -54dB and 2dB/step from -54dB to -60dB. <u>Figure 3</u> shows the I/O curve of the volume control.

#### Headphone Volume Slewing

Volume slewing breaks up large volume changes into the smallest available step size as it goes through each gain level between the initial and final volume setting. Volume

MAXIM

MAX97236

RING1

OR TIP

RING2

OR SLEEVE

PGND

Figure 2. Headphone Amplifier Signal Path

slewing also occurs at device turn-on and turn-off when enabled. During turn-on, the volume is set to mute before the output is enabled. Once the output is on, the volume ramps to the programmed level. At turn-off, the volume is ramped to mute before the output is disabled.

As briefly described in the last section, the  $\overline{\text{VSEN}}$  (volume slew enable) bit decides whether each volume step is used when changing volume settings or whether the final volume setting jumps to the new value after writing. The volume slew enable function is used in conjunction with the zero-crossing detection enable ( $\overline{\text{ZDEN}}$ ).

#### Examples:

**VSEN** = **0**, **ZDEN** = **0**, **both functions on:** The volume changes one gain step at a time. The gain only changes at the zero crossing of the audio signal.

**VSEN** = **0**, **ZDEN** = **1**: The volume changes one gain step at a time.

**VSEN** = 1, **ZDEN** = 0: New volume is asserted as soon as audio signal has gone through a zero crossing (or 100ms after the last gain change, whichever comes first).

$\overline{\text{VSEN}}$  = 1,  $\overline{\text{ZDEN}}$  = 1: New volume is asserted as soon as the I<sup>2</sup>C command is received.

#### Headphone Volume Zero-Crossing Detection

Zero-crossing detection is implemented on the headphone amplifier volume control to prevent large glitches when volume changes are made. Instead of making a volume change immediately when requested, the change is made when the audio signal has a zero crossing or after 100ms, whichever comes first.

Figure 3. Headphone Volume Control Input/Output Transfer Function

#### Microphone Bias

The IC features a low-noise microphone bias generator and amplifier. The bias voltage resistors are selectable through I<sup>2</sup>C register 0x09.

Ensure that  $V_{MICVDD}$  is greater than the desired microphone bias voltage.

The microphone bias line is also used by passive single button and passive multibutton headsets.

### Microphone Preamplifier

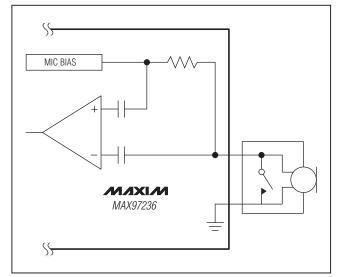

A microphone preamplifier provides an additional gain of 12dB or 24dB (programmable) with low input-referred noise and high power-supply rejection. Figure 4 shows the configuration of the microphone bias, amplifier, and microphone. Internal AC-coupling capacitors connect both the microphone output and also the MBIAS line to a differential amplifier, giving improved PSRR.

Figure 4. Microphone Preamplifier Simplified Schematic

# Jack Detection and Configuration Algorithm

The IC features a detection scheme that senses when a 3.5mm plug is inserted into the system jack. After sensing insertion, a configuration detection algorithm takes over and reads the makeup of the installed plug. Information regarding the makeup of the plug is reported back through the I<sup>2</sup>C status registers. The device can also be placed in autoconfigure mode. This mode allows the IC to automatically enable the correct functional blocks depending upon the class of cable that has been inserted.

### Jack Insertion Testing

The jack insertion detection uses an inaudible AC waveform output on the jack pins to sense when a load is plugged in. This electrical test is used to verify and work in conjunction with a mechanical switch (JACKSW). The mechanical switch, while not used as the main sensing mechanism, can be used to save system power. When a jack is plugged into a device, the switch at JACKSW is closed. When no jack is plugged in, the switch at JACKSW is working, the electrical polling of the jack can be done less often. A test is done every time a jack is sensed to check if the switch at JACKSW is working correctly. If the IC deems that the switch at JACKSW is broken, the system is flagged. At that point, the system can decide whether to ignore JACKSW results and poll more quickly.

#### **Jack Configuration Detection**

The jack detection and configuration is bounded by certain load resistance and capacitance limitations. The correct detection and configuration cannot be guaranteed outside those limitations. The limitations are shown in Table 1.

Table 2 shows each load case that is detectable with the IC's jack configuration algorithm and which class of cable is found. The status bits of the I<sup>2</sup>C register (0x01, 0x02, 0x03) report the load found during testing. The functional blocks are set automatically if AUTO = 10 or 01 (register 0x01E bits 0 and 1), according to what class of cable is detected.

Table 1. Jack Detection and Configuration Load Limits

| PARAMETER                  | SYMBOL             | MIN | TYP | MAX  | UNITS |

|----------------------------|--------------------|-----|-----|------|-------|

| Cable Shield Capacitance   | C <sub>CABLE</sub> | 150 |     | 500  | рF    |

| Headphone Load Resistance  | R <sub>HP</sub>    | 12  |     | 650  | Ω     |

| Headphone Load Inductance  | L <sub>HP</sub>    | 30  |     | 1600 | μΗ    |

| Audio Line Load Resistance | R <sub>LINE</sub>  | 6   |     | 50   | kΩ    |

| Microphone Load Resistance | R <sub>MIC</sub>   | 0.5 |     | 15   | kΩ    |

Case 9 is a special case that requires subsequent testing of the load pins while servicing the left audio load that has been found. In this case only, the status bits report that a line level audio load had been found on TIP while tests continue to run on RING1 and SLEEVE. Once a load is found with one of the subsequent tests, enough information about the cable class is known to stop testing. The status bits reflect what is found, and the signal paths are configured according to the cable class and testing stops.

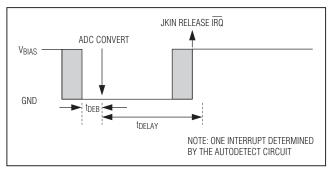

#### Detecting Jack Removal

There are two main jack removal detection methods: an electrical method and a mechanical method. The electrical

unplug detection method varies, depending on which load is plugged in. Cases with a microphone wait for the microphone bias to fly up to its full value. The audio only headphones wait for SLEEVE to fly up when the jack is removed.

For cases with an AV cable and audio only connected, the IC can only rely on JACKSW to sense removal or to wait for user input to shut down audio.

The electrical unplug detection (JKIN bit) is not available when the IC is running the jack configuration algorithm, when in FORCE mode, or when in test mode. In those cases, an unplug can only be detected mechanically through the JACKSW bit.

Table 2. Jack Configurations and Status Registers (After DDONE Bit Has Been Reset)

| CASE | CABLE CLASS                                            |   | PI      | NS |       | JACKSW | REGISTER | REGISTER | REGISTER |

|------|--------------------------------------------------------|---|---------|----|-------|--------|----------|----------|----------|

| NO.  | CABLE CLASS                                            | 1 | 1 2 3 4 |    | STATE | 0x00   | 0x01     | 0x02     |          |

| 1    | Nothing                                                | F | F       | F  | F     | Short  | 0x00     | 0x00     | 0x00     |

| 2    | Extension cable                                        | С | С       | С  | С     | Open   | 0x84     | 0x00     | 0x00     |

| 3    | Stereo headset (headphones with microphone), GND on P3 | L | R       | G  | М     | Open   | 0x8C     | 0x30     | 0x01     |

| 4    | Stereo headset (headphones with microphone), GND on P4 | L | R       | М  | G     | Open   | 0x8C     | 0x30     | 0x02     |

| 5    | Line audio cable                                       | L | R       | G  | G     | Open   | 0x84     | 0xC0     | 0x03     |

| 6    | Mono headset, GND on P3                                | L | G       | G  | М     | Open   | 0x8C     | 0x20     | 0x01     |

| 7    | Mono headset, GND on P4                                | L | G       | М  | G     | Open   | 0x8C     | 0x20     | 0x02     |

| 8    | Mono headset, GND on P3                                | L | L       | G  | М     | Open   | 0x8C     | 0x20     | 0x01     |

| 9    | Mono headset, GND on P4                                | L | L       | М  | G     | Open   | 0x8C     | 0x20     | 0x02     |

| 10   | Mono headset, GND on P3                                | L | F       | G  | М     | Open   | 0x8C     | 0x20     | 0x01     |

| 11   | Mono headset, GND on P4                                | L | F       | М  | G     | Open   | 0x8C     | 0x20     | 0x02     |

| 12   | Stereo headphones                                      | L | L       | G  | G     | Open   | 0x84     | 0x30     | 0x03     |

| 13   | Stereo headphones, right channel open                  | L | F       | G  | G     | Open   | 0x84     | 0x20     | 0x03     |

| 14   | Stereo headphones, left channel open                   | F | L       | G  | G     | Open   | 0x84     | 0x10     | 0x03     |

### **Key Switch Encoder**

There are two types of keypads that can be connected to the IC:

- A single-button hook switch or MIC switch that grounds out the microphone bias when pressed

- A passive multibutton headset

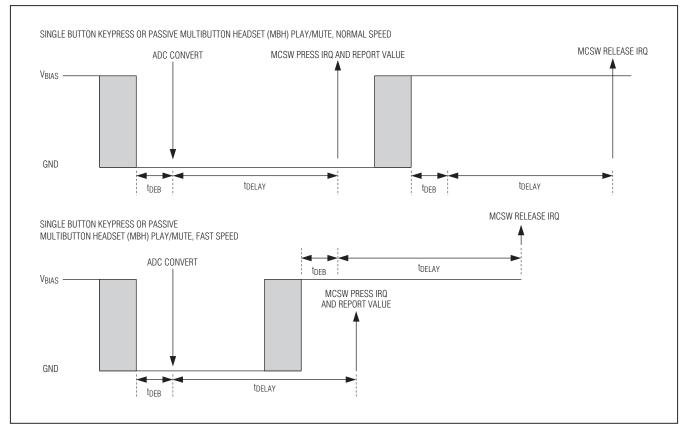

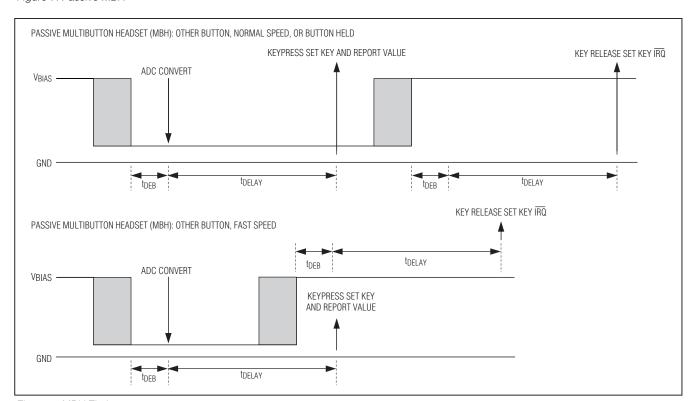

### Key Switch Encoder Timing

Two registers, 0x15 and 0x16, control the key switch debounce time,  $t_{DEB}$ , and delay time,  $t_{DELAY}$ .

The debounce time, 0x15, is the time from when the switch stops bouncing and when the ADC converts.

The delay time, 0x16, is set long to ensure that an unplug event is not encoded as a keypress. See Figure 9.

### The PRESS Bit

The PRESS bit alerts the system to whether the current interrupt was caused by a button press or release.

Figure 5. Passive Single-Button Hook Switch

Figure 6. Single-Button, Passive Multibutton Hook Switch/Microphone Switch Timing

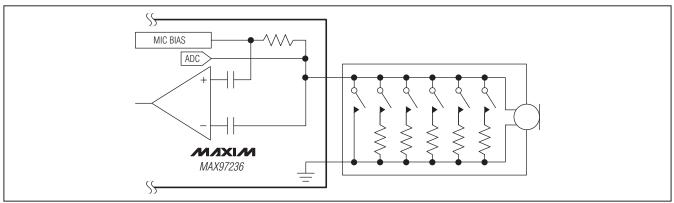

#### Passive Multibutton Headset (MBH)

A passive MBH consists of a microphone with numerous switches that connect different value resistors to ground. The switched resistor and the microphone bias resistor set up a voltage-divider that creates a unique voltage. The on-chip ADC then encodes the voltage and reports to the system.

A maximum  $0.5\Omega$  resistance between IC pins RING2 and SLEEVE and the headset is required for proper operation of the passive multibutton headset.

Figure 7 shows the circuit diagram of a passive MBH.

<u>Figure 8</u> shows the timing for a fast or normal speed keypress on a passive MBH. Note that a keypress develops a voltage that is above ground. The switch that shorts the microphone bias to ground is handled like the hook switch in the previous section.

Figure 7. Passive MBH

Figure 8. MBH Timing

#### Slow Jack Removal

Removing the headphone jack slowly can cause a false trigger of the key switch encoder because the right speaker between RING1 and RING2 shorts between microphone bias and ground. The programmable delay time must be set by the system to mask out this slow removal so that an interrupt does not flag until the JKIN status bit tells the system the jack is unplugged. Figure 9 shows the timing and interrupt reporting for a slow jack removal event. The act of microphone bias flying all the way up is the trigger for a microphone removal event. The <u>Jack Detection and Configuration Algorithm</u> section explains more about sensing jack removal.

Figure 9. Slow Jack Removal Timing

## Register and Bit Descriptions

## **Table 3. Register Map**

| REGISTER                     | В7          | В6          | B5    | B4    | В3        | B2     | B1    | В0   | ADDRESS | DEFAULT | R/W |

|------------------------------|-------------|-------------|-------|-------|-----------|--------|-------|------|---------|---------|-----|

| Status1                      | JKIN        | DDONE       | VOL   | _     | MIC_IN    | JACKSW | MCSW  | MBH  | 0x00    | 0x00    | R   |

| Status2                      | LINE_L      | LINE_R      | HP_L  | HP_R  | JACKSWINC | KEY    | _     | _    | 0x01    | 0x00    | R   |

| Status3                      | _           | _           | _     | _     | _         | _      | G۱    | 1D   | 0x02    | 0x00    | R   |

| For Expansion                | _           | _           | _     | _     | _         | _      | _     | _    | 0x03    | _       | _   |

| IRQ Mask1                    | IJKIN       | IDDONE      | IVOL  | _     | IMIC      | JACKSW | IMCSW | IMBH | 0x04    | 0x00    | R/W |

| IRQ Mask2                    | ILINE_L     | ILINE_R     | IHP_L | IHP_R | IJACKSW   | IKEY   | _     |      | 0x05    | 0x00    | R/W |

| For Expansion                | _           | _           | _     | _     | _         | _      | _     | _    | 0x06    | _       | _   |

| Left Volume                  | L = R       | MUTEL       |       |       | LV        | OL     |       |      | 0x07    | 0xC0    | R/W |

| Right Volume                 | _           | MUTER       |       |       | RV        | OL     |       |      | 0x08    | 0x40    | R/W |

| Microphone                   | _           | GAIN        |       | MICF  | }         | BIAS   | _     |      | 0x09    | 0x00    | R/W |

| For Expansion                |             |             |       | For e | expansion |        |       |      | 0x0A    | 0x00    | R/W |

| Vendor ID<br>Register        | ID — — — —  |             |       |       |           |        | 0x0B  | 0x90 | R       |         |     |

| For Expansion                |             |             |       | For e | expansion |        |       |      | 0x0C    | 0x00    | R/W |

| For Expansion                |             |             |       | For e | expansion |        |       |      | 0x0D    | 0x00    | R/W |

| For Expansion                |             |             |       | For e | expansion |        |       |      | 0x0E    | 0x00    | R/W |

| For Expansion                |             |             |       | For e | expansion |        |       |      | 0x0F    | 0x00    | R/W |

| For Expansion                |             |             |       | For e | expansion |        |       |      | 0x10    | 0x00    | R/W |

| For Expansion                |             |             |       | For e | expansion |        |       |      | 0x11    | 0x00    | R/W |

| Keyscan Clock<br>Divider 1   |             |             |       | KEY_  | DIV_HIGH  |        |       |      | 0x12    | 0x00    | R/W |

| Keyscan Clock<br>Divider 2   |             | KEY_DIV_LOW |       |       |           |        |       |      | 0x13    | 0x00    | R/W |

| Keyscan Clock<br>Divider ADC | KEY_DIV_ADC |             |       |       |           |        |       | 0x14 | 0x00    | R/W     |     |

| Keyscan<br>Debounce          |             |             |       | KE    | EY_DEB    |        |       |      | 0x15    | 0x00    | R/W |

| Keyscan Delay                |             |             |       | KE    | EY_DEL    |        |       |      | 0x16    | 0x00    | R/W |

Table 3. Register Map (continued)

|                             | _     |         |         | -                                  |         |      |    |      |         |         |     |

|-----------------------------|-------|---------|---------|------------------------------------|---------|------|----|------|---------|---------|-----|

| REGISTER                    | B7    | B6      | B5      | B4                                 | В3      | B2   | B1 | В0   | ADDRESS | DEFAULT | R/W |

| Passive MBH<br>Keyscan Data | PRESS | RANGE   | KEYDATA |                                    |         |      |    | 0x17 | 0x00    | R       |     |

| DC Test Slew<br>Control     |       | DC_SLEW |         |                                    |         |      |    | 0x18 | 0x00    | R/W     |     |

| State Forcing               | _     | _       | FORCE   | FORCE STATE —                      |         |      |    | 0x19 | 0x20    | R/W     |     |

| AC Test Control             | _     | _       | AC_RE   | AC_REPEAT_ PULSE_WIDTH_ PULSE_AMP_ |         |      |    | 0x1A | 0x05    | R/W     |     |

| For Expansion               | _     | _       | _       | _                                  | _       | _    | _  | _    | 0x1B    | _       | _   |

| For Expansion               |       | _       |         | _                                  | _       | _    |    | _    | 0x1C    | _       | _   |

| Enable1                     | SHDN  | RESET   | _       | MIC_<br>BIAS                       | MIC_AMP | KS   | _  | _    | 0x1D    | 0x00    | R/W |

| Enable2                     | LFTEN | RGHEN   | VSEN    | ZDEN                               | FAST    | THRH | AU | TO   | 0x1E    | 0x00    | R/W |

### **Device Status Registers**

Registers 0x00 and 0x01 are used to report the makeup of the inserted jack as well as report when a microphone switch has been pressed or the jack has been removed. The IC uses registers 0x00, 0x01, 0x02, and  $\overline{\text{IRQ}}$  to report the status of various device functions. The Status\_ register bits are set when their respective event occurs. Device status can be determined either by polling registers 0x00, 0x01, and 0x02 or configuring the  $\overline{\text{IRQ}}$  to go low when specific events occur. Registers 0x04 and 0x05 determine which bits in the Status\_ register trigger  $\overline{\text{IRQ}}$  to go low.  $\overline{\text{IRQ}}$  is cleared upon reading the register.

**Table 4. Configuration and Device Status Registers**

| REGISTER    | BIT | NAME  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | 7   | JKIN  | Jack Detected  JKIN changes state when the jack detect circuit senses a load at the left headphone output and SHDN = high  0 = No load at TIP.  1 = Load detected at TIP.                                                                                                                                                                                                                                                 |

| Status1     | 6   | DDONE | Jack Configuration Detect Done  DDONE changes state when the jack detect algorithm finishes and the jack configuration is known and reported in the status registers 0x00, 0x01, and 0x02. Resets after reading.  0 = Jack detect algorithm is not complete.  1 = Jack detection algorithm is complete.                                                                                                                   |

| (Read Only) | 5   | VOL   | Volume Slew Complete  VOL goes high after the headphone volume has slewed to its final programmed value. VOL sets every time a gain change is complete whether the gain change is positive or negative.  Ramp the volume down and wait for VOL to set to ensure clickless turn off. Resets after reading.  0 = No volume slewing sequences have completed since any register was last read.  1 = Volume slewing complete. |

|             | 4   | _     | _                                                                                                                                                                                                                                                                                                                                                                                                                         |

**Table 4. Configuration and Device Status Registers (continued)**

| REGISTER                       | BIT | NAME      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------|-----|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                | 3   | MIC_IN    | Microphone Connected/Disconnected  MIC_IN reports when a microphone is connected or removed. Set the MIC_INM interrupt mask to alert the system when the microphone load status has changed.  0 = Microphone is removed.  1 = Microphone is connected.                                                                                                                                                                                                                                                                                     |

| Status1<br>0x00<br>(Read Only) | 2   | JACKSW    | JACKSW Status  JACKSW reports the mechanical jack switch status. For an operational mechanical jack switch, JACKSW flags at the same time. If the switch is broken, or if the jack is not plugged in all the way, JACKSW and JKIN do not report the same value. The JACKSW bit also reports when a jack has been removed. Set the PIN5M interrupt mask bit to signal the system when the status of JACKSW changes.  0 = Mechanical jack switch reports no jack is connected.  1 = Mechanical jack switch shows that the jack is connected. |

|                                | 1   | MCSW      | Microphone Switch Status  MCSW goes high when the microphone bias goes low for the debounce period plus the delay period. This happens when a switch shorts across the microphone, pulling the micbias node down, indicating a keypress from a hook switch, ADC ≤ 4 LSB.  Resets after reading.  0 = No change in microphone bias, no switch press.  1 = Microphone bias has been pulled to ground and debounced since the last status read. Debounce time set by KEY_DEB. Delay time set by KEY_DEL.                                      |

|                                | 0   | MBH       | Multibutton Headset Status  MBH reports when a keypress from a multibutton headset is ready to be read.  Resets after reading.  0 = No active keypress detected.  1 = Active keypress has been detected.                                                                                                                                                                                                                                                                                                                                   |

|                                | 7   | LINE_L    | Line-Level Load on TIP Detected  0 = Line-level load on TIP not detected.  1 = Line-level load on TIP detected.                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                | 6   | LINE_R    | Line-Level Load on ROUT Detected  0 = Line-level load on RING1 not detected.  1 = Line-level load on RING1 detected.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Status                         | 5   | HP_L      | Headphone Load on TIP Detected  0 = Headphone load on TIP not detected.  1 = Headphone load on TIP detected.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Status2<br>0x01<br>(Read Only) | 4   | HP_R      | Headphone Load on RING1 Detected  0 = Headphone load on RING1 not detected.  1 = Headphone load on RING1 detected.                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                | 3   | JACKSWINC | JACKSW Incorrect JACKSWINC reports when there are inconsistencies between the mechanical switch and the electrical plug and unplug detection. The exception is when a plug-in occurs and SHDN is LOW. JACKSWINC does NOT clear when the STATUS register is read. JACKSW is checked at jack plug-in and unplug JACKSWINC is updated when JACKSW is checked.  0 = JACKSW reporting is correct and correlates with JKIN.  1 = JACKSW reporting is not correct and does not correlate with JKIN.                                               |

## **Table 4. Configuration and Device Status Registers (continued)**

| REGISTER                       | BIT | NAME | DESCRIPTION                                                                                                                                                                                                                                                                    |

|--------------------------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status2<br>0x01<br>(Read Only) | 2   | KEY  | Passive Multibutton Headset KEY Status KEY reports when the passive multibutton has been pressed. Data is available in KEYDATA. See Figure 8. Resets after reading. 0 = No button pressed. 1 = Button has been pressed/released. Debounce and delay times have occurred.       |

|                                | 1   | _    | _                                                                                                                                                                                                                                                                              |

|                                | 0   | _    | _                                                                                                                                                                                                                                                                              |

|                                | 7   | _    | _                                                                                                                                                                                                                                                                              |

|                                | 6   | _    | _                                                                                                                                                                                                                                                                              |

|                                | 5   | _    | _                                                                                                                                                                                                                                                                              |

|                                | 4   | _    |                                                                                                                                                                                                                                                                                |

|                                | 3   | _    | _                                                                                                                                                                                                                                                                              |

| Status3                        | 2   | _    | _                                                                                                                                                                                                                                                                              |

| 0x02<br>(Read Only)            | 1   | GND  | Jack Common Location Identifier  The two GND bits tell the system whether the jack's common connection is at RING2 or SLEEVE. GND is also used to indicate when a jack has been removed.  00 = No common connection sensed, jack has been removed or nothing has been inserted |

|                                | 0   | GIND | yet.  01 = The common jack connection is RING2.  10 = The common jack connection is SLEEVE.  11 = Common on both RING2 and SLEEVE.                                                                                                                                             |

## **Interrupt Mask Registers**

The Interrupt Mask registers control which status bits flag a system interrupt. Setting an interrupt mask bit causes  $\overline{IRQ}$  to pull low whenever the target status bits set. The  $\overline{IRQ}$  output resets to high, after I<sup>2</sup>C register is read.

**Table 5. Interrupt Mask Registers**

| REGISTER          | BIT | NAME    | DESCRIPTION                                                              |

|-------------------|-----|---------|--------------------------------------------------------------------------|

|                   | 7   | IJKIN   | Jack Detect Interrupt Enable 0 = Disabled 1 = Enabled                    |

|                   | 6   | IDDONE  | Jack Configuration Detect Done Interrupt Enable 0 = Disabled 1 = Enabled |

|                   | 5   | IVOL    | Volume Slew Interrupt Enable 0 = Disabled 1 = Enabled                    |

|                   | 4   | _       | _                                                                        |

| IRQ Mask1<br>0x04 | 3   | IMIC    | Microphone Interrupt Enable 0 = Disabled 1 = Enabled                     |

|                   | 2   | JACKSW  | JACKSW Status Interrupt Enable 0 = Disabled 1 = Enabled                  |

|                   | 1   | IMCSW   | Microphone Switch Interrupt Enable 0 = Disabled 1 = Enabled              |

|                   | 0   | IMBH    | Multibutton Release Status Interrupt Enable 0 = Disabled 1 = Enabled     |

|                   | 7   | ILINE_L | Line-Level Load TIP Interrupt Enable 0 = Disabled 1 = Enabled            |

|                   | 6   | ILINE_R | Line-Level Load RING1 Interrupt Enable 0 = Disabled 1 = Enabled          |

|                   | 5   | IHP_L   | Headphone Load TIP Interrupt Enable 0 = Disabled 1 = Enabled             |

| IRQ Mask2<br>0x05 | 4   | IHP_R   | Headphone Load RING1 Interrupt Enable 0 = Disabled 1 = Enabled           |

|                   | 3   | IJACKSW | JACKSW Incorrect Interrupt Enable 0 = Disabled 1 = Enabled               |

|                   | 2   | IKEY    | KEY Interrupt Enable 0 = Disabled 1 = Enabled                            |

|                   | 1   | _       | _                                                                        |

|                   | 0   | _       | _                                                                        |

### **Headphone Volume Control Registers**

The Headphone Volume registers independently control and report the gain of the left and right headphone amplifiers. Set B7 in Register 0x07 to have the right-channel gain track the left-channel gain.

**Table 6. Headphone Volume Registers**

| REGISTER            | BIT | NAME            | DESCRIPTION                                                                                                                                                                                                                                                                  |                    |                      |                                                                   |  |  |  |

|---------------------|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|-------------------------------------------------------------------|--|--|--|

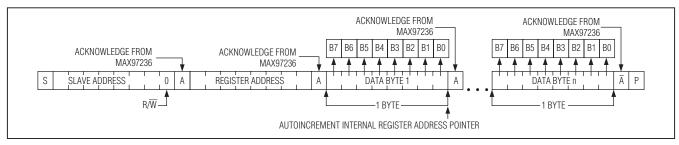

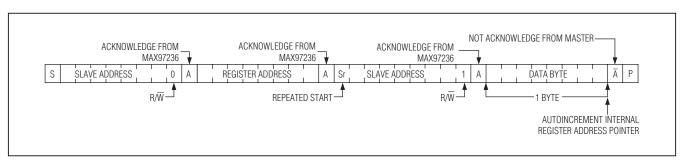

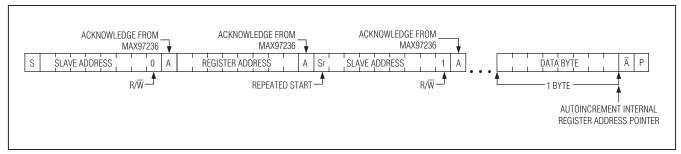

| Left Volume<br>0x07 | 7   | L = R           | Left/Right Tracking  0 = The right-channel volume control is independent of the left.  1 = The left and right volume controls track each other allowing for only one register to be written to change both channel volumes. Control both volume controls by writing to LVOL. |                    |                      |                                                                   |  |  |  |