# SSC050-01

# **Two-Wire Serial Backplane Controller**

**Data Sheet**

Revision 4.0 November 10, 2004

Maxim Integrated Products

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# Contents

#### **Revision History**

| Chapter 1 | Introduction                                | 1-1  |

|-----------|---------------------------------------------|------|

| •         | Feature Summary                             |      |

|           | Typical Applications                        |      |

|           | FC-AL Drive Enclosure Configuration         |      |

|           | General Purpose I/O Configuration           |      |

| Chapter 2 | Functional Description                      | 2-1  |

| -         | Two-wire Serial Interface                   | 2-1  |

|           | Control Registers                           |      |

|           | I/O Logic                                   |      |

|           | Clock Generator                             |      |

|           | Power-On Reset                              | 2-3  |

| Chapter 3 | Pin Description                             | 3-1  |

|           | Functional Signal Grouping                  | 3-1  |

|           | Pinout Diagram                              |      |

|           | Pin Description List                        |      |

| Chapter 4 | Control Registers                           | 4-1  |

|           | Register Map                                | 4-1  |

|           | Address Map                                 | 4-4  |

|           | Control Register Definition                 | 4-6  |

|           | 00h: General Purpose I/O Port 0 Data (GPD0) | 4-6  |

|           | 01h: General Purpose I/O Port 1 Data (GPD1) | 4-7  |

|           | 02h: General Purpose I/O Port 2 Data (GPD2) | 4-7  |

|           | 03h: General Purpose I/O Port 3 Data (GPD3) | 4-8  |

|           | 04h: General Purpose I/O Port 4 Data (GPD4) | 4-8  |

|           | 10h: I/O Port 0 Data Direction (DDP0)       | 4-9  |

|           | 11h: I/O Port 1 Data Direction (DDP1)       | 4-9  |

|           | 12h: I/O Port 2 Data Direction (DDP2)       | 4-10 |

|           | 13h: I/O Port 3 Data Direction (DDP3)       | 4-10 |

|           | 14h: I/O Port 4 Data Direction (DDP4)       | 4-11 |

|           | 20h: Port Bypass Control 0 (PBC0)           | 4-12 |

|           | 21h: Port Bypass Control 1 (PBC1)           | 4-13 |

|           | 22h: Port Bypass Control 2 (PBC2)           | 4-14 |

|           | 23h: Port Bypass Control 3 (PBC3)           | 4-15 |

|           | 24h: Port Bypass Control 4 (PBC4)           |      |

|           | 25h: Port Bypass Control 5 (PBC5)           | 4-17 |

|           | 26h: Port Bypass Control 6 (PBC6)                                 | 4-18 |

|-----------|-------------------------------------------------------------------|------|

|           | 27h: Port Bypass Control 7 (PBC7)                                 | 4-19 |

|           | 30h: Fan Speed Control 0 Register (FSC0)                          | 4-20 |

|           | 31h: Fan Speed Count Overflow 0 (FSCO0, R/W)                      | 4-22 |

|           | 32h: Fan Speed Current Count 0 (FSCC0)                            | 4-23 |

|           | 34h: Fan Speed Control 1 (FSC1)                                   | 4-24 |

|           | 35h: Fan Speed Count Overflow 1 (FSCO1)                           | 4-26 |

|           | 36h: Fan Speed Current Count 1 (FSCC1)                            | 4-27 |

|           | 38h: Fan Speed Control 2 (FSC2)                                   | 4-28 |

|           | 39h: Fan Speed Count Overflow 2 (FSCO2)                           | 4-30 |

|           | 3Ah: Fan Speed Current Count 2 (FSCC2)                            | 4-31 |

|           | 3Ch: Fan Speed Control 3 (FSC3)                                   | 4-32 |

|           | 3Dh: Fan Speed Count Overflow 3 (FSCO3)                           | 4-34 |

|           | 3Eh: Fan Speed Current Count 3 (FSCC3)                            | 4-35 |

|           | 80h-87h: Bit Control Port 0 Registers (BCP00-BCP07)               | 4-36 |

|           | 90h-97h: Bit Control Port 1 Registers (BCP10-BCP17)               | 4-38 |

|           | 98h-9Bh: Pulse Width Modulation Control Registers (PWMC0-PWMC3) . | 4-40 |

|           | A0h-A7h: Bit Control Port 2 Registers (BCP20-BCP27)               | 4-42 |

|           | B0h-B7h: Bit Control Port 3 Registers (BCP30-BCP37)               | 4-44 |

|           | C0h-C7h: Bit Control Port 4 Registers (BCP40-BCP47)               | 4-46 |

|           | F8h: Backplane Controller Interrupt Status (BCIS)                 | 4-48 |

|           | FCh: Backplane Controller Test (BCT)                              | 4-49 |

|           | FDh: Backplane Controller Option (BCO)                            | 4-50 |

|           | FFh: Backplane Controller Version (VER)                           | 4-51 |

| Chapter 5 | Electrical Characteristics                                        | 5-1  |

| -         | Maximum Ratings                                                   | 5-1  |

|           | DC Characteristics                                                |      |

|           | AC Characteristics                                                | 5-5  |

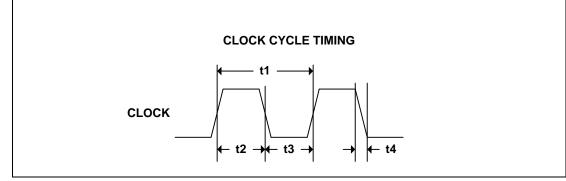

|           | External Clock Timing                                             | 5-5  |

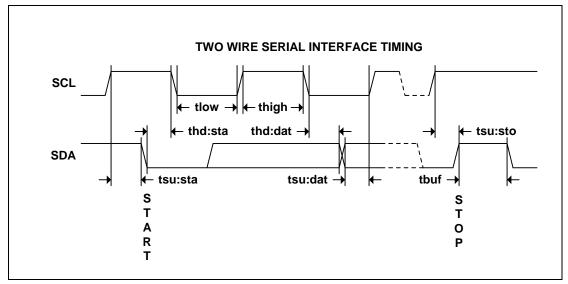

|           | Two-wire Serial Interface Operation                               | 5-7  |

|           | Oscillator Requirements                                           |      |

|           | External Reset Circuit                                            | 5-9  |

|           | Optional External Tach Filter                                     | 5-10 |

| Chapter 6 | Mechanical Drawing                                                | 6-1  |

| Chapter 7 | Ordering Information                                              | 7-1  |

| Revision | Date     | Section | Change                                    |

|----------|----------|---------|-------------------------------------------|

| 1.01     | 11/4/03  | All     | Initial Revision                          |

| 1.0      | 11/10/04 |         | Updated                                   |

| 4.0      | 11/10/04 |         | Data Manual migrated to Data Sheet status |

# **REVISION HISTORY**

# Chapter 1 Introduction

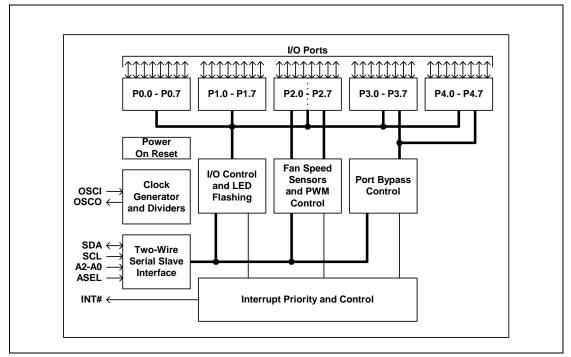

The SSC050-01 is a I/O-intensive peripheral device which is intended to be a portion of a cost effective FC-AL, SCSI, SAS or SATA enclosure management solution. The device contains an address programmable two wire serial interface, a block of control and status registers, I/O port control logic, specialized port bypass control logic and a clock generation block. Along with an external crystal, the device can be configured to support up to 40 bits of general purpose I/O or 16 bits of general purpose I/O, 16 bits of port bypass control (8 pairs supporting 8 drives), 4 fan speed monitoring inputs and 4 pulse width modulated outputs.

The SSC050-01 is capable of supporting various combinations of individual PBC/CRU/SDU functions as well as integrated solutions. The control register portion of the device allows the user to individually program each I/O pin as an input, output or open source/drain output. Additional control features include selectable flash rates for direct LED drive, input edge detection for interrupt generation, fan speed monitoring and pulse width modulated outputs. The addressing capability of the SSC050-01 includes three pins, which are used for device addressing, as well as one pin, which can be used to select two device type identifiers. Sixteen devices can be used in a single two-wire serial interface system.

Figure 1-1. Chip Block Diagram

## FEATURE SUMMARY

- Up to 40 bits of user-definable, bidirectional general purpose I/O

- Integrated Port Bypass, Clock Recovery and Signal Detect support for up to 8 drives

- Four programmable fan speed monitoring inputs

- 5 volt tolerant Interrupt output eliminates polling requirements

- Selectable direct LED drive flashing capability

- Pin-programmable addressing for up to 16 devices on a single serial bus

- 5 volt tolerant slave mode two wire serial interface

- 20% of package pins are power and ground

- Four programmable pulse width modulation outputs

- Enhanced fan speed monitor input filters

# **TYPICAL APPLICATIONS**

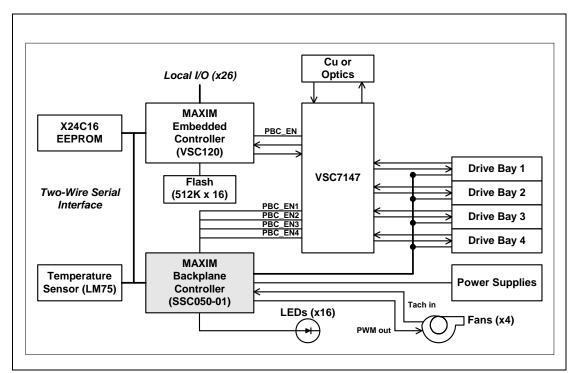

#### **FC-AL Drive Enclosure Configuration**

- Basic port bypass configuration

- Support for up to 128 drives

- Backplane controller supports up to two sets of CRU/SDU functions and 8 drives

- Sixteen Backplane controllers can be simultaneously attached to the serial bus

- Four drive implementation shown four channel PBC with two CRU/SDU functions

- General purpose I/O lines used for drive control/status and system control/status

Figure 1-2. Single Loop, Single Controller with Four Drives

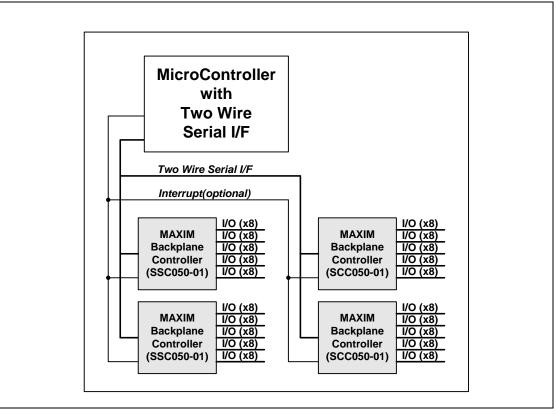

#### **General Purpose I/O Configuration**

- Controlled by general purpose Microcontroller with two wire serial interface

- Support for up to 640 I/O lines

- Backplane controller supports up to 40 I/O lines

- Sixteen backplane controllers can be simultaneously attached to the serial bus

Four backplane controller implementation shown with shared open drain interrupt

Figure 1-3. Four Backplane Controllers, 160 Bidirectional I/O Lines

# **Chapter 2 FUNCTIONAL DESCRIPTION**

The SSC050-01 is composed of five major functional blocks; a slave mode two-wire serial interface, a block of control registers, general purpose I/O and specialized port bypass control logic, a clock generator and power-on reset control logic. The SSC050-01 fully supports a generic two-wire serial interface and is compatible with other industry standard devices which also support this interface at both 100K and 400K bits per second.

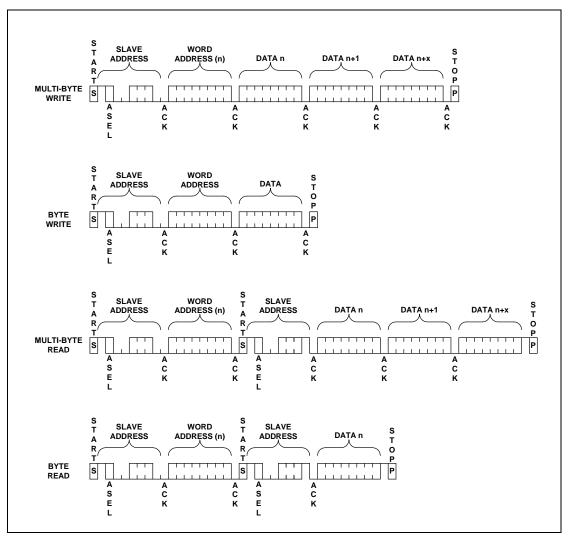

#### **TWO-WIRE SERIAL INTERFACE**

The device supports a single slave mode two-wire serial interface. All inter-chip communication to a microcontroller takes place over this bus. The interface supports a three-bit address bus, which allows the user to select one of eight possible addresses. The address bus is compared to bits three through one of the slave address byte, which is the first byte transmitted to the device after a start condition. The SSC050-01 supports two pin selectable four-bit device type identifier values, 1000b and 1100b. The address bits and the device identifier allow the use of up to 16 devices on a single two-wire serial interface. The serial interface control logic includes the slave state machine, address comparison logic, serial to parallel and parallel to serial conversion, register read/write control and filtering for the clock and data line.

A read or write transaction is determined by the least significant bit (R/W) of the first byte transferred. Write accesses require a three-byte transfer. The first byte is the slave address with the R/W bit low, the second byte contains the register address and the third byte is the write data. Read accesses require a four-byte transfer since data transfer direction can not change after receipt of the slave address byte. The first byte is the slave address with the R/W bit low, the second byte contains the register address with the R/W bit low, the second byte contains the register address, the third byte is a repeated slave address with the R/W bit high and the fourth byte is the read data. If the transaction is a write, the data will be latched into the appropriate register during the acknowledge of the third byte allowing the user to immediately initiate another transfer to the device. Sequential read or write transactions are allowed and are extensions of the above protocol with additional data bytes added to the end of the transaction. All sequential transactions will cause the internal address to increment by one regardless of the register address.

# **CONTROL REGISTERS**

The SSC050-01 contains five groups of control registers. Each group supports a specific function within the device as follows; the first group is the port data registers, the second is the data direction registers, the third contains special bit control features, the fourth supports the port bypass control function and the fifth supports fan speed monitoring. Currently the device contains 78 registers to support all required functions. In normal I/O operation, each eight-bit group of I/O pins are controlled by a pair of registers, Port Data and Data Direction. The use of these pairs of registers allows each I/O line to be individually configured as an input with internal pull-up, output or open drain output with internal pull-up.

The bit control features are enabled through a separate register for each I/O pin. The Bit Control registers allow the user to independently configure each I/O pin to enable one of the special control features as well as control Port Data and Data Direction (which are shadowed copies of the standard control bits found in the Port Data and Data Direction registers). Each I/O pin which has been configured as an input can also be configured to assert the open drain interrupt pin when a rising edge, a falling edge or either edge is detected on the I/O pin. An Interrupt Status register provides the user with a binary indication of which I/O pin is the source of the current interrupt. Each I/O pin which is configured as an output can automatically generate one of seven selectable flashing rates, which are normally driven in an open drain mode. By providing all I/O control capability in a single register, the user can control the operation of the I/O on a pin-by-pin basis.

The Port Bypass registers control the operation of a selected group of I/O lines which can be dedicated to support various combinations of individual PBC/CRU/SDU functions as well as integrated solutions. Enabling port bypass control causes the normal or bit control register settings to be overridden and any further changes to the affected registers will have no effect. Each Port Bypass Control register will automatically configure the I/O lines to support a Force Bypass output and a Signal Detected input.

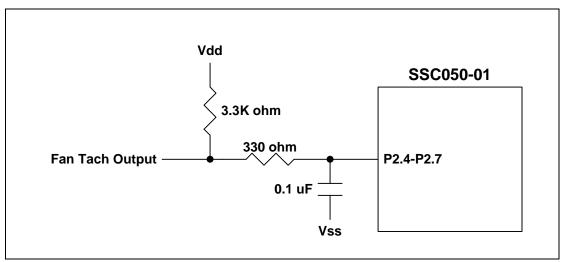

The Fan Speed registers control the operation of four programmable inputs which can be used to monitor signals from fans equipped with tachometer outputs. Enabling fan speed control causes the normal or bit control register settings to be overridden and any further changes to the affected registers will have no effect. Each group of three registers provides the capability to enable the function, establish a user defined RPM overflow value which indicates a failure and determine the current RPM value of the fan. The digital filters on the fan speed inputs can optionally be enabled to increase the normal 100 to 200 nanosecond filter to 400 to 500 nanoseconds.

The Pulse Width Modulation Control registers enable internal logic to provide duty cycles of 0% to 100% in 3% increments at default frequencies of 26KHz, 52KHz and 104KHz. Optionally, the PWM outputs can be programmed for three additional frequency ranges of 5.2KHz, 10.4KHz and 20.8KHz or 1.04KHz, 2.08KHz and 4.16KHz or 208Hz, 416Hz and 833Hz. These outputs can vary the speed of up to four fans through the use of external drivers and power MOSFETs or pulse width to voltage converters. They can also be used to support other pulse width modulated requirements within the system.

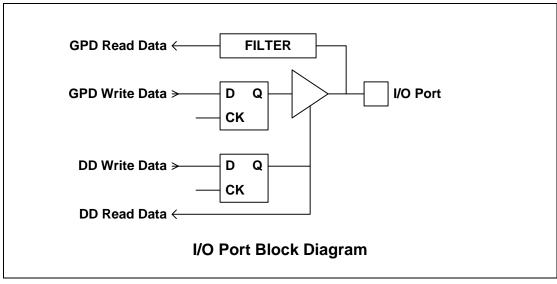

# I/O Logic

Each general purpose I/O pin is controlled by a set of registers in the Control Register Block. The I/O supports a high current drive output buffer, which can be configured as a totem pole or open drain driver. The input section of the I/O supports TTL signaling and includes an internal weak pull-up device. This allows unused I/O pins to be left unconnected without high current drain issues. The port bypass control I/O pins which are shared with Port 3 and Port 4 are generated using the same buffer logic as the other ports. When enabled in port bypass control mode, internal logic overrides the existing configuration, with each I/O pin dedicated to the specific port bypass function. All I/O lines default as inputs with the weak internal pull-up enabled.

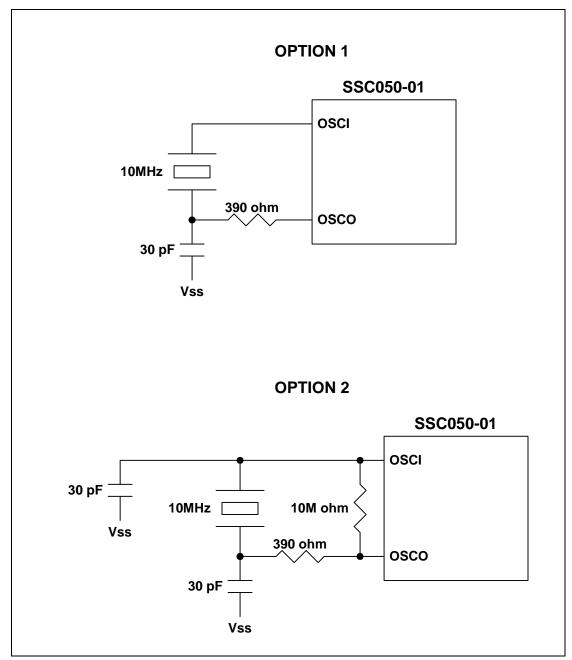

# **CLOCK GENERATOR**

Clock generation for the device is composed of an internal oscillator, divider circuits and a distribution network. The primary clock frequency of 10.0MHz is used for filtering incoming serial interface signals and interrupt sources as well as clocking the slave state machine. Divided clocks provide the source for LED flash rate generators. Logic within the SSC050-01 synchronizes the divided clocks between devices attached to the same two-wire serial bus with no more than 200 nanoseconds of skew. Multiple devices can then be used to drive different LED's at the same frequency, providing a synchronized visible indication. The oscillator provides a stable clock source for the device and requires the use of an off chip crystal and related passive components or external clock source. There are no programmable options related to clock generation except the selection of the seven fixed LED Flashing rates. The SSC050-01 can operate at frequencies other than 10.0MHz and continue to meet both the standard mode (100KHz) and fast mode (400KHz) serial interface timings. Frequencies from 8.0MHz to 12.5MHz are allowable as long as they meet the AC timing requirements listed in section 5.3.1 of this manual. Operation of the LED flashing circuits, fan speed counters and pulse width modulated outputs will be affected by a change in base operating frequency. The user must scale the expected operating parameters by the change in frequency from a nominal 10.0MHz. As and example, operating the SSC050-01 at 8.0MHz will cause the LED flashing circuits, fan speed counters and pulse width modulated outputs to operate 25% slower than normal.

## **POWER-ON RESET**

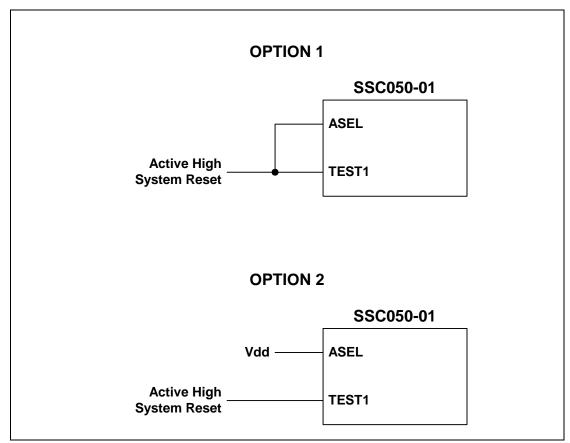

Power-On Reset is accomplished by the use of logic internal to the device. No external components are required. After power-on, the serial interface state machine will always return an idle state waiting for a start condition to appear on the SCL and SDA pins. A proper power-on reset sequence will clear the serial interface state machine, the clock generators, the control registers, the I/O control logic and the port bypass control logic. The divided clocks used for LED flash rate generation will also be in a known state. An external reset circuit utilizing the TEST1 and ASEL pins can be developed as an option to the internal Power-On Reset logic. Regardless of the effectiveness of either power-on reset sequence, it is highly recommended that the control registers and I/O control logic be cleared through the Soft Reset Register bit. This can be accomplished by writing a 80h to the BCT Register (FCh) followed immediately by a STOP condition. This bit is self resetting and will not require further attention.

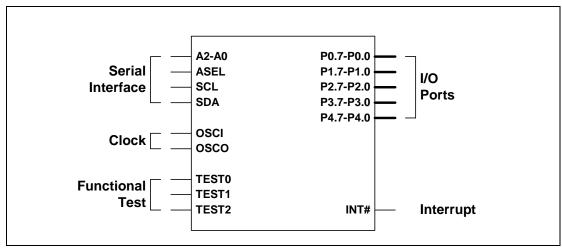

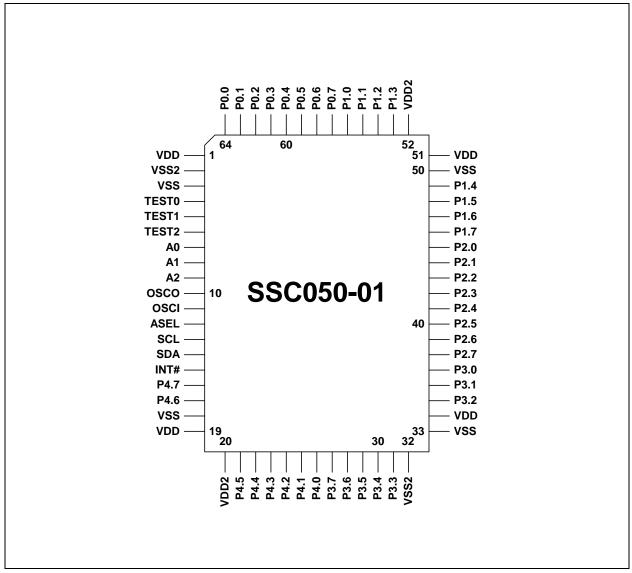

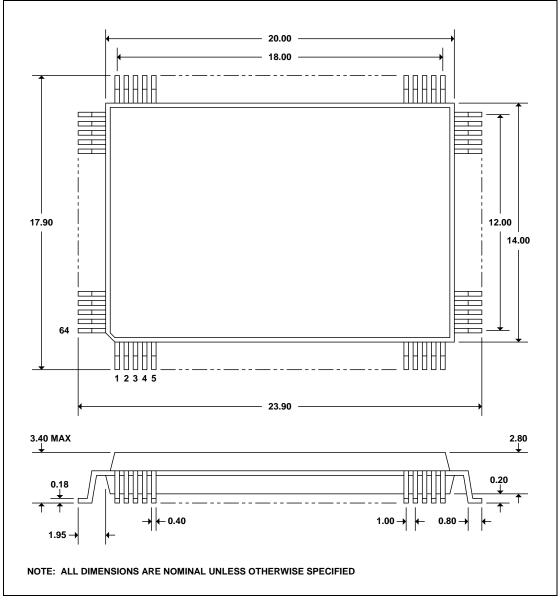

# Chapter 3 Pin Description

The SSC050-01 is packaged in a 64-pin PQFP. All pins have been placed to optimize their connection to external components. Power and ground distribution has also been optimized for core and high current I/ O connections. All serial interface pins as well as the interrupt output are 5 volt tolerant. VDD and VDD2 should be connected to a 3.3 volt supply with no more than 10% tolerances.

### **FUNCTIONAL SIGNAL GROUPING**

Figure 3-1. Functional Signal Grouping

### **PINOUT DIAGRAM**

Figure 3-2. Pinout Diagram

# **PIN DESCRIPTION LIST**

The following pin descriptions are grouped by function.

#### Table 3-1: Serial Interface

| Pin Names | Pin No. | Туре          | Pin Description                                                                                                                                                                                                                                               |

|-----------|---------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A2-A0     | 9-7     | Inputs        | Address Select Bus<br>This pin group provides the value, which will be compared to bits<br>3 through 1 of the serial slave address. These pins should be<br>strapped to VDD or VSS to provide the appropriate binary value.                                   |

| ASEL      | 12      | Input         | Device Type Address Select<br>This pin provides the ability to select between two-device type<br>address values in the serial slave address. When tied to VSS,<br>the device type address is 1000b and when tied to VDD, the<br>device type address is 1100b. |

| SCL       | 13      | Input         | Two-wire Serial Interface Clock<br>This pin is used by the device to latch the data present on the<br>SDA pin. This pin in conjunction with the SDA pin also deter-<br>mines Start and Stop conditions on the serial bus.                                     |

| SDA       | 14      | Bidirectional | Two-wire Serial Interface Data<br>This pin is used to transfer all serial data into and out of the<br>device. This pin in conjunction with the SCL pin also determines<br>Start and Stop conditions on the serial bus.                                        |

#### Table 3-2: Clock

| Pin Names | Pin No. | Туре   | Pin Description                                                                                                                                                                                                                                                                                |

|-----------|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSCI      | 11      | Input  | Oscillator Input<br>This pin is connected to one side of an external 10.0MHz crystal<br>to produce the clock required for serial signal filtering, state<br>machine clocking and flash rate generation. An alternate exter-<br>nal 3.3 volt 10.0MHz clock source can be connected to this pin. |

| OSCO      | 10      | Output | Oscillator Output<br>This pin is connected to the other side of an external 10.0MHz<br>crystal. When an alternate external clock source is used, this pin<br>should be left unconnected.                                                                                                       |

#### Table 3-3: Interrupt

| Pin Names | Pin No. | Туре                 | Pin Description                                                                                                                                                                                                                                                                                                         |

|-----------|---------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT#      | 15      | Open-Drain<br>Output | Interrupt<br>This open-drain output can be used to signal the microcontroller<br>that an event has occurred on an I/O pin which is configured as<br>an input or that a special function event has occurred. This pin<br>can be wire ORed with other open drain outputs to provide a sin-<br>gle interrupt input source. |

#### Table 3-4: I/O Ports

| Pin Names                                          | Pin No.          | Туре          | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------|------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P0.7-P0.0                                          | 57-64            | Bidirectional | I/O Port 0<br>Port 0 is a dedicated eight-bit bidirectional I/O port. The user<br>can select between an input, totem pole output or open-drain<br>output. Additional capability to detect input edge changes and<br>select various output flashing rates is also available.                                                                                                                                                                                                                                                                                                                                                                           |

| P1.7-P1.0                                          | 46-49,<br>53-56  | Bidirectional | I/O Port 1<br>Port 1 is a dedicated eight-bit bidirectional I/O port. The user<br>can select between an input, totem pole output or open-drain<br>output. Additional capability to detect input edge changes and<br>select various output flashing rates is also available.                                                                                                                                                                                                                                                                                                                                                                           |

| P2.7-P2.0<br>(Tach Inputs<br>and PWM out-<br>puts) | 38-45            | Bidirectional | I/O Port 2<br>Port 2 is an eight-bit bidirectional I/O port. The user can select<br>between an input, totem pole output or open-drain output. Addi-<br>tional capability to detect input edge changes and select various<br>output flashing rates is also available. Through control register<br>setup, P2.7-P2.4 can be dedicated to monitoring fans equipped<br>with tachometer outputs. Through control register setup, P2.3-<br>P2.0 can be dedicated to controlling fan speed utilizing pulse<br>width modulated outputs.                                                                                                                        |

| P3.7-P3.0<br>(Bypass I/O)                          | 27-31,<br>35-37  | Bidirectional | I/O Port 3<br>Port 3 is a shared eight bit bidirectional I/O port which can be<br>used as a general purpose I/O port or as Port Bypass control.<br>The user can select between an input, totem pole output or<br>open-drain output. Additional capability to detect input edge<br>changes and select various output flashing rates is also availa-<br>ble. Through control register setup, four two-bit portions of this<br>port can be dedicated to the control of a combination of PBC/<br>CRU/SDU functions. Any combination of port bypass control<br>functions can be enabled with the remaining I/O pins used for<br>general purpose functions. |

| P4.7-P4.0<br>(Bypass I/O)                          | 16, 17,<br>21-26 | Bidirectional | I/O Port 4<br>Port 4 is a shared eight bit bidirectional I/O port which can be<br>used as a general purpose I/O port or as Port Bypass control.<br>The user can select between an input, totem pole output or<br>open-drain output. Additional capability to detect input edge<br>changes and select various output flashing rates is also availa-<br>ble. Through control register setup, four two-bit portions of this<br>port can be dedicated to the control of a combination of PBC/<br>CRU/SDU functions. Any combination of port bypass control<br>functions can be enabled with the remaining I/O pins used for<br>general purpose functions. |

#### Table 3-5: Test

| Pin Names       | Pin No. | Туре  | Pin Description                                                                                                                                                                      |

|-----------------|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST2-<br>TEST0 | 6-4     | Input | Functional Test<br>These inputs allow the device to be placed in specific test<br>modes for device level testing. These inputs should be con-<br>nected to VSS for normal operation. |

#### Table 3-6: Supply

| Pin Names | Pin No.          | Туре   | Pin Description                                                                                                                                          |

|-----------|------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD       | 1, 19, 34,<br>51 | Power  | I/O Power<br>These pins are the power sources for the I/O drivers of all non-<br>analog output and bidirectional pins.                                   |

| VSS       | 3, 18, 33,<br>50 | Ground | I/O Ground<br>These pins are the ground connections for the I/O drivers of all<br>non-analog output and bidirectional pins.                              |

| VDD2      | 20, 52           | Power  | Digital Core Power<br>These pins are the power sources for the digital core logic and<br>receivers of all non-analog input and bidirectional pins.       |

| VSS2      | 2, 32            | Ground | Digital Core Ground<br>These pins are the ground connections for the digital core logic<br>and receivers of all non-analog input and bidirectional pins. |

# Chapter 4 CONTROL REGISTERS

This section contains descriptions for the device-specific control registers. All register locations are fixed within the device and are mapped for easy access as well as future enhancements.

The control register section is separated into three sub-sections; a register map, an address map and the bit level description of all registers. The register map lists all registers by operating address. The address map shows the relative layout of all control registers. All registers can be accessed at any time and no register function will interfere with the operation of the serial interface. However, changing register bits will have an immediate effect on the respective I/O lines.

### **REGISTER MAP**

| Data Memory<br>Address | Read/Write | Label | Description                              |

|------------------------|------------|-------|------------------------------------------|

| 00h                    | R/W        | GPD0  | General Purpose I/O Port 0 Data Register |

| 01h                    | R/W        | GPD1  | General Purpose I/O Port 1 Data Register |

| 02h                    | R/W        | GPD2  | General Purpose I/O Port 2 Data Register |

| 03h                    | R/W        | GPD3  | General Purpose I/O Port 3 Data Register |

| 04h                    | R/W        | GPD4  | General Purpose I/O Port 4 Data Register |

| 10h                    | R/W        | DDP0  | I/O Port 0 Data Direction Register       |

| 11h                    | R/W        | DDP1  | I/O Port 1 Data Direction Register       |

| 12h                    | R/W        | DDP2  | I/O Port 2 Data Direction Register       |

| 13h                    | R/W        | DDP3  | I/O Port 3 Data Direction Register       |

| 14h                    | R/W        | DDP4  | I/O Port 4 Data Direction Register       |

| 20h                    | R/W        | PBC0  | Port Bypass Control 0 Register           |

| 21h                    | R/W        | PBC1  | Port Bypass Control 1 Register           |

| 22h                    | R/W        | PBC2  | Port Bypass Control 2 Register           |

| 23h                    | R/W        | PBC3  | Port Bypass Control 3 Register           |

#### Table 4-1: Register Map

| Table 4-1: | Register Map | (continued) |

|------------|--------------|-------------|

|------------|--------------|-------------|

| Data Memory<br>Address | Read/Write | Label | Description                         |

|------------------------|------------|-------|-------------------------------------|

| 24h                    | R/W        | PBC4  | Port Bypass Control 4 Register      |

| 25h                    | R/W        | PBC5  | Port Bypass Control 5 Register      |

| 26h                    | R/W        | PBC6  | Port Bypass Control 6 Register      |

| 27h                    | R/W        | PBC7  | Port Bypass Control 7 Register      |

| 30h                    | R/W        | FSC0  | Fan Speed Control 0 Register        |

| 31h                    | R/W        | FSCO0 | Fan Speed Count Overflow 0 Register |

| 32h                    | R          | FSCC0 | Fan Speed Current Count 0 Register  |

| 34h                    | R/W        | FSC1  | Fan Speed Control 1 Register        |

| 35h                    | R/W        | FSCO1 | Fan Speed Count Overflow 1 Register |

| 36h                    | R          | FSCC1 | Fan Speed Current Count 1 Register  |

| 38h                    | R/W        | FSC2  | Fan Speed Control 2 Register        |

| 39h                    | R/W        | FSCO2 | Fan Speed Count Overflow 2 Register |

| 3Ah                    | R          | FSCC2 | Fan Speed Current Count 2 Register  |

| 3Ch                    | R/W        | FSC3  | Fan Speed Control 3 Register        |

| 3Dh                    | R/W        | FSCO3 | Fan Speed Count Overflow 3 Register |

| 3Eh                    | R          | FSCC3 | Fan Speed Current Count 3 Register  |

| 80h                    | R/W        | BCP00 | Bit Control Port 0 - Bit 0 Register |

| 81h                    | R/W        | BCP01 | Bit Control Port 0 - Bit 1 Register |

| 82h                    | R/W        | BCP02 | Bit Control Port 0 - Bit 2 Register |

| 83h                    | R/W        | BCP03 | Bit Control Port 0 - Bit 3 Register |

| 84h                    | R/W        | BCP04 | Bit Control Port 0 - Bit 4 Register |

| 85h                    | R/W        | BCP05 | Bit Control Port 0 - Bit 5 Register |

| 86h                    | R/W        | BCP06 | Bit Control Port 0 - Bit 6 Register |

| 87h                    | R/W        | BCP07 | Bit Control Port 0 - Bit 7 Register |

| 90h                    | R/W        | BCP10 | Bit Control Port 1 - Bit 0 Register |

| 91h                    | R/W        | BCP11 | Bit Control Port 1 - Bit 1 Register |

| 92h                    | R/W        | BCP12 | Bit Control Port 1 - Bit 2 Register |

| 93h                    | R/W        | BCP13 | Bit Control Port 1 - Bit 3 Register |

| 94h                    | R/W        | BCP14 | Bit Control Port 1 - Bit 4 Register |

| 95h                    | R/W        | BCP15 | Bit Control Port 1 - Bit 5 Register |

| 96h                    | R/W        | BCP16 | Bit Control Port 1 - Bit 6 Register |

| 97h                    | R/W        | BCP17 | Bit Control Port 1 - Bit 7 Register |

| Table 4-1: | Register Map | (continued) |

|------------|--------------|-------------|

|------------|--------------|-------------|

| Data Memory<br>Address | Read/Write | Label | Description                                    |

|------------------------|------------|-------|------------------------------------------------|

| 98h                    | R/W        | PWMC0 | Pulse Width Modulation Control 0 Register      |

| 99h                    | R/W        | PWMC1 | Pulse Width Modulation Control 1 Register      |

| 9Ah                    | R/W        | PWMC2 | Pulse Width Modulation Control 2 Register      |

| 9Bh                    | R/W        | PWMC3 | Pulse Width Modulation Control 3 Register      |

| A0h                    | R/W        | BCP20 | Bit Control Port 2 - Bit 0 Register            |

| A1h                    | R/W        | BCP21 | Bit Control Port 2 - Bit 1 Register            |

| A2h                    | R/W        | BCP22 | Bit Control Port 2 - Bit 2 Register            |

| A3h                    | R/W        | BCP23 | Bit Control Port 2 - Bit 3 Register            |

| A4h                    | R/W        | BCP24 | Bit Control Port 2 - Bit 4 Register            |

| A5h                    | R/W        | BCP25 | Bit Control Port 2 - Bit 5 Register            |

| A6h                    | R/W        | BCP26 | Bit Control Port 2 - Bit 6 Register            |

| A7h                    | R/W        | BCP27 | Bit Control Port 2 - Bit 7 Register            |

| B0h                    | R/W        | BCP30 | Bit Control Port 3 - Bit 0 Register            |

| B1h                    | R/W        | BCP31 | Bit Control Port 3 - Bit 1 Register            |

| B2h                    | R/W        | BCP32 | Bit Control Port 3 - Bit 2 Register            |

| B3h                    | R/W        | BCP33 | Bit Control Port 3 - Bit 3 Register            |

| B4h                    | R/W        | BCP34 | Bit Control Port 3 - Bit 4 Register            |

| B5h                    | R/W        | BCP35 | Bit Control Port 3 - Bit 5 Register            |

| B6h                    | R/W        | BCP36 | Bit Control Port 3 - Bit 6 Register            |

| B7h                    | R/W        | BCP37 | Bit Control Port 3 - Bit 7 Register            |

| C0h                    | R/W        | BCP40 | Bit Control Port 4 - Bit 0 Register            |

| C1h                    | R/W        | BCP41 | Bit Control Port 4 - Bit 1 Register            |

| C2h                    | R/W        | BCP42 | Bit Control Port 4 - Bit 2 Register            |

| C3h                    | R/W        | BCP43 | Bit Control Port 4 - Bit 3 Register            |

| C4h                    | R/W        | BCP44 | Bit Control Port 4 - Bit 4 Register            |

| C5h                    | R/W        | BCP45 | Bit Control Port 4 - Bit 5 Register            |

| C6h                    | R/W        | BCP46 | Bit Control Port 4 - Bit 6 Register            |

| C7h                    | R/W        | BCP47 | Bit Control Port 4 - Bit 7 Register            |

| F8h                    | R/W        | BCIS  | Backplane Controller Interrupt Status Register |

| FCh                    | R/W        | BCT   | Backplane Controller Test Register             |

| FDh                    | R/W        | BCO   | Backplane Controller Option Register           |

| FFh                    | R          | VER   | Backplane Controller Version Register          |

# ADDRESS MAP

| 11b      | 10b      | 01b           | 00b      | Address |

|----------|----------|---------------|----------|---------|

| GPD3     | GPD2     | GPD1 GPD0     |          | 00h     |

| reserved | reserved | reserved GPD4 |          | 04h     |

| reserved | reserved | reserved      | reserved | 08h     |

| reserved | reserved | reserved      | reserved | 0Ch     |

| DDP3     | DDP2     | DDP1          | DDP0     | 10h     |

| reserved | reserved | reserved      | DDP4     | 14h     |

| reserved | reserved | reserved      | reserved | 18h     |

| reserved | reserved | reserved      | reserved | 1Ch     |

| PBC3     | PBC2     | PBC1          | PBC0     | 20h     |

| PBC7     | PBC6     | PBC5          | PBC4     | 24h     |

| reserved | reserved | reserved      | reserved | 28h     |

| reserved | reserved | reserved      | reserved | 2Ch     |

| reserved | FSCC0    | FSCO0         | FSC0     | 30h     |

| reserved | FSCC1    | FSCO1         | FSC1     | 34h     |

| reserved | FSCC2    | FSCO2         | FSC2     | 38h     |

| reserved | FSCC3    | FSCO3         | FSC3     | 3Ch     |

| reserved | reserved | reserved      | reserved | 40h-7Ch |

| BCP03    | BCP02    | BCP01         | BCP00    | 80h     |

| BCP07    | BCP06    | BCP05         | BCP04    | 84h     |

| reserved | reserved | reserved      | reserved | 88h     |

| reserved | reserved | reserved      | reserved | 8Ch     |

| BCP13    | BCP12    | BCP11         | BCP10    | 90h     |

| BCP17    | BCP16    | BCP15         | BCP14    | 94h     |

| PWMC3    | PWMC2    | PWMC1         | PWMC0    | 98h     |

| reserved | reserved | reserved      | reserved | 9Ch     |

| BCP23    | BCP22    | BCP21         | BCP20    | A0h     |

| BCP27    | BCP26    | BCP25         | BCP24    | A4h     |

| reserved | reserved | reserved      | reserved | A8h     |

| reserved | reserved | reserved      | reserved | ACh     |

| BCP33    | BCP32    | BCP31         | BCP30    | B0h     |

Table 4-2: Address Map

| 11b      | 10b      | 01b      | 00b      | Address |

|----------|----------|----------|----------|---------|

| BCP37    | BCP36    | BCP35    | BCP34    | B4h     |

| reserved | reserved | reserved | reserved | B8h     |

| reserved | reserved | reserved | reserved | BCh     |

| BCP43    | BCP42    | BCP41    | BCP40    | C0h     |

| BCP47    | BCP46    | BCP45    | BCP44    | C4h     |

| reserved | reserved | reserved | reserved | C8h-F4h |

| reserved | reserved | reserved | BCIS     | F8h     |

| VER      | reserved | BCO      | BCT      | FCh     |

# **CONTROL REGISTER DEFINITION**

The register definition provides a bit-level description of all register bits including power-on and default values. The terms "set" and "assert" refer to bits which are programmed to a binary one. The terms "reset", "de-assert" and "clear" refer to bits which are programmed to a binary zero. Reserved bits are represented by "RES" and will always return an unknown value and should be masked. Any bits which are reserved should never be set to a binary one. These bits may be defined in future versions of the device.

#### 00h: General Purpose I/O Port 0 Data (GPD0)

| Register Name: | GPD0                            |

|----------------|---------------------------------|

| Address:       | 00h                             |

| Reset Value:   | XXXX_XXXb                       |

| Description    | General Purpose I/O Port 0 Data |

| 7 | 6                    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---|----------------------|---|---|---|---|---|---|--|

|   | General Purpose Data |   |   |   |   |   |   |  |

| Bit(s) | Bit Label | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0    | GPD0.7-0  | R/W    | When the I/O pin has been enabled as an output, writing these bits determines the data value which will be present on the corresponding I/O pin. If the I/O pin has been enabled as an input, reading these register bits will represent the current voltage applied to the pin. At no time will the bits directly represent the value latched into the data register. If a pin is enabled as an input and there is no signal applied, weak internal pull-up resistors will hold the pin at a binary one. After a reset or power-on, the register bits will be set to a binary one, but the value returned from a register read will be the level applied to the pin since by default each pin is an input. |

Figure 4-1. I/O Port Block Diagram

#### 01h: General Purpose I/O Port 1 Data (GPD1)

| Register Name        | : | GPD1            | ₽D1                             |  |  |  |  |  |

|----------------------|---|-----------------|---------------------------------|--|--|--|--|--|

| Address:             |   | 01h             | h                               |  |  |  |  |  |

| Reset Value:         |   | XXXX_XXXb       |                                 |  |  |  |  |  |

| Description          |   | General Purpose | General Purpose I/O Port 1 Data |  |  |  |  |  |

|                      |   |                 |                                 |  |  |  |  |  |

| 7                    | 6 | 5               | 5 4 3 2 1 0                     |  |  |  |  |  |

| General Purpose Data |   |                 |                                 |  |  |  |  |  |

| Bit(s) | Bit Label | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0    | GPD0.7-0  | R/W    | When the I/O pin has been enabled as an output, writing these bits determines the data value which will be present on the corresponding I/O pin. If the I/O pin has been enabled as an input, reading these register bits will represent the current voltage applied to the pin. At no time will the bits directly represent the value latched into the data register. If a pin is enabled as an input and there is no signal applied, weak internal pull-up resistors will hold the pin at a binary one. After a reset or power-on, the register bits will be set to a binary one, but the value returned from a register read will be the level applied to the pin since by default each pin is an input. |

#### 02h: General Purpose I/O Port 2 Data (GPD2)

| Register Name: | GPD2                            |

|----------------|---------------------------------|

| Address:       | 02h                             |

| Reset Value:   | XXXX_XXXb                       |

| Description    | General Purpose I/O Port 2 Data |

|                |                                 |

| 7 | 6                    | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---|----------------------|---|---|---|---|---|---|--|

|   | General Purpose Data |   |   |   |   |   |   |  |

| Bit(s) | Bit Label | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0    | GPD0.7-0  | R/W    | When the I/O pin has been enabled as an output, writing these bits determines the data value which will be present on the corresponding I/O pin. If the I/O pin has been enabled as an input, reading these register bits will represent the current voltage applied to the pin. At no time will the bits directly represent the value latched into the data register. If a pin is enabled as an input and there is no signal applied, weak internal pull-up resistors will hold the pin at a binary one. After a reset or power-on, the register bits will be set to a binary one, but the value returned from a register read will be the level applied to the pin since by default each pin is an input. |

#### 03h: General Purpose I/O Port 3 Data (GPD3)

| Register Name          | : | GPD3                            |  |  |  |   |  |  |

|------------------------|---|---------------------------------|--|--|--|---|--|--|

| Address: 03h           |   |                                 |  |  |  |   |  |  |

| Reset Value: XXXX_XXXb |   |                                 |  |  |  |   |  |  |

| Description            |   | General Purpose I/O Port 3 Data |  |  |  |   |  |  |

|                        | i |                                 |  |  |  |   |  |  |

| 7 6 5 4 3 2 1 0        |   |                                 |  |  |  | 0 |  |  |

| General Purpose Data   |   |                                 |  |  |  |   |  |  |

| Bit(s) | Bit Label | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0    | GPD0.7-0  | R/W    | When the I/O pin has been enabled as an output, writing these bits determines the data value which will be present on the corresponding I/O pin. If the I/O pin has been enabled as an input, reading these register bits will represent the current voltage applied to the pin. At no time will the bits directly represent the value latched into the data register. If a pin is enabled as an input and there is no signal applied, weak internal pull-up resistors will hold the pin at a binary one. After a reset or power-on, the register bits will be set to a binary one, but the value returned from a register read will be the level applied to the pin since by default each pin is an input. |

#### 04h: General Purpose I/O Port 4 Data (GPD4)

| Register Name: | GPD4                            |

|----------------|---------------------------------|

| Address:       | 04h                             |

| Reset Value:   | XXXX_XXXb                       |

| Description    | General Purpose I/O Port 4 Data |

|                |                                 |

| 7                    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|----------------------|---|---|---|---|---|---|---|--|

| General Purpose Data |   |   |   |   |   |   |   |  |

| Bit(s) | Bit Label | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0    | GPD0.7-0  | R/W    | When the I/O pin has been enabled as an output, writing these bits determines the data value which will be present on the corresponding I/O pin. If the I/O pin has been enabled as an input, reading these register bits will represent the current voltage applied to the pin. At no time will the bits directly represent the value latched into the data register. If a pin is enabled as an input and there is no signal applied, weak internal pull-up resistors will hold the pin at a binary one. After a reset or power-on, the register bits will be set to a binary one, but the value returned from a register read will be the level applied to the pin since by default each pin is an input. |

## 10h: I/O Port 0 Data Direction (DDP0)

| Register Name          | : | DDP0                      |  |  |  |  |   |  |

|------------------------|---|---------------------------|--|--|--|--|---|--|

| Address: 10h           |   |                           |  |  |  |  |   |  |

| Reset Value: 1111_111b |   |                           |  |  |  |  |   |  |

| Description            |   | I/O Port 0 Data Direction |  |  |  |  |   |  |

|                        |   |                           |  |  |  |  |   |  |

| 7 6 5 4 3 2 1 0        |   |                           |  |  |  |  | 0 |  |

| Data Direction         |   |                           |  |  |  |  |   |  |

| Bit(s) | Bit Label | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0    | DDP0.7-0  | R/W    | Data Direction                                                                                                                                                                                                                                                                                                                                                                                                      |

|        |           |        | These bits determine the direction of the data flow through the I/O pin.                                                                                                                                                                                                                                                                                                                                            |

|        |           |        | To enable the respective I/O pin as an input, set the appropriate bit. To enable the respective I/O pin as an output, reset the appropriate bit. Each I/O pin can be individually configured as a true bidirectional function. Additionally, an open-drain or open-source function can be developed by resetting or setting the appropriate data bit and using the data direction bit as the programmed data value. |

|        |           |        | After a reset or power-on, these bits will be set to a binary one, enabling the I/O as an input with weak pull-up.                                                                                                                                                                                                                                                                                                  |

### 11h: I/O Port 1 Data Direction (DDP1)

| Register Name: | DDP1                      |

|----------------|---------------------------|

| Address:       | 11h                       |

| Reset Value:   | 1111_111b                 |

| Description    | I/O Port 1 Data Direction |

| 7 | 6              | 5 | 4 | 3 | 2 | 1 | 0 |  |

|---|----------------|---|---|---|---|---|---|--|

|   | Data Direction |   |   |   |   |   |   |  |

| Bit(s) | Bit Label | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0    | DDP0.7-0  | R/W    | Data Direction                                                                                                                                                                                                                                                                                                                                                                                                                  |

|        |           |        | These bits determine the direction of the data flow through the I/O pin.                                                                                                                                                                                                                                                                                                                                                        |

|        |           |        | To enable the respective I/O pin as an input, set the appropriate bit. To enable the respective I/O pin as an output, reset the appropriate bit. Each I/O pin can be individ-<br>ually configured as a true bidirectional function. Additionally, an open-drain or open-<br>source function can be developed by resetting or setting the appropriate data bit and<br>using the data direction bit as the programmed data value. |

|        |           |        | After a reset or power-on, these bits will be set to a binary one, enabling the I/O as an input with weak pull-up.                                                                                                                                                                                                                                                                                                              |

#### 12h: I/O Port 2 Data Direction (DDP2)

| Register Name          | : | DDP2                      |  |  |  |   |  |  |

|------------------------|---|---------------------------|--|--|--|---|--|--|

| Address: 12h           |   |                           |  |  |  |   |  |  |

| Reset Value: 1111_111b |   |                           |  |  |  |   |  |  |

| Description            |   | I/O Port 2 Data Direction |  |  |  |   |  |  |

|                        |   |                           |  |  |  |   |  |  |

| 7 6 5 4 3 2 1 0        |   |                           |  |  |  | 0 |  |  |

| Data Direction         |   |                           |  |  |  |   |  |  |

| Bit(s) | Bit Label | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0    | DDP0.7-0  | R/W    | Data Direction                                                                                                                                                                                                                                                                                                                                                                                                                  |

|        |           |        | These bits determine the direction of the data flow through the I/O pin.                                                                                                                                                                                                                                                                                                                                                        |

|        |           |        | To enable the respective I/O pin as an input, set the appropriate bit. To enable the respective I/O pin as an output, reset the appropriate bit. Each I/O pin can be individ-<br>ually configured as a true bidirectional function. Additionally, an open-drain or open-<br>source function can be developed by resetting or setting the appropriate data bit and<br>using the data direction bit as the programmed data value. |

|        |           |        | After a reset or power-on, these bits will be set to a binary one, enabling the I/O as an input with weak pull-up.                                                                                                                                                                                                                                                                                                              |

### 13h: I/O Port 3 Data Direction (DDP3)

| Register Name: | DDP3                      |

|----------------|---------------------------|

| Address:       | 13h                       |

| Reset Value:   | 1111_111b                 |

| Description    | I/O Port 3 Data Direction |

| 7              | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------|---|---|---|---|---|---|---|

| Data Direction |   |   |   |   |   |   |   |

| Bit(s) | Bit Label | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0    | DDP0.7-0  | R/W    | Data Direction                                                                                                                                                                                                                                                                                                                                                                                                                  |

|        |           |        | These bits determine the direction of the data flow through the I/O pin.                                                                                                                                                                                                                                                                                                                                                        |

|        |           |        | To enable the respective I/O pin as an input, set the appropriate bit. To enable the respective I/O pin as an output, reset the appropriate bit. Each I/O pin can be individ-<br>ually configured as a true bidirectional function. Additionally, an open-drain or open-<br>source function can be developed by resetting or setting the appropriate data bit and<br>using the data direction bit as the programmed data value. |

|        |           |        | After a reset or power-on, these bits will be set to a binary one, enabling the I/O as an input with weak pull-up.                                                                                                                                                                                                                                                                                                              |

### 14h: I/O Port 4 Data Direction (DDP4)

| Register Name | :              | DDP4                      |  |  |  |  |   |  |

|---------------|----------------|---------------------------|--|--|--|--|---|--|

| Address: 14h  |                |                           |  |  |  |  |   |  |

| Reset Value:  |                | 1111_1111b                |  |  |  |  |   |  |

| Description   |                | I/O Port 4 Data Direction |  |  |  |  |   |  |

|               |                |                           |  |  |  |  |   |  |

| 7             | 6              | 5 4 3 2 1 0               |  |  |  |  | 0 |  |

|               | Data Direction |                           |  |  |  |  |   |  |

| Bit(s) | Bit Label | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0    | DDP0.7-0  | R/W    | Data Direction                                                                                                                                                                                                                                                                                                                                                                                                      |

|        |           |        | These bits determine the direction of the data flow through the I/O pin.                                                                                                                                                                                                                                                                                                                                            |

|        |           |        | To enable the respective I/O pin as an input, set the appropriate bit. To enable the respective I/O pin as an output, reset the appropriate bit. Each I/O pin can be individually configured as a true bidirectional function. Additionally, an open-drain or open-source function can be developed by resetting or setting the appropriate data bit and using the data direction bit as the programmed data value. |

|        |           |        | After a reset or power-on, these bits will be set to a binary one, enabling the I/O as an input with weak pull-up.                                                                                                                                                                                                                                                                                                  |

### 20h: Port Bypass Control 0 (PBC0)

| Register Name: | PBC0                  |

|----------------|-----------------------|

| Address:       | 20h                   |

| Reset Value:   | 00XX_XX1Xb            |

| Description    | Port Bypass Control 0 |

|                |                       |

| 7                                  | 6                                           | 5 | 4 | 3 | 2 | 1               | 0                  |

|------------------------------------|---------------------------------------------|---|---|---|---|-----------------|--------------------|

| Port Bypass<br>Control Ena-<br>ble | Signal<br>Detected<br>Interrupt Ena-<br>ble |   |   |   |   | Force<br>Bypass | Signal<br>Detected |

| Bit(s) | Bit Label | Access | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|-----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|