## VSC056 Data Sheet

## **Enhanced Two-Wire Serial Backplane Controller**

## **F**EATURES

- Up to 64 bits of user-definable, bidirectional general-purpose inputs and outputs

- Integrated port bypass, clock recovery and signal detect support for up to 16 drives

- Eight programmable fan speed monitoring inputs

- Eight programmable pulse-width modulated fan control outputs

- Up to 32 programmable input-to-output bypass pairs

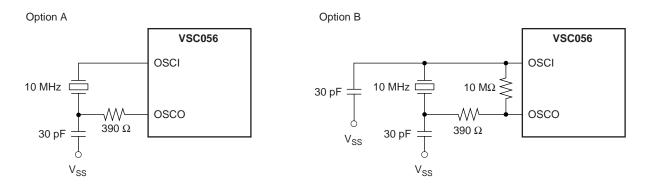

- Two clock input ranges: 8.0 MHz to 12.5 MHz (external crystal or external clock source) and 32.0 MHz to 75.0 MHz (external clock source)

- Selectable direct LED drive flashing capability

- Pin-programmable addressing for up to 16 devices on a single serial bus

- 5-V tolerant high current I/O, Slave mode two-wire serial interface and interrupt output

- Ten programmable LED pulse train circuits

- One 24-bit general-purpose timer (supports a timeout greater than four seconds with a 12.5 MHz core clock)

- Up to 16 subaddressed Master mode two-wire serial interface ports

- External reset of the slave two-wire serial core

- Enhanced fan speed monitor input filters

- 20% of package pins are power and ground for excellent noise immunity and long-term reliability

## **APPLICATIONS**

- Enterprise storage environments

- Storage Area Network (SAN) appliances

- Network Attached Storage (NAS) systems

- Fabric Attached Storage (FAS) systems

- Rack-mounted servers with RAID

- JBOD arrays

- Disk-based backup storage

- Near-line storage replacement systems

- Fixed-content storage systems

To order the VSC056 device, see "Ordering Information," page 134.

## **GENERAL DESCRIPTION**

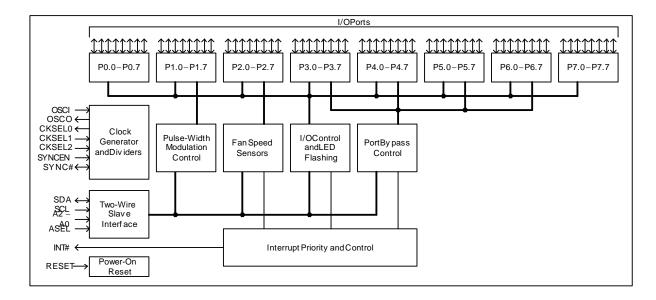

The VSC056 device is an I/O-intensive peripheral device that is intended to be part of a cost-effective Fibre Channel Arbitrated Loop (FC-AL), Small Computer System Interface (SCSI), Serial Attached SCSI (SAS), or Serial ATA (SATA) enclosure management solution. The device contains an address-programmable two-wire serial interface, a block of control and status registers, I/O port control logic, specialized port bypass control logic, and a clock-generation block.

Along with an external crystal, the device can be configured to support up to 64 bits of general-purpose I/O; or 16 bits of general-purpose I/O, 32 bits of port bypass control (16 pairs supporting 16 drives), eight fan speed monitoring inputs, and eight pulse-width modulated general-purpose control outputs.

The VSC056 supports various combinations of individual port bypass circuit (PBC), clock recovery unit (CRU), and signal detect unit (SDU) functions, as well as integrated solutions. The control register portion of the device allows the user to individually program each I/O pin as an input, an output, or an open-drain or open-source output.

Maxim Integrated Products

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com. 1 of 134

Additional control features include: selectable flash rates for direct LED drive, input edge detection for interrupt generation, input to output bypass capability, fan speed monitoring control, and pulse-width modulated output control. Support for sub-addressing additional two-wire serial slave devices using a set of seven control registers is included. This capability allows up to 16 independent Master mode two-wire serial slave ports to be created using 32 of the I/O pins.

The addressing capability of the VSC056 includes three pins, which are used for device addressing, as well as one pin that can be used to select two device type identifiers. Sixteen VSC056 devices can be used in a single two-wire serial interface system.

## **Block Diagram**

# **TYPICAL APPLICATIONS**

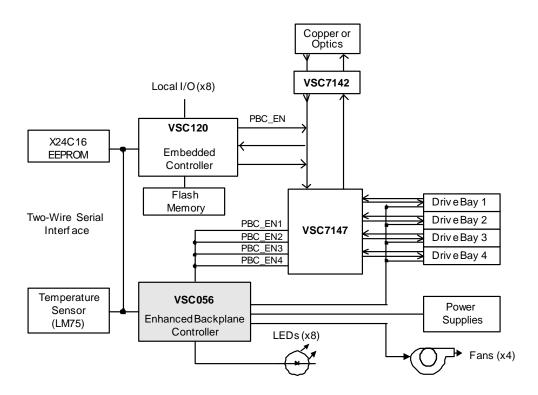

## **FC-AL Drive Enclosure Configuration**

- Basic port bypass configuration

- Support for up to 128 drives: Backplane Controller supports up to two sets of CRU/SDU functions and drives, and 16 Backplane Controllers can be attached simultaneously to the serial bus

- Four-drive implementation is shown below; four-channel PBC with two CRU/SDU functions and generalpurpose I/O lines for drive control and status, and other enclosure control functions.

#### Figure 1. Single Loop, Single Controller with Four Drives

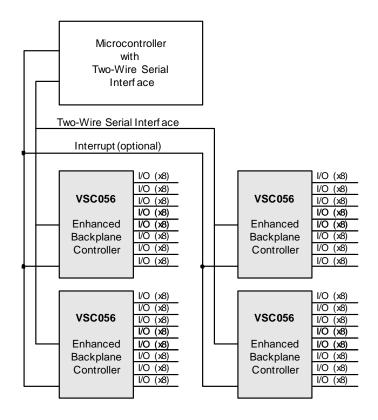

## **General-Purpose I/O Configuration**

- Controlled by general-purpose microcontroller with two-wire serial interface

- Support for up to 1024 I/O lines: Backplane controller supports up to 64 I/O lines and 16 backplane controllers can be simultaneously attached to the serial bus

- Four-backplane controller implementation is shown here with shared open-drain interrupt

Figure 2. Four Backplane Controllers, 256 Bidirectional I/O Lines

# Contents

| Ge  | neral   | Descrip  | otion                                       | . 1 |

|-----|---------|----------|---------------------------------------------|-----|

| Fea | atures  |          |                                             | . 1 |

| Ap  | olicati | ions     |                                             | . 1 |

|     |         |          | tions                                       |     |

|     |         |          |                                             |     |

| Rev | vision  | HIStor   | y                                           | . 9 |

| 1   | Intro   | oductio  | on                                          | 10  |

| 2   | Fun     | ctional  | I Descriptions                              | 11  |

|     | 2.1     | Two-Wi   | ire Serial Interface                        | .11 |

|     | 2.2     | Control  | I Registers                                 | .11 |

|     | 2.3     | I/O Log  | jic                                         | .13 |

|     | 2.4     | Clock C  | Generator                                   | .13 |

|     | 2.5     | Power-   | on Reset                                    | .14 |

| 3   | Reg     | jisters. |                                             | 15  |

|     | 3.1     | Control  | I Registers                                 | .15 |

|     | 3.2     | Control  | Register Definitions                        | .21 |

|     |         | 3.2.1    | 00h: General-Purpose I/O Port 0 Data (GPD0) | .21 |

|     |         | 3.2.2    | 01h: General-Purpose I/O Port 1 Data (GPD1) | .22 |

|     |         | 3.2.3    | 02h: General-Purpose I/O Port 2 Data (GPD2) | .22 |

|     |         | 3.2.4    | 03h: General-Purpose I/O Port 3 Data (GPD3) | .23 |

|     |         | 3.2.5    | 04h: General-Purpose I/O Port 4 Data (GPD4) | .23 |

|     |         | 3.2.6    | 05h: General-Purpose I/O Port 5 Data (GPD5) | .24 |

|     |         | 3.2.7    | 06h: General-Purpose I/O Port 6 Data (GPD6) | .24 |

|     |         | 3.2.8    | 07h: General-Purpose I/O Port 7 Data (GPD7) | .25 |

|     |         | 3.2.9    | 10h: I/O Port 0 Data Direction (DDP0)       | .25 |

|     |         | 3.2.10   | 11h: I/O Port 1 Data Direction (DDP1)       | .26 |

|     |         | 3.2.11   | 12h: I/O Port 2 Data Direction (DDP2)       | .26 |

|     |         | 3.2.12   | 13h: I/O Port 3 Data Direction (DDP3)       | .27 |

|     |         | 3.2.13   | 14h: I/O Port 4 Data Direction (DDP4)       | .27 |

|     |         | 3.2.14   | 15h: I/O Port 5 Data Direction (DDP5)       | .28 |

|     |         | 3.2.15   | 16h: I/O Port 6 Data Direction (DDP6)       | .28 |

|     |         | 3.2.16   | 17h: I/O Port 7 Data Direction (DDP7)       | .29 |

|     |         | 3.2.17   | 20h: Port Bypass Control 0 (PBC0)           | .30 |

|     |         | 3.2.18   | 21h: Port Bypass Control 1 (PBC1)           | .31 |

|     |         | 3.2.19   | 22h: Port Bypass Control 2 (PBC2)           | .32 |

|     |         | 3.2.20   | 23h: Port Bypass Control 3 (PBC3)           | .33 |

|     |         | 3.2.21   | 24h: Port Bypass Control 4 (PBC4)           | .34 |

|     |         | 3.2.22   | 25h: Port Bypass Control 5 (PBC5)           | .35 |

|     |         | 3.2.23   | 26h: Port Bypass Control 6 (PBC6)           | .36 |

| 3.2.25       28h: Port Bypass Control 9 (PBC9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.2.24 | 27h: Port Bypass Control 7 (PBC7)       |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------|----|

| 3.2.27       2Ah: Port Bypass Control 10 (PBC10)       40         3.2.28       2Bh: Port Bypass Control 11 (PBC11)       41         3.2.29       2Ch: Port Bypass Control 12 (PBC12)       42         3.2.30       2Dh: Port Bypass Control 13 (PBC13)       43         3.2.31       2Eh: Port Bypass Control 15 (PBC15)       45         3.2.33       30h: Fan Speed Control 0 (FSC0)       47         3.2.33       32h: Fan Speed Control 0 (FSC0)       47         3.2.35       32h: Fan Speed Control 0 (FSC0)       47         3.2.36       34h: Fan Speed Control 1 (FSC1)       48         3.2.37       35h: Fan Speed Control 1 (FSC0)       47         3.2.38       36h: Fan Speed Control 1 (FSC0)       49         3.2.39       36h: Fan Speed Control 1 (FSC1)       49         3.2.39       36h: Fan Speed Control 2 (FSC2)       50         3.2.41       3Ah: Fan Speed Control 3 (FSC3)       52         3.2.42       3Ch: Fan Speed Control 3 (FSC3)       53         3.2.43       3Dh: Fan Speed Control 4 (FSCC4)       55         3.2.44       3Ch: Fan Speed Control 4 (FSCC4)       55         3.2.44       3Ch: Fan Speed Control 4 (FSCC4)       55         3.2.44       4th: Fan Speed Control 4 (FSCC5)       57 </td <td>3.2.25</td> <td>28h: Port Bypass Control 8 (PBC8)</td> <td></td>                                                 | 3.2.25 | 28h: Port Bypass Control 8 (PBC8)       |    |

| 3.2.27       2Ah: Port Bypass Control 10 (PBC10)       40         3.2.28       2Bh: Port Bypass Control 11 (PBC11)       41         3.2.29       2Ch: Port Bypass Control 12 (PBC12)       42         3.2.30       2Dh: Port Bypass Control 13 (PBC13)       43         3.2.31       2Eh: Port Bypass Control 15 (PBC15)       45         3.2.33       30h: Fan Speed Control 0 (FSC0)       47         3.2.33       32h: Fan Speed Control 0 (FSC0)       47         3.2.35       32h: Fan Speed Control 0 (FSC0)       47         3.2.36       34h: Fan Speed Control 1 (FSC1)       48         3.2.37       35h: Fan Speed Control 1 (FSC0)       47         3.2.38       36h: Fan Speed Control 1 (FSC0)       49         3.2.39       36h: Fan Speed Control 1 (FSC1)       49         3.2.39       36h: Fan Speed Control 2 (FSC2)       50         3.2.41       3Ah: Fan Speed Control 3 (FSC3)       52         3.2.42       3Ch: Fan Speed Control 3 (FSC3)       53         3.2.43       3Dh: Fan Speed Control 4 (FSCC4)       55         3.2.44       3Ch: Fan Speed Control 4 (FSCC4)       55         3.2.44       3Ch: Fan Speed Control 4 (FSCC4)       55         3.2.44       4th: Fan Speed Control 4 (FSCC5)       57 </td <td>3.2.26</td> <td>29h: Port Bypass Control 9 (PBC9)</td> <td></td>                                                 | 3.2.26 | 29h: Port Bypass Control 9 (PBC9)       |    |

| 3.2.28       2Bh: Port Bypass Control 12 (PBC11)       41         3.2.29       2Ch: Port Bypass Control 13 (PBC13)       43         3.2.31       2Eh: Port Bypass Control 15 (PBC15)       44         3.2.32       2Fh: Port Bypass Control 15 (PBC15)       45         3.2.31       2Eh: Port Bypass Control 15 (PBC15)       45         3.2.33       30h: Fan Speed Control 0 (FSC0)       46         3.2.33       30h: Fan Speed Count Overflow 0 (FSC00)       47         3.2.33       34h: Fan Speed Count O (FSC0)       47         3.2.33       34h: Fan Speed Count 0 (FSC0)       47         3.2.33       35h: Fan Speed Count 0 (FSC1)       49         3.2.33       36h: Fan Speed Count 0 (FSC2)       50         3.2.43       38h: Fan Speed Count 0 (FSC2)       51         3.2.43       39h: Fan Speed Count 0 (FSC2)       51         3.2.43       39h: Fan Speed Count 0 (FSC03)       52         3.2.44       31h: Fan Speed Count 0 (FSC3)       53         3.2.44       31h: Fan Speed Count 0 (FSC3)       53         3.2.44       31h: Fan Speed Count 0 (FSC04)       55         3.2.44       31h: Fan Speed Count 0 (FSC4)       55         3.2.44       31h: Fan Speed Count 0 (FSC5)       57                                                                                                                                             | 3.2.27 |                                         |    |

| 3.2.30       2Dh: Port Bypass Control 13 (PBC13)       43         3.2.31       2Eh: Port Bypass Control 14 (PBC14)       44         3.2.32       2Fh: Port Bypass Control 15 (PBC15)       45         3.2.33       30h: Fan Speed Control 0 (FSC0)       47         3.2.35       32h: Fan Speed Court Overflow 0 (FSC0)       47         3.2.35       32h: Fan Speed Court Overflow 1 (FSC0)       47         3.2.36       34h: Fan Speed Court Overflow 1 (FSC01)       48         3.2.37       35h: Fan Speed Court Overflow 1 (FSC01)       49         3.2.39       38h: Fan Speed Court Overflow 2 (FSC02)       50         3.2.40       39h: Fan Speed Court Overflow 2 (FSC02)       51         3.2.41       3Ah: Fan Speed Court 0 yerflow 3 (FSC03)       53         3.2.42       3Ch: Fan Speed Court 0 yerflow 3 (FSC03)       53         3.2.43       3Dh: Fan Speed Court 0 yerflow 4 (FSC04)       54         3.2.44       3Eh: Fan Speed Court 0 yerflow 4 (FSC04)       55         3.2.44       4Dh: Fan Speed Court 0 yerflow 4 (FSC04)       55         3.2.44       4Dh: Fan Speed Court 0 yerflow 4 (FSC04)       55         3.2.44       4Dh: Fan Speed Court 0 yerflow 5 (FSC05)       57         3.2.44       4Dh: Fan Speed Court 0 yerflow 5 (FSC05)       57 </td <td>3.2.28</td> <td></td> <td></td>                                      | 3.2.28 |                                         |    |

| 3.2.30       2Dh: Port Bypass Control 13 (PBC13)       43         3.2.31       2Eh: Port Bypass Control 14 (PBC14)       44         3.2.32       2Fh: Port Bypass Control 15 (PBC15)       45         3.2.33       30h: Fan Speed Control 0 (FSC0)       47         3.2.35       32h: Fan Speed Court Overflow 0 (FSC0)       47         3.2.35       32h: Fan Speed Court Overflow 1 (FSC0)       47         3.2.36       34h: Fan Speed Court Overflow 1 (FSC01)       48         3.2.37       35h: Fan Speed Court Overflow 1 (FSC01)       49         3.2.39       38h: Fan Speed Court Overflow 2 (FSC02)       50         3.2.40       39h: Fan Speed Court Overflow 2 (FSC02)       51         3.2.41       3Ah: Fan Speed Court 0 yerflow 3 (FSC03)       53         3.2.42       3Ch: Fan Speed Court 0 yerflow 3 (FSC03)       53         3.2.43       3Dh: Fan Speed Court 0 yerflow 4 (FSC04)       54         3.2.44       3Eh: Fan Speed Court 0 yerflow 4 (FSC04)       55         3.2.44       4Dh: Fan Speed Court 0 yerflow 4 (FSC04)       55         3.2.44       4Dh: Fan Speed Court 0 yerflow 4 (FSC04)       55         3.2.44       4Dh: Fan Speed Court 0 yerflow 5 (FSC05)       57         3.2.44       4Dh: Fan Speed Court 0 yerflow 5 (FSC05)       57 </td <td>3.2.29</td> <td>2Ch: Port Bypass Control 12 (PBC12)</td> <td>42</td> | 3.2.29 | 2Ch: Port Bypass Control 12 (PBC12)     | 42 |

| 3.2.31       2Eh: Port Bypass Control 14 (PBC14)       44         3.2.32       2Fh: Port Bypass Control 15 (PBC15)       45         3.2.33       30h: Fan Speed Countrol 0 (FSC00)       46         3.2.34       31h: Fan Speed Count Overflow 0 (FSC00)       47         3.2.35       32h: Fan Speed Count Overflow 1 (FSC0)       47         3.2.36       34h: Fan Speed Count Overflow 1 (FSC0)       47         3.2.37       35h: Fan Speed Count Overflow 1 (FSC01)       49         3.2.39       38h: Fan Speed Count Overflow 2 (FSC02)       50         3.2.40       39h: Fan Speed Count Overflow 2 (FSC02)       51         3.2.41       3Ah: Fan Speed Count Overflow 3 (FSC03)       53         3.2.42       3Ch: Fan Speed Count Overflow 3 (FSC03)       53         3.2.43       3Dh: Fan Speed Count Overflow 3 (FSC03)       53         3.2.44       4Dh: Fan Speed Count Overflow 4 (FSC04)       55         3.2.44       4Dh: Fan Speed Count Overflow 4 (FSC04)       55         3.2.44       4Dh: Fan Speed Count Overflow 5 (FSC05)       57         3.2.45       4Dh: Fan Speed Count Overflow 5 (FSC05)       57         3.2.44       4Dh: Fan Speed Count Overflow 5 (FSC05)       57         3.2.45       4Dh: Fan Speed Count Overflow 6 (FSC06)       58 <td>3.2.30</td> <td></td> <td></td>                                             | 3.2.30 |                                         |    |

| 3.2.32       2Fh: Port Bypass Control 15 (PBC15)       45         3.2.33       30h: Fan Speed Control 0 (FSC0)       46         3.2.34       31h: Fan Speed Count Overflow 0 (FSC0)       47         3.2.35       32h: Fan Speed Count 0 (FSC0)       47         3.2.35       34h: Fan Speed Count 0 (FSC0)       47         3.2.35       34h: Fan Speed Count 0 (FSC0)       49         3.2.37       35h: Fan Speed Count Overflow 1 (FSC01)       49         3.2.39       38h: Fan Speed Count Overflow 2 (FSC02)       50         3.2.40       39h: Fan Speed Count Overflow 2 (FSC02)       51         3.2.41       3h: Fan Speed Count Overflow 3 (FSC03)       52         3.2.43       30h: Fan Speed Count Overflow 3 (FSC03)       53         3.2.44       30h: Fan Speed Count Overflow 4 (FSC04)       55         3.2.43       30h: Fan Speed Count Overflow 4 (FSC04)       55         3.2.44       4th: Fan Speed Count Overflow 4 (FSC04)       55         3.2.45       40h: Fan Speed Count Overflow 4 (FSC05)       57         3.2.44       4th: Fan Speed Count Overflow 5 (FSC05)       57         3.2.44       4th: Fan Speed Count Overflow 5 (FSC05)       57         3.2.44       4th: Fan Speed Count Overflow 6 (FSC05)       57         3.2.54<                                                                                             | 3.2.31 |                                         |    |

| 3.2.34       31h: Fan Speed Court Overflow 0 (FSCO0)       47         3.2.35       32h: Fan Speed Current Count 0 (FSCO)       47         3.2.36       34h: Fan Speed Count Overflow 1 (FSCO1)       48         3.2.37       35h: Fan Speed Court (FSCO)       49         3.2.38       36h: Fan Speed Court 1 (FSCC1)       49         3.2.39       38h: Fan Speed Court Overflow 2 (FSCO2)       50         3.2.40       39h: Fan Speed Court Overflow 2 (FSCO2)       51         3.2.41       3Ah: Fan Speed Court Overflow 3 (FSCO3)       52         3.2.42       3Ch: Fan Speed Court Overflow 3 (FSCO3)       53         3.2.43       3Dh: Fan Speed Court Overflow 3 (FSCO3)       53         3.2.44       3Ch: Fan Speed Court Overflow 4 (FSCO4)       55         3.2.45       40h: Fan Speed Court Overflow 4 (FSCO4)       55         3.2.44       41h: Fan Speed Court Overflow 4 (FSCO4)       55         3.2.45       40h: Fan Speed Court Overflow 4 (FSCO5)       57         3.2.44       44h: Fan Speed Court Overflow 5 (FSCO5)       57         3.2.45       44h: Fan Speed Court Overflow 5 (FSCO5)       57         3.2.44       44h: Fan Speed Court Overflow 5 (FSCO5)       57         3.2.50       46h: Fan Speed Court Overflow 6 (FSCO6)       59      <                                                                                 | 3.2.32 | 2Fh: Port Bypass Control 15 (PBC15)     | 45 |

| 3.2.34       31h: Fan Speed Court Overflow 0 (FSCO0)       47         3.2.35       32h: Fan Speed Current Count 0 (FSCO)       47         3.2.36       34h: Fan Speed Count Overflow 1 (FSCO1)       48         3.2.37       35h: Fan Speed Court (FSCO)       49         3.2.38       36h: Fan Speed Court 1 (FSCC1)       49         3.2.39       38h: Fan Speed Court Overflow 2 (FSCO2)       50         3.2.40       39h: Fan Speed Court Overflow 2 (FSCO2)       51         3.2.41       3Ah: Fan Speed Court Overflow 3 (FSCO3)       52         3.2.42       3Ch: Fan Speed Court Overflow 3 (FSCO3)       53         3.2.43       3Dh: Fan Speed Court Overflow 3 (FSCO3)       53         3.2.44       3Ch: Fan Speed Court Overflow 4 (FSCO4)       55         3.2.45       40h: Fan Speed Court Overflow 4 (FSCO4)       55         3.2.44       41h: Fan Speed Court Overflow 4 (FSCO4)       55         3.2.45       40h: Fan Speed Court Overflow 4 (FSCO5)       57         3.2.44       44h: Fan Speed Court Overflow 5 (FSCO5)       57         3.2.45       44h: Fan Speed Court Overflow 5 (FSCO5)       57         3.2.44       44h: Fan Speed Court Overflow 5 (FSCO5)       57         3.2.50       46h: Fan Speed Court Overflow 6 (FSCO6)       59      <                                                                                 | 3.2.33 | 30h: Fan Speed Control 0 (FSC0)         | 46 |

| 3.2.36       34h: Fan Speed Control 1 (FSC1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3.2.34 |                                         |    |

| 3.2.37       35h: Fan Speed Count Overflow 1 (FSCO1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.2.35 | 32h: Fan Speed Current Count 0 (FSCC0)  | 47 |

| 3.2.38       36h: Fan Speed Current Count 1 (FSCC1)       .49         3.2.39       38h: Fan Speed Control 2 (FSC2)       .50         3.2.40       39h: Fan Speed Count Overflow 2 (FSCO2)       .51         3.2.41       3Ah: Fan Speed Court 0 (FSC3)       .52         3.2.42       3Ch: Fan Speed Court 0 verflow 3 (FSC03)       .53         3.2.43       3Dh: Fan Speed Court Overflow 3 (FSC3)       .53         3.2.44       3Eh: Fan Speed Court 0 verflow 4 (FSC04)       .54         3.2.45       40h: Fan Speed Court 0 verflow 4 (FSC04)       .55         3.2.44       41h: Fan Speed Court 0 verflow 4 (FSC04)       .55         3.2.47       42h: Fan Speed Current Count 4 (FSC04)       .55         3.2.48       44h: Fan Speed Court 0 verflow 5 (FSC05)       .57         3.2.50       46h: Fan Speed Court 0 verflow 5 (FSC05)       .57         3.2.51       48h: Fan Speed Court 0 verflow 6 (FSC06)       .59         3.2.54       49h: Fan Speed Court 0 Verflow 7 (FSC07)       .60         3.2.54       49h: Fan Speed Current Count 6 (FSC07)       .61         3.2.55       4Dh: Fan Speed Current Count 7 (FSC07)       .61         3.2.54       4Dh: Fan Speed Current Count 7 (FSC07)       .61         3.2.55       4Dh: Fan Speed Current Count 7 (FSC07)                                                                          | 3.2.36 | 34h: Fan Speed Control 1 (FSC1)         | 48 |

| 3.2.39       38h: Fan Speed Control 2 (FSC2)       .50         3.2.40       39h: Fan Speed Court Overflow 2 (FSC02)       .51         3.2.41       3Ah: Fan Speed Courrol 3 (FSC3)       .52         3.2.42       3Ch: Fan Speed Court Overflow 3 (FSC03)       .53         3.2.43       3Dh: Fan Speed Courrol 0 (FSC4)       .53         3.2.44       3Eh: Fan Speed Current Count 3 (FSC03)       .53         3.2.45       40h: Fan Speed Current Count 3 (FSC04)       .54         3.2.44       41h: Fan Speed Courrent Count 4 (FSC04)       .55         3.2.47       42h: Fan Speed Current Count 4 (FSC04)       .55         3.2.48       44h: Fan Speed Courrent Count 4 (FSC05)       .57         3.2.50       46h: Fan Speed Courrent Count 5 (FSC05)       .57         3.2.51       48h: Fan Speed Courrent Count 5 (FSC05)       .57         3.2.52       49h: Fan Speed Courrent Count 5 (FSC05)       .57         3.2.52       49h: Fan Speed Courrent Count 6 (FSC06)       .59         3.2.53       4Ah: Fan Speed Courrent Count 6 (FSC06)       .59         3.2.54       40h: Fan Speed Courrent Count 7 (FSC07)       .60         3.2.55       40h: Fan Speed Courrent Count 7 (FSC07)       .61         3.2.54       40h: Fan Speed Courtol 0 (PTC00)       .62 <td>3.2.37</td> <td>35h: Fan Speed Count Overflow 1 (FSCO1)</td> <td>49</td>    | 3.2.37 | 35h: Fan Speed Count Overflow 1 (FSCO1) | 49 |

| 3.2.40       39h: Fan Speed Court Overflow 2 (FSCO2)       .51         3.2.41       3Ah: Fan Speed Current Count 2 (FSCC2)       .51         3.2.42       3Ch: Fan Speed Court Overflow 3 (FSCO3)       .53         3.2.43       3Dh: Fan Speed Court Overflow 3 (FSCO3)       .53         3.2.44       3Eh: Fan Speed Court Overflow 3 (FSCO3)       .53         3.2.44       3Eh: Fan Speed Court Overflow 3 (FSCO3)       .53         3.2.45       40h: Fan Speed Court Overflow 4 (FSCC4)       .54         3.2.46       41h: Fan Speed Court Overflow 4 (FSCO4)       .55         3.2.47       42h: Fan Speed Court Overflow 4 (FSCC4)       .55         3.2.48       44h: Fan Speed Court Overflow 5 (FSCO5)       .57         3.2.50       45h: Fan Speed Court Overflow 5 (FSCO5)       .57         3.2.51       48h: Fan Speed Court Overflow 5 (FSCO5)       .57         3.2.51       48h: Fan Speed Court Overflow 6 (FSCC6)       .59         3.2.52       49h: Fan Speed Court Overflow 6 (FSCC6)       .59         3.2.54       4Ch: Fan Speed Court Overflow 7 (FSCO7)       .61         3.2.55       4Dh: Fan Speed Court Overflow 7 (FSCO7)       .61         3.2.57       70h: Pulse Train Control 00 (PTC00)       .62         3.2.57       70h: Pulse Train Control 10 (PTC10)                                                                  | 3.2.38 | 36h: Fan Speed Current Count 1 (FSCC1)  | 49 |

| 3.2.41       3Ah: Fan Speed Current Count 2 (FSCC2)       .51         3.2.42       3Ch: Fan Speed Control 3 (FSC3)       .52         3.2.43       3Dh: Fan Speed Court Overflow 3 (FSC03)       .53         3.2.44       3Eh: Fan Speed Current Count 3 (FSCC3)       .53         3.2.45       40h: Fan Speed Court Overflow 4 (FSC04)       .54         3.2.46       41h: Fan Speed Court Overflow 4 (FSC04)       .55         3.2.47       42h: Fan Speed Court Overflow 4 (FSC04)       .55         3.2.48       44h: Fan Speed Court Overflow 5 (FSC05)       .56         3.2.49       45h: Fan Speed Court Overflow 5 (FSC05)       .57         3.2.50       46h: Fan Speed Court Overflow 5 (FSC05)       .57         3.2.51       48h: Fan Speed Court Overflow 6 (FSC06)       .59         3.2.52       49h: Fan Speed Court Overflow 6 (FSC06)       .59         3.2.53       4Ah: Fan Speed Court Overflow 7 (FSC07)       .60         3.2.54       4Ch: Fan Speed Court Overflow 7 (FSC07)       .61         3.2.55       4Dh: Fan Speed Current Count 7 (FSC07)       .61         3.2.54       4Dh: Fan Speed Current Count 7 (FSC07)       .61         3.2.55       71h: Pulse Train Control 00 (PTC00)       .62         3.2.57       70h: Pulse Train Control 01 (PTC10)       .63                                                                   | 3.2.39 | 38h: Fan Speed Control 2 (FSC2)         | 50 |

| 3.2.42       3Ch: Fan Speed Control 3 (FSC3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3.2.40 | 39h: Fan Speed Count Overflow 2 (FSCO2) | 51 |

| 3.2.43       3Dh: Fan Speed Court Overflow 3 (FSCO3)       53         3.2.44       3Eh: Fan Speed Current Count 3 (FSCC3)       53         3.2.45       40h: Fan Speed Control 4 (FSC4)       54         3.2.46       41h: Fan Speed Count Overflow 4 (FSCO4)       55         3.2.47       42h: Fan Speed Court Overflow 4 (FSCO4)       55         3.2.48       44h: Fan Speed Court Overflow 5 (FSCO5)       56         3.2.49       45h: Fan Speed Court Overflow 5 (FSCO5)       57         3.2.50       46h: Fan Speed Court Overflow 5 (FSCO5)       57         3.2.51       48h: Fan Speed Court Overflow 5 (FSCO5)       57         3.2.52       49h: Fan Speed Court Overflow 6 (FSCO6)       59         3.2.52       49h: Fan Speed Court Overflow 6 (FSCO6)       59         3.2.54       4Ch: Fan Speed Court Overflow 7 (FSCO7)       61         3.2.55       4Dh: Fan Speed Court Overflow 7 (FSCO7)       61         3.2.54       4Eh: Fan Speed Current Count 7 (FSCO7)       61         3.2.55       4Dh: Fan Speed Current Count 7 (FSCO7)       61         3.2.57       70h: Pulse Train Control 00 (PTC00)       62         3.2.58       71h: Pulse Train Control 10 (PTC10)       63         3.2.59       72h: Pulse Train Control 20 (PTC20)       66      <                                                                                 | 3.2.41 | 3Ah: Fan Speed Current Count 2 (FSCC2)  | 51 |

| 3.2.44       3Eh: Fan Speed Current Count 3 (FSCC3)       53         3.2.45       40h: Fan Speed Control 4 (FSC4)       54         3.2.46       41h: Fan Speed Count Overflow 4 (FSCO4)       55         3.2.47       42h: Fan Speed Current Count 4 (FSCC4)       55         3.2.48       44h: Fan Speed Current Count 4 (FSCC4)       55         3.2.49       45h: Fan Speed Count Overflow 5 (FSC05)       56         3.2.49       45h: Fan Speed Count Overflow 5 (FSC05)       57         3.2.50       46h: Fan Speed Count Overflow 5 (FSC05)       57         3.2.51       48h: Fan Speed Count Overflow 6 (FSC06)       59         3.2.52       49h: Fan Speed Count Overflow 6 (FSC06)       59         3.2.53       4Ah: Fan Speed Count Overflow 6 (FSC06)       59         3.2.54       4Ch: Fan Speed Count Overflow 7 (FSC07)       60         3.2.55       4Dh: Fan Speed Count Overflow 7 (FSC07)       61         3.2.56       4Eh: Fan Speed Count Overflow 7 (FSC07)       61         3.2.57       70h: Pulse Train Control 00 (PTC00)       62         3.2.58       71h: Pulse Train Control 01 (PTC01)       63         3.2.59       72h: Pulse Train Control 10 (PTC10)       64         3.2.60       73h: Pulse Train Control 20 (PTC20)       66                                                                                            | 3.2.42 | 3Ch: Fan Speed Control 3 (FSC3)         | 52 |

| 3.2.45       40h: Fan Speed Control 4 (FSC4)       .54         3.2.46       41h: Fan Speed Count Overflow 4 (FSC04)       .55         3.2.47       42h: Fan Speed Current Count 4 (FSC04)       .55         3.2.48       44h: Fan Speed Control 5 (FSC5)       .56         3.2.49       45h: Fan Speed Count Overflow 5 (FSC05)       .57         3.2.50       46h: Fan Speed Current Count 5 (FSC05)       .57         3.2.51       48h: Fan Speed Control 6 (FSC6)       .58         3.2.52       49h: Fan Speed Court Overflow 6 (FSC06)       .59         3.2.53       4Ah: Fan Speed Court Overflow 6 (FSC06)       .59         3.2.54       4Ch: Fan Speed Court Overflow 7 (FSC07)       .60         3.2.55       4Dh: Fan Speed Court Overflow 7 (FSC07)       .61         3.2.56       4Eh: Fan Speed Current Count 7 (FSC07)       .61         3.2.57       70h: Pulse Train Control 00 (PTC00)       .62         3.2.58       71h: Pulse Train Control 10 (PTC10)       .63         3.2.59       72h: Pulse Train Control 10 (PTC10)       .64         3.2.60       73h: Pulse Train Control 20 (PTC20)       .66         3.2.61       74h: Pulse Train Control 20 (PTC20)       .66         3.2.62       75h: Pulse Train Control 30 (PTC30)       .68                                                                                                  | 3.2.43 | 3Dh: Fan Speed Count Overflow 3 (FSCO3) | 53 |

| 3.2.46       41h: Fan Speed Count Overflow 4 (FSCO4)       .55         3.2.47       42h: Fan Speed Current Count 4 (FSCC4)       .55         3.2.48       44h: Fan Speed Count O 5 (FSC5)       .56         3.2.49       45h: Fan Speed Count Overflow 5 (FSCO5)       .57         3.2.50       46h: Fan Speed Current Count 5 (FSCC5)       .57         3.2.51       48h: Fan Speed Count Overflow 6 (FSCC6)       .58         3.2.52       49h: Fan Speed Count Overflow 6 (FSCC6)       .59         3.2.53       4Ah: Fan Speed Count Overflow 6 (FSCC6)       .59         3.2.54       4Ch: Fan Speed Count Overflow 7 (FSC7)       .60         3.2.55       4Dh: Fan Speed Count Overflow 7 (FSCO7)       .61         3.2.56       4Eh: Fan Speed Current Count 7 (FSC7)       .61         3.2.57       70h: Pulse Train Control 00 (PTC00)       .62         3.2.58       71h: Pulse Train Control 10 (PTC10)       .63         3.2.59       72h: Pulse Train Control 10 (PTC10)       .64         3.2.60       73h: Pulse Train Control 20 (PTC20)       .66         3.2.61       74h: Pulse Train Control 20 (PTC20)       .66         3.2.63       76h: Pulse Train Control 30 (PTC30)       .68         3.2.64       77h: Pulse Train Control 31 (PTC31)       .69      <                                                                                 | 3.2.44 | 3Eh: Fan Speed Current Count 3 (FSCC3)  | 53 |

| 3.2.47       42h: Fan Speed Current Count 4 (FSCC4)       55         3.2.48       44h: Fan Speed Control 5 (FSC5)       56         3.2.49       45h: Fan Speed Count Overflow 5 (FSC05)       57         3.2.50       46h: Fan Speed Court Count 5 (FSCC5)       57         3.2.51       48h: Fan Speed Count Overflow 6 (FSC06)       58         3.2.52       49h: Fan Speed Count Overflow 6 (FSC06)       59         3.2.53       4Ah: Fan Speed Count Overflow 6 (FSC06)       59         3.2.54       4Ch: Fan Speed Count Overflow 7 (FSC07)       60         3.2.55       4Dh: Fan Speed Count Overflow 7 (FSC07)       61         3.2.56       4Eh: Fan Speed Current Count 7 (FSC07)       61         3.2.57       70h: Pulse Train Control 00 (PTC00)       62         3.2.58       71h: Pulse Train Control 01 (PTC01)       63         3.2.59       72h: Pulse Train Control 10 (PTC10)       64         3.2.60       73h: Pulse Train Control 20 (PTC20)       66         3.2.61       74h: Pulse Train Control 21 (PTC21)       67         3.2.63       76h: Pulse Train Control 30 (PTC30)       68         3.2.64       77h: Pulse Train Control 31 (PTC31)       69         3.2.65       78h: Pulse Train Control 40 (PTC40)       70         3.2.66 </td <td>3.2.45</td> <td>40h: Fan Speed Control 4 (FSC4)</td> <td>54</td>                     | 3.2.45 | 40h: Fan Speed Control 4 (FSC4)         | 54 |

| 3.2.48       44h: Fan Speed Control 5 (FSC5)       56         3.2.49       45h: Fan Speed Count Overflow 5 (FSC05)       57         3.2.50       46h: Fan Speed Current Count 5 (FSC05)       57         3.2.51       48h: Fan Speed Control 6 (FSC6)       58         3.2.52       49h: Fan Speed Count Overflow 6 (FSC06)       59         3.2.53       4Ah: Fan Speed Count Overflow 6 (FSC06)       59         3.2.54       4Ch: Fan Speed Count Overflow 7 (FSC7)       60         3.2.55       4Dh: Fan Speed Count Overflow 7 (FSC07)       61         3.2.56       4Eh: Fan Speed Current Count 7 (FSC07)       61         3.2.57       70h: Pulse Train Control 00 (PTC00)       62         3.2.58       71h: Pulse Train Control 01 (PTC01)       63         3.2.59       72h: Pulse Train Control 10 (PTC10)       64         3.2.60       73h: Pulse Train Control 11 (PTC11)       65         3.2.61       74h: Pulse Train Control 20 (PTC20)       66         3.2.63       76h: Pulse Train Control 30 (PTC30)       68         3.2.64       77h: Pulse Train Control 31 (PTC31)       69         3.2.65       78h: Pulse Train Control 31 (PTC41)       70         3.2.66       79h: Pulse Train Control 41 (PTC41)       71                                                                                                                        | 3.2.46 | 41h: Fan Speed Count Overflow 4 (FSCO4) | 55 |

| 3.2.49       45h: Fan Speed Count Overflow 5 (FSCO5)       57         3.2.50       46h: Fan Speed Current Count 5 (FSCC5)       57         3.2.51       48h: Fan Speed Control 6 (FSC6)       58         3.2.52       49h: Fan Speed Count Overflow 6 (FSCO6)       59         3.2.53       4Ah: Fan Speed Count Overflow 6 (FSCO6)       59         3.2.54       4Ch: Fan Speed Count Overflow 7 (FSC7)       60         3.2.55       4Dh: Fan Speed Count Overflow 7 (FSCO7)       61         3.2.56       4Eh: Fan Speed Current Count 7 (FSC07)       61         3.2.57       70h: Pulse Train Control 00 (PTC00)       62         3.2.58       71h: Pulse Train Control 01 (PTC10)       63         3.2.59       72h: Pulse Train Control 10 (PTC10)       64         3.2.60       73h: Pulse Train Control 20 (PTC20)       66         3.2.61       74h: Pulse Train Control 20 (PTC20)       66         3.2.62       75h: Pulse Train Control 20 (PTC20)       66         3.2.63       76h: Pulse Train Control 30 (PTC30)       68         3.2.64       77h: Pulse Train Control 31 (PTC31)       69         3.2.65       78h: Pulse Train Control 40 (PTC40)       70         3.2.66       79h: Pulse Train Control 41 (PTC41)       71                                                                                                                    | 3.2.47 | 42h: Fan Speed Current Count 4 (FSCC4)  | 55 |

| 3.2.50       46h: Fan Speed Current Count 5 (FSCC5)       .57         3.2.51       48h: Fan Speed Control 6 (FSC6)       .58         3.2.52       49h: Fan Speed Count Overflow 6 (FSCO6)       .59         3.2.53       4Ah: Fan Speed Current Count 6 (FSCC6)       .59         3.2.54       4Ch: Fan Speed Control 7 (FSC7)       .60         3.2.55       4Dh: Fan Speed Count Overflow 7 (FSCO7)       .61         3.2.54       4Eh: Fan Speed Current Count 7 (FSC7)       .61         3.2.55       4Dh: Fan Speed Current Count 7 (FSCC7)       .61         3.2.56       4Eh: Fan Speed Current Count 7 (FSCC7)       .61         3.2.57       70h: Pulse Train Control 00 (PTC00)       .62         3.2.58       71h: Pulse Train Control 01 (PTC01)       .63         3.2.59       72h: Pulse Train Control 10 (PTC10)       .64         3.2.60       73h: Pulse Train Control 10 (PTC20)       .66         3.2.61       74h: Pulse Train Control 20 (PTC20)       .66         3.2.62       75h: Pulse Train Control 30 (PTC30)       .68         3.2.64       77h: Pulse Train Control 30 (PTC30)       .68         3.2.65       78h: Pulse Train Control 30 (PTC40)       .70         3.2.65       78h: Pulse Train Control 40 (PTC40)       .70         3.2                                                                                             | 3.2.48 | 44h: Fan Speed Control 5 (FSC5)         | 56 |

| 3.2.51       48h: Fan Speed Control 6 (FSC6)       58         3.2.52       49h: Fan Speed Count Overflow 6 (FSCO6)       59         3.2.53       4Ah: Fan Speed Current Count 6 (FSCC6)       59         3.2.54       4Ch: Fan Speed Control 7 (FSC7)       60         3.2.55       4Dh: Fan Speed Count Overflow 7 (FSCO7)       61         3.2.54       4Eh: Fan Speed Count Overflow 7 (FSCO7)       61         3.2.55       4Dh: Fan Speed Current Count 7 (FSCO7)       61         3.2.56       4Eh: Fan Speed Current Count 7 (FSCO7)       61         3.2.57       70h: Pulse Train Control 00 (PTC00)       62         3.2.58       71h: Pulse Train Control 01 (PTC01)       63         3.2.59       72h: Pulse Train Control 10 (PTC10)       64         3.2.60       73h: Pulse Train Control 10 (PTC20)       66         3.2.61       74h: Pulse Train Control 20 (PTC20)       66         3.2.62       75h: Pulse Train Control 21 (PTC21)       67         3.2.63       76h: Pulse Train Control 30 (PTC30)       68         3.2.64       77h: Pulse Train Control 31 (PTC31)       69         3.2.65       78h: Pulse Train Control 40 (PTC40)       70         3.2.66       79h: Pulse Train Control 41 (PTC41)       71                                                                                                                            | 3.2.49 |                                         |    |

| 3.2.52       49h: Fan Speed Count Overflow 6 (FSCO6)       59         3.2.53       4Ah: Fan Speed Current Count 6 (FSCC6)       59         3.2.54       4Ch: Fan Speed Control 7 (FSC7)       60         3.2.55       4Dh: Fan Speed Count Overflow 7 (FSCO7)       61         3.2.56       4Eh: Fan Speed Current Count 7 (FSCC7)       61         3.2.57       70h: Pulse Train Control 00 (PTC00)       62         3.2.58       71h: Pulse Train Control 01 (PTC01)       63         3.2.59       72h: Pulse Train Control 10 (PTC10)       64         3.2.60       73h: Pulse Train Control 10 (PTC11)       65         3.2.61       74h: Pulse Train Control 20 (PTC20)       66         3.2.62       75h: Pulse Train Control 21 (PTC21)       67         3.2.63       76h: Pulse Train Control 30 (PTC30)       68         3.2.64       77h: Pulse Train Control 31 (PTC31)       69         3.2.65       78h: Pulse Train Control 40 (PTC40)       70         3.2.66       79h: Pulse Train Control 41 (PTC41)       71                                                                                                                                                                                                                                                                                                                                     | 3.2.50 |                                         |    |

| 3.2.53       4Ah: Fan Speed Current Count 6 (FSCC6)       59         3.2.54       4Ch: Fan Speed Control 7 (FSC7)       60         3.2.55       4Dh: Fan Speed Count Overflow 7 (FSCO7)       61         3.2.56       4Eh: Fan Speed Current Count 7 (FSCO7)       61         3.2.57       70h: Pulse Train Control 00 (PTC00)       62         3.2.58       71h: Pulse Train Control 01 (PTC01)       63         3.2.59       72h: Pulse Train Control 10 (PTC10)       64         3.2.60       73h: Pulse Train Control 11 (PTC11)       65         3.2.61       74h: Pulse Train Control 20 (PTC20)       66         3.2.62       75h: Pulse Train Control 21 (PTC21)       67         3.2.63       76h: Pulse Train Control 30 (PTC30)       68         3.2.64       77h: Pulse Train Control 31 (PTC31)       69         3.2.65       78h: Pulse Train Control 40 (PTC40)       70         3.2.66       79h: Pulse Train Control 41 (PTC41)       71                                                                                                                                                                                                                                                                                                                                                                                                           | 3.2.51 |                                         |    |

| 3.2.54       4Ch: Fan Speed Control 7 (FSC7)       60         3.2.55       4Dh: Fan Speed Count Overflow 7 (FSCO7)       61         3.2.56       4Eh: Fan Speed Current Count 7 (FSCC7)       61         3.2.57       70h: Pulse Train Control 00 (PTC00)       62         3.2.58       71h: Pulse Train Control 01 (PTC01)       63         3.2.59       72h: Pulse Train Control 10 (PTC10)       64         3.2.60       73h: Pulse Train Control 11 (PTC11)       65         3.2.61       74h: Pulse Train Control 20 (PTC20)       66         3.2.62       75h: Pulse Train Control 21 (PTC21)       67         3.2.63       76h: Pulse Train Control 30 (PTC30)       68         3.2.64       77h: Pulse Train Control 31 (PTC31)       69         3.2.65       78h: Pulse Train Control 40 (PTC40)       70         3.2.66       79h: Pulse Train Control 41 (PTC41)       71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.2.52 |                                         |    |

| 3.2.55       4Dh: Fan Speed Count Overflow 7 (FSCO7)       61         3.2.56       4Eh: Fan Speed Current Count 7 (FSCC7)       61         3.2.57       70h: Pulse Train Control 00 (PTC00)       62         3.2.58       71h: Pulse Train Control 01 (PTC01)       63         3.2.59       72h: Pulse Train Control 10 (PTC10)       64         3.2.60       73h: Pulse Train Control 11 (PTC11)       65         3.2.61       74h: Pulse Train Control 20 (PTC20)       66         3.2.62       75h: Pulse Train Control 21 (PTC21)       67         3.2.63       76h: Pulse Train Control 30 (PTC30)       68         3.2.64       77h: Pulse Train Control 31 (PTC31)       69         3.2.65       78h: Pulse Train Control 40 (PTC40)       70         3.2.66       79h: Pulse Train Control 41 (PTC41)       71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3.2.53 |                                         |    |

| 3.2.56       4Eh: Fan Speed Current Count 7 (FSCC7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |                                         |    |

| 3.2.57       70h: Pulse Train Control 00 (PTC00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.2.55 |                                         |    |

| 3.2.58       71h: Pulse Train Control 01 (PTC01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |                                         |    |

| 3.2.59       72h: Pulse Train Control 10 (PTC10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.2.57 |                                         |    |

| 3.2.60       73h: Pulse Train Control 11 (PTC11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.2.58 |                                         |    |

| 3.2.61       74h: Pulse Train Control 20 (PTC20)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        | · · ·                                   |    |

| 3.2.62       75h: Pulse Train Control 21 (PTC21)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |                                         |    |

| 3.2.63       76h: Pulse Train Control 30 (PTC30)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |                                         |    |

| 3.2.64       77h: Pulse Train Control 31 (PTC31)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |                                         |    |

| 3.2.65       78h: Pulse Train Control 40 (PTC40)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |        |                                         |    |

| 3.2.66 79h: Pulse Train Control 41 (PTC41)71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |                                         |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |                                         |    |

| 3.2.67 7Ab: Pulse Train Control 50 (PTC50) 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |                                         |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3.2.67 | 7Ah: Pulse Train Control 50 (PTC50)     | 72 |

|      | 3.2.68   | 7Bh: Pulse Train Control 51 (PTC51)                    | .73 |

|------|----------|--------------------------------------------------------|-----|

|      | 3.2.69   | 7Ch: Pulse Train Control 60 (PTC60)                    | .74 |

|      | 3.2.70   | 7Dh: Pulse Train Control 61 (PTC61)                    | .75 |

|      | 3.2.71   | 7Eh: Pulse Train Control 70 (PTC70)                    | .76 |

|      | 3.2.72   | 7Fh: Pulse Train Control 71 (PTC71)                    | .77 |

|      | 3.2.73   | 80h-87h: Bit Control Port 0 (BCP00-BCP07)              | .78 |

|      | 3.2.74   | 88h: Pulse Train Control 80 (PTC80)                    | .81 |

|      | 3.2.75   | 89h: Pulse Train Control 81 (PTC81)                    | .82 |

|      | 3.2.76   | 8Ch: Pulse Train Control 90 (PTC90)                    | .83 |

|      | 3.2.77   | 8Dh: Pulse Train Control 91 (PTC91)                    | .84 |

|      | 3.2.78   | 90h-97h: Bit Control Port 1 (BCP10-BCP17)              | .85 |

|      | 3.2.79   | 98h-9Fh: Pulse-Width Modulation Control (PWMC0-PWMC7)  | .87 |

|      | 3.2.80   | A0h-A7h: Bit Control Port 2 (BCP20-BCP27)              | .89 |

|      | 3.2.81   | B0h-B7h: Bit Control Port 3 (BCP30-BCP37)              | .91 |

|      | 3.2.82   | C0h-C7h: Bit Control Port 4 (BCP40-BCP47)              | .93 |

|      | 3.2.83   | CCh: General-Purpose Timer Count 0 (GPTC0)             | .95 |

|      | 3.2.84   | CDh: General-Purpose Timer Count 1 (GPTC1)             | .95 |

|      | 3.2.85   | CEh: General-Purpose Timer Count 2 (GPTC2)             | .96 |

|      | 3.2.86   | CFh: General-Purpose Timer Enable (GPTE)               | .96 |

|      | 3.2.87   | D0h-D7h: Bit Control Port 5 (BCP50-BCP57)              | .97 |

|      | 3.2.88   | E0h-E7h: Bit Control Port 6 (BCP60-BCP67)              | .99 |

|      | 3.2.89   | E8h: Master Interface Clock Divider (MICD)1            | 101 |

|      | 3.2.90   | E9h: Master Interface Port Select (MIPS)1              | 102 |

|      | 3.2.91   | EAh: Master Interface Data (MID)1                      | 102 |

|      | 3.2.92   | EBh: Master Interface Command (MIC)1                   | 103 |

|      | 3.2.93   | ECh: Master Interface Low-Level Control (MILC)1        | 107 |

|      | 3.2.94   | EDh: Master Interface Status (MIS)1                    | 107 |

|      | 3.2.95   | EEh: Master Interface Read Data (MIRD)1                | 108 |

|      | 3.2.96   | F0h-F7h: Bit Control Port 7 (BCP70-BCP77)1             | 108 |

|      | 3.2.97   | F8h: Backplane Controller Interrupt Status (BCIS)1     | 110 |

|      | 3.2.98   | FCh: Backplane Controller Test (BCT)1                  | 111 |

|      | 3.2.99   | FDh: Clock Select Control (CSC)                        | 111 |

|      | 3.2.100  | FEh: Clock Divider Control (CDC)1                      | 113 |

|      | 3.2.101  | FFh: Backplane Controller Version (VER)1               | 114 |

| Elec | trical S | specifications                                         | 15  |

| 4.1  | DC Cha   | racteristics1                                          | 115 |

|      | 4.1.1    | General-Purpose I/O Ports                              | 115 |

|      | 4.1.2    | Two-Wire Serial Interface                              | 116 |

|      | 4.1.3    | Address Inputs1                                        | 116 |

|      | 4.1.4    | Interrupt Output1                                      |     |

|      | 4.1.5    | Reset, Test, and Synchronization Clock Control Inputs1 |     |

|      | 4.1.6    | Device Synchronization1                                |     |

|      | 4.1.7    | Oscillator and Clock Input1                            | 118 |

|      |          |                                                        |     |

4

|        |                                 | 4.1.8                                                   | Oscillator Output                                                | 118 |

|--------|---------------------------------|---------------------------------------------------------|------------------------------------------------------------------|-----|

|        | 4.2                             | AC Ch                                                   | aracteristics                                                    |     |

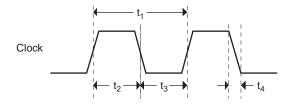

|        |                                 | 4.2.1                                                   | External Clock Timing                                            |     |

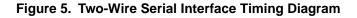

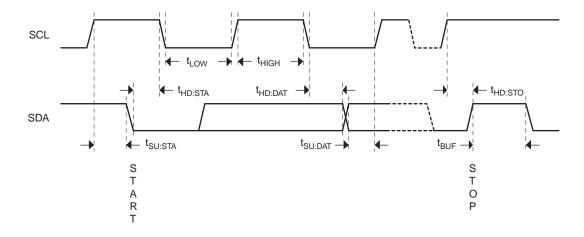

|        |                                 | 4.2.2                                                   | Two-Wire Serial Interface Timing                                 |     |

|        | 4.3                             | Operat                                                  | ting Conditions                                                  |     |

|        | 4.4                             | Maxim                                                   | um Ratings                                                       |     |

|        | 4.5                             |                                                         | /ire Serial Interface Operation                                  |     |

|        | 4.6                             | Oscilla                                                 | tor Requirements                                                 |     |

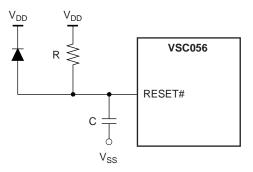

|        | 4.7                             | Extern                                                  | al Reset Circuit                                                 |     |

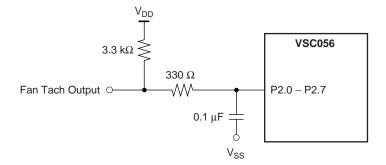

|        | 4.8                             | Optior                                                  | nal External Tach Filter                                         |     |

|        |                                 |                                                         |                                                                  |     |

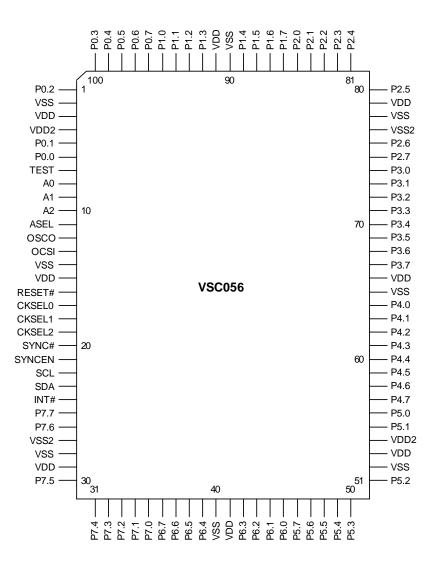

| 5      | Pin                             | Descri                                                  | iptions                                                          | 125 |

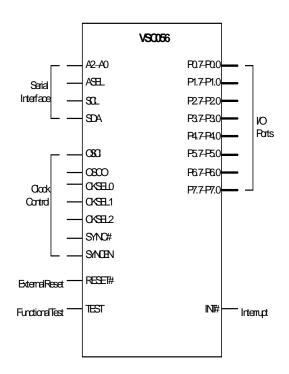

| 5      | <b>Pin</b><br>5.1               |                                                         | -                                                                |     |

| 5      |                                 | Pin Dia                                                 | iptions<br>agram<br>entifications                                |     |

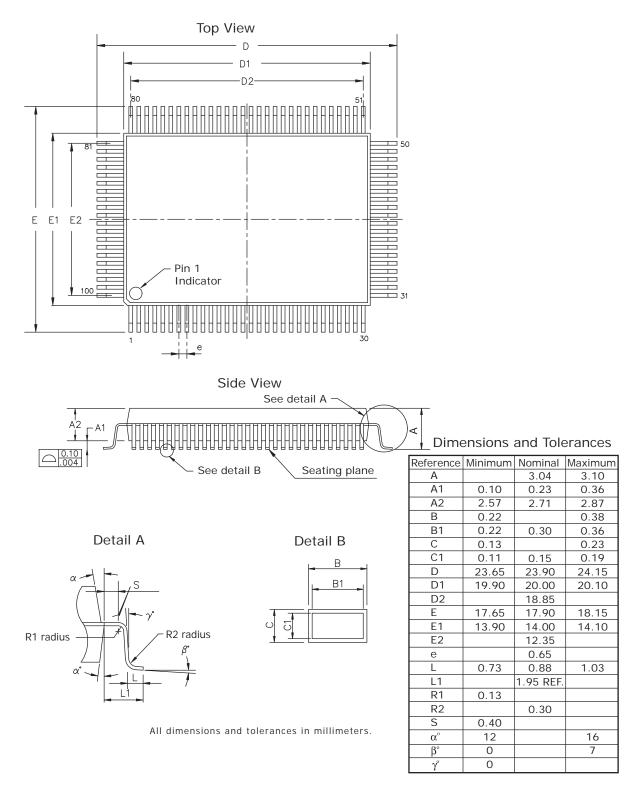

| 5<br>6 | 5.1<br>5.2                      | Pin Dia<br>Pin Ide                                      | agram                                                            |     |

| -      | 5.1<br>5.2                      | Pin Dia<br>Pin Ide<br><b>kage I</b> I                   | agram                                                            |     |

| -      | 5.1<br>5.2<br><b>Pac</b>        | Pin Dia<br>Pin Ide<br><b>kage I</b> I<br>Therm          | agram<br>entifications                                           |     |

| -      | 5.1<br>5.2<br><b>Pac</b><br>6.1 | Pin Dia<br>Pin Ide<br><b>kage Ii</b><br>Therm<br>Moistu | agram<br>entifications<br><b>nformation</b><br>al Specifications |     |

# **REVISION HISTORY**

This section describes changes that have been implemented in this document. The changes are listed by revision, starting with the most recent publication.

## **Revision 4.1**

Revision 4.1 of this data sheet was published in January 2008. The following is a summary of the changes implemented in the data sheet.

• The power supply voltage for the recommended operating conditions were corrected. The minimum power supply voltage is 3.0 V and maximum is 3.6 V. For more information, see Table 22, page 121.

## **Revision 4.0**

Revision 4.0 of this data sheet was published in April 2007. The following is a summary of the changes implemented in the data sheet:

- The electrostatic discharge voltage was added. For charged device model, it is ±1500 V. For human body model, it is a Class 2 rating.

- The moisture sensitivity is now specified as level 3.

## **Revision 2.0**

Revision 2.0 of this data sheet was published in October 2006. This is the first publication of this document.

# 1 Introduction

This data sheet provides reference information for the Maxim Enhanced Two-Wire Serial Backplane Controller, VSC056. It is intended for system designers and software and firmware developers who are using this device to support enclosure management functions or other related remote I/O expansion tasks. TheVSC056 is package and power supply compatible with the VSC055. The VSC056 is similar to the VSC055 in feature and function, except for differences in the reset and clock out functions.

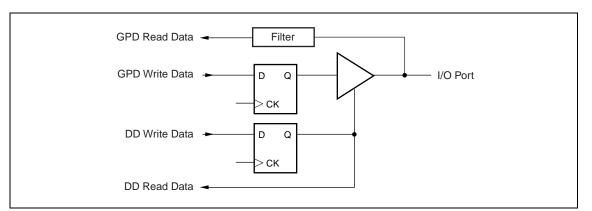

This document assumes that the user is familiar with the two-wire serial interfaces, the programmable I/O control, and the operation of FC-AL control functions, such as a PBC (port bypass controller), a CRU (clock recovery unit), and an SDU (signal detect unit). The user may also need to be familiar with Fibre Channel Arbitrated Loop (FC-AL) operation and SCSI Enclosure Services (SES).