# A3M39SL039 Airfast Power Amplifier Module with Autobias Control

Rev. 0 — March 2022 Data Sheet: Technical Data

The A3M39SL039 is a fully integrated Doherty power amplifier module designed for wireless infrastructure applications that demand high performance in the smallest footprint. Ideal for applications in massive MIMO systems, outdoor small cells and low power remote radio heads. The field-proven LDMOS power amplifiers are designed for TDD and FDD LTE systems. The module integrates an autobias feature with the option to overwrite production settings. Autobias automatically sets and regulates transistor bias over temperature upon power up. An integrated sensor for monitoring temperature is also present. Communications to the module can be accomplished via either I<sup>2</sup>C or SPI.

### 3700-3980 MHz

Typical LTE Performance:  $P_{out} = 8 \text{ W Avg.}$ ,  $V_{DD} = 30 \text{ Vdc}$ ,  $1 \times 20 \text{ MHz LTE}$ , Input Signal PAR = 8 dB @ 0.01% Probability on CCDF.<sup>1</sup>

| Carrier Center<br>Frequency | Gain<br>(dB) | ACPR<br>(dBc) | PAE<br>(%) |

|-----------------------------|--------------|---------------|------------|

| 3710 MHz                    | 28.1         | -33.0         | 33.0       |

| 3840 MHz                    | 28.0         | -35.0         | 34.0       |

| 3970 MHz                    | 28.1         | -32.0         | 34.0       |

<sup>1.</sup> All data measured with device soldered in NXP reference circuit.

### **Features**

- · Advanced high performance in-package Doherty

- Fully matched (50 ohm input/output, DC blocked)

- · Designed for low complexity analog or digital linearization systems

- · Autobias on power up

- · Temperature sensing

- Digital interface (I<sup>2</sup>C or SPI)

- · Embedded registers and DACs for setting bias conditions

- Tx Enable control pin for TDD operation

### A3M39SL039I A3M39SL039S

3700–3980 MHz, 28 dB, 8 W Avg. Airfast Power Amplifier Module with Autobias Control

# **Contents**

| 1     | Pinout configuration and function3 | 7     | Component layout and parts list                            | 14 |

|-------|------------------------------------|-------|------------------------------------------------------------|----|

| 1.1   | Pin connections3                   | 7.1   | Component layout                                           |    |

| 1.2   | Functional pin description4        | 7.2   | Component designations and values                          |    |

| 2     | Electrical characteristics4        | 8     | Temperature sensor                                         |    |

| 2.1   | Ratings4                           | 9     | Communication interfaces                                   |    |

| 2.1.1 | Maximum ratings4                   | 9.1   | SPI                                                        | 16 |

| 2.1.2 | Lifetime5                          | 9.1.1 | SPI timing diagram                                         | 16 |

| 2.1.3 | ESD protection characteristics5    | 9.1.2 | SPI instruction set definition                             |    |

| 2.1.4 | Moisture sensitivity level5        | 9.2   | I <sup>2</sup> C                                           |    |

| 2.2   | Operating characteristics5         | 9.2.1 | I <sup>2</sup> C addressing                                |    |

| 2.2.1 | Nominal DAC settings5              | 9.2.2 | I <sup>2</sup> C instruction set                           |    |

| 2.2.2 | Functional tests6                  | 9.2.3 | I <sup>2</sup> C Device ID Read instruction                |    |

| 2.2.3 | Wideband ruggedness6               | 9.3   | I <sup>2</sup> C electrical specification and timing for I | /O |

| 2.2.4 | Typical performance6               |       | stages and bus lines                                       |    |

| 3     | Register map and OTP memory7       | 9.3.1 | I <sup>2</sup> C SCLK and SDA characteristics              |    |

| 3.1   | One-time programmable memory7      | 9.3.2 | I <sup>2</sup> C bus electrical characteristics            | 22 |

| 3.2   | Register map7                      | 10    | Design considerations                                      | 22 |

| 4     | Power supply sequence10            | 10.1  | Power on sequence                                          |    |

| 5     | Autobias functionality11           | 10.2  | Programming guidelines to avoid hardwar                    |    |

| 5.1   | General overview11                 |       | failure or damage                                          |    |

| 5.2   | Operational overview11             | 10.3  | Group programming                                          |    |

| 5.3   | Tx enable control12                | 11    | Product marking                                            |    |

| 5.4   | Sense DAC12                        | 12    | Package information                                        |    |

| 5.5   | VGS DAC13                          | 13    | Product software and tools                                 |    |

| 5.6   | Engineering Mode (EM)13            | 14    | Failure analysis                                           |    |

| 6     | Ordering information13             | 15    | Revision history                                           |    |

# 1 Pinout configuration and function

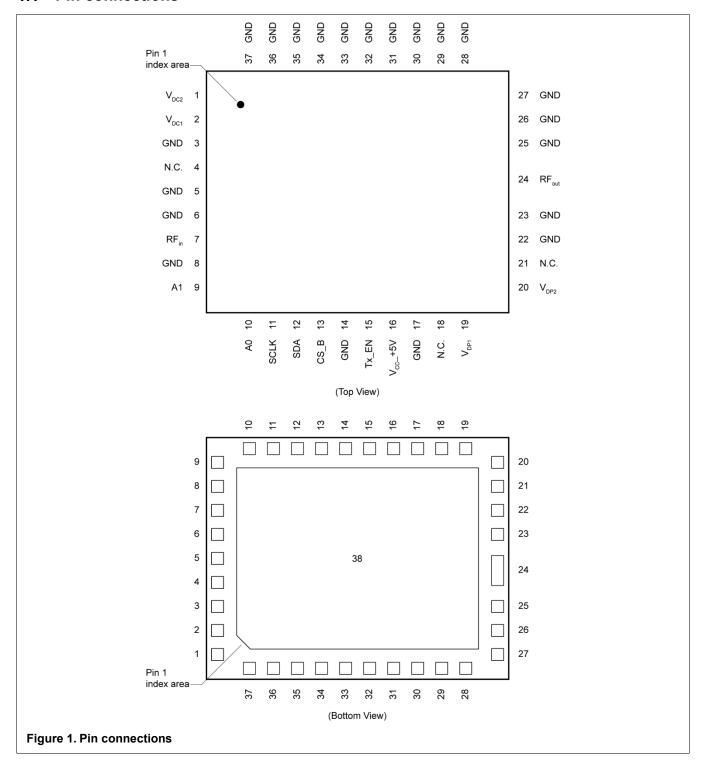

## 1.1 Pin connections

Data Sheet: Technical Data 3 / 33

# 1.2 Functional pin description

Table 1. Functional pin description

| Pin Number                                                                         | Pin Function         | Pin Description                                                                      |

|------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------|

| 1                                                                                  | V <sub>DC2</sub>     | Carrier Drain Supply, Stage 2                                                        |

| 2                                                                                  | V <sub>DC1</sub>     | Carrier Drain Supply, Stage 1                                                        |

| 3, 5, 6, 8, 14, 17, 22, 23, 25, 26, 27, 28, 29, 30, 31, 32, 33, 34, 35, 36, 37, 38 | GND                  | Ground                                                                               |

| 4, 18, 21                                                                          | N.C.                 | No Connection                                                                        |

| 7                                                                                  | RFin                 | RF Input Signal @ 50 Ohm                                                             |

| 9                                                                                  | A1                   | I <sup>2</sup> C Address A1 (tri-state, tie to 5 V, tie to ground or leave floating) |

| 10                                                                                 | A0                   | I <sup>2</sup> C Address A0 (tri-state, tie to 5 V, tie to ground or leave floating) |

| 11                                                                                 | SCLK                 | SPI/I <sup>2</sup> C Serial Clock Signal (1.8 V JEDEC compatible)                    |

| 12                                                                                 | SDA                  | SPI/I <sup>2</sup> C Serial Data Signal (1.8 V JEDEC compatible)                     |

| 13                                                                                 | CS_B                 | Chip Selection Bar for SPI (1.8 V JEDEC compatible)                                  |

| 15                                                                                 | Tx_EN                | PA Enable Signal (1.8 V JEDEC compatible)                                            |

| 16                                                                                 | V <sub>CC</sub> _+5V | 5 V Vcc Power Source for Autobias Chip                                               |

| 19                                                                                 | V <sub>DP1</sub>     | Peaking Drain Supply, Stage 1                                                        |

| 20                                                                                 | V <sub>DP2</sub>     | Peaking Drain Supply, Stage 2                                                        |

| 24                                                                                 | RFout                | RF Output Signal @ 50 Ohm                                                            |

## 2 Electrical characteristics

# 2.1 Ratings

## 2.1.1 Maximum ratings

Table 2. Maximum ratings

| Rating                                                              | Symbol                          | Value        | Unit |

|---------------------------------------------------------------------|---------------------------------|--------------|------|

| Operating Voltage Range                                             | Vcc_+5V                         | 4.75 to 5.25 | Vdc  |

| Operating Voltage Range                                             | $V_{DD}$                        | 24 to 30     | Vdc  |

| Operating Voltage Range                                             | A1, A0                          | 4.75 to 5.25 | Vdc  |

| Operating Voltage Range                                             | CS_B,<br>SDA,<br>SCLK,<br>Tx_EN | 1.65 to 1.95 | Vdc  |

| Storage Temperature Range                                           | T <sub>stg</sub>                | -65 to +150  | °C   |

| Case Operating Temperature                                          | Tc                              | 125          | °C   |

| Peak Input Power (3840 MHz, Pulsed CW, 10 µsec(on), 10% Duty Cycle) | Pin                             | 25           | dBm  |

Data Sheet: Technical Data 4 / 33

### 2.1.2 Lifetime

### Table 3. Lifetime

| Characteristic                                                                                                  | Symbol | Value | Unit  |

|-----------------------------------------------------------------------------------------------------------------|--------|-------|-------|

| Mean Time to Failure Case Temperature 125°C, Internal Sense Temperature 108°C, 8 W Avg., 75% Duty Cycle, 30 Vdc | MTTF   | >10   | Years |

## 2.1.3 ESD protection characteristics

### Table 4. Lifetime ESD protection characteristics

| Test Methodology                      | Class |

|---------------------------------------|-------|

| Human Body Model (per JS-001-2017)    | 3A    |

| Charge Device Model (per JS-002-2014) | C3    |

## 2.1.4 Moisture sensitivity level

### Table 5. Moisture sensitivity level

| Test Methodology                     | Rating | Package Peak Temperature | Unit |

|--------------------------------------|--------|--------------------------|------|

| Per JESD22-A113, IPC/JEDEC J-STD-020 | 3      | 260                      | Ô    |

# 2.2 Operating characteristics

## 2.2.1 Nominal DAC settings

Table 6. Nominal DAC settings<sup>1</sup>

| Characteristic                                                                      | Symbol            | Тур | Unit |

|-------------------------------------------------------------------------------------|-------------------|-----|------|

| Gate Quiescent DAC (V <sub>DS</sub> = 30 Vdc, A_SENSE_DAC = 40, A_VGS1_DAC = 6)     | I <sub>DQ1C</sub> | 26  | mA   |

| Gate Quiescent DAC<br>(V <sub>DS</sub> = 30 Vdc, A_SENSE_DAC = 40, A_VGS2_DAC = 34) | I <sub>DQ2C</sub> | 77  | mA   |

| Gate Quiescent DAC<br>(V <sub>DS</sub> = 30 Vdc, B_SENSE_DAC = 34, B_VGS1_DAC = 60) | I <sub>DQ1P</sub> | 1   | mA   |

| Gate Quiescent DAC (V <sub>DS</sub> = 30 Vdc, B_SENSE_DAC = 34, B_VGS2_DAC = 67)    | I <sub>DQ2P</sub> | 1   | mA   |

<sup>1.</sup> Each side of device measured separately.

Data Sheet: Technical Data 5 / 33

### 2.2.2 Functional tests

**Table 7. Functional tests**

| Characteristic                                                                                                                                                                                                                                      | Symbol                         | Min  | Тур       | Max | Unit |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------|-----------|-----|------|--|--|--|

| <b>Functional Tests</b> — <b>3700 MHz</b> <sup>1</sup> (In NXP Doherty Production ATE <sup>2</sup> Test Fixture, 50 ohm system) V <sub>DD</sub> = 30 Vdc, Nominal DAC Settings, Tx_EN = High, P <sub>out</sub> = 8 W Avg., 1-tone CW, f = 3700 MHz. |                                |      |           |     |      |  |  |  |

| Gain                                                                                                                                                                                                                                                | G 26.0 28.3                    |      |           |     |      |  |  |  |

| Drain Efficiency                                                                                                                                                                                                                                    | η <sub>D</sub>                 | 29.0 | 34.3      | _   | %    |  |  |  |

| Pout @ 3 dB Compression Point                                                                                                                                                                                                                       | P3dB                           | 45.8 | 15.8 47.0 |     | dBm  |  |  |  |

| <b>Functional Tests</b> — <b>3980 MHz¹</b> (In NXP Doherty Production ATE² Test Fixture, 50 ohm system) V <sub>DD</sub> = 30 Vdc, Nominal DAC Settings, Tx EN = High, P <sub>out</sub> = 8 W Avg., 1-tone CW, f = 3980 MHz.                         |                                |      |           |     |      |  |  |  |

| Gain                                                                                                                                                                                                                                                | G                              | 25.5 | 27.6      |     | dB   |  |  |  |

| Drain Efficiency                                                                                                                                                                                                                                    | ficiency η <sub>D</sub> 28.0 3 |      |           |     |      |  |  |  |

| Pout @ 3 dB Compression Point                                                                                                                                                                                                                       | P3dB                           | 45.8 | 47.0      | _   | dBm  |  |  |  |

## 2.2.3 Wideband ruggedness

## Table 8. Wideband ruggedness

| Characteristic                                                                                                                                                                                                         | Symbol | Min | Тур | Max | Unit |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----|-----|-----|------|--|--|

| <b>Wideband Ruggedness</b> <sup>3</sup> (In NXP Doherty Power Amplifier Module Reference Circuit, 50 ohm system) Nominal DAC Settings, Tx_EN = High, f = 3840 MHz, Additive White Gaussian Noise (AWGN) with 10 dB PAR |        |     |     |     |      |  |  |

| ISBW of 400 MHz at 30 Vdc, 3 dB Input Overdrive from 8 W  Avg. Modulated Output Power  No Device Degradation                                                                                                           |        |     |     |     |      |  |  |

## 2.2.4 Typical performance

### Table 9. Typical performance

| Characteristic                                                                                                                                   | Symbol         | Min           | Тур         | Max                      | Unit      |

|--------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|-------------|--------------------------|-----------|

| <b>Typical Performance</b> <sup>3</sup> (In NXP Doherty Power Amplifier Module DAC Settings, Tx_EN = High, P <sub>out</sub> = 8 W Avg., 3840 MHz | e Reference C  | ircuit, 50 oh | m system) \ | / <sub>DD</sub> = 30 Vdc | , Nominal |

| VBW Resonance Point, 2-tone, 1 MHz Tone Spacing (IMD Third Order Intermodulation Inflection Point)                                               | _              | 280           | _           | MHz                      |           |

| 1-carrier 20 MHz LTE, 8 dB Input Signal PAR                                                                                                      |                |               |             |                          |           |

| Gain                                                                                                                                             | G              | _             | 28.0        | _                        | dB        |

| Power Added Efficiency                                                                                                                           | PAE            | _             | 34.0        | _                        | %         |

| Adjacent Channel Power Ratio                                                                                                                     | ACPR           | _             | -35.0       | _                        | dBc       |

| Adjacent Channel Power Ratio                                                                                                                     | ALT1           | _             | -44.4       | _                        | dBc       |

| Adjacent Channel Power Ratio                                                                                                                     | ALT2           | _             | -51.5       | _                        | dBc       |

| Gain Flatness <sup>4</sup>                                                                                                                       | G <sub>F</sub> | _             | 0.7         | _                        | dB        |

| Fast CW, 27 ms Sweep                                                                                                                             |                |               |             | •                        |           |

| Pout @ 3 dB Compression Point                                                                                                                    | P3dB           | _             | 47.0        | _                        | dBm       |

| AM/PM @ P3dB                                                                                                                                     | Φ              | _             | -20         | _                        | 0         |

| Gain Variation @ Avg. Power over Temperature (–40°C to +105°C)                                                                                   | ΔG             | _             | 0.035       | _                        | dB/°C     |

| P3dB Variation over Temperature (–40°C to +105°C)                                                                                                | P3dB           |               | 0.013       | _                        | dB/°C     |

- 1. Part input and output matched to 50 ohms.

- 2. ATE is a socketed test environment.

- All data measured in fixture with device soldered in NXP reference circuit.

- 4. Gain flatness =  $Max(G(f_{Low} \text{ to } f_{High})) Min(G(f_{Low} \text{ to } f_{High}))$

### Register map and OTP memory 3

### One-time programmable memory

The A3M39SL039 contains a one-time programmable (OTP) memory array that is used to store register values for the integrated autobias controller. The data sheet IDQ target values are determined and programmed into the OTP memory during NXP's production testing. When programmed, the OTP memory is used to store these values for automatic loading into autobias registers at power on or reset. These values can be overwritten using the Engineering Mode (EM) sequence; however, the overwritten values do not persist after a power cycle or a reset.

The OTP memory can be programmed only by NXP during the manufacturing process and cannot be changed by the user. The values in OTP memory have been selected to allow the device to operate in a wide variety of applications.

#### Register map 3.2

There are nine 8-bit user accessible registers available in the A3M39SL039. The register mapping is listed in Table 10. Address 0 RW register is designed to control soft reset, refresh OTP and read the chip version. Address 1-6 registers are RW and/or OTP controlled and provide settings for the two RF transistor group DACs. Address 15 is read only for temperature sense functionality. Address 17 is a virtual write only register for enabling Engineering Mode.

7 / 33 Data Sheet: Technical Data

Table 10. Register map

| Address      | Register            | Register    |                                    |                              | Reg                                        | ister De | efinition | 1            |           |           | Default   |

|--------------|---------------------|-------------|------------------------------------|------------------------------|--------------------------------------------|----------|-----------|--------------|-----------|-----------|-----------|

| (in Decimal) |                     | Name        | bit7                               | bit6                         | bit5                                       | bit4     | bit3      | bit2         | bit1      | bit0      | Value     |

| 0            | RW                  | System_Reg  | N/A                                | Soft<br>Reset                | Refresh OTP Chip Version [3:0] (Read only) |          | Read      | 8'b0000_0001 |           |           |           |

| 1            | OTP<br>COPY<br>(RW) | A_Sense_DAC | Res                                | Group A Sense DAC            |                                            |          |           |              |           | OTP value |           |

| 2            | OTP<br>COPY<br>(RW) | A_VGS1_DAC  |                                    | Group A V <sub>GS1</sub> DAC |                                            |          |           |              |           |           | OTP value |

| 3            | OTP<br>COPY<br>(RW) | A_VGS2_DAC  | Group A V <sub>GS2</sub> DAC OTP v |                              | Group A V <sub>GS2</sub> DAC               |          |           |              |           |           | OTP value |

| 4            | OTP<br>COPY<br>(RW) | B_Sense_DAC | Res                                | Reserved Group B Sense DAC   |                                            |          |           |              | OTP value |           |           |

| 5            | OTP<br>COPY<br>(RW) | B_VGS3_DAC  |                                    | Group B V <sub>GS3</sub> DAC |                                            |          |           |              |           | OTP value |           |

| 6            | OTP<br>COPY<br>(RW) | B_VGS4_DAC  |                                    | Group B V <sub>GS4</sub> DAC |                                            |          |           |              |           | OTP value |           |

| 7–14         | _                   | _           |                                    | Reserved                     |                                            |          |           |              |           |           | _         |

| 15           | RO                  | Temp_ADC    | Temperature Sensor [7:0]           |                              |                                            |          |           |              | _         |           |           |

| 16           | _                   | _           | Reserved                           |                              |                                            |          |           |              |           | _         |           |

| 17           | Virtual W<br>only   | EM_Passcode |                                    | Engi                         | neering M                                  | ode (EN  | l) passo  | ode 8'h      | E3        |           | _         |

Read Only register (RO)

Read Write register (RW)

Read Write register with OTP overwrite at Startup (RW)

Reserved non-accessible register

Write Only register

Data Sheet: Technical Data 8 / 33

Table 11. Register overview and bit description

| Address | Register<br>Name | Bit | Bit Descriptions                                                                                                                                                                                                                                                                                         | Power<br>On/Reset<br>Value <sup>1</sup> | Overwritten by OTP | Attribute       | EM<br>Mode |

|---------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------|-----------------|------------|

| 0       | System_Reg       | 7   |                                                                                                                                                                                                                                                                                                          |                                         | N/A                | N/A             | N/A        |

|         |                  | 6   | Soft Reset. A 1 written to this register will perform a reset of all registers to their default values. A 0 should be written after the reset operation is completed.                                                                                                                                    | 0                                       | No                 | RW              |            |

|         |                  | 5   | Refresh OTP. A 1 written to this register will overwrite values stored in OTP into registers identified in the "Overwritten by OTP" column. A 0 should be written after the reset operation is completed.                                                                                                | 0                                       | No                 |                 |            |

|         |                  | 4   | Not available                                                                                                                                                                                                                                                                                            | N/A                                     | N/A                | N/A             |            |

|         |                  | 0–3 | Chip version bits. Inserted by NXP to provide revision information. Cannot be changed.                                                                                                                                                                                                                   | N/A                                     | No                 | R               |            |

| 1       | A_Sense_DAC      | 6–7 | Not available                                                                                                                                                                                                                                                                                            | N/A                                     | N/A                | N/A             |            |

|         |                  | 0–5 | Sense DAC A 6-bit logic value for carrier amplifiers. DAC A sets the reference voltage to compare to the V <sub>DS</sub> across the reference device. Minimum typical value is 6'b001000 and maximum value is 6'b111111. Recommendation is that the value in this register be set higher than 6'b010000. | 6'h20                                   | Yes                | RW <sup>2</sup> | Yes        |

| 2       | A_VGS1_DAC       | 0–7 | Sets 8-bit DAC logic value for carrier amplifier driver stage. 8'h00 sets gate to equal ceiling voltage. 8'hFF reduces gate voltage by a max value.                                                                                                                                                      | 8'h80                                   |                    |                 |            |

| 3       | A_VGS2_DAC       | 0–7 | Sets 8-bit DAC logic value for carrier amplifier final stage. 8'h00 sets gate to equal ceiling voltage. 8'hFF reduces gate voltage by a max value.                                                                                                                                                       | 8'h80                                   |                    |                 |            |

(continued)

Table 11. Register overview and bit description (continued)

| Address | Register<br>Name | Bit | Bit Descriptions                                                                                                                                                                                                                                                                                         | Power<br>On/Reset<br>Value <sup>1</sup>                                                            | Overwritten by OTP | Attribute       | EM<br>Mode |

|---------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------------|-----------------|------------|

| 4       | B_Sense_DAC      | 6–7 | Not available                                                                                                                                                                                                                                                                                            | N/A                                                                                                | N/A                | N/A             | No         |

|         |                  | 0–5 | Sense DAC B 6-bit logic value for peaking amplifiers. DAC B sets the reference voltage to compare to the V <sub>DS</sub> across the reference device. Minimum typical value is 6'b001000 and maximum value is 6'b111111. Recommendation is that the value in this register be set higher than 6'b010000. | 6'h20                                                                                              | Yes                | RW <sup>2</sup> | Yes        |

| 5       | B_VGS3_DAC       | 0–7 | Sets 8-bit DAC logic value for peaking driver stage. 8'h00 sets gate to equal ceiling voltage. 8'hFF reduces gate voltage by a max value.                                                                                                                                                                | aking driver stage. 8'h00 sets gate<br>equal ceiling voltage. 8'hFF<br>luces gate voltage by a max |                    |                 |            |

| 6       | B_VGS4_DAC       | 0–7 | Sets 8-bit DAC logic value for peaking final stage. 8'h00 sets gate to equal ceiling voltage. 8'hFF reduces gate voltage by a max value.                                                                                                                                                                 | 8'h80                                                                                              |                    |                 |            |

| 7–14    | Reserved         | N/A | Not available                                                                                                                                                                                                                                                                                            | N/A                                                                                                | N/A                | N/A             | No         |

| 15      | Temp_ADC         | 0–7 | Temperature sensor 8-bit DAC value. 8'h00 is lowest temperature, 8'hFF is highest temperature.                                                                                                                                                                                                           | 8'h00                                                                                              | No                 | R               | No         |

| 16      | Reserved         | N/A | Not available                                                                                                                                                                                                                                                                                            | N/A                                                                                                | N/A                | N/A             | No         |

| 17      | EM_Passcode      | 0-7 | Engineering Mode (EM). By writing 8'hE3 to this register the user can enter engineering mode. EM can be cleared by writing any other code to this register. In EM registers identified in EM mode column can be changed.                                                                                 | N/A                                                                                                | No                 | W               | Yes        |

At power on or reset, OTP values set by NXP are automatically loaded into registers indicated with a "Yes" in the "Overwritten by OTP" column. For these registers, values shown in the "Power On/Reset Value column" will be loaded only if OTP has not been programmed to prevent damage to the device.

### Power supply sequence 4

Power Up Sequence

- V<sub>CC</sub>\_+5V: 5 V power up

- SPI/I<sup>2</sup>C interface is active

- 3.  $V_{DP1}, V_{DP2}, V_{DC1}, V_{DC2}$  power up

Data Sheet: Technical Data 10 / 33

Register can be read at any time. Can write to register only when in Engineering Mode (EM).

### Power Down Sequence

- V<sub>DP1</sub>, V<sub>DP2</sub>, V<sub>DC1</sub>, V<sub>DC2</sub> power down

- SPI/I<sup>2</sup>C interface deactivated

- V<sub>CC</sub> +5V: 5 V power down

Note: All digital interfaces (SDA, SCLK, CS\_B,Tx\_EN) are 1.8 V logic.

### **Autobias functionality** 5

#### 5.1 General overview

After power up, the integrated bias controller develops and applies a thermally compensated quiescent bias voltage to the gate of each of the four RF transistors contained within the power amplifier module (PAM) based on the preset OTP values. See Section 3.1 for more information on the OTP memory. This achieves optimal RF performance over the full temperature range. The standard SPI or I<sup>2</sup>C interface can be used to read the temperature sensor and overwrite preset DAC values. The device can be used without the programming interface. The thermal compensation circuit is analog and not programmable; however, the preset DAC values can be overwritten to provide an alternate thermal compensation scheme via the SPI or I<sup>2</sup>C interface. This section describes the operation and programming of the bias controller.

### 5.2 Operational overview

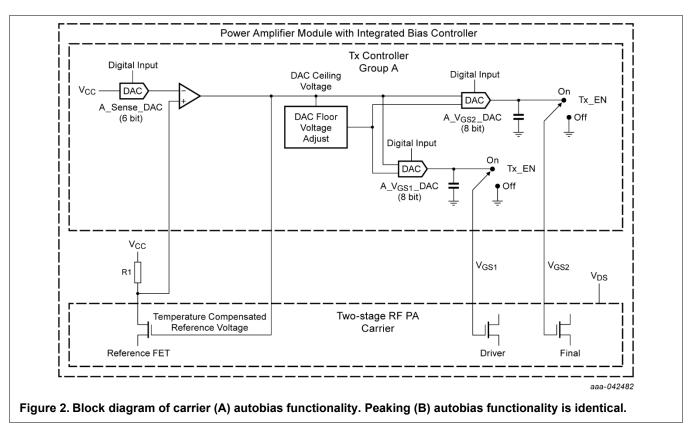

Figure 2 shows a detailed view of the carrier side (Group A) autobias controller. The peaking side (Group B) controller is a duplicate of the carrier; however, the RF transistor peripheries and quiescent operating points will be different as required by the Doherty operation. The module contains four RF LDMOS field-effect transistors (FET) consisting of a driver and final for the carrier amplifier (on a single IC die) and a driver and final for the peaking amplifier (on a single IC die). Each IC die also contains a small periphery reference FET that is designed to match the properties of the larger RF transistors with regard to part-to-part process and temperature-dependent variations. The bias controller interfaces with each of the RF FETs and provides flexibility to control the biasing of each transistor independently.

The bias controller operates by establishing a known current through the reference FET typically in the range of 1-2 mA per reference FET. This in turn establishes a gate-source operating voltage by sensing the voltage drop across an integrated, high tolerance resistor placed between Vcc (5 V) and the reference device drain terminal. The bias controller Vcc +5V pin should be operated from a 5 V supply with tolerance of ±5%. The reference voltage across the precision resistor R1 is compared to a voltage programmed in the bias controller (A Sense DAC and B Sense DAC), thereby providing fine incremental adjustment to the default bias current of the reference FET. Because the reference FET and RF FET are manufactured on the same die in close proximity, they exhibit similar process and temperature dependencies.

Data Sheet: Technical Data 11 / 33

The initial bias condition is set via the A Sense DAC register. The bias condition is then sensed and adjusted as temperature changes via the closed-loop feedback. The feedback mechanism adjusts the DAC ceiling voltage to maintain a constant IDS current through the reference FET. The temperature compensated DAC ceiling voltage can either be passed to the carrier PA final and carrier PA driver directly, or reduced by values set in the A VGS1 DAC and A VGS2 DAC to the DAC floor voltage.

#### 5.3 Tx enable control

A 1.8 V JEDEC compliant enable signal (Tx EN) is included for bias On/Off operation to support TDD operation. The controller provides capability to quickly switch the RF FETs between ON and OFF modes in less than 100 ns. With Tx EN in an ON state, the RF FET gate terminals are internally decoupled with sufficient capacitance providing a low impedance for wide baseband signals. The large capacitance also serves as a charge holding cap for reducing switching transient time in TDD operation. In Tx OFF mode, RF FET device gates are grounded shutting them OFF.

Table 12. TX EN Off-State Typical Currents

| Characteristic                                                                                              | Typical Value | Unit |

|-------------------------------------------------------------------------------------------------------------|---------------|------|

| V <sub>CC</sub> _+5V Supply Current                                                                         | 11            | mA   |

| Combined Drain Supply Currents (V <sub>DC1</sub> , V <sub>DC2</sub> , V <sub>DP1</sub> , V <sub>DP2</sub> ) | 20            | μΑ   |

#### Sense DAC 5.4

The current in the reference FET is controlled and programmed with 6 bits (two MSBs of the 8-bit register are not used) via the sense DAC (A Sense DAC and B Sense DAC). By programming the sense DAC, the RF stage DAC ceiling voltage reference operating point can be optimally set. The DAC ceiling voltage reference point impacts both RF PA stages (driver and final) simultaneously. After OTP has been programmed, the Sense DAC is loaded with the programmed values and are then only programmable in Engineering Mode.

The factory programmed values for A Sense DAC and B Sense DAC are decimal 40 and 34 respectively. These values have been optimized for best power, linearity and efficiency tradeoffs.

A3M39SL039 Airfast Power Amplifier Module with Autobias Control, Rev. 0, March 2022 12 / 33

### 5.5 VGS DAC

The VGS\_DAC voltage is determined via the Sense\_DAC setting, creating the top end or ceiling of the VGS\_DAC voltage range and a fixed offset voltage creating the bottom end or floor of the VGS DAC voltage range. With a decimal VGS DAC setting of 0, the gate voltage developed on the reference FET is buffered with minimum offset to the gates of the RF transistors in the carrier amplifier. As the VGS DAC value increases, the voltage applied to the gates of the RF transistors decreases, which also reduces I<sub>DO</sub>. This allows the operating point of the four RF devices to be set to any desired value, from Class AB to Class C.

The reference FETs and RF FETs exhibit approximately the same current density (that is, IDQ/mm gate width). It is important to note that, because the reference device and RF transistors are manufactured on the same die in close proximity, they exhibit similar process and temperature dependencies. Both the peaking amplifier and the carrier amplifier operate in the same way with regard to the reference device and the RF transistors.

### **Engineering Mode (EM)** 5.6

Flexibility exists to overwrite the OTP memory values, if needed. A special Engineering Mode (EM) is available to allow the user to overwrite data that has been placed into the OTP memory space. To enter EM, issue the write address d'17 command with the predefined EM passcode (see Table 10). After entering EM, all DAC OTP registers (address 1-6) can be overwritten with the normal I<sup>2</sup>C/SPI write instruction. This interface programmed value will be valid so long the V<sub>CC</sub> supply power is maintained. The V<sub>CC</sub> power cycle will load OTP programmed DAC settings again. If the user writes the address d'17 register with any value other than the passcode, EM will automatically exit.

### 6 Ordering information

Table 13. Ordering information

| Device          | Tape and Reel Information                               | Digital<br>Interface | Package             |

|-----------------|---------------------------------------------------------|----------------------|---------------------|

| A3M39SL039IAAT2 | T2 Suffix = 2,000 Units, 24 mm Tape Width, 13-inch Reel | I <sup>2</sup> C     | 10 mm × 8 mm Module |

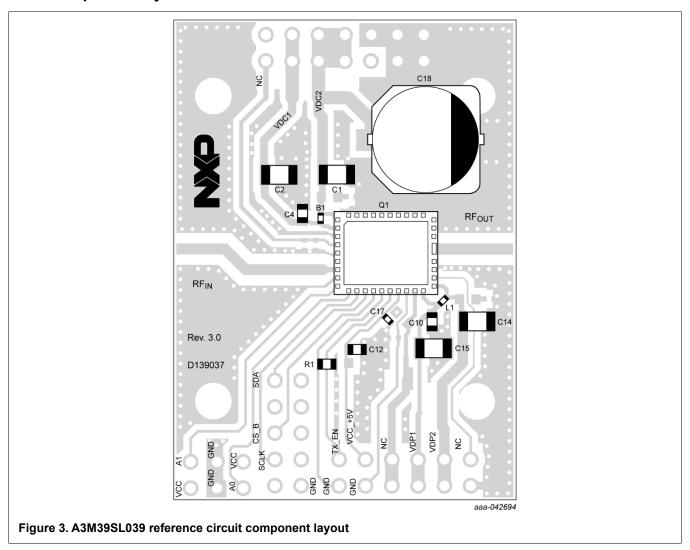

# 7 Component layout and parts list

# 7.1 Component layout

Data Sheet: Technical Data 14 / 33

## 7.2 Component designations and values

Table 14. A3M39SL039 reference circuit component designations and values

| Part             | Description                                   | Part Number        | Manufacturer |

|------------------|-----------------------------------------------|--------------------|--------------|

| B1               | 30 Ω Ferrite Bead                             | BLM15PD300SN1      | Murata       |

| C1, C2, C14, C15 | 10 μF Chip Capacitor                          | GRM31CR61H106KA12  | Murata       |

| C4, C10, C12     | 1 μF Chip Capacitor                           | GRM188R61H105KAAL  | Murata       |

| C17              | 1000 pF Chip Capacitor                        | GRM022R71A102KA12L | Murata       |

| C18              | 220 μF, 50 V Electrolytic Capacitor           | UUJ1H221MNQ1MS     | Nichicon     |

| L1               | 13 nH Chip Inductor                           | LQW15AN13NG80D     | Murata       |

| Q1               | Power Amplifier Module                        | A3M39SL039         | NXP          |

| R1               | 0 Ω, 1/8 W Chip Resistor                      | CRCW08050000Z0EA   | Vishay       |

| PCB              | Rogers RO4350B, 0.020", ε <sub>r</sub> = 3.66 | D139037            | MTL          |

Note: Component numbers C3, C5, C6, C7, C8, C9, C11, C13 and C16 are intentionally omitted.

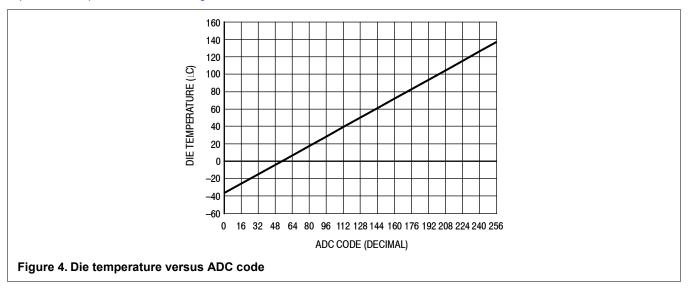

# 8 Temperature sensor

The temperature value is converted from the 8-bit temperature sense ADC value (stored in the Temp\_ADC register) via the following equation.

Temperature (°C) =  $(0.67798 \times Temp\_ADC) - 36.64$

A plot of this equation is shown in Figure 4.

Table 15. Temperature sensor accuracy

| Characteristic                                             | Value | Unit |

|------------------------------------------------------------|-------|------|

| Operating Die Temperature, T <sub>J</sub> = 25°C to 125°C  | ±3    | °C   |

| Operating Die Temperature, T <sub>J</sub> = -35°C to 125°C | ±5    | °C   |

Data Sheet: Technical Data 15 / 33

### **Communication interfaces** 9

The A3M39SL039 device contains a digital interface that supports either a 3-pin SPI or 2-pin I<sup>2</sup>C interface. The digital interface is used to both read and write data to and from the device. The preferred interface type must be set at the factory prior to shipment. For I<sup>2</sup>C functionality, order part number A3M39SL039I. For SPI functionality, order part number A3M39SL039S.

#### SPI 9.1

The A3M39SL039S can be programmed and the Tx bias settings and temperature read through the 3-pin SPI interface.

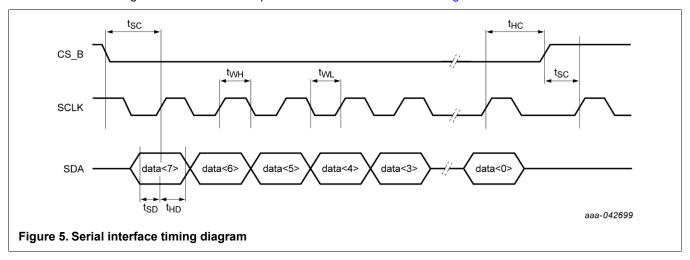

### 9.1.1 SPI timing diagram

The SPI interface timing of A3M39SL039S complies with SPI mode3 as shown in Figure 5.

Table 16. Serial interface timing specification

| Symbol          | Parameter                                                                                         | Min (ns) |

|-----------------|---------------------------------------------------------------------------------------------------|----------|

| tsc             | Setup timing requirement of CS_B (both rising and falling) in relation to the rising edge of SCLK | 50       |

| t <sub>WH</sub> | clk high duration                                                                                 | 160      |

| t <sub>WL</sub> | clk low duration                                                                                  | 160      |

| t <sub>SD</sub> | Date to clock rising edge setup                                                                   | 20       |

| t <sub>HD</sub> | clk rising edge to data hold time                                                                 | 20       |

| t <sub>HC</sub> | clk to CS_B hold time                                                                             | 50       |

| twh + twl       | Minimum clock period                                                                              | 400      |

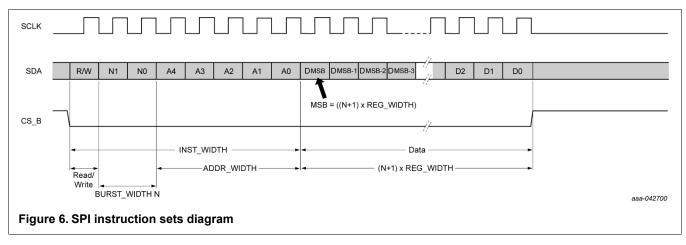

### 9.1.2 SPI instruction set definition

The SPI instruction set is determined by the first byte after releasing the CS\_B signal. The order of SPI instruction is MSB sent first, LSB sent last. Bit 7 of the SPI instruction set is defined as read (1) or write (0) command. Bits 6-5 define the burst width in the range of 1-4 bytes: 00 is for 1 byte data, 01 for 2 bytes data, 10 for 3 bytes data and 11 is for 4 bytes data. Bits 4-0 are defined as the register address that is to be accessed.

Data Sheet: Technical Data

SPI instruction set information:

- R/W read = 1, write = 0

- N1, N0

- o 2'b00 1 byte

- o 2'b01 2 bytes

- o 2'b10 3 bytes

- o 2'b11 4 bytes

- A4, A3, A2, A1, A0 decode for address 0-15

- MSB sent first, LSB last

## 9.2 I<sup>2</sup>C

The A3M39SL039I follows the I<sup>2</sup>C protocol standard. It supports I<sup>2</sup>C fast mode with a bit rate up to 400 Kbit/s. It also supports I<sup>2</sup>C standard mode with bit rate up to 100 Kbit/s.

## 9.2.1 I<sup>2</sup>C addressing

The two external tri-state address pins A0 and A1 use 5 V logic levels and are decoded into 7-bit l<sup>2</sup>C addresses as shown in Table 17. The three LSBs of the 7-bit address are set via the A0 and A1 pins. The four MSBs are the base address, which is fixed at 1000.

Table 17. I<sup>2</sup>C 7-bit address assignment

| <b>A</b> 1 | Α0 | I <sup>2</sup> C 7-Bit Address |

|------------|----|--------------------------------|

| 0          | 0  | Not Translated                 |

| 0          | Z  | 1000 000                       |

| 0          | 1  | 1000 001                       |

| Z          | 0  | 1000 010                       |

| Z          | Z  | 1000 011                       |

| Z          | 1  | 1000 100                       |

| 1          | 0  | 1000 101                       |

| 1          | Z  | 1000 110                       |

| 1          | 1  | 1000 111                       |

Data Sheet: Technical Data 17 / 33

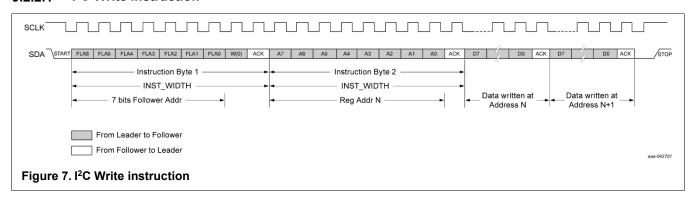

### 9.2.2 I2C instruction set

### 9.2.2.1 I<sup>2</sup>C Write instruction

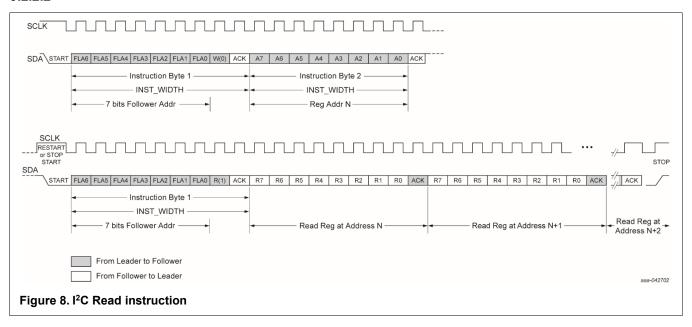

### 9.2.2.2 I<sup>2</sup>C Read instruction

Data Sheet: Technical Data 18 / 33

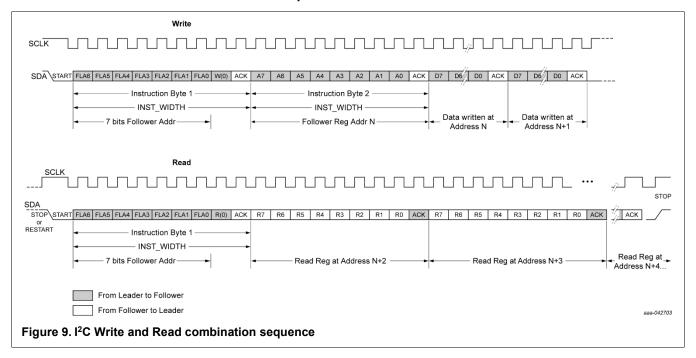

#### 9.2.2.3 I<sup>2</sup>C Write and Read combination sequence

#### 9.2.3 I<sup>2</sup>C Device ID Read instruction

The Device ID is read only, hardwired in the device and can be accessed as follows:

- START condition

- The leader sends the Reserved Device ID I2C bus address followed by the R/W bit set to '0' (write): '1111 1000'.

- The leader sends the I<sup>2</sup>C bus follower address of the follower device it must identify. The LSB is a "don't care" value. Only one device must acknowledge this byte (the device that has the I<sup>2</sup>C bus follower address).

- The leader sends a RESTART condition.

Remark: A STOP condition followed by a START condition resets the follower state machine and the Device ID read cannot be performed. Also, a STOP condition or a RESTART condition followed by an access to another follower device resets the follower state machine and the Device ID read cannot be performed.

- The leader sends the Reserved Device ID I2C bus address followed by the R/W bit set to '1' (read): '1111 1001'.

- The Device ID read can be completed, starting with the 12 manufacturer bits (first byte + four MSBs of the second byte), followed by the nine part identification bits (four LSBs of the second byte + five MSBs of the third byte), and then the three die revision bits (three LSBs of the third byte).

- The leader ends the reading sequence by NACKing the last byte, thus resetting the follower device state machine and allowing the leader to send the STOP condition.

Remark: The reading of the Device ID can be stopped anytime by sending a NACK.

Table 18. I<sup>2</sup>C Device Read instructions

| Leader to<br>Follower | Leader to Follower | Leader to Follower | Leader to Follower | Leader to Follower | Follower to<br>Leader | Leader to Follower | Leader to Follower |

|-----------------------|--------------------|--------------------|--------------------|--------------------|-----------------------|--------------------|--------------------|

| START                 | 1111 1000          | XXXXXXX+'0/1'      | RESTART            | 1111 1001          | 3 bytes ID            | NACK               | STOP               |

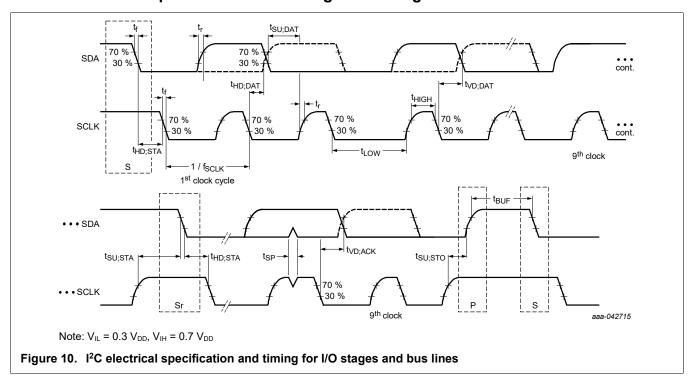

# 9.3 I<sup>2</sup>C electrical specification and timing for I/O stages and bus lines

#### I<sup>2</sup>C SCLK and SDA characteristics 9.3.1

Table 19. I<sup>2</sup>C SCLK and SDA

| Symbol              | Parameter                                                 | Conditions                                             | Min              | Max | Unit |

|---------------------|-----------------------------------------------------------|--------------------------------------------------------|------------------|-----|------|

| f <sub>SCLK</sub>   | SCLK clock frequency                                      | _                                                      | 0                | 400 | kHz  |

| thd;sta             | Hold time (repeated) START condition                      | After this period, the first clock pulse is generated. | 0.6              | _   | μs   |

| t <sub>LOW</sub>    | Low period of the SCLK clock <sup>1</sup>                 | _                                                      | 1.3              | _   | μs   |

| tніgн               | High Period of the SCLK clock                             | _                                                      | 0.6              | _   | μs   |

| t <sub>SU;STA</sub> | Setup time for a repeated START condition                 | _                                                      | 0.6              | _   | μs   |

| 1                   | Data haldina 2                                            | BBUS-compatible masters                                | _                | _   | μs   |

| thd;sta             | Data hold time <sup>2</sup>                               | I <sup>2</sup> C bus devices                           | 0                | _   | μs   |

| t <sub>SU;STA</sub> | Data setup time                                           | _                                                      | 100 <sup>3</sup> | _   | μs   |

| t <sub>r</sub>      | Rise time of both SDA and SCLK signals                    | _                                                      | 20               | 300 | ns   |

| t <sub>f</sub>      | Fall time of both SDA and SCLK signals <sup>4, 5, 6</sup> | _                                                      | 6.5              | 300 | ns   |

| t <sub>SU;STA</sub> | Setup time for STOP condition                             | _                                                      | 0.6              | _   | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition          | _                                                      | 1.3              | _   | μs   |

| t <sub>VD;DAT</sub> | Data valid time <sup>7</sup>                              | _                                                      | _                | 0.9 | μs   |

| t <sub>VD;ACK</sub> | Data valid acknowledge time <sup>6</sup>                  | _                                                      | _                | 0.9 | μs   |

- Note: All values referred to V<sub>IH(min)</sub> (0.3 V<sub>DD</sub>) and V<sub>IL(max)</sub>(0.7 V<sub>DD</sub>) level.

- 2. thd: Dat is the data hold time that is measured from the falling edge of SCLK and applies to data in transmission and the Acknowledge.

- 3. A fast mode I<sup>2</sup>C bus device can be used in a standard mode I<sup>2</sup>C bus system, but the requirement tsu:DAT 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCLK signal. If such a device does not stretch the LOW period of the SCLK signal, it must output the next data bit to the SDA line  $t_{r(max)} + t_{SU;DATA} =$ 1000 + 250 = 1250 ns (according to the Standard Mode I<sup>2</sup>C Bus Specification) before the SCLK line is released. Also the Acknowledge timing must meet this setup time.

- 4. A device must internally provide a hold time of at least 300 ns for the SDA signal (with respect to the VIH(min) of the SCLK signal) to bridge the undefined region of the falling edge of SCLK.

- The maximum t<sub>HD:DAT</sub> could be 3.45 µs and 0.9 µs for standard mode and fast mode, but must be less than the maximum of tvd:dat or tvd:ack by a transition time. This maximum must only be met if the device does not stretch the LOW period (iLOW) of the SCLK signal. If the clock stretches the SCLK, the data must be valid by the setup mode before it releases the clock.

- 6. tvp:ACK = time for Acknowledgement signal from SCLK LOW to SDA output (HIGH or LOW, depending on which one is

- t<sub>VD:DAT</sub> = time for data signal from SCLK LOW to SDA output (HIGH or LOW, depending on which one is longer).

### 9.3.2 I<sup>2</sup>C bus electrical characteristics

Table 20. I2C SCLK and SDA

| Symbol           | Parameter                                                          | Conditions                                                                            | Min                               | Max                              | Unit |

|------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------|----------------------------------|------|

| VIL              | LOW-level input voltage                                            | _                                                                                     | _                                 | 0.3*V <sub>DD</sub> <sup>1</sup> | V    |

| V <sub>IH</sub>  | HIGH-level input voltage                                           | _                                                                                     | 0.7*V <sub>DD</sub> <sup>1</sup>  | _                                | V    |

| V <sub>hys</sub> | Hysteresis of Schmitt trigger inputs                               | _                                                                                     | 0.05*V <sub>DD</sub> <sup>1</sup> | _                                | V    |

| VoL              | LOW-level output voltage                                           | (Open-drain/open-collector) at 2 mA sink current $V_{DD}^1 = < 2 \text{ V}$           | 0                                 | 0.2*V <sub>DD</sub> <sup>1</sup> | V    |

| Vон              | HIGH-level output voltage                                          | (Open-drain/open-collector)                                                           | 0.7*V <sub>DD</sub> <sup>1</sup>  | V <sub>DD</sub> <sup>1</sup>     | V    |

|                  | LOW lovel entent entent                                            | V <sub>OL</sub> = 0.4 V                                                               | 3                                 | _                                | mA   |

| loL              | LOW-level output current                                           | V <sub>OL</sub> = 0.6 V                                                               | 6                                 | _                                | mA   |

| l <sub>iL</sub>  | Input leakage current at the pin                                   | $V_{DD}$ = 1.8, Pin voltage = 1.8 V,<br>0.1 $V_{DD}$ < VI < 0.9 $V_{DD}$ <sup>1</sup> | -10                               | 10                               | μΑ   |

| Ci               | Capacitance for each I/O pin                                       | _                                                                                     | _                                 | 10                               | pF   |

| tsp              | Pulse width of spikes that must be suppressed by the input filter  | _                                                                                     | 0                                 | 50                               | ns   |

| t <sub>of</sub>  | Output fall time from V <sub>IH(min)</sub> to V <sub>IL(max)</sub> | Pullup res = 250 ohm and max allowed load capacitance C <sub>b</sub>                  | _                                 | 250                              | ns   |

| Сь               | Capacitive load for each bus line <sup>2</sup>                     | _                                                                                     |                                   | 400                              | pF   |

<sup>1.</sup>  $V_{DD}$  in this table refers to 1.8 V provided by the Leader.

# 10 Design considerations

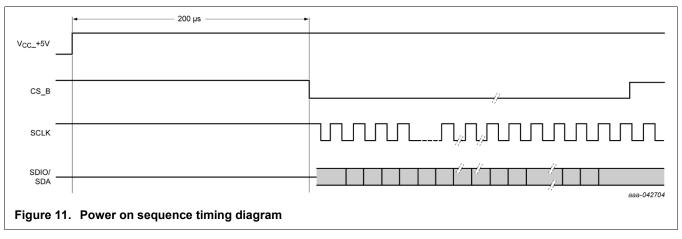

## 10.1 Power on sequence

The initial power on sequence will take approximately 200 µs to complete the OTP memory fetching process. Therefore, it is suggested to wait at least 200 µs before issuing the SPI or I2C read and write processes. The normal SPI or I2C read and write processes should follow the sequence illustrated in Figure 11, "Power on sequence timing diagram."

A3M39SL039 Airfast Power Amplifier Module with Autobias Control, Rev. 0, March 2022 Data Sheet: Technical Data

The maximum tr for the SDA and SCLK bus lines is specified at 300 ns. This allows series protection resistors to be connected in between the SDA and the SCLK pins and the SCLK bus lines without exceeding the maximum specified tr.

## 10.2 Programming guidelines to avoid hardware failure or damage

Users must be aware of the following guidelines to avoid potential hardware failure or damage.

- Do not program the Refresh OTP and Soft Reset bits to a 1 state at the same time.

- · Soft Reset bit will reset Engineering Mode (EM).

- The Soft Reset bit is easily accessible; therefore, be cautious of the accidental reset.

- Tx\_EN must not be active during an OTP refresh or during Engineering Mode.

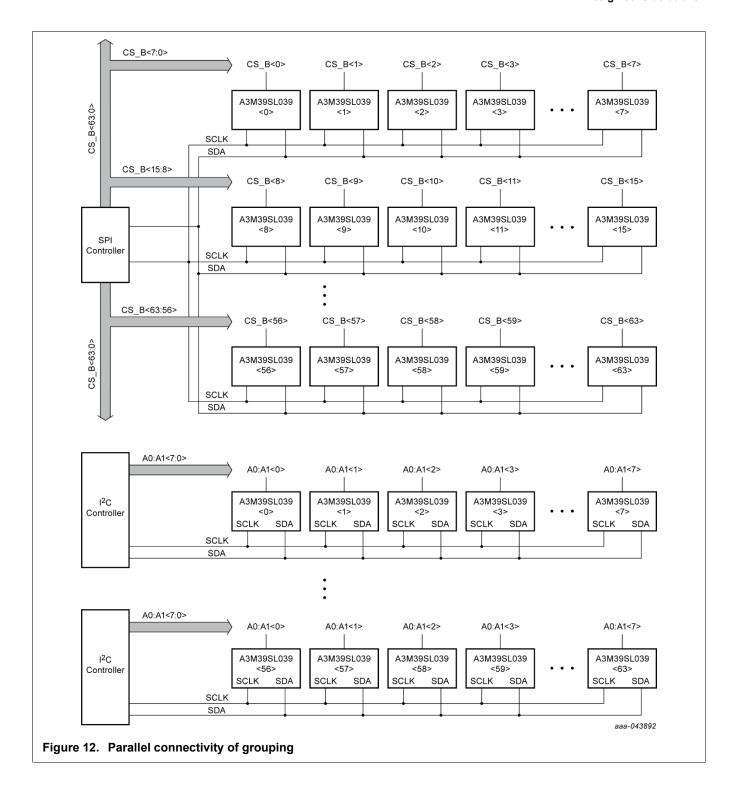

## 10.3 Group programming

A common way of grouping A3M39SL039 modules is with parallel data inputs and unique chip CS B connectivity. In this case, each module can be independently controlled and programmed by its individual CS\_B, which has more flexibility to program each module separately as Figure 12 illustrates.

Data Sheet: Technical Data 24 / 33

# 11 Product marking

Figure 13. Product marking

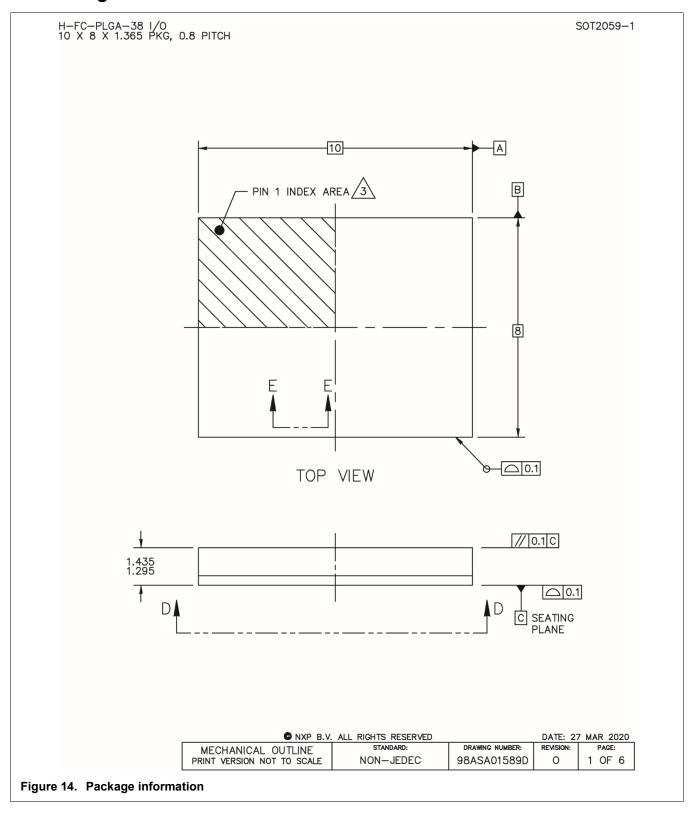

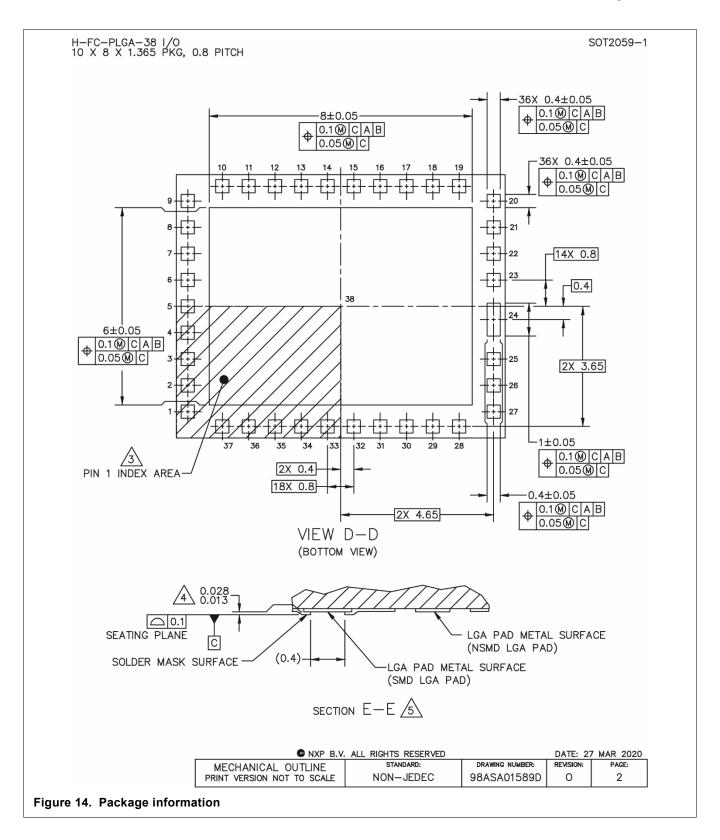

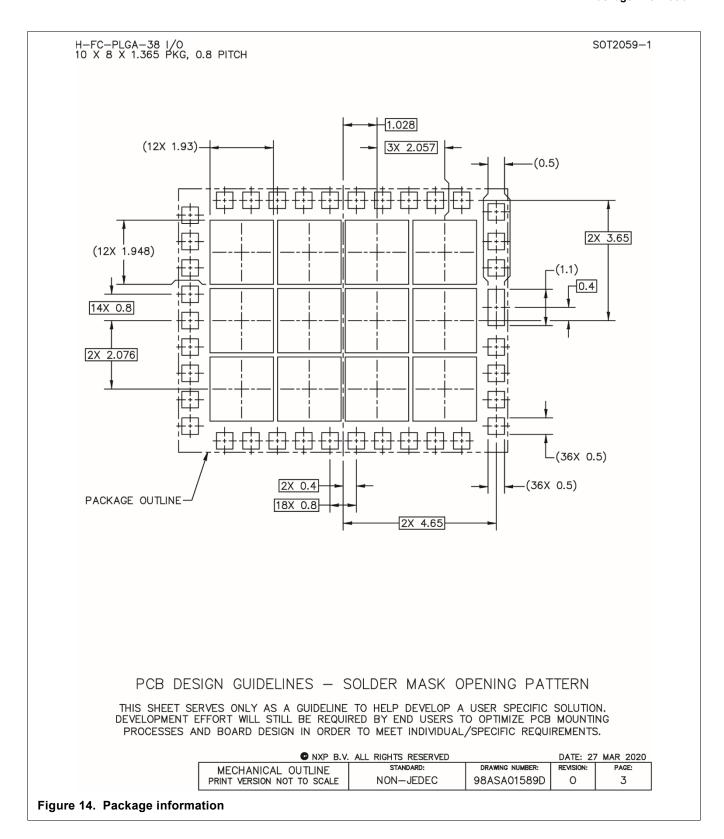

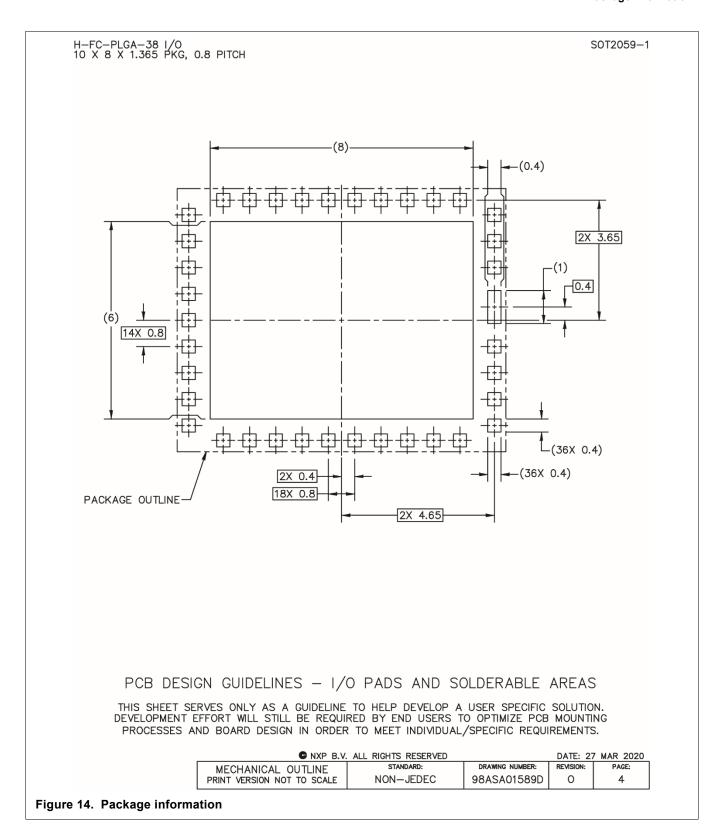

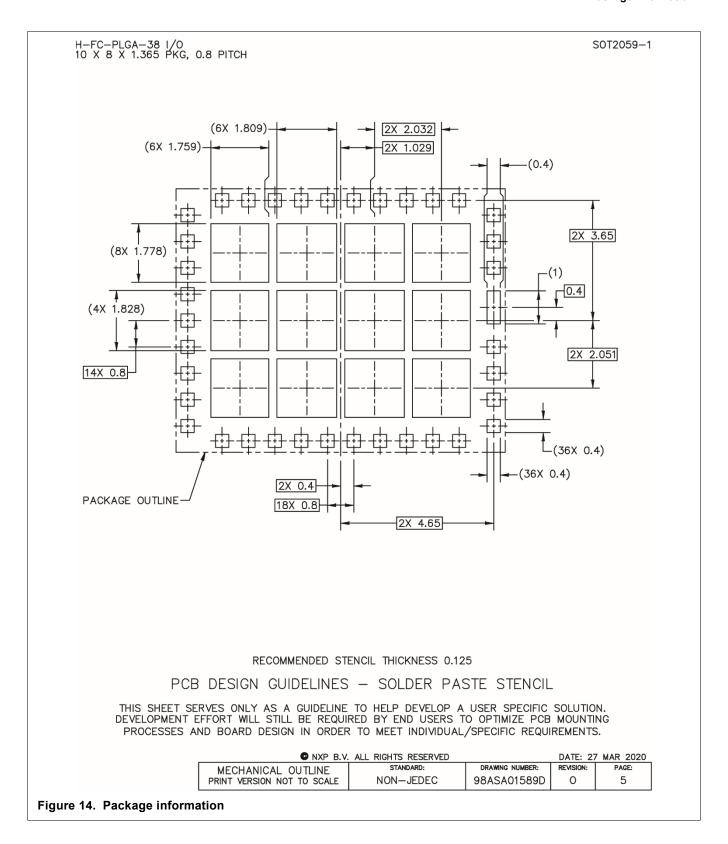

# 12 Package information

Data Sheet: Technical Data 26 / 33

Data Sheet: Technical Data 27 / 33

Data Sheet: Technical Data 28 / 33

Data Sheet: Technical Data 29 / 33

Data Sheet: Technical Data 30 / 33

H-FC-PLGA-38 I/O 10 X 8 X 1.365 PKG, 0.8 PITCH

SOT2059-1

### NOTES:

- 1. ALL DIMENSIONS IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

PIN 1 FEATURE SHAPE, SIZE AND LOCATION MAY VARY.

DIMENSION APPLIES TO ALL LEADS AND FLAG.

THE BOTTOM VIEW SHOWS THE SOLDERABLE AREA OF THE PADS. THE CENTER PAD (PIN 38) IS SOLDER MASK DEFINED. SOME PERIPHERAL PADS ARE SOLDER MASK DEFINED (SMD) AND OTHERS ARE NON-SOLDERMASK DEFINED (NSMD).

O NXP B.V. ALL RIGHTS RESERVED DATE: 27 MAR 2020 DRAWING NUMBER: STANDARD: REVISION: PAGE: MECHANICAL OUTLINE PRINT VERSION NOT TO SCALE NON-JEDEC 98ASA01589D 0 6

Figure 14. Package information

Data Sheet: Technical Data 31 / 33

## 13 Product software and tools

Refer to the following resources to aid your design process.

### **Development Software**

· Test, Debug and Analyzer Software

### **Development Tools**

· Printed Circuit Boards

# 14 Failure analysis

At this time, because of the physical characteristics of the part, failure analysis is limited to electrical signature analysis. In cases where NXP is contractually obligated to perform failure analysis (FA) services, full FA may be performed by third party vendors with moderate success. For updates contact your local NXP Sales Office.

# 15 Revision history

The following table summarizes revisions to this document.

Table 21. Revision history

| Revision | Date      | Description                   |

|----------|-----------|-------------------------------|

| 0        | Mar. 2022 | Initial release of data sheet |

A3M39SL039 Airfast Power Amplifier Module with Autobias Control, Rev. 0, March 2022 Data Sheet: Technical Data 32 / 33

### How to Reach Us

Home Page: nxp.com

Web Support: nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners.

© NXP B.V. 2022

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

> Date of release: March 2022 Document identifier: A3M39SL039