## **BGU8821/A**

# **Dual channel low-noise high linearity amplifier with DSA and SPDT**

Rev. 6 — 15 April 2020

**Product data sheet**

### 1 General description

The BGU8821/A, also known as the BTS5201L/A, is a highly integrated dual channel digitally controlled low noise amplifier (LNA) with digital step attenuator (DSA) and a single-pole double-through (SPDT) switch. The BGU8821/A supports receivers (main and diversity) in both TDD and FDD systems. It has a first stage LNA optimized for sensitivity, followed by a DSA and output stage amplifier. To support highly integrated solutions and reduce platform costs a standalone SPDT switch is included.

The BGU8821/A is optimized for frequency band 700 MHz - 1000 MHz, but supports 452.5 MHz - 457.5 MHz as well.

The BGU8821/A is controlled via SPI bus, supporting both 3- and 4-wire configurations. Additionally, in TDD systems the LNAs and DSA can also be controlled via direct-access pins.

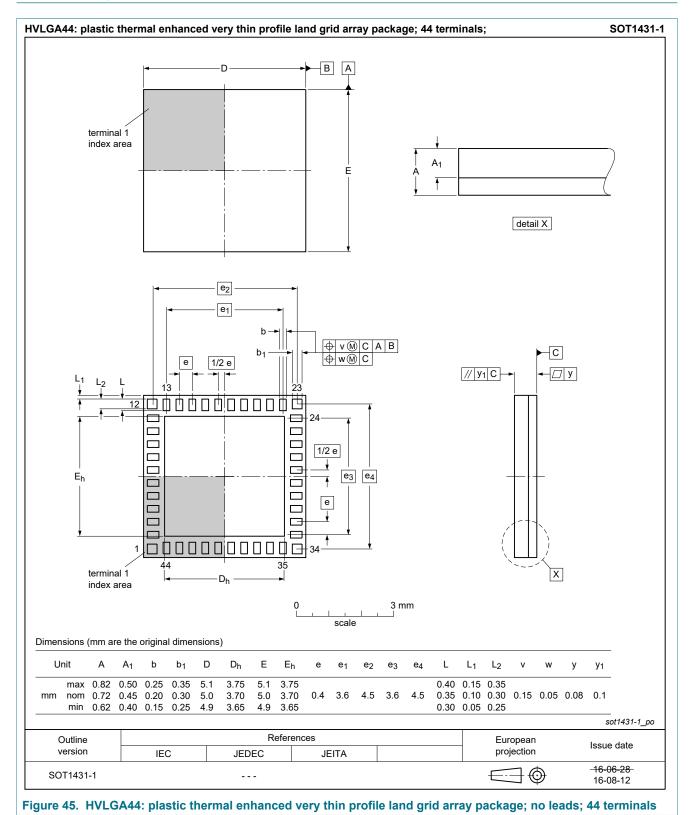

The BGU8821/A is housed in a small footprint (5 mm x 5 mm x 0.72 mm) 44-pin leadless package.

#### 2 Features and benefits

- Dual channel (diversity and main) highly integrated LNA + DSA

- Frequency bands 452.5 MHz 457.5 MHz and 700 MHz 1000 MHz

- Noise figure = 0.6 dB

- High linearity: IP3<sub>O</sub> = 38 dBm

- High input return loss >12 dB

- High output return loss > 12 dB

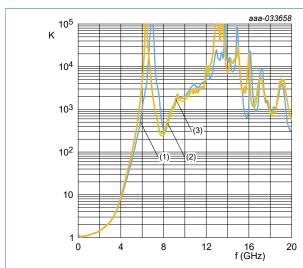

- Unconditionally stable up to 20 GHz

- Digital step attenuator with 31 dB range and 1 dB step

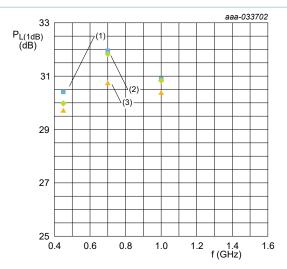

- High linearity SPDT, P<sub>i(1dB)</sub> = 35 dBm, IP3<sub>i</sub> = 50 dBm

- Programmable via 3 wire or 4-wire SPI (Read/write)

- Small 44-terminal leadless package 5 mm × 5 mm × 0.72 mm

- · ESD protection on all terminals

- · Moisture sensitivity level 3

- +5 V single supply

### Dual channel low-noise high linearity amplifier with DSA and SPDT

### 3 Applications

- · Wireless infrastructure

- 5G ready

- · Low noise and high linearity applications

- LTE, W-CDMA, CDMA, GSM

- · General-purpose wireless applications

- TDD or FDD systems

- · Suitable for small cells

#### 4 Quick reference data

#### Table 1. Quick reference data BGU8821/A LNA1

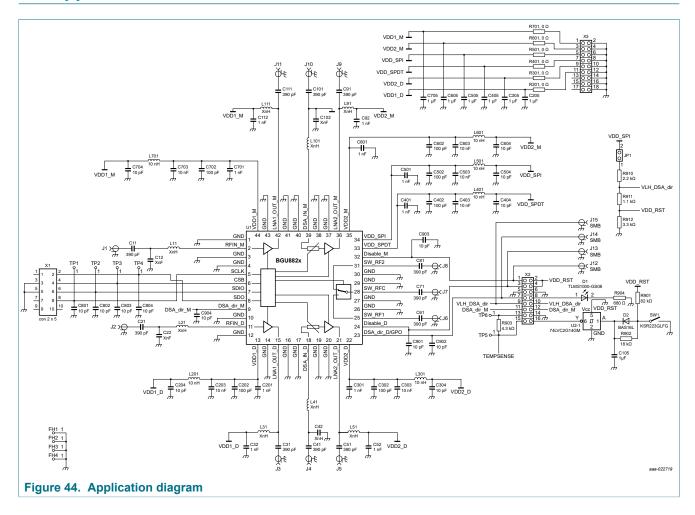

f = 900 MHz;  $V_{CC}$  = 5 V;  $T_{amb}$  = 25 °C; input and output 50  $\Omega$ ; unless otherwise specified. All RF parameters are measured in an application board as shown in Figure 44 with components listed in Table 33 optimized for f = 900 MHz.

| Symbol              | Parameter                             | Conditions                                                         |     | Min  | Тур | Max | Unit |

|---------------------|---------------------------------------|--------------------------------------------------------------------|-----|------|-----|-----|------|

| I <sub>CC</sub>     | supply current                        | LNA1 enable                                                        |     | -    | 54  | 64  | mA   |

|                     |                                       | Disable                                                            |     | -    | 3   | -   | mA   |

| Gp                  | power gain                            |                                                                    | [1] | 15.9 | 19  | -   | dB   |

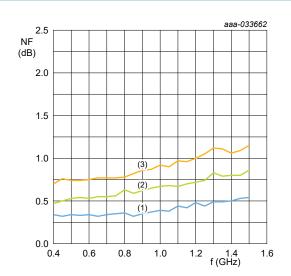

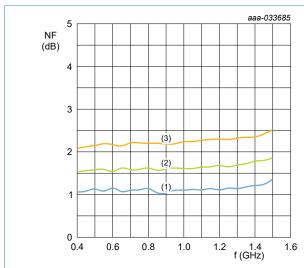

| NF                  | noise figure                          |                                                                    | [1] | -    | 0.6 | -   | dB   |

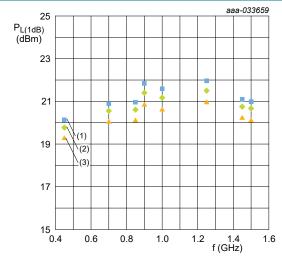

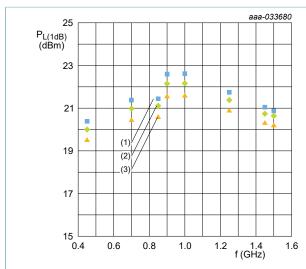

| P <sub>L(1dB)</sub> | output power at 1 dB gain compression |                                                                    | [1] | 17.9 | 21  | -   | dBm  |

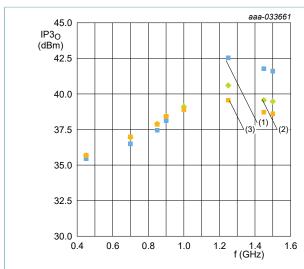

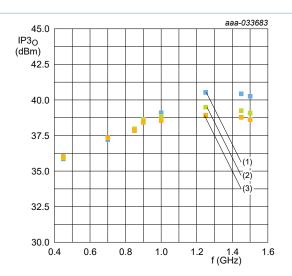

| IP3 <sub>O</sub>    | output third-order intercept point    | 2-tone; tone spacing = 1 MHz;<br>P <sub>i</sub> = -15 dBm per tone | [1] | 34   | 38  | -   | dBm  |

<sup>[1]</sup> Connector and Printed-Circuit Board (PCB) losses have been de-embedded for all RF parameters.

#### Table 2. Quick reference data BGU8821/A DSA+LNA2

f = 900 MHz;  $V_{CC}$  = 5 V;  $T_{amb}$  = 25 °C; input and output 50  $\Omega$ ; unless otherwise specified. All RF parameters are measured in an application board as shown in Figure 44 with components listed in Table 33 optimized for f = 900 MHz

| Symbol              | Parameter                             | Conditions                                                         |     | Min  | Тур | Max | Unit |

|---------------------|---------------------------------------|--------------------------------------------------------------------|-----|------|-----|-----|------|

| I <sub>CC</sub>     | supply current                        | LNA2 enable                                                        |     | -    | 57  | 67  | mA   |

|                     |                                       | Disable                                                            |     | -    | 5   | -   | mA   |

| G <sub>p</sub>      | power gain                            |                                                                    | [1] | 14.5 | 18  | -   | dB   |

| NF                  | noise figure                          |                                                                    | [1] | -    | 1.6 | -   | dB   |

| P <sub>L(1dB)</sub> | output power at 1 dB gain compression |                                                                    | [1] | 18.0 | 22  | -   | dBm  |

| IP3 <sub>O</sub>    | output third-order intercept point    | 2-tone; tone spacing = 1 MHz;<br>P <sub>i</sub> = -15 dBm per tone | [1] | 34   | 39  | -   | dBm  |

<sup>[1]</sup> Connector and Printed-Circuit Board (PCB) losses have been de-embedded for all RF parameters.

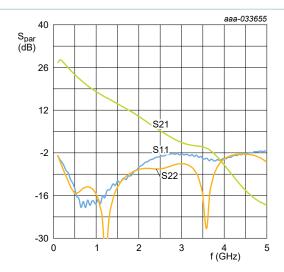

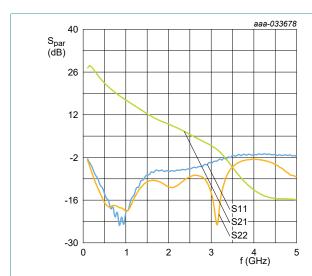

Table 3. Quick reference data BGU8821/A SPDT

f = 900 MHz;  $V_{CC}$  = 5 V;  $T_{amb}$  = 25 °C; input and output 50  $\Omega$ ; unless otherwise specified. All RF parameters are measured in an application board as shown in Figure 44 with components listed in Table 33 optimized for f = 900 MHz

| Symbol                | Parameter                            | Conditions                                                        | Min | Тур | Max | Unit |

|-----------------------|--------------------------------------|-------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>CC</sub>       | supply current                       |                                                                   | -   | 2.1 | -   | mA   |

| $\alpha_{\text{ins}}$ | insertion loss                       | [1]                                                               | -   | 1.3 | 1.6 | dB   |

| RLin                  | input return loss                    | all SPDT                                                          | -   | 17  | -   | dB   |

| P <sub>i(1dB)</sub>   | input power at 1 dB gain compression |                                                                   | -   | 35  | -   | dBm  |

| IP3 <sub>i</sub>      | input third-order intercept point    | 2-tone; tone spacing = 1 MHz;<br>P <sub>i</sub> = +5 dBm per tone | -   | 54  | -   | dBm  |

<sup>[1]</sup> Connector and Printed-Circuit Board (PCB) losses have been de-embedded for all RF parameters.

### 5 Ordering information

Table 4. Table 4. Ordering information

| Type number | Orderable part number | Package |                                                                                                                  |           |

|-------------|-----------------------|---------|------------------------------------------------------------------------------------------------------------------|-----------|

|             |                       | Name    | Description                                                                                                      | Version   |

| BGU8821/A   | BGU8821/AY            | HVLGA44 | plastic thermal enhanced very thin profile land grid array package; no leads; 44 terminals; body 5 × 5 × 0.72 mm | SOT1431-1 |

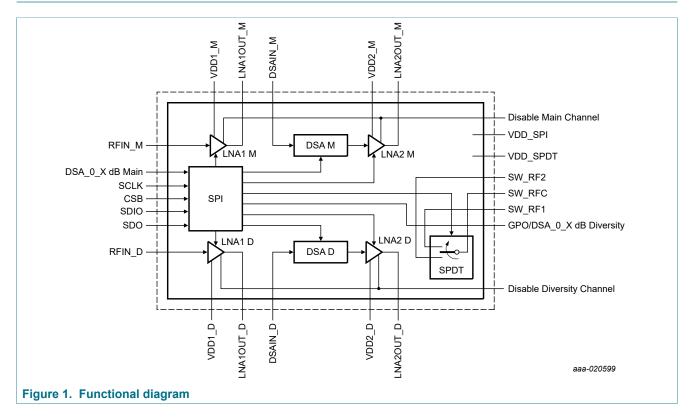

### 6 Functional diagram

BGU8821/A

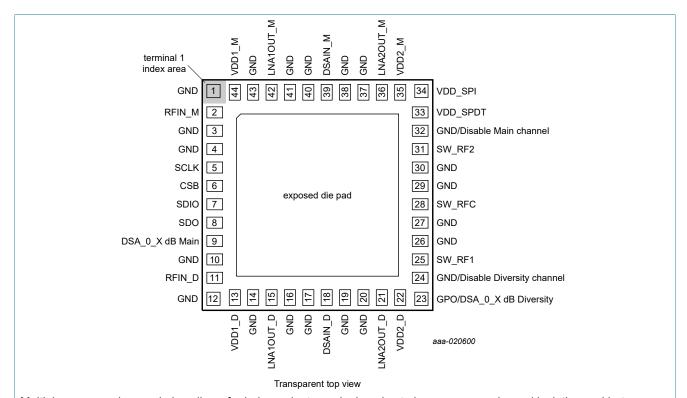

### 7 Pinning information

#### 7.1 Pinning

Multiple power and ground pins allows for independent supply domains to improve cross channel isolation and between blocks in one single channel. In, order to reduce series inductance at all RF ports and RF grounding a small package footprint was chosen.

Figure 2. Pin configuration

#### 7.2 Pin description

Table 5. Pin description

| Symbol          | Pin                                                                           | Description                                                                                                           |

|-----------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| GND             | 1, 3, 4, 10, 12,<br>14,16, 17, 19, 20,<br>26, 27, 29, 30, 37,<br>38,40, 41,43 | Ground                                                                                                                |

| RFIN_M          | 2                                                                             | RF Input to LNA1, main channel. An external DC block is required. External SMD is required for matching.              |

| SCLK            | 5                                                                             | Clock input for SPI                                                                                                   |

| CSB             | 6                                                                             | Chip select active low                                                                                                |

| SDIO            | 7                                                                             | Serial data in/out. Push-Pull pin                                                                                     |

| SDO             | 8                                                                             | Serial data out. Push-Pull pin                                                                                        |

| DSA_0_X dB Main | 9                                                                             | Direct-access DSA setting between minimum attenuation and X dB attenuation programmed prior to TDD mode, main channel |

BGU8821/A

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

### Dual channel low-noise high linearity amplifier with DSA and SPDT

| Symbol                           | Pin             | Description                                                                                                                                                                       |

|----------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RFIN_D                           | 11              | RF Input to LNA1, diversity channel. An external DC block is required. External SMD is required for matching.                                                                     |

| VDD1_D                           | 13              | Supply to LNA1, diversity channel. Decoupling capacitors are required                                                                                                             |

| LNA1OUT_D                        | 15              | RF output of LNA1, diversity channel. An external DC block + BIAS choke are required.                                                                                             |

| DSAIN_D                          | 18              | RF input to DSA, diversity channel. An external DC block + matching SMD are required.                                                                                             |

| LNA2OUT_D                        | 21              | RF output of LNA2, diversity channel. An external DC block + BIAS choke are required.                                                                                             |

| VDD2_D                           | 22              | Supply to LNA2, diversity channel. Decoupling capacitors are required.                                                                                                            |

| GPO/DSA_0_X dB<br>Diversity      | 23              | GPO (General Purpose Output). Leave open when not used. Direct-access DSA setting between minimum attenuation and X dB attenuation programmed prior to TDD mode diversity channel |

| GND/Disable Diversity<br>Channel | 24              | Ground or Disable Diversity Channel                                                                                                                                               |

| SW_RF1                           | 25              | Switch RF path 1. An external DC block is required                                                                                                                                |

| SW_RFC                           | 28              | Switch RF common. An external DC block is required                                                                                                                                |

| SW_RF2                           | 31              | Switch RF path 2. An external DC block is required                                                                                                                                |

| GND/Disable Main<br>Channel      | 32              | Ground or Disable Main Channel                                                                                                                                                    |

| VDD_SPDT                         | 33              | V <sub>DD</sub> into SPDT, decoupling capacitors are required                                                                                                                     |

| VDD_SPI                          | 34              | V <sub>DD</sub> into SPI, decoupling capacitors are required                                                                                                                      |

| VDD2_M                           | 35              | Supply to LNA2, main channel. Decoupling capacitors are required                                                                                                                  |

| LNA2OUT_M                        | 36              | RF output of LNA2, main channel. An external DC block + BIAS choke are required.                                                                                                  |

| DSAIN_M                          | 39              | RF input to DSA, main channel. An external DC block + matching SMD are required.                                                                                                  |

| LNA1OUT_M                        | 42              | RF output from LNA1, main channel. An external DC block + BIAS choke are required.                                                                                                |

| VDD1_M                           | 44              | Supply to LNA2, diversity channel. Decoupling capacitors are required.                                                                                                            |

| GND                              | Exposed die pad | Ground                                                                                                                                                                            |

Dual channel low-noise high linearity amplifier with DSA and SPDT

### 8 Functional description

# 8.1 Direct-Access Functionality for Main and Diversity Channels in TDD Systems

In addition to SPI in TDD systems the LNAs and DSA can also be controlled via direct-access pins. Pins 32 and 24 are used for Direct Disable mode for Main and Diversity channels correspondingly.

Pins 9 and 23 are used for Direct DSA Attenuation mode for Main and Diversity channels correspondingly.

By default, the BGU8821/A starts up in direct-access mode. SPI bus remains fully functional. <VDD\_SPI> pin has to be connected to power supply. Reset command <SPI\_RST> must be applied.

#### 8.1.1 Direct Disable mode

In Direct Disable mode Main and Diversity channels can be disabled independently without accessing SPI bus.

Pin 32 < Disable Main Channel> shall be set to HIGH to disable Main channel (LNA1\_M and LNA2\_M of the Main channel are disabled (set in low current mode).

Pin 24 < Disable Diversity Channel> shall be set to HIGH to disable Diversity channel (LNA1\_D and LNA2\_D of the Diversity channel are disabled (set in low current mode).

VIH voltage for those pins is limited to 2.75 V, as indicated in <u>Table 31</u>.

Direct Disable mode functionality has similar effect as if both LNA1 and LNA2 of Main or Diversity channels have been disabled via LNA Enable bits (register 0x10h, bits [7-6] for Main channel and bits [5-4] for Diversity channel).

#### 8.1.2 Direct DSA Attenuation mode

In Direct DSA Attenuation mode, Main and Diversity DSAs can be toggled independently without accessing SPI bus.

Pin 9 <DSA\_0\_X\_dB Main> can be toggled to set DSA\_M between Minimum Attenuation (level LOW) and predefined X dB attenuation (level HIGH). X dB attenuation is defined in DSA M TDD ATTN (register 0x16h, bits [6-2]). Default reset value is 15 dB.

Table 6. Direct DSA Attenuation mode for Main channel truth table

Legend: \* reset value

| Pin 9           | DIRECT_DSA_M            | DSA_M Attenuation                 | Description                                                                                    |

|-----------------|-------------------------|-----------------------------------|------------------------------------------------------------------------------------------------|

| DSA_0_X dB Main | register 0x13h, bit [1] |                                   |                                                                                                |

| 0               | 0*                      | Min attenuation I <sub>L</sub>    |                                                                                                |

| 1               | 0*                      | I <sub>L</sub> x X dB Attenuation | X dB is set in register 0x16h, default value is 15 dB                                          |

| X               | 1                       | SPI setting                       | DSA_M controlled by SPI using register 0x11h, default value is Min attenuation, I <sub>L</sub> |

Pin 23 <GPO/DSA\_0\_X\_dB Diversity> can be toggled to set DSA\_M between Minimum Attenuation (level LOW) and predefined X dB attenuation (level HIGH). X dB attenuation is defined in DSA\_D\_TDD\_ATTN (register 0x17h, bits [6-2]). Default reset value is 15 dB.

Table 7. Direct DSA Attenuation mode for Diversity channel truth table

Legend: \* reset value

| Pin 23               | DIRECT_DSA_D            | DSA_D Attenuation                 | Description                                                                                    |

|----------------------|-------------------------|-----------------------------------|------------------------------------------------------------------------------------------------|

| DSA_0_X dB Diversity | register 0x13h, bit [2] |                                   |                                                                                                |

| 0                    | 0*                      | Min attenuation I <sub>L</sub>    |                                                                                                |

| 1                    | 0*                      | I <sub>L</sub> x X dB Attenuation | X dB is set in register 0x17h, default value is 15 dB                                          |

| GPO functionality    | 1                       | SPI setting                       | DSA_D controlled by SPI using register 0x12h, default value is Min attenuation, I <sub>L</sub> |

By default, the BGU8821/A starts up in Direct DSA Attenuation mode. This mode can be switched off via register 0x13h, bits [1] (for the Main channel) and [2] (for the Diversity channel). While Direct DSA Attenuation mode for Diversity channel is active, GPO functionality is not available.

When DIRECT\_DSA\_D (register 0x13h bit [2]) is set HIGH, Direct DSA Attenuation mode for Diversity channel is switched off and Pin 23 is used as <GPO> pin.

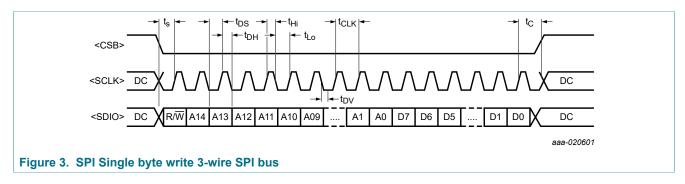

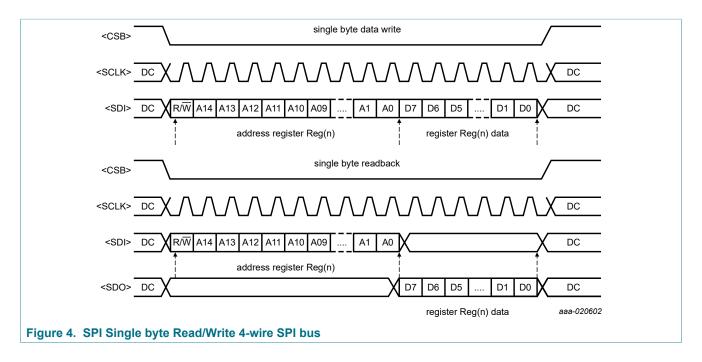

#### 8.2 Serial Peripheral interface (SPI) Bus

The Serial Peripheral Interface (SPI) bus allows simple interfacing with many industry microprocessors; it provides access to all the registers that define the operation of the BGU8821/A.

#### Dual channel low-noise high linearity amplifier with DSA and SPDT

#### 8.2.1 Hardware Interface description

The SPI functionality includes registers and an address decoder to support both read and write operations. Register mapping is organized as a 15-bit address register and an 8-bit data register. In order to avoid register coupling, data should always be sent as an 8-bit sequence.

Register addresses 0x00h - 0x06h, 0x10h - 0x13h, 0x16h - 0x17h and 0x0Ch - 0x0Fh set the operation of the BGU8821/A. Any other address used does not affect the behavior of the device (e.g. device does not stall).

The BGU8821/A supports a 3-wire or 4-wire SPI bus operation mode. <SDIO> is used as a bidirectional pin in 3-wire mode. During the write cycle, it is used as an input pin and during the read cycle as output pin. In 4-wire bus mode, <SDIO> and <SDO> are used as unidirectional input and output pins correspondingly. <CLK> acts as the serial clock input. The status of <CSB> defines whether the SPI interface of the device is enabled (<CSB> is LOW) or disabled (<CSB> is HIGH). Programming clock edges (rising edges) at <CLK> input and data at the <SDIO> input are ignored until LOW-level is applied to the <CSB> input.

When the BGU8821/A is in power-down mode or there is no power supplied, the <SDIO> and <CSB> pins become high-impedance and do not disturb the SPI bus.

#### 8.2.2 Programming registers

The programming word is set through the input <SDIO> pin and a shift register, while <CSB> level is LOW. To release the SPI bus, <CSB> is set HIGH again.

The rising edge of the clock pulse <CLK> shifts each data bit value into the shift register.

The BGU8821/A supports single-byte and multi-byte (streaming) read/write access (register 0x01h bit [7]). In single-byte access, the new settings of the programmed register are applied on the last rising edge of <CLK> of data byte period. In multi-byte (streaming) access mode register address is auto-incremented or auto-decremented (depends on register 0x00h bits [5] and [2]) for the next 8-bit programming word.

By default, the data is entered with the most significant bit (MSB) first and the least significant bit (LSB) last. Register 0x00h bits [6] and [1] can be used to reverse the order (LSB bit first).

BGU8821/A

#### Dual channel low-noise high linearity amplifier with DSA and SPDT

#### 8.2.3 Power up Sequence

The BGU8821/A powers-up with the default register list content after supply voltage is applied to the  $V_{\text{DD(SPI)}}$  pin.

#### Dual channel low-noise high linearity amplifier with DSA and SPDT

#### 8.2.4 SPI control registers

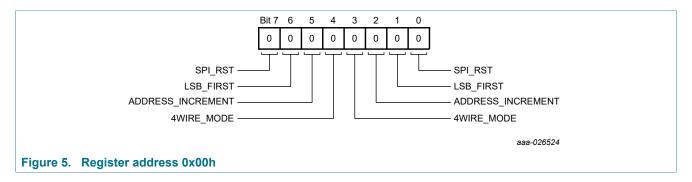

Register addresses 0x00h to 0x02h and 0x0Fh are dedicated to SPI control settings. Register 0x00h is mirror register, it will change to level HIGH if both corresponding bits are set HIGH.

Table 8. Register address 0×00h

| Bits        | Name              | Access | Value                                                                                 | Description                                                                                                                                                             |  |

|-------------|-------------------|--------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7           | SPI_RST           | W      | SPI reset bit. All registers are reverted to default state when bit is HIGH           |                                                                                                                                                                         |  |

| 7           | SPI_RST           | W      | 0*                                                                                    | Normal operation                                                                                                                                                        |  |

|             |                   |        | 1                                                                                     | Reset registers from address 0x02h up to 0x17h to default states. Bit shall be HIGH together with bit [0]. Bit value resets back to LOW level after command is executed |  |

| 6 LSB_FIRST |                   | R/W    | Sets MSI                                                                              | B_FIRST (default) or LSB_FIRST mode of operation                                                                                                                        |  |

|             |                   |        | 0*                                                                                    | MSB first mode. The data is entered with MSB first and LSB last.                                                                                                        |  |

|             |                   |        | 1                                                                                     | LSB first mode. The data is entered with LSB first and MSB last. Bit shall be set HIGH together with bit [1]                                                            |  |

| 5           | ADDRESS_INCREMENT | T R/W  | Sets register address read/write order for the streaming (multi-byte) SPI access mode |                                                                                                                                                                         |  |

|             |                   |        | 0*                                                                                    | Auto-decrementing register address order in the streaming mode                                                                                                          |  |

|             |                   |        | 1                                                                                     | Auto-incrementing register address order in the streaming mode. Bit shall be set HIGH together with bit [2]                                                             |  |

| 4           | 4WIRE_MODE        | R/W    | Switches                                                                              | SPI bus between 3-wire and 4-wire modes                                                                                                                                 |  |

|             |                   |        | 0*                                                                                    | 3-wire mode with <sdio> as bidirectional input and output pin</sdio>                                                                                                    |  |

|             |                   |        | 1                                                                                     | 4-wire mode with <sdio> as unidirectional input and <sdo> as unidirectional output pins. Bit shall be set HIGH together with bit [3]</sdo></sdio>                       |  |

### Dual channel low-noise high linearity amplifier with DSA and SPDT

| Bits               | Name       | Access | Value                                                                                                                                             | Description                                                                                                                                                                       |

|--------------------|------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3                  | 4WIRE_MODE | R/W    | Switches                                                                                                                                          | SPI bus between 3-wire and 4-wire modes                                                                                                                                           |

|                    |            |        | 0*                                                                                                                                                | 3-wire mode with <sdio> as bidirectional input and output pin</sdio>                                                                                                              |

|                    |            | 1      | 4-wire mode with <sdio> as unidirectional input and <sdo> as unidirectional output pins. Bit shall be set HIGH together with bit [4]</sdo></sdio> |                                                                                                                                                                                   |

| 2 ADRESS_INCREMENT |            | R/W    | _                                                                                                                                                 | ister address read/write order for the streaming (multi-byte) ess mode                                                                                                            |

|                    |            |        | 0*                                                                                                                                                | Auto-decrementing register address order in the streaming mode                                                                                                                    |

|                    |            |        | 1                                                                                                                                                 | Auto-incrementing register address order in the streaming mode. Bit shall be set HIGH together with bit [5]                                                                       |

| 1                  | LSB_FIRST  | R/W    | Sets MS                                                                                                                                           | B_FIRST (default) or LSB_FIRST mode of operation                                                                                                                                  |

|                    |            |        | 0*                                                                                                                                                | MSB_FIRST mode. The data is entered with MSB first and LSB last                                                                                                                   |

|                    |            |        | 1                                                                                                                                                 | LSB_FIRST mode. The data is entered with LSB first and MSB last. Bit shall be set HIGH together with bit [6]                                                                      |

| 0                  | SPI_FIRST  | W      | SPI rese<br>HIGH                                                                                                                                  | t bit. All registers are reverted to default state when bit is set                                                                                                                |

|                    |            |        | 0*                                                                                                                                                | Normal operation                                                                                                                                                                  |

|                    |            |        | 1                                                                                                                                                 | Resets all registers from address 0x02h up to 0x17h to default states. Bit shall be set HIGH together with bit [7]. Bit value resets back to LOW level after command is executed. |

#### Dual channel low-noise high linearity amplifier with DSA and SPDT

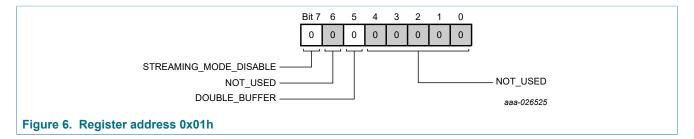

Table 9. Register address 0×01h

| Bits | Name                       | Access | Value             | Description                                                                                                                                                                                                                                                                                                   |

|------|----------------------------|--------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | STREAMING_MODE_<br>DISABLE | R/W    | LOW). Ad based on | g (multi-byte) read/write access is enabled by default (level ddresses will be auto-incremented or auto-decremented, register 0x00h, bit [5] and bit [2]. Setting HIGH disables g mode and switches to single-byte read/write access  Streaming (multi-byte) read/write access  Single-byre read/write access |

| _    |                            | _      |                   |                                                                                                                                                                                                                                                                                                               |

| 6    | NOT_USED                   | R      | Not used          |                                                                                                                                                                                                                                                                                                               |

| 5    | DOUBLE_BUFFER              | R/W    | Enables l         | Double-buffer mode for register 0x02h                                                                                                                                                                                                                                                                         |

|      |                            |        | 0*                | Read-back from active registers                                                                                                                                                                                                                                                                               |

|      |                            |        | 1                 | Read-back from buffer registers                                                                                                                                                                                                                                                                               |

| 4-0  | NOT_USED                   | R      | Not used          |                                                                                                                                                                                                                                                                                                               |

#### Dual channel low-noise high linearity amplifier with DSA and SPDT

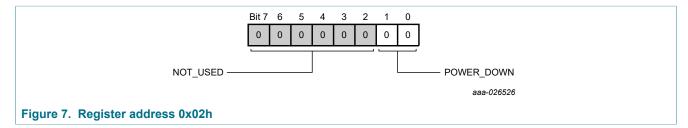

Table 10. Register address 0×02h

| Bits | Name       | Access | Value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Description     |  |  |

|------|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

| 7-2  | NOT_USED   | R      | Not used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |  |  |

| 1-0  | POWER_DOWN | R/W    | Sets power-down mode. In power-down mode all LNAs are discussed by the set of |                 |  |  |

|      |            |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |  |  |

|      |            |        | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |  |  |

|      |            |        | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |  |  |

|      |            |        | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Power-down mode |  |  |

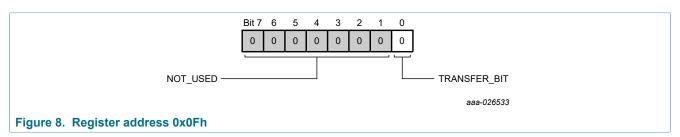

Table 11. Register address 0×0Fh

Legend: \* reset value

| Bits | Name         | Access | Value                                                                                         | Description                                                                                       |

|------|--------------|--------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| 7-1  | NOT_USED     | R      | Not used                                                                                      |                                                                                                   |

| 0    | TRANSFER_BIT | W      | Transfer bit must be set HIGH to transfer the contents of the binto the active register 0x02h |                                                                                                   |

|      |              |        | 0*                                                                                            | No transfer                                                                                       |

|      |              |        | 1                                                                                             | Transfer data into active registers. Bit value resets back to LOW level after command is executed |

#### Dual channel low-noise high linearity amplifier with DSA and SPDT

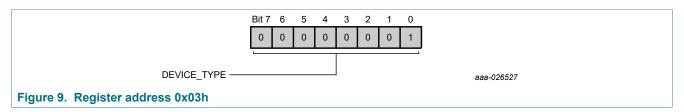

#### 8.2.5 Identification registers

Register addresses 0x03h to 0x06h, 0x0Ch and 0x0Dh are read-only registers and are used for identification (such as vendor ID, chip ID, chip version, etc).

Table 12. Register address 0×03h

Legend: \* reset value

| Bits | Name        | Access | Value                     | Description |

|------|-------------|--------|---------------------------|-------------|

| 7-0  | DEVICE_TYPE | R      | Sets device type: RF CHIP |             |

|      |             |        | 00000001*                 |             |

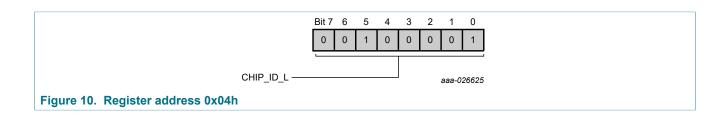

Table 13. Register address 0×04h

| Bits | Name      | Access | Value                        | Description |

|------|-----------|--------|------------------------------|-------------|

| 7-0  | CHIP_ID_L | R      | Low byte of Chip ID: 0x8821h |             |

|      |           |        | 00100001*                    |             |

#### Dual channel low-noise high linearity amplifier with DSA and SPDT

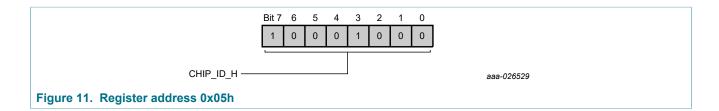

Table 14. Register address 0×05h

Legend: \* reset value

| I | Bits | Name      | Access | Value                         | Description |

|---|------|-----------|--------|-------------------------------|-------------|

|   | 7-0  | CHIP_ID_H | R      | High byte of Chip ID: 0x8821h |             |

|   |      |           |        | 10001000*                     |             |

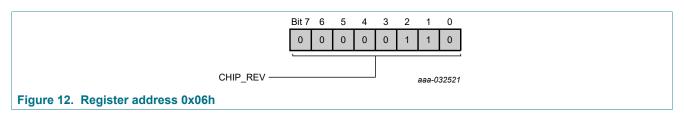

#### Table 15. Register address 0×06h

Legend: \* reset value

| •    |          |        |                |             |

|------|----------|--------|----------------|-------------|

| Bits | Name     | Access | Value          | Description |

| 7-0  | CHIP_REV | R      | Chip Revision: | : 0x06h     |

|      |          |        | 00000110*      |             |

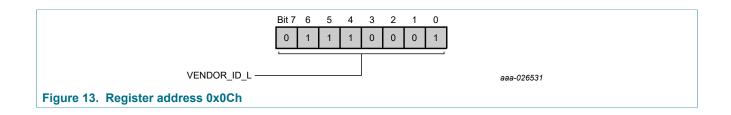

#### Table 16. Register address 0×0Ch

Legend: \* reset value

| Bits | Name        | Access | Value                                              | Description |

|------|-------------|--------|----------------------------------------------------|-------------|

| 7-0  | VENDOR_ID_L | R      | Low byte of Vendor ID: 0x471h - NXP Semiconductors |             |

|      |             |        | 01110001*                                          |             |

BGU8821/A

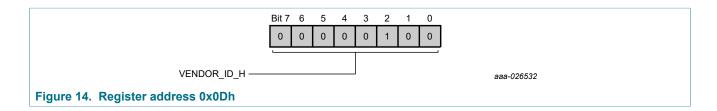

Table 17. Register address 0×0Dh

Legend: \* reset value

| Bits | Name        | Access | Value                                               | Description |

|------|-------------|--------|-----------------------------------------------------|-------------|

| 7-0  | VENDOR_ID_H | R      | High byte of Vendor ID: 0x471h - NXP Semiconductors |             |

|      |             |        | 0000100*                                            |             |

#### 8.2.6 Functional registers

Register addresses 0x10h - 0x13h, 0x16h, and 0x17h are used to set BGU8821/A functionality when accessed in write mode and to provide status update when accessed in read mode.

Registers 0x10h - 0x13h, 0x16h, and 0x17h are not double buffered. Transfer bit (register 0x0Fh, bit [0]) is not needed for these registers.

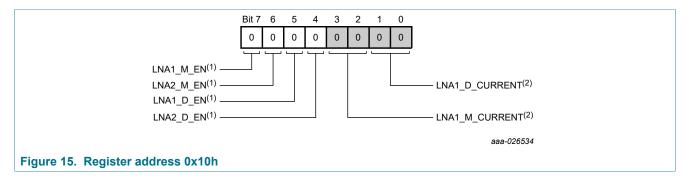

Table 18. Register address 0×10h

Legend: \* reset value

| Bits | Name                     | Access | Value                        | Description                              |

|------|--------------------------|--------|------------------------------|------------------------------------------|

| 7    | LNA1_M_EN <sup>[1]</sup> | R/W    | Enables LNA1 in Main Channel |                                          |

|      |                          |        | 0                            | LNA1_M is disabled (in low current mode) |

|      |                          |        | 1*                           | LNA1_M is enabled                        |

| 6    | LNA2_M_EN <sup>[1]</sup> | R/W    | Enables LNA2 in Main Channel |                                          |

|      |                          |        | 0                            | LNA2_M is disabled (in low current mode) |

|      |                          |        | 1*                           | LNA2_M is enabled                        |

| 5    | LNA1_D_EN <sup>[1]</sup> | R/W    | Enables                      | LNA1 in Diversity Channel                |

|      |                          | (      | 0                            | LNA1_D is disabled (in low current mode) |

|      |                          |        | 1*                           | LNA1_D is enabled                        |

BGU8821/A

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

#### Dual channel low-noise high linearity amplifier with DSA and SPDT

| Bits | Name                          | Access | Value                         | Description                                          |  |

|------|-------------------------------|--------|-------------------------------|------------------------------------------------------|--|

| 4    | LNA2_D_EN <sup>[1]</sup>      | R/W    | Enables I                     | LNA2 in Diversity Channel                            |  |

|      |                               |        | 0                             | LNA2_D is disabled (in low current mode)             |  |

|      |                               |        | 1*                            | LNA2_D is enabled                                    |  |

| 3-2  | LNA1_M_CURRENT <sup>[2]</sup> | R      | LNA1_M                        | current monitor status                               |  |

|      |                               |        | 00*                           | Normal operation                                     |  |

|      |                               |        | 10                            | N/A                                                  |  |

|      |                               |        | 01                            | Abnormal low current (min/typ/max => 9/23/33 mA)     |  |

|      |                               |        | 11                            | Abnormal high current (min/typ/max => 80/100/171 mA) |  |

| 1-0  | LNA1_D_CURRENT <sup>[2]</sup> | R/W    | LNA1_D current monitor status |                                                      |  |

|      |                               |        | 00*                           | Normal operation                                     |  |

|      |                               |        | 10                            | N/A                                                  |  |

|      |                               |        | 01                            | Abnormal low current (min/typ/max => 9/23/33 mA)     |  |

|      |                               |        | 11                            | Abnormal high current (min/typ/max => 80/100/171 mA) |  |

- [1] After reset/start-up LNAs are enabled.

- [2] Current monitor shall not be used with RF signals above +5 dBm.

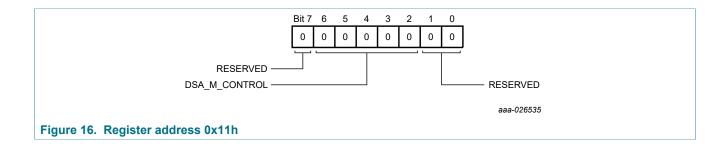

Table 19. Register address 0×11h

| Bits | Name          | Access | Value    | Description                                  |

|------|---------------|--------|----------|----------------------------------------------|

| 7    | RESERVED      | R/W    | Reserved | d bit. Shall be kept LOW                     |

|      |               |        | 0*       |                                              |

| 6-2  | DSA_M_CONTROL | R/W    | Main Cha | annel DSA 5-bit attenuation control          |

|      |               |        | 00000*   | Minimum Attenuation, equal to I <sub>L</sub> |

|      |               |        | 00001    | I <sub>L</sub> + 1 dB Attenuation            |

|      |               |        | 00010    | I <sub>L</sub> + 2 dB Attenuation            |

|      |               |        |          |                                              |

|      |               |        | 11111    | I <sub>L</sub> + 31 dB Attenuation           |

| 1-0  | RESERVED      | R/W    | Reserved | bits. Shall be kept LOW                      |

|      |               |        | 0*       |                                              |

#### Dual channel low-noise high linearity amplifier with DSA and SPDT

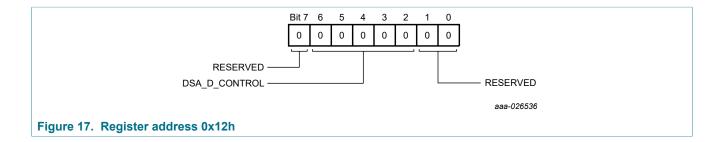

Table 20. Register address 0×12h

Legend: \* reset value

| Bits | Name          | Access | Value     | Description                                  |

|------|---------------|--------|-----------|----------------------------------------------|

| 7    | RESERVED      | R/W    | Reserved  | d bit. Shall be kept LOW                     |

|      |               | 0*     |           |                                              |

| 6-2  | DSA_D_CONTROL | R/W    | Diversity | Channel DSA 5-bit attenuation control        |

|      |               |        | 00000*    | Minimum Attenuation, equal to I <sub>L</sub> |

|      |               |        | 00001     | I <sub>L</sub> + 1 dB Attenuation            |

|      |               |        | 00010     | I <sub>L</sub> + 2 dB Attenuation            |

|      |               |        |           |                                              |

|      |               |        | 11111     | I <sub>L</sub> + 31 dB Attenuation           |

| 1-0  | RESERVED      | R/W    | Reserved  | bits. Shall be kept LOW                      |

|      |               |        | 0*        |                                              |

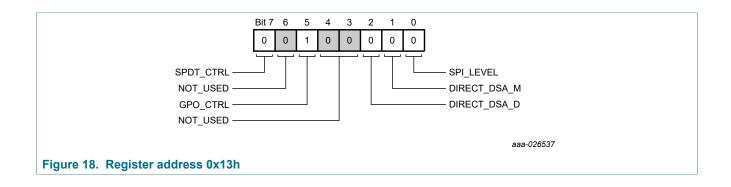

Table 21. Register address 0×13h

Legend: \* reset value

|   | •    |           |        |          |                                                                       |

|---|------|-----------|--------|----------|-----------------------------------------------------------------------|

|   | Bits | Name      | Access | Value    | Description                                                           |

|   | 7    | SPDT_CTRL | R/W    |          | ntrol bit. Connects SW_RFC input to SW_RF1 output or to SW_RF2 output |

|   |      |           |        | 0*       | SW_RFC connected to SW_RF1                                            |

|   |      |           |        | 1        | SW_RFC connected to SW_RF2                                            |

| Ì | 6    | NOT_USED  | R      | Not used |                                                                       |

BGU8821/A

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

### Dual channel low-noise high linearity amplifier with DSA and SPDT

| Bits | Name         | Access                  | Value    | Description                                                                                                                                                     |  |  |  |  |

|------|--------------|-------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 5    | GPO_CTRL     | R/W                     |          | n 23) control bit. GPO functionality is disabled, when device is access mode (register 0x13h bit [2] is LOW)                                                    |  |  |  |  |

|      |              |                         | 0        | GPO LOW                                                                                                                                                         |  |  |  |  |

|      |              |                         | 1*       | GPO HIGH                                                                                                                                                        |  |  |  |  |

| 4-3  | NOT_USED     | R                       | Not used | d                                                                                                                                                               |  |  |  |  |

| 2    | DIRECT_DSA_D | R/W                     | Disables | s direct access for DSA_D (DSA in Diversity channel)                                                                                                            |  |  |  |  |

|      |              |                         | 0*       | Direct access is enabled. DSA_D can be toggled between $I_L$ and prior programmed value x dB (set via register 0x17h) by pin 23. GPO functionality is disabled. |  |  |  |  |

|      |              |                         | 1        | Direct access is disabled. DSA can be set via register 0x12h.                                                                                                   |  |  |  |  |

| 1    | DIRECT_DSA_M | R/W                     | Disables |                                                                                                                                                                 |  |  |  |  |

|      |              |                         | 0*       | Direct access is enabled. DSA_M can be toggled between $I_L$ and prior programmed value x dB (set via register 0x16h) by pin 9.                                 |  |  |  |  |

|      |              |                         | 1        | Direct access is disabled. DSA can be set via register 0x11h.                                                                                                   |  |  |  |  |

| 0    | SPI_LEVEL    | R/W                     | Sets the | V <sub>OH</sub> voltage to be used by SPI                                                                                                                       |  |  |  |  |

|      |              |                         | 0*       | V <sub>OH</sub> = 1.8 V                                                                                                                                         |  |  |  |  |

|      |              | V <sub>OH</sub> = 3.3 V |          |                                                                                                                                                                 |  |  |  |  |

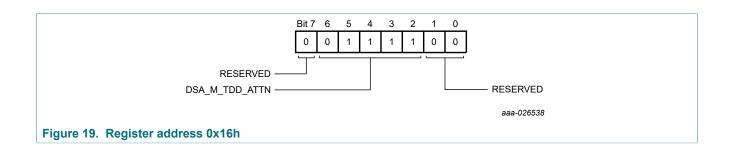

Table 22. Register address 0×16h

Legend: \* reset value

| Bits | Name           | Access                                                                                                        | Value                           | Description                                  |  |  |  |

|------|----------------|---------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------------------|--|--|--|

| 7    | RESERVED       | R/W                                                                                                           | Reserved bit. Shall be kept LOW |                                              |  |  |  |

|      |                |                                                                                                               | 0*                              |                                              |  |  |  |

| 6-2  | DSA_M_TDD_ATTN | R/W Main channel DSA attenuation level for direct-access mode in TDE systems. Attenuation is toggled by pin 9 |                                 |                                              |  |  |  |

|      |                |                                                                                                               | 00000                           | Minimum Attenuation, equal to I <sub>L</sub> |  |  |  |

|      |                |                                                                                                               | 00001                           | I <sub>L</sub> + 1 dB Attenuation            |  |  |  |

|      |                |                                                                                                               | 01111*                          | I <sub>L</sub> + 15 dB Attenuation           |  |  |  |

|      |                |                                                                                                               |                                 |                                              |  |  |  |

BGU8821/A

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

### Dual channel low-noise high linearity amplifier with DSA and SPDT

| Bits | Name     | Access | Value    | Description                        |

|------|----------|--------|----------|------------------------------------|

|      |          |        | 11111    | I <sub>L</sub> + 31 dB Attenuation |

| 1-0  | RESERVED | R/W    | Reserved | bits. Shall be kept LOW            |

|      |          |        | 0*       |                                    |

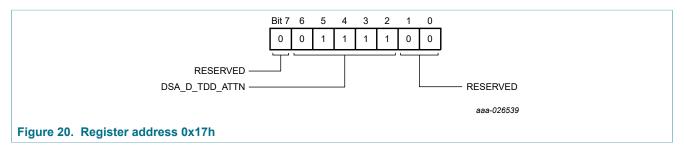

Table 23. Register address 0×17h

| Bits | Name           | Access | Value    | Description                                                                                    |  |  |

|------|----------------|--------|----------|------------------------------------------------------------------------------------------------|--|--|

| 7    | RESERVED       | R/W    | Reserved | bit. Shall be kept LOW                                                                         |  |  |

|      |                |        | 0*       |                                                                                                |  |  |

| 6-2  | DSA_D_TDD_ATTN | R/W    | _        | channel DSA attenuation level for direct-access mode in tems. Attenuation is toggled by pin 23 |  |  |

|      |                |        | 00000    | Minimum Attenuation, equal to I <sub>L</sub>                                                   |  |  |

|      |                |        | 00001    | I <sub>L</sub> + 1 dB Attenuation                                                              |  |  |

|      |                |        | 01111*   | I <sub>L</sub> + 15 dB Attenuation                                                             |  |  |

|      |                |        |          |                                                                                                |  |  |

|      |                |        | 11111    | I <sub>L</sub> + 31 dB Attenuation                                                             |  |  |

| 1-0  | RESERVED       | R/W    | Reserved | Reserved bits. Shall be kept LOW                                                               |  |  |

|      |                |        | 0*       |                                                                                                |  |  |

#### Dual channel low-noise high linearity amplifier with DSA and SPDT

#### 8.3 Device Functionality

The BGU8821/A supports both main and diversity receiver channels in both TDD and FDD systems. It has a first stage LNA optimized for sensitivity followed by a digital step attenuator and output stage amplifier. The first stage LNA output is routed outside the device, so there is a possibility to use the device in different system configurations (e.g. connect frequency selective filters in-between output of the first stage LNA and DSA input, refer to Functional Diagram in Section 6).

Main and Diversity channels are controlled separately, via addressing different registers in device's memory. LNAs can be set in power-down mode to save current consumption depending on system configuration (address 0x10h, refer to <u>Table 18</u>).

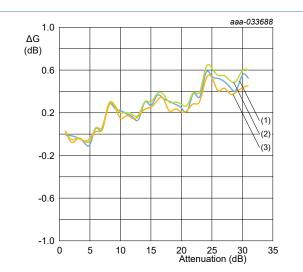

Attenuation levels of DSAs can be set with steps of 1 dB and total range of 31 dB. Attenuation can be written to the address 0x11h for Main channel (<u>Table 19</u>) and the address 0x12h for Diversity channel (<u>Table 20</u>).

To support highly integrated solutions and reduce platform costs a standalone SPDT switch is included. Switch is controlled at address 0x13h (refer to Table 21).

All RF inputs and outputs are single-ended and matched to 50  $\Omega$  (external matching components may be required, refer to Application information in Section 14). The BGU8821/A is controlled via SPI bus, supporting both 3- and 4-wire configurations. Full description of SPI interface is provided in Section 8.2. In TDD systems, the LNAs and DSA can also be controlled via direct-access pins. The direct-access functionality is described in Section 8.1.

#### Dual channel low-noise high linearity amplifier with DSA and SPDT

### 9 Limiting values

#### Table 24. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol               | Parameter                          | Conditions                        | Min | Max  | Unit |

|----------------------|------------------------------------|-----------------------------------|-----|------|------|

| V <sub>CC</sub>      | supply voltage                     | for all supply pins               | -   | 6    | V    |

| P <sub>i(RF)CW</sub> | continuous waveform RF input power | for 2 hrs all RF input pins       | -   | 20   | dBm  |

|                      |                                    | at SPDT ports for 2 hrs           |     | 30   | dBm  |

| T <sub>stg</sub>     | storage temperature                |                                   | -40 | +150 | °C   |

| Tj                   | junction temperature               |                                   | -   | 150  | °C   |

| Р                    | power dissipation                  | $T_{case} \le 105  ^{\circ}C$ [1] | -   | 1.7  | W    |

| V <sub>ESD</sub>     | electrostatic discharge voltage    | Human Body Model (HBM) [2]        | -   | 1.0  | kV   |

|                      |                                    | Charged Device Model (CDM) [3]    | -   | 0.5  | kV   |

<sup>[1]</sup> Case is ground solder pad.

### 10 Recommended operating conditions

#### **Table 25. Characteristics**

| Symbol            | Parameter                | Conditions | Min  | Тур | Max  | Unit |

|-------------------|--------------------------|------------|------|-----|------|------|

| V <sub>CC</sub>   | supply voltage           |            | 4.75 | 5   | 5.25 | V    |

| $Z_0$             | characteristic impedance |            | -    | 50  | -    | Ω    |

| T <sub>case</sub> | case temperature         |            | -40  | -   | +105 | °C   |

### 11 Thermal characteristics

#### **Table 26. Thermal characteristics**

| Symbol                  | Parameter                           | Conditions                                                  | Тур | Unit |

|-------------------------|-------------------------------------|-------------------------------------------------------------|-----|------|

| $R_{th(j\text{-case})}$ | junction to case thermal resistance | Soldered on NXP evaluation board, $T_{amb} = 95  ^{\circ}C$ | 29  | K/W  |

Based on simulation,  $T_{case} = 105$  °C under the mentioned conditions. Case is the center ground solder pad.

According to ANSI/ESDA/JEDEC standard JS-001-2010. For pins 2, 11 (RFIN M, RFIN D) limiting value is 1 kV, for all other pins limiting value is 2 kV

<sup>3]</sup> According to JEDEC standard 22-C101B.

<sup>[2]</sup> Thermal resistance measured using on die thermal sensing diodes.

#### 12 Characteristics

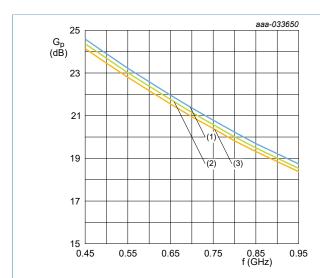

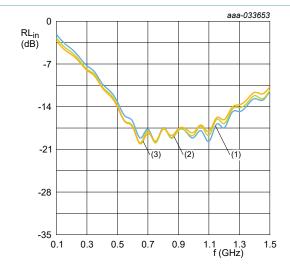

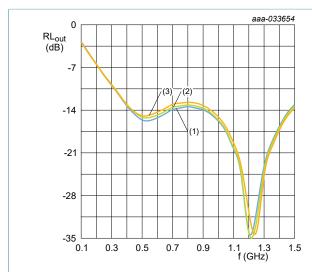

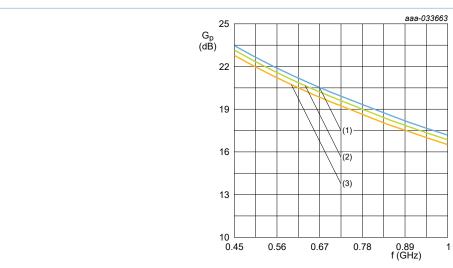

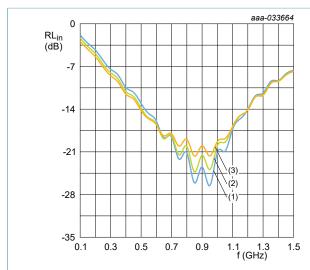

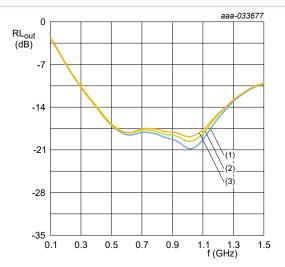

#### Table 27. Characteristics BGU8821/A LNA1 for Main and Diversity Channel

f = 900 MHz;  $V_{CC}$  = 5 V;  $T_{amb}$  = 25 °C; input and output 50  $\Omega$ ; unless otherwise specified. All RF parameters are measured in an application board as shown in Figure 44 with components listed in Table 33 optimized for f = 900 MHz.

| Symbol               | Parameter                                | Conditions                                                                                                 |     | Min  | Тур | Max | Unit |

|----------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|------|-----|-----|------|

| I <sub>CC</sub>      | supply current                           | LNA1 Enable                                                                                                |     | -    | 54  | 64  | mA   |

|                      |                                          | Disable                                                                                                    |     | -    | 3   | -   | mA   |

| G <sub>p</sub>       | power gain                               |                                                                                                            | [1] | 15.9 | 19  | -   | dB   |

| NF                   | noise figure                             | At room temperature                                                                                        | [1] | -    | 0.6 | -   | dB   |