Freescale Semiconductor, Inc.

HC05G3GRS/D REV 1.1

# 68HC05G3 68HC705G4

# SPECIFICATION (General Release)

© December 14, 1994

Freescale Semiconductor, Inc.

## **TABLE OF CONTENTS**

| <b>SECTION 1</b>                                                                                                                                | INTRODUCTION                                                                                                                                                                                                         | 1                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 1.1<br>1.2<br>1.3<br>1.4<br>1.4.1<br>1.5<br>1.5.1<br>1.5.2                                                                                      | GENERAL<br>FEATURES<br>MASK OPTIONS<br>SYSTEM CONFIGURATIONS<br>OSCILLATORS AND CLOCK DISTRIBUTIONS<br>TST/V <sub>PP</sub> PIN<br>SUMMARY OF INTERNAL REGISTERS AND I/O MAP<br>OPTION MAP FOR THE I/O CONFIGURATIONS | 1<br>6<br>6<br>16<br>17                                                                |

| <b>SECTION 2</b>                                                                                                                                | MODES OF OPERATION                                                                                                                                                                                                   | 27                                                                                     |

| 2.1<br>2.2<br>2.3<br>2.4                                                                                                                        | GENERAL<br>MODE ENTRY<br>SINGLE-CHIP MODE (SCM)<br>SELF-CHECK/BOOTSTRAP MODE                                                                                                                                         | 27<br>28                                                                               |

| <b>SECTION 3</b>                                                                                                                                | MEMORY                                                                                                                                                                                                               | 29                                                                                     |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.7.1                                                                                          | GENERAL<br>RAM<br>SELF-CHECK ROM (MC68HC05G3)<br>BOOT ROM (MC68HC705G4)<br>MASK ROM (MC68HC05G3)<br>EPROM (MC68HC705G4)<br>PROGRAMMING SEQUENCE<br>PROGRAM CONTROL REGISTER (PCR)                                    | 31<br>31<br>31<br>31<br>31<br>31<br>32                                                 |

| <b>SECTION 4</b>                                                                                                                                | CPU CORE                                                                                                                                                                                                             | 33                                                                                     |

| 4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5<br>4.1.6<br>4.2<br>4.2.1<br>4.2.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.3<br>4.2.4 | REGISTERS                                                                                                                                                                                                            | 33<br>33<br>33<br>34<br>34<br>34<br>36<br>36<br>36<br>37<br>38<br>39<br>39<br>39<br>39 |

| 4.3.1<br>4.3.2                                                                                                                                  | IMMEDIATE<br>DIRECT                                                                                                                                                                                                  |                                                                                        |

|         | 4.3.3                                                                                                                                             | EXTENDED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40                                                                                                                                                                               |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 4.3.4                                                                                                                                             | RELATIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40                                                                                                                                                                               |

|         | 4.3.5                                                                                                                                             | INDEXED, NO OFFSET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 41                                                                                                                                                                               |

|         | 4.3.6                                                                                                                                             | INDEXED, 8-BIT OFFSET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41                                                                                                                                                                               |

|         | 4.3.7                                                                                                                                             | INDEXED, 16-BIT OFFSET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41                                                                                                                                                                               |

|         | 4.3.8                                                                                                                                             | BIT SET/CLEAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 41                                                                                                                                                                               |

|         | 4.3.9                                                                                                                                             | BIT TEST AND BRANCH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 41                                                                                                                                                                               |

|         | 4.3.10                                                                                                                                            | INHERENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                  |

|         | 4.4                                                                                                                                               | LOW-POWER MODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                  |

|         | 4.4.1                                                                                                                                             | STOP MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                  |

|         | 4.4.2                                                                                                                                             | WAIT MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                  |

| SECTION | 5                                                                                                                                                 | RESET/ INTERRUPT STRUCTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45                                                                                                                                                                               |

|         | 5.1                                                                                                                                               | GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                  |

|         | 5.1.1                                                                                                                                             | SOFTWARE INTERRUPT (SWI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                  |

|         | 5.2                                                                                                                                               | INTERRUPTS OF THE MC68HC05G3 (705G4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                  |

|         | 5.2.1                                                                                                                                             | IRQ1/IRQ2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                  |

|         | 5.2.2                                                                                                                                             | KEY WAKEUP INTERRUPT (KWI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                  |

|         | 5.2.3                                                                                                                                             | KEY WAKE-UP INTERRUPT TIMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                  |

|         | 5.2.4                                                                                                                                             | TIMER 1 INTERRUPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                                                                                                                                                                               |

|         | 5.2.5                                                                                                                                             | TIMER 2 INTERRUPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50                                                                                                                                                                               |

|         | 5.2.6                                                                                                                                             | SPI1 AND SPI2 INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50                                                                                                                                                                               |

|         | 5.2.7                                                                                                                                             | TB INTERRUPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 50                                                                                                                                                                               |

|         |                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50                                                                                                                                                                               |

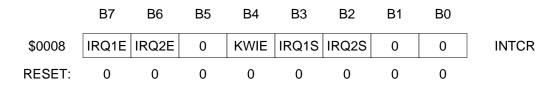

|         | 5.2.8                                                                                                                                             | INTERRUPT CONTROL REGISTER (INTCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                  |

|         | 5.2.8<br>5.2.9                                                                                                                                    | INTERRUPT CONTROL REGISTER (INTCR)<br>INTERRUPT STATUS REGISTER (INTSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                  |

| SECTION | 5.2.9                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53                                                                                                                                                                               |

| SECTION | 5.2.9                                                                                                                                             | INTERRUPT STATUS REGISTER (INTSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53<br><b>57</b>                                                                                                                                                                  |

| SECTION | 5.2.9                                                                                                                                             | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS<br>PORT A                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53<br><b>57</b><br>57                                                                                                                                                            |

| SECTION | 5.2.9<br>  <b>6</b><br>6.1                                                                                                                        | INTERRUPT STATUS REGISTER (INTSR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53<br><b>57</b><br>57<br>58                                                                                                                                                      |

| SECTION | 5.2.9<br>6<br>6.1<br>6.1.1                                                                                                                        | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS<br>PORT A<br>PORT A DATA REGISTER (PORTA)                                                                                                                                                                                                                                                                                                                                                                                                                                     | 53<br>57<br>57<br>58<br>58                                                                                                                                                       |

| SECTION | 5.2.9<br>6.1<br>6.1.1<br>6.1.2                                                                                                                    | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS<br>PORT A<br>PORT A DATA REGISTER (PORTA)<br>PORT A DATA DIRECTION REGISTER (DDRA)<br>PORT B                                                                                                                                                                                                                                                                                                                                                                                  | 53<br>57<br>57<br>58<br>58<br>59                                                                                                                                                 |

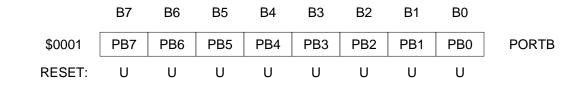

| SECTION | 5.2.9<br>6.1<br>6.1.1<br>6.1.2<br>6.2                                                                                                             | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS<br>PORT A DATA REGISTER (PORTA)<br>PORT A DATA DIRECTION REGISTER (DDRA)<br>PORT B<br>PORT B DATA REGISTER (PORTB)<br>PORT C                                                                                                                                                                                                                                                                                                                                                  | 53<br>57<br>58<br>58<br>59<br>59<br>59<br>60                                                                                                                                     |

| SECTION | 5.2.9<br>6.1<br>6.1.1<br>6.1.2<br>6.2<br>6.2.1                                                                                                    | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS<br>PORT A<br>PORT A DATA REGISTER (PORTA)<br>PORT A DATA DIRECTION REGISTER (DDRA)<br>PORT B<br>PORT B DATA REGISTER (PORTB)<br>PORT C<br>PORT C DATA REGISTER (PORTC)                                                                                                                                                                                                                                                                                                        | 53<br>57<br>57<br>58<br>58<br>59<br>60<br>61                                                                                                                                     |

| SECTION | 5.2.9<br>6.1<br>6.1.1<br>6.1.2<br>6.2<br>6.2.1<br>6.3                                                                                             | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS<br>PORT A DATA REGISTER (PORTA)<br>PORT A DATA DIRECTION REGISTER (DDRA)<br>PORT B<br>PORT B DATA REGISTER (PORTB)<br>PORT C                                                                                                                                                                                                                                                                                                                                                  | 53<br>57<br>57<br>58<br>58<br>59<br>60<br>61                                                                                                                                     |

| SECTION | 5.2.9<br>6.1<br>6.1.1<br>6.1.2<br>6.2<br>6.2.1<br>6.3<br>6.3.1                                                                                    | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS<br>PORT A<br>PORT A DATA REGISTER (PORTA)<br>PORT A DATA DIRECTION REGISTER (DDRA)<br>PORT B<br>PORT B DATA REGISTER (PORTB)<br>PORT C<br>PORT C DATA REGISTER (PORTC)<br>PORT C DATA DIRECTION REGISTER (DDRC)                                                                                                                                                                                                                                                               | 53<br>57<br>58<br>58<br>59<br>60<br>61<br>61<br>61                                                                                                                               |

| SECTION | 5.2.9<br>6.1<br>6.1.1<br>6.1.2<br>6.2<br>6.2.1<br>6.3<br>6.3.1<br>6.3.2                                                                           | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS<br>PORT A<br>PORT A DATA REGISTER (PORTA)<br>PORT A DATA DIRECTION REGISTER (DDRA)<br>PORT B<br>PORT B DATA REGISTER (PORTB)<br>PORT C<br>PORT C DATA REGISTER (PORTC)<br>PORT C DATA DIRECTION REGISTER (DDRC)                                                                                                                                                                                                                                                               | 53<br>57<br>58<br>58<br>59<br>60<br>61<br>61<br>61                                                                                                                               |

| SECTION | 5.2.9<br>6.1<br>6.1.1<br>6.1.2<br>6.2<br>6.2.1<br>6.3<br>6.3.1<br>6.3.2<br>6.4                                                                    | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS<br>PORT A<br>PORT A DATA REGISTER (PORTA)<br>PORT A DATA DIRECTION REGISTER (DDRA)<br>PORT B<br>PORT B DATA REGISTER (PORTB)<br>PORT C<br>PORT C DATA REGISTER (PORTC)<br>PORT C DATA DIRECTION REGISTER (DDRC)                                                                                                                                                                                                                                                               | 53<br>57<br>58<br>58<br>58<br>59<br>59<br>60<br>61<br>61<br>61<br>62<br>62                                                                                                       |

| SECTION | 5.2.9<br>6.1<br>6.1.1<br>6.1.2<br>6.2<br>6.2.1<br>6.3<br>6.3.1<br>6.3.2<br>6.4<br>6.4.1<br>6.4.2<br>6.5                                           | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS<br>PORT A<br>PORT A DATA REGISTER (PORTA)<br>PORT A DATA DIRECTION REGISTER (DDRA)<br>PORT B<br>PORT B DATA REGISTER (PORTB)<br>PORT C<br>PORT C DATA REGISTER (PORTC)<br>PORT C DATA DIRECTION REGISTER (DDRC)<br>PORT D DATA REGISTER (PORTD)<br>PORT D DATA REGISTER (PORTD)<br>PORT D DATA DIRECTION REGISTER (DDRD)                                                                                                                                                      | 53<br>57<br>58<br>58<br>58<br>59<br>59<br>60<br>61<br>61<br>61<br>62<br>62<br>62<br>62<br>63                                                                                     |

| SECTION | 5.2.9<br>6.1<br>6.1.1<br>6.1.2<br>6.2<br>6.2.1<br>6.3<br>6.3.1<br>6.3.2<br>6.4<br>6.4.1<br>6.4.2<br>6.5<br>6.5.1                                  | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 53<br>57<br>58<br>58<br>58<br>59<br>59<br>60<br>61<br>61<br>61<br>62<br>62<br>62<br>62<br>63<br>63                                                                               |

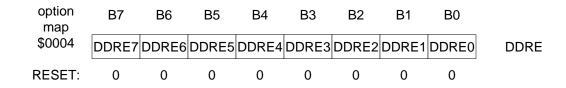

| SECTION | 5.2.9<br>6.1<br>6.1.1<br>6.1.2<br>6.2<br>6.2.1<br>6.3<br>6.3.1<br>6.3.2<br>6.4<br>6.4.1<br>6.4.2<br>6.5<br>6.5.1<br>6.5.2                         | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS<br>PORT A DATA REGISTER (PORTA)<br>PORT A DATA DIRECTION REGISTER (DDRA)<br>PORT B DATA REGISTER (PORTB)<br>PORT C DATA REGISTER (PORTC)<br>PORT C DATA REGISTER (PORTC)<br>PORT C DATA DIRECTION REGISTER (DDRC)<br>PORT D DATA REGISTER (PORTD)<br>PORT D DATA REGISTER (PORTD)<br>PORT D DATA REGISTER (PORTD)<br>PORT E DATA REGISTER (PORTE)<br>PORT E DATA REGISTER (PORTE)                                                                                             | 53<br>57<br>58<br>58<br>58<br>59<br>59<br>59<br>60<br>61<br>61<br>61<br>62<br>62<br>62<br>62<br>63<br>63<br>63                                                                   |

| SECTION | 5.2.9<br>6<br>6.1<br>6.1.1<br>6.1.2<br>6.2<br>6.2<br>6.2<br>6.2<br>6.3<br>6.3.1<br>6.3.2<br>6.4<br>6.4.1<br>6.4.2<br>6.5<br>6.5.1<br>6.5.2<br>6.6 | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS<br>PORT A DATA REGISTER (PORTA)<br>PORT A DATA DIRECTION REGISTER (DDRA)<br>PORT B DATA REGISTER (PORTB)<br>PORT C DATA REGISTER (PORTC)<br>PORT C DATA REGISTER (PORTC)<br>PORT D DATA REGISTER (PORTD)<br>PORT D DATA REGISTER (PORTD)<br>PORT D DATA REGISTER (PORTD)<br>PORT D DATA REGISTER (PORTD)<br>PORT E DATA REGISTER (PORTE)<br>PORT E DATA REGISTER (PORTE)<br>PORT E DATA DIRECTION REGISTER (DDRE)                                                             | 53<br>57<br>58<br>58<br>58<br>59<br>59<br>60<br>61<br>61<br>61<br>62<br>62<br>62<br>62<br>62<br>63<br>63<br>63<br>63<br>63                                                       |

| SECTION | 5.2.9<br>6.1<br>6.1.1<br>6.1.2<br>6.2<br>6.2.1<br>6.3<br>6.3.1<br>6.3.2<br>6.4<br>6.4.1<br>6.4.2<br>6.5<br>6.5.1<br>6.5.2<br>6.6<br>6.6.1         | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS<br>PORT A<br>PORT A DATA REGISTER (PORTA)<br>PORT A DATA DIRECTION REGISTER (DDRA)<br>PORT B<br>PORT B DATA REGISTER (PORTB)<br>PORT C<br>PORT C DATA REGISTER (PORTC)<br>PORT C DATA DIRECTION REGISTER (DDRC)<br>PORT D DATA DIRECTION REGISTER (DDRC)<br>PORT D DATA REGISTER (PORTD)<br>PORT D DATA REGISTER (PORTD)<br>PORT E DATA REGISTER (PORTE)<br>PORT E DATA REGISTER (PORTE)<br>PORT E DATA REGISTER (PORTE)<br>PORT F DATA REGISTER (PORTF)                      | 53<br>57<br>58<br>58<br>58<br>59<br>59<br>60<br>61<br>61<br>61<br>62<br>62<br>62<br>62<br>63<br>63<br>63<br>63<br>64<br>64                                                       |

| SECTION | 5.2.9<br>6.1<br>6.1.1<br>6.1.2<br>6.2<br>6.2.1<br>6.3<br>6.3.1<br>6.3.2<br>6.4<br>6.4.1<br>6.4.2<br>6.5<br>6.5.1<br>6.5.2<br>6.6<br>6.6.1<br>6.7  | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS<br>PORT A<br>PORT A DATA REGISTER (PORTA)<br>PORT A DATA DIRECTION REGISTER (DDRA)<br>PORT B<br>PORT B DATA REGISTER (PORTB)<br>PORT C<br>PORT C DATA REGISTER (PORTC)<br>PORT C DATA DIRECTION REGISTER (DDRC)<br>PORT D DATA REGISTER (PORTD)<br>PORT D DATA REGISTER (PORTD)<br>PORT D DATA REGISTER (PORTD)<br>PORT E<br>PORT E DATA REGISTER (PORTE)<br>PORT E DATA REGISTER (PORTE)<br>PORT E DATA REGISTER (PORTE)<br>PORT F DATA REGISTER (PORTF)<br>PORT F<br>PORT G | 53<br>57<br>58<br>58<br>59<br>59<br>60<br>61<br>61<br>61<br>62<br>62<br>62<br>62<br>63<br>63<br>63<br>63<br>63<br>64<br>64<br>65                                                 |

| SECTION | 5.2.9<br>6.1<br>6.1.1<br>6.1.2<br>6.2<br>6.2.1<br>6.3<br>6.3.1<br>6.3.2<br>6.4<br>6.4.1<br>6.4.2<br>6.5<br>6.5.1<br>6.5.2<br>6.6<br>6.6.1         | INTERRUPT STATUS REGISTER (INTSR)<br>INPUT/OUTPUT PORTS<br>PORT A<br>PORT A DATA REGISTER (PORTA)<br>PORT A DATA DIRECTION REGISTER (DDRA)<br>PORT B<br>PORT B DATA REGISTER (PORTB)<br>PORT C<br>PORT C DATA REGISTER (PORTC)<br>PORT C DATA DIRECTION REGISTER (DDRC)<br>PORT D DATA DIRECTION REGISTER (DDRC)<br>PORT D DATA REGISTER (PORTD)<br>PORT D DATA REGISTER (PORTD)<br>PORT E DATA REGISTER (PORTE)<br>PORT E DATA REGISTER (PORTE)<br>PORT E DATA REGISTER (PORTE)<br>PORT F DATA REGISTER (PORTF)                      | 53<br>57<br>58<br>58<br>58<br>59<br>59<br>60<br>61<br>61<br>61<br>61<br>62<br>62<br>62<br>62<br>62<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>63<br>64<br>64<br>65<br>66 |

| 6.8              | PORT H                                      |      |

|------------------|---------------------------------------------|------|

| 6.8.1            | PORT H DATA REGISTER (PORTH)                | 67   |

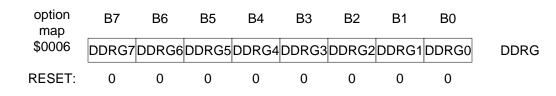

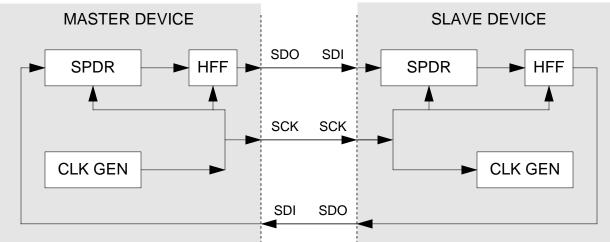

| 6.8.2            | PORT H DATA DIRECTION REGISTER (DDRH)       | 68   |

| 6.9              | PORT J                                      | 68   |

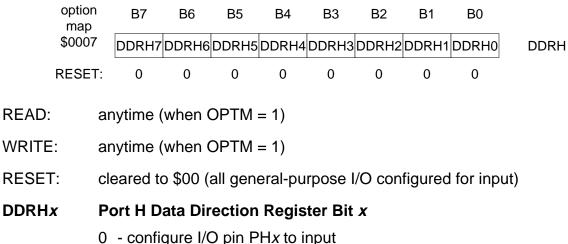

| 6.9.1            | PORT J DATA REGISTER (PORTJ)                | 68   |

| SECTION 7        | SERIAL PERIPHERAL INTERFACE (SPI)           | . 69 |

| 7.1              | FEATURES                                    | 69   |

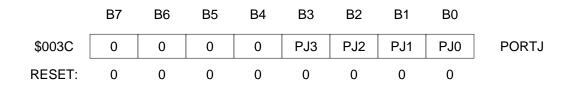

| 7.2              | FUNCTIONAL DESCRIPTIONS                     |      |

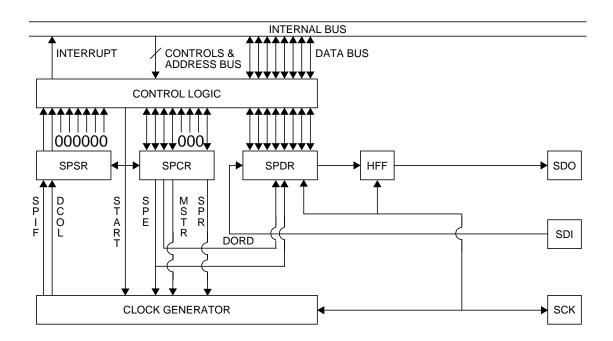

| 7.2.1            | INTERNAL BLOCK DESCRIPTIONS                 | 70   |

| 7.3              | SIGNAL DESCRIPTIONS                         |      |

| 7.3.1            | SPI DATA I/O (SDI and SDO)                  |      |

| 7.3.2            | SERIAL CLOCK (SCK)                          |      |

| 7.4              | REGISTERS                                   | 73   |

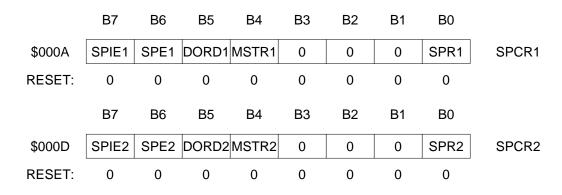

| 7.4.1            | SERIAL PERIPHERAL CONTROL REGISTER (SPCRx). |      |

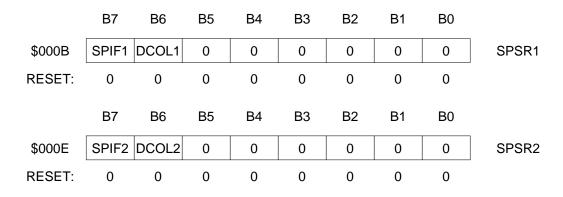

| 7.4.2            | SERIAL PERIPHERAL STATUS REGISTER (SPSRx)   |      |

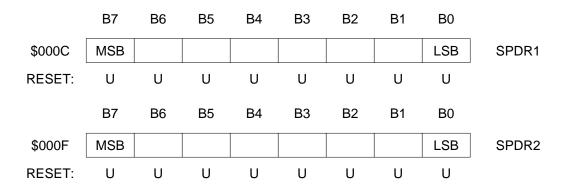

| 7.4.3            | SERIAL PERIPHERAL DATA REGISTER (SPDRx)     |      |

| 7.5              | PORT FUNCTION                               | 79   |

| <b>SECTION 8</b> | TIMER SYSTEM                                | . 81 |

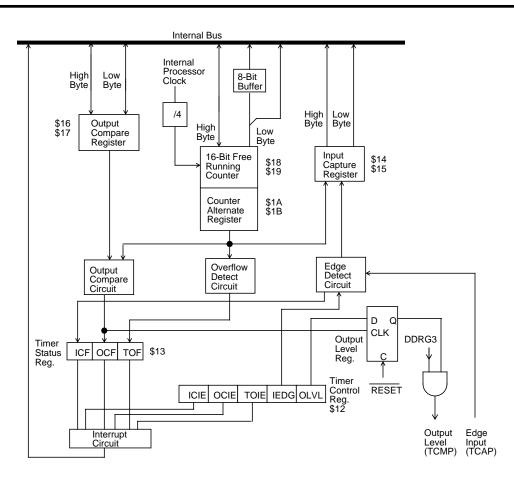

| 8.1              | TIMER 1                                     | 81   |

| 8.1.1            | COUNTER                                     | -    |

| 8.1.2            | OUTPUT COMPARE REGISTER                     |      |

| 8.1.3            | INPUT CAPTURE REGISTER                      |      |

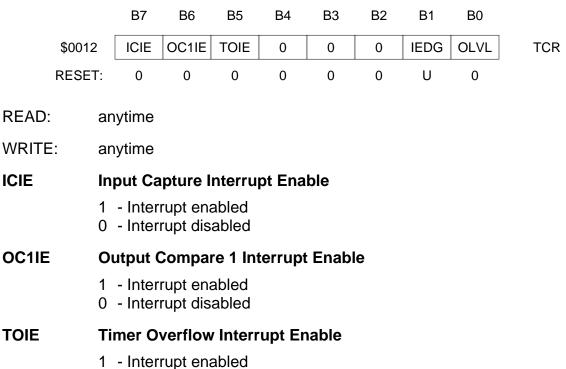

| 8.1.4            | TIMER CONTROL REGISTER (TCR) \$12           |      |

| 8.1.5            | TIMER STATUS REGISTER (TSR) \$13            |      |

| 8.1.6            | TIMER DURING WAIT MODE                      |      |

| 8.1.7            | TIMER DURING STOP MODE                      |      |

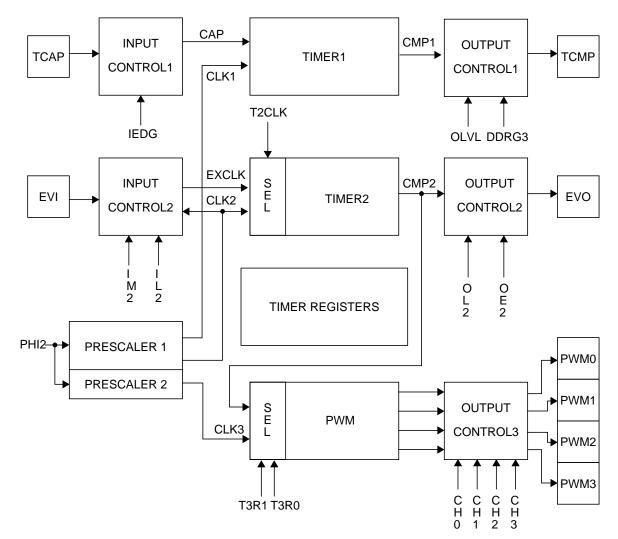

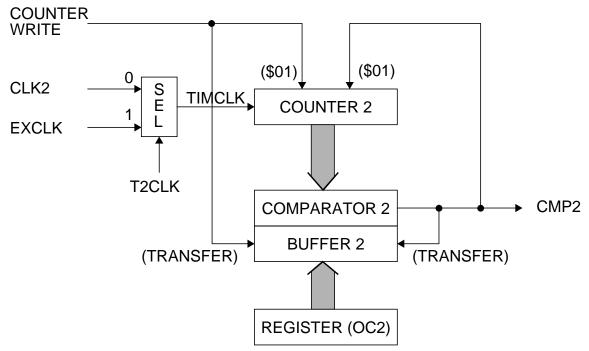

| 8.2              |                                             |      |

| 8.3              |                                             |      |

| 8.4<br>8.4.1     | TIMER I/O PINS<br>TIMER INPUT 1 (TCAP)      |      |

| 8.4.2            | TIMER INPUT 2 (EVI)                         |      |

| 8.4.3            | TIMER OUTPUT 1 (TCMP)                       |      |

| 8.4.4            | TIMER OUTPUT 2 (EVO)                        |      |

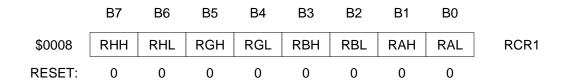

| 8.5              | TIMER REGISTERS                             |      |

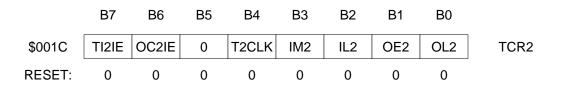

| 8.5.1            | TIMER CONTROL REGISTER 2 (TCR2)             | 97   |

| 8.5.2            | TIMER STATUS REGISTER 2 (TSR2)              |      |

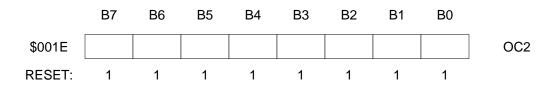

| 8.5.3            | OUTPUT COMPARE REGISTER 2 (ÓC2)             |      |

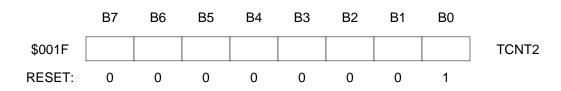

| 8.5.4            | TIMER COUNTER 2 (TCNT2)                     | 100  |

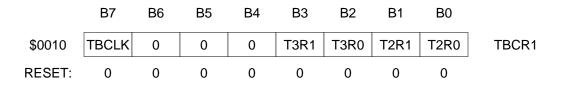

| 8.5.5            | TIMER BASE CONTROL REGISTER 1 (TBCR1)       | 101  |

| <b>SECTION 9</b> | PULSE WIDTH MODULATOR                       | 103  |

| 9.1              | GENERAL                                     | 103  |

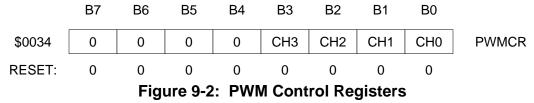

| 9.2              | PWM CONTROL REGISTER (PWMCR)                |      |

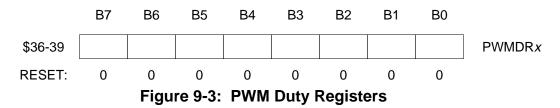

| 9.3              | PWM DUTY REGISTER (PWMDRx)                  |      |

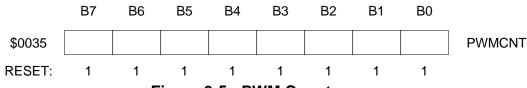

| 9.4              | PWM COUNTER (PWMCNT)                        |      |

|                  |                                             |      |

| 9.5<br>9.6        |        | M DURING WAIT MODE<br>M DURING STOP MODE |     |

|-------------------|--------|------------------------------------------|-----|

| <b>SECTION 10</b> | A/D C  | ONVERTER1                                | 111 |

| 10.               | .1 ANA | ALOG SECTION                             | 111 |

| 10.               |        | RATIOMETRIC CONVERSION                   |     |

| 10.               |        | VREFH and VREFL                          |     |

| 10.               | .1.3 / | ACCURACY AND PRECISION                   | 111 |

| 10.               | .2 COI | NVERSION PROCESS                         | 111 |

| 10.               |        | ITAL SECTION                             |     |

| 10.               |        | CONVERSION TIMES                         |     |

|                   |        | MULTI-CHANNEL OPERATION                  |     |

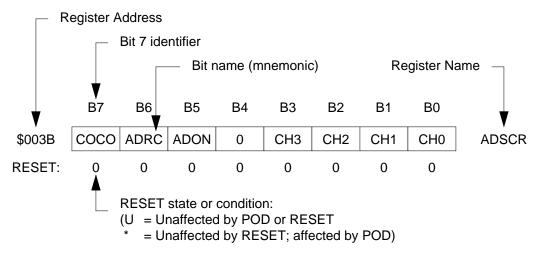

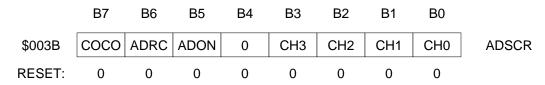

| 10.               |        | STATUS AND CONTROL REGISTER (ADSCR) \$3B |     |

| 10.               |        | COCO - CONVERSIONS COMPLETE              |     |

| -                 |        | ADRC - RC OSCILLATOR ON                  | 112 |

| -                 | -      | ADON - A/D On                            | -   |

| -                 |        | CH3:CH0 - CHANNEL SELECT BITS            |     |

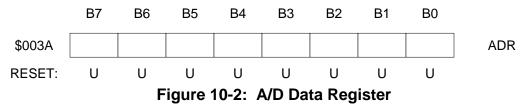

| 10.               |        | DATA REGISTER (\$3A)                     |     |

| 10.               |        | DURING WAIT MODE                         |     |

| 10.               | .7 A/D | DURING STOP MODE                         | 114 |

| <b>SECTION 11</b> | ELEC   | TRICAL SPECIFICATIONS1                   | 15  |

| 11.               | .1 MAX | XIMUM RATINGS                            | 115 |

| 11.               | .2 DC  | OPERATING CHARACTERISTICS                | 115 |

| 11.               | .3 DC  | ELECTRICAL CHARACTERISTICS (5.0 Vdc)     | 116 |

| 11.               | .4 DC  | ELECTRICAL CHARACTERISTICS (2.5 Vdc)     | 117 |

| 11.               |        | CONVERTER CHARACTERISTICS                | -   |

| 11.               | .6 COI | NTROL TIMING (5.0 Vdc)                   | 119 |

| 11.               |        | NTROL TIMING (2.5 Vdc)                   |     |

# LIST OF FIGURES

| Figure 1-1:                                                             | Block Diagram of the MC68HC05G3 (705G4)                                                                                                            | 2                                |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Figure 1-2:                                                             | Pin Assignment for Single-Chip Mode                                                                                                                |                                  |

| Figure 1-3:                                                             | Memory Map of MC68HC05G3                                                                                                                           |                                  |

| Figure 1-4:                                                             | Memory Map of MC68HC705G4                                                                                                                          | 5                                |

| Figure 1-5:                                                             | Clock Signal Distribution                                                                                                                          | 6                                |

| Figure 1-6:                                                             | OSC1/2 and XOSC1/2 Mask Options                                                                                                                    | 7                                |

| Figure 1-7:                                                             | Clock State and STOP/POD Delay Diagram                                                                                                             | 10                               |

| Figure 1-8:                                                             | Time Base Clock Divider                                                                                                                            | 11                               |

| Figure 1-9:                                                             | Register Description Key                                                                                                                           | 17                               |

| Figure 1-10:                                                            | Main I/O Map (\$0000-\$000F)                                                                                                                       | 18                               |

| Figure 1-11:                                                            | Main I/O Map (\$0010-\$001F)                                                                                                                       | 19                               |

| Figure 1-12:                                                            | Main I/O Map (\$0034-\$003F)                                                                                                                       | 20                               |

| Figure 1-13:                                                            | Option Map (\$0000-\$000F)                                                                                                                         | 21                               |

|                                                                         |                                                                                                                                                    |                                  |

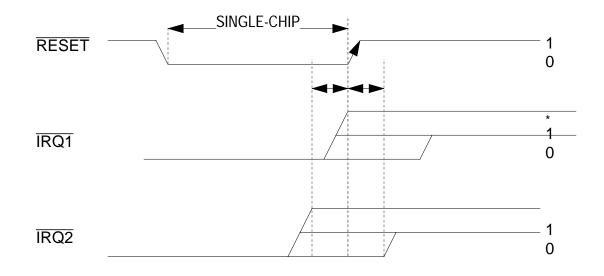

| Figure 2-1:                                                             | HC05G3 (705G4) Mode Entry Diagram                                                                                                                  | 28                               |

|                                                                         |                                                                                                                                                    |                                  |

| Figure 3-1:                                                             | MC68HC05G3 (705G4) Memory Map                                                                                                                      | 30                               |

|                                                                         |                                                                                                                                                    |                                  |

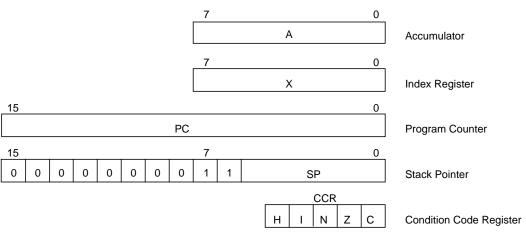

| Figure 4-1:                                                             | Programming Model                                                                                                                                  | 33                               |

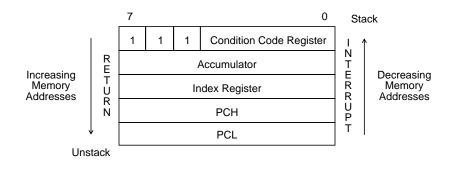

| Figure 4-2:                                                             | Stacking Order                                                                                                                                     | 34                               |

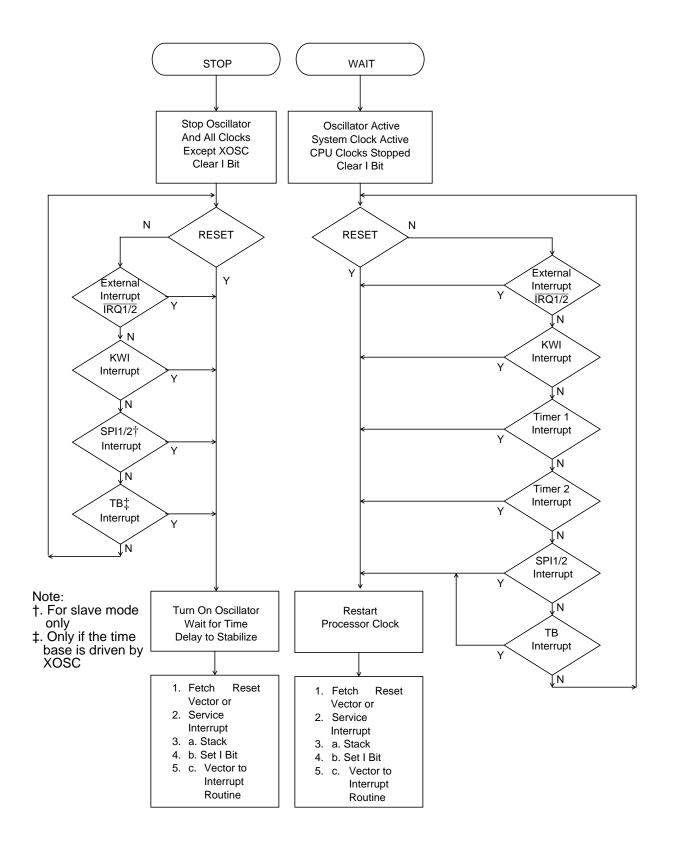

| Figure 4-3:                                                             | STOP/WAIT Flowcharts                                                                                                                               | 43                               |

|                                                                         |                                                                                                                                                    |                                  |

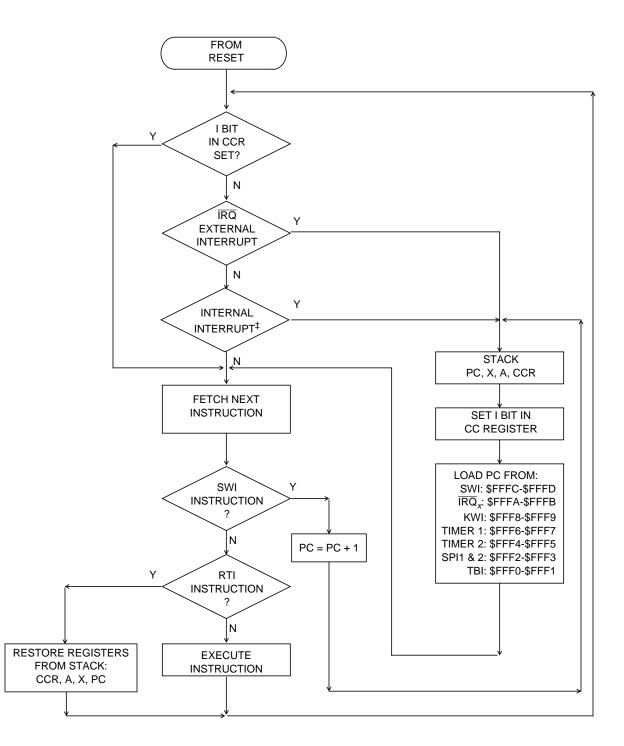

| Figure 5-1:                                                             | Interrupt Flowchart                                                                                                                                | 47                               |

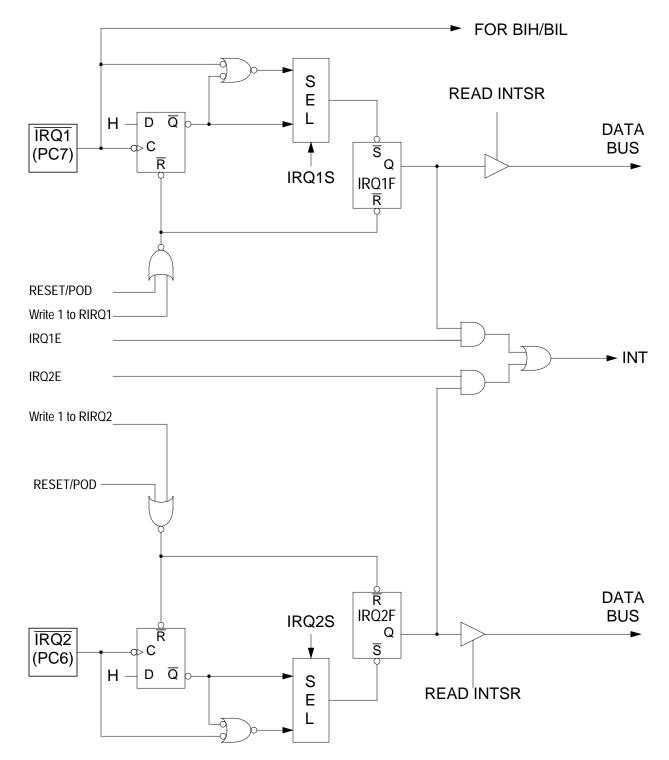

| Figure 5-2:                                                             |                                                                                                                                                    |                                  |

| rigaro o E.                                                             | IRQ1 and IRQ2 Block Diagram                                                                                                                        | 48                               |

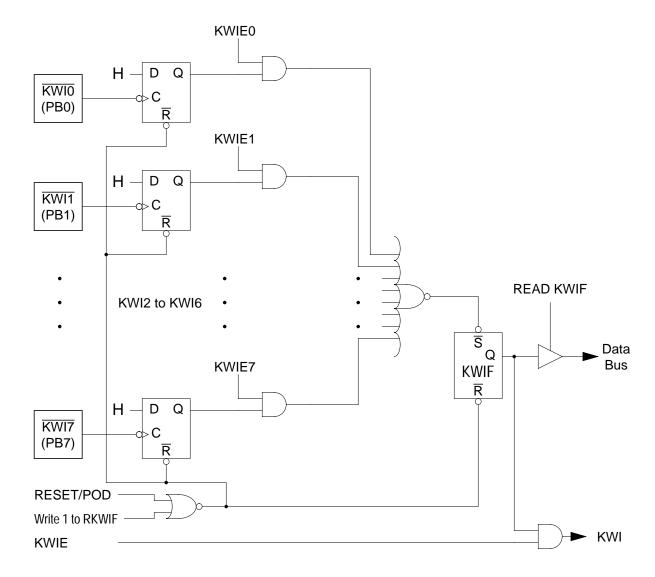

| Figure 5-3:                                                             | IRQ1 and IRQ2 Block Diagram<br>Key Wakeup Interrupt (KWI)                                                                                          |                                  |

| 0                                                                       |                                                                                                                                                    |                                  |

| 0                                                                       |                                                                                                                                                    | 49                               |

| Figure 5-3:                                                             | Key Wakeup Interrupt (KWI)                                                                                                                         | 49                               |

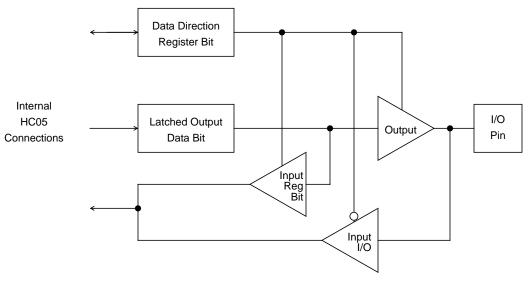

| Figure 5-3:                                                             | Key Wakeup Interrupt (KWI)                                                                                                                         | 49<br>57                         |

| Figure 5-3:<br>Figure 6-1:                                              | Key Wakeup Interrupt (KWI)                                                                                                                         | 49<br>57<br>70                   |

| Figure 5-3:<br>Figure 6-1:<br>Figure 7-1:                               | Key Wakeup Interrupt (KWI)<br>Port I/O Circuitry for One Bit<br>SPI Master-Slave Interconnection                                                   | 49<br>57<br>70<br>70             |

| Figure 5-3:<br>Figure 6-1:<br>Figure 7-1:<br>Figure 7-2:                | Key Wakeup Interrupt (KWI)<br>Port I/O Circuitry for One Bit<br>SPI Master-Slave Interconnection<br>SPI Block Diagram                              | 49<br>57<br>70<br>70             |

| Figure 5-3:<br>Figure 6-1:<br>Figure 7-1:<br>Figure 7-2:                | Key Wakeup Interrupt (KWI)<br>Port I/O Circuitry for One Bit<br>SPI Master-Slave Interconnection<br>SPI Block Diagram                              | 49<br>57<br>70<br>70<br>72       |

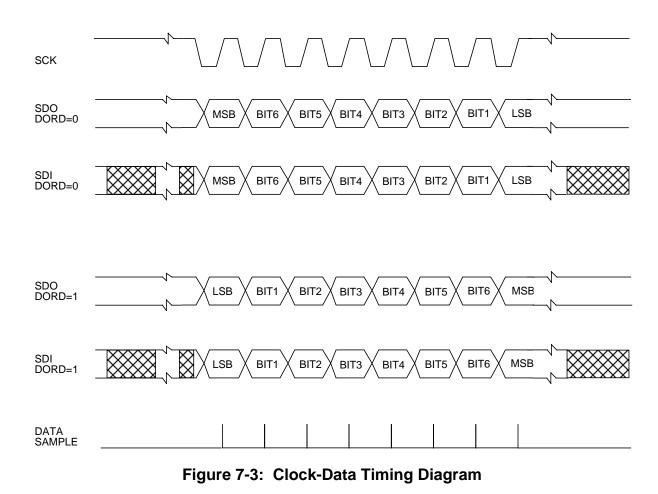

| Figure 5-3:<br>Figure 6-1:<br>Figure 7-1:<br>Figure 7-2:<br>Figure 7-3: | Key Wakeup Interrupt (KWI)<br>Port I/O Circuitry for One Bit<br>SPI Master-Slave Interconnection<br>SPI Block Diagram<br>Clock-Data Timing Diagram | 49<br>57<br>70<br>70<br>72<br>81 |

# :68HC05G3 (705G4) SFraescale Semiconductor, Inc.

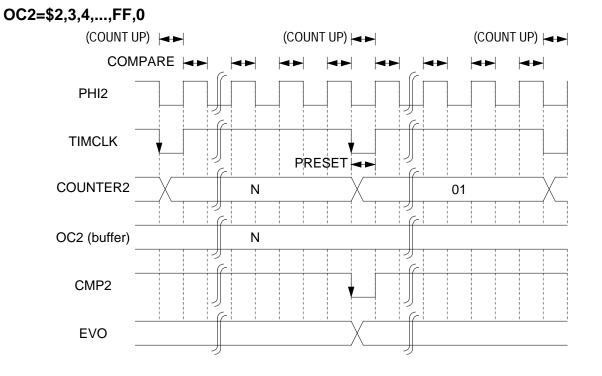

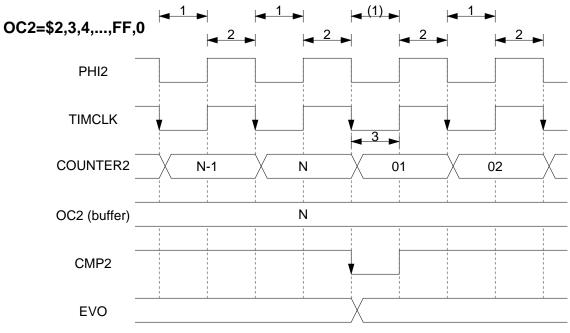

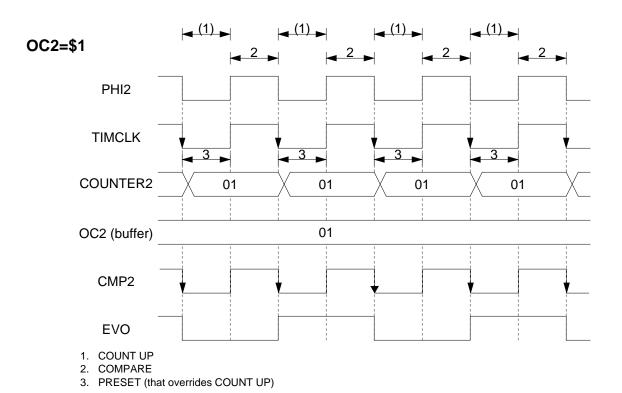

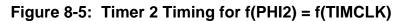

| Figure 8-4:  | Timer 2 Timing for f(PHI2) > f(TIMCLK)      | 90  |

|--------------|---------------------------------------------|-----|

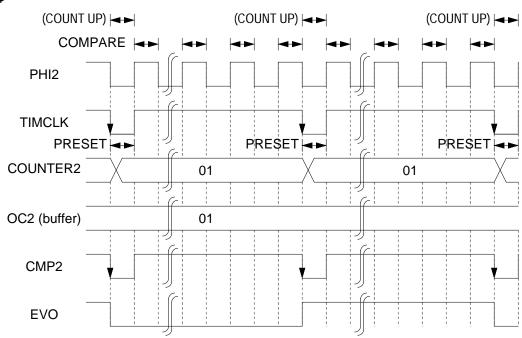

| Figure 8-5:  | Timer 2 Timing for f(PHI2) = f(TIMCLK)      | 91  |

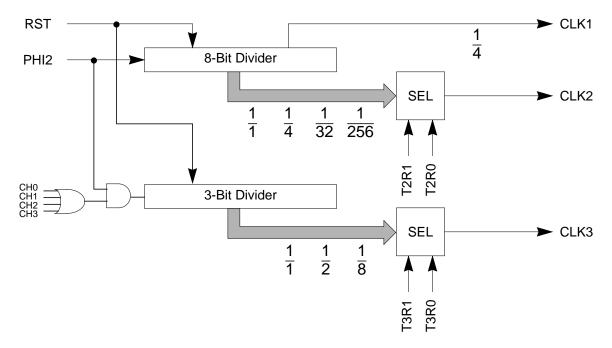

| Figure 8-6:  | Prescaler Block Diagram                     |     |

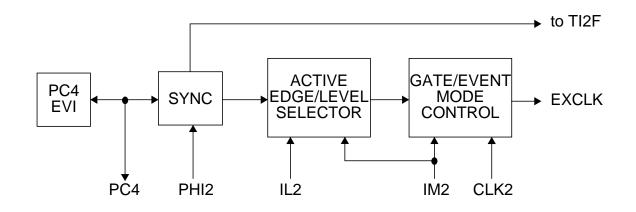

| Figure 8-7:  | EVI Block Diagram                           | 93  |

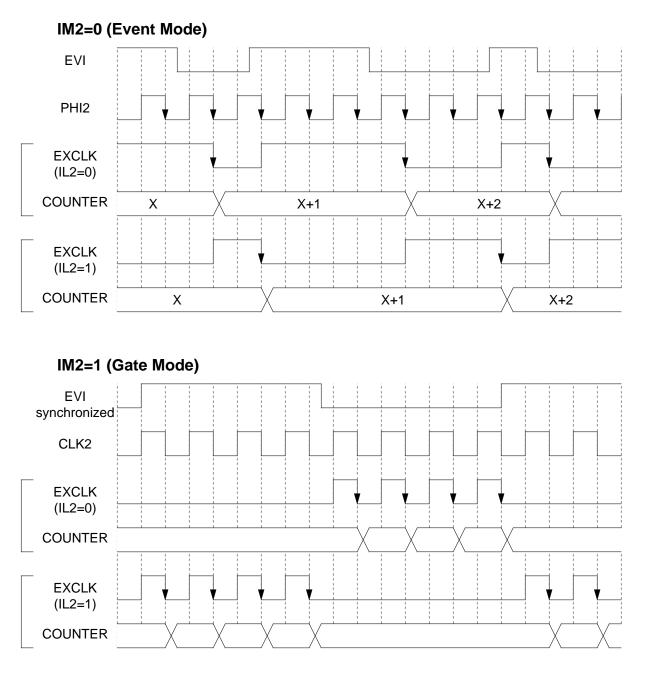

| Figure 8-8:  | EVI Timing Examples                         | 94  |

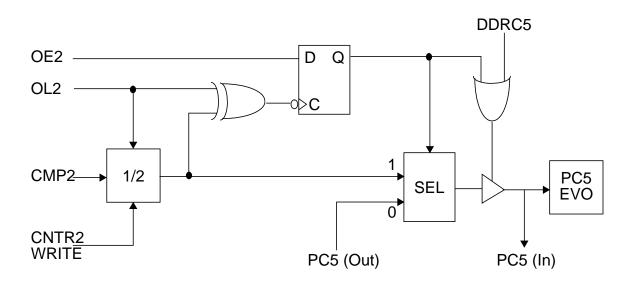

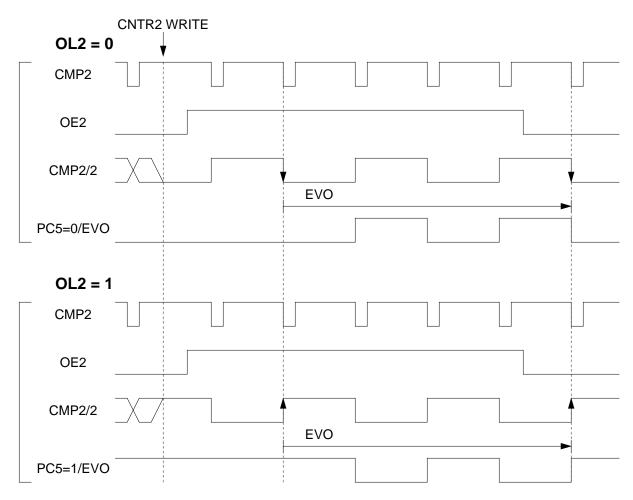

| Figure 8-9:  | VO Block Diagram                            | 95  |

| Figure 8-10: | EVO Timing Example                          |     |

|              |                                             |     |

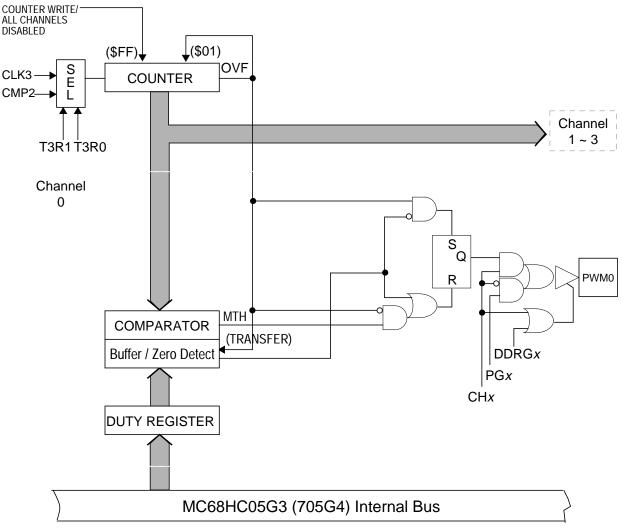

| Figure 9-1:  | PWM System Block Diagram                    |     |

| Figure 9-2:  | WM Control Registers                        |     |

| Figure 9-3:  | PWM Duty Registers                          |     |

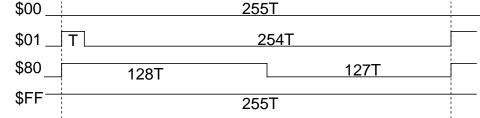

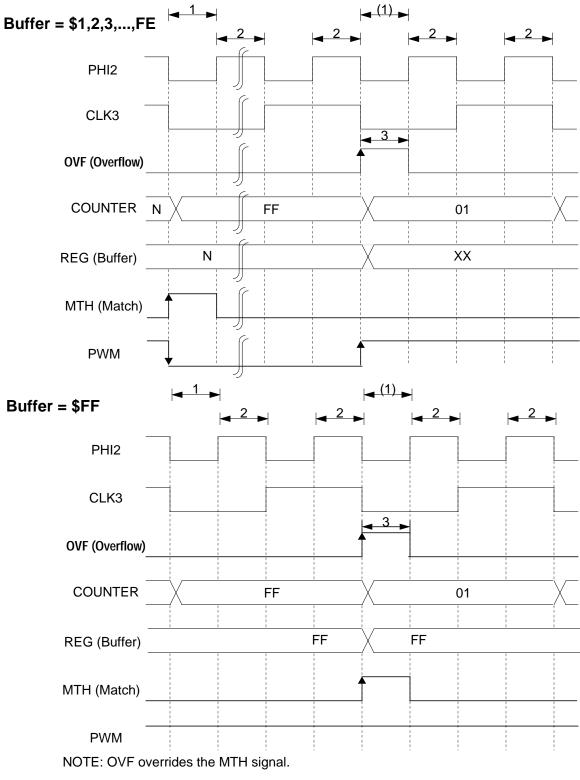

| Figure 9-4:  | PWM Waveform Examples (E = 2MHz; CLK = E/2) |     |

| Figure 9-5:  | PWM Counter                                 |     |

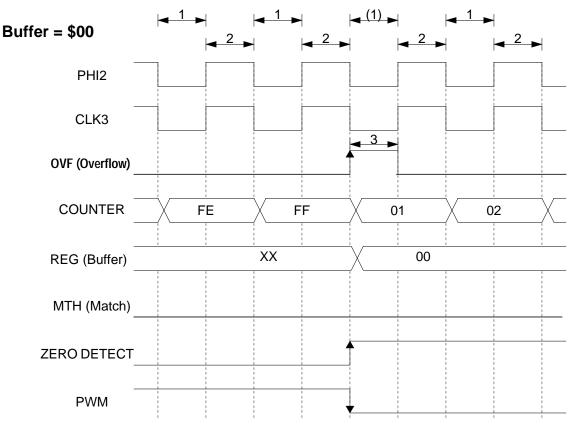

| Figure 9-6:  | PWM Timing for f(CLK3) = f(PHI2)            |     |

| Figure 9-7:  | PWM Timing for f(CLK3) = f(PHI2)            |     |

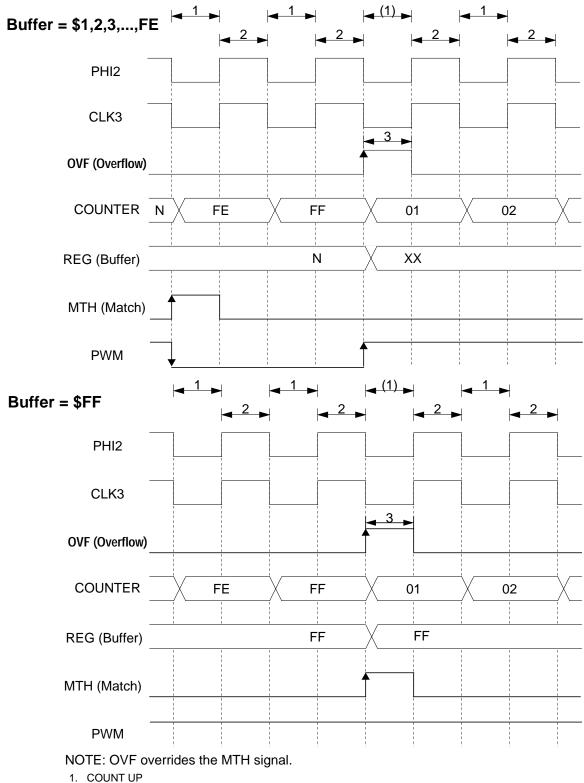

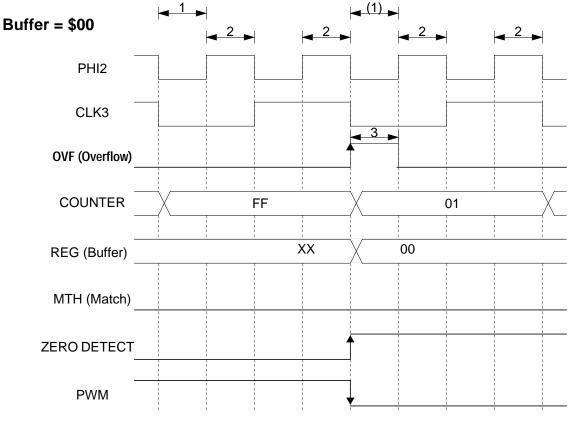

| Figure 9-8:  | PWM Timing for f(CLK3) < f(PHI2)            |     |

| Figure 9-9:  | PWM Timing for f(CLK3) < f(PHI2             |     |

|              |                                             |     |

| Figure 10-1: | A/D Status and Control Register             | 112 |

| Figure 10-2: | A/D Data Register                           |     |

## LIST OF TABLES

| Table 1-1:  | System Clock Frequency       | 8   |

|-------------|------------------------------|-----|

| Table 1-2:  | Recovery Time Requirements   | 9   |

| Table 1-3:  | TB Interrupt Frequency       | 12  |

| Table 1-4:  | COP Timeout Period           | 12  |

| Table 2-1:  | Mode Select Summary          | 27  |

| Table 5-1:  | Interrupt Vector Assignments | 45  |

| Table 8-1:  | EVI Mode Select              | 94  |

| Table 9-1:  | PWM Clock Selection          | 104 |

| Table 10-1: | A/D Channel Assignments      |     |

### **SECTION 1**

### INTRODUCTION

### 1.1 GENERAL

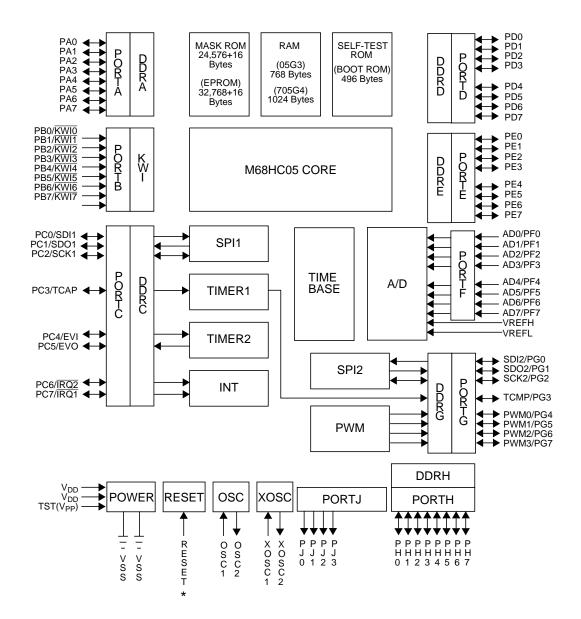

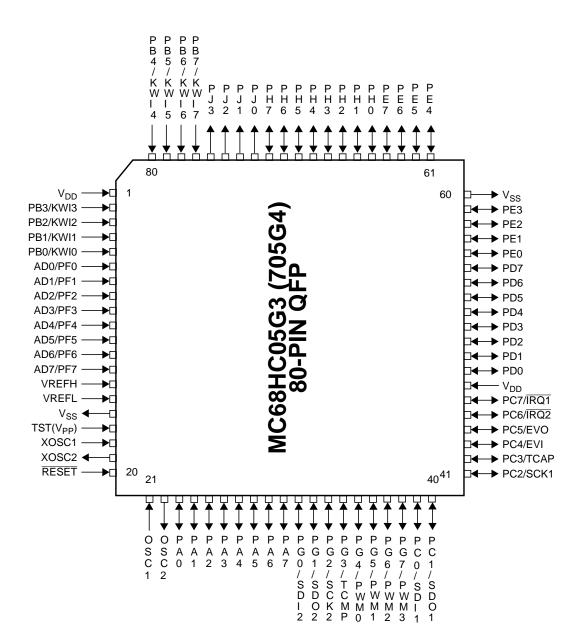

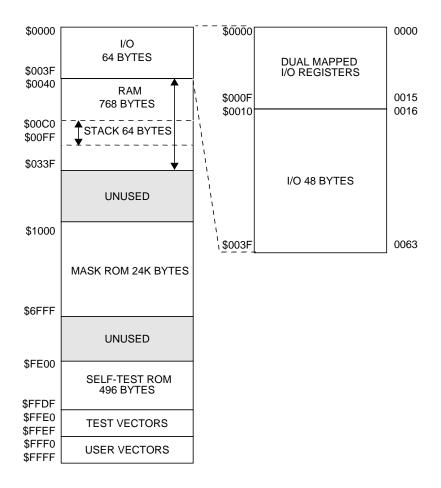

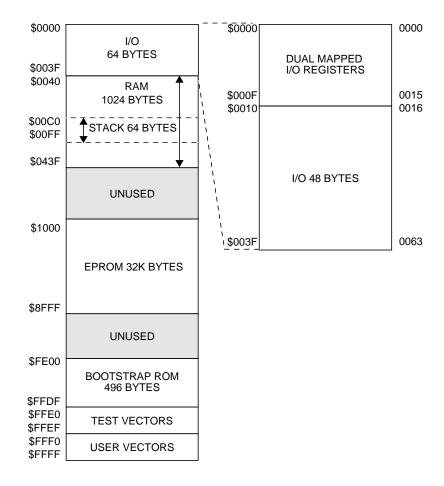

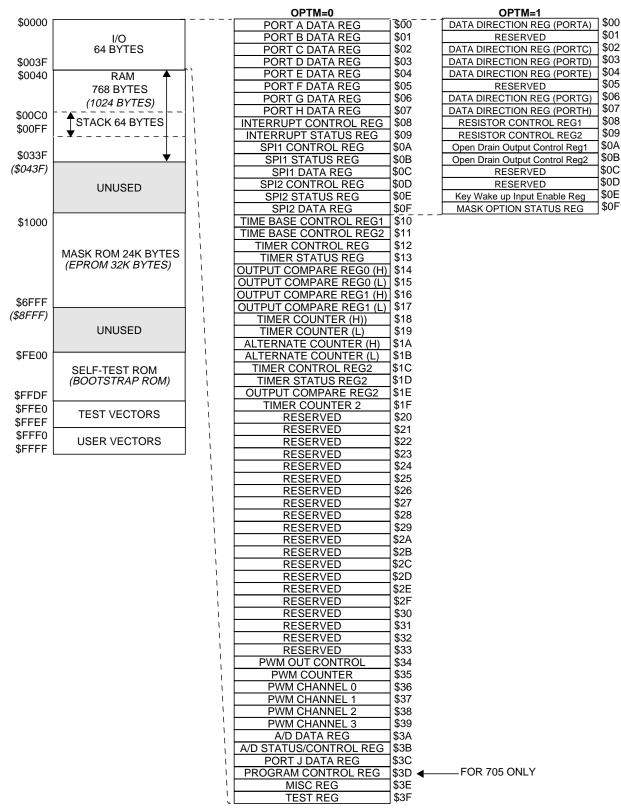

The MC68HC05G3 (705G4) is an 80-pin microcontroller unit (MCU) with highly sophisticated on-chip peripheral functions. The memory map of MC68HC05G3 (ROM device) includes 24 Kbytes of user ROM and 768 bytes of RAM. The memory map of MC68HC705G4 erasable programmable read-only memory (EPROM device) includes 32 Kbytes of user EPROM and 1 Kbyte of RAM. The MCU has nine ports: A, B, C, D, E, F, G, H, and J. Ports A, C, D, E, G, and H each have eight input-output (I/O) pins, ports B and F each have eight input-only pins, and port J has four output-only pins. The MC68HC05G3 includes a time-based circuit, 8- and 16-bit timers, an 8-bit pulse width modulator, a computer operating properly (COP) watchdog timer, an 8-bit analog/digital (A/D) converter, eight key wakeup interrupts, and two serial peripheral interfaces.

### 1.2 FEATURES

- Low Cost

- HC05 Core

- 80-Pin Quad Flat Package (QFP)

- 24,592 Bytes of Mask ROM or 32,784 Bytes of EPROM (Including 16 Bytes of User Vectors)

- 768 Bytes (ROM Device) or 1024 Bytes (EPROM Device) of On-Chip RAM

- 48 Bidirectional I/O Lines, 16 Input-Only Lines, Four Output-Only Lines

- 16-Bit Timer with Output Compare and Input Capture

- 8-Bit Event Counter/Modulus Clock Divider

- COP Watchdog Timer

- Two Serial Peripheral Interfaces (SPI)

- Four Channels of 8-bit Pulse Width Modulator (PWM)

- Eight Channels of 8-Bit A/D Converter

- On-Chip Time-Based Circuits

- Dual Oscillators and Selectable System Clock Frequency

- Power-Saving Stop Mode/Wait Mode

- Time Base Interrupts

- Two IRQ Inputs

- Key Wakeup Interrupt with 8-Bit Inputs

## BHC05G3 (705G4) Sp**Errenciale**, Semiconductor, Inc.

Figure 1-1: Block Diagram of the MC68HC05G3 (705G4)

### 1.3 MASK OPTIONS

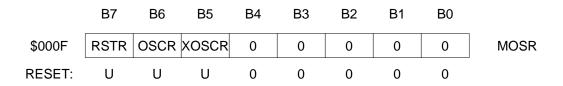

The three mask options on the MC68HC05G3 are: RSTR (RESET pin pullup resistor), OSCR (OSC feedback resistor), and XOSCR (XOSC feedback and damping resistors). The MC68HC705G4 has no mask options.

Figure 1-2: Pin Assignment for Single-Chip Mode

Figure 1-3: Memory Map of MC68HC05G3

Figure 1-4: Memory Map of MC68HC705G4

### 1.4 SYSTEM CONFIGURATIONS

The MC68HC05G3 (705G4) has several options. The sections below describe oscillator clocks, time base, and I/O pin configurations.

### 1.4.1 OSCILLATORS AND CLOCK DISTRIBUTIONS

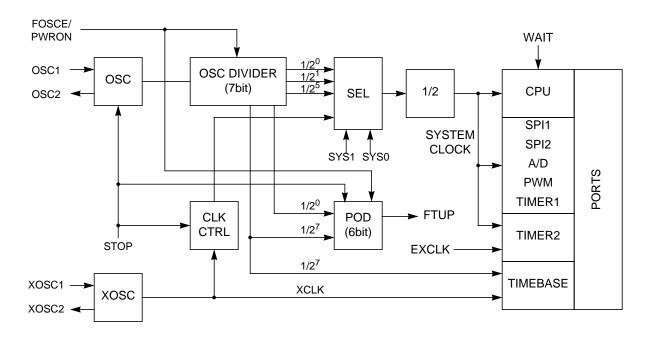

There are two oscillator blocks: OSC and XOSC. Several combinations of the clock distributions are allowed for the modules in the MC68HC05G3 (705G4). Refer to the following block diagram.

Figure 1-5: Clock Signal Distribution

### 1.4.1.1 OSC ON LINE

The main oscillator (OSC) can be stopped to conserve power via the STOP instruction or the FOSCE bit in the MISC register. The effects of restarting the OSC will vary depending on the current state of the MCU, including SYS0:1 and FOSCE.

If XOSC is not used, XOSC1 should be connected to either Vss or Vdd.

If OSC is the system clock, FOSCE should remain 1. Executing the STOP instruction in this condition will halt OSC, put the MCU into a low-power mode and clear the 6-bit power-on delay (POD) counter. The 7-bit divider is not initialized. Exiting STOP with external IRQ or reset re-starts the oscillator. When the POD counter overflows, internal reset is released and execution can begin. The stabilization time will vary between 8064 and 8192 counts.

NOTE: Exiting STOP with external reset will always return the MCU to the states defined by the register definitions, such as SYS0:1=0:0, FOSCE=1.

### 1.4.1.2 XOSC ON LINE

The secondary oscillator (XOSC) runs continuously after power-up.

If XOSC is the system clock (SYS0:1=1:1), OSC can be stopped either by the STOP instruction or by clearing the FOSCE bit.

The sub oscillator (XOSC) never stops except during power down. This clock also may be used as the source for the system clock and/or time base.

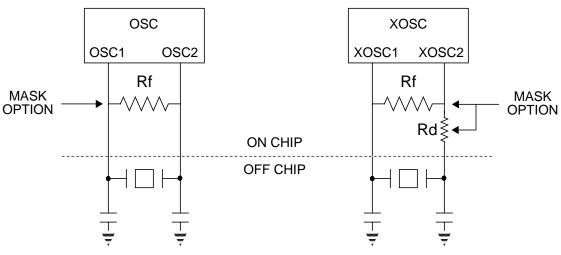

OSC and XOSC pins have options for feedback and damping resistor implementations. These options are set through mask option and may be read through the MOSR register.

Figure 1-6: OSC1/2 and XOSC1/2 Mask Options

### XOSC WITH FOSCE=1

If XOSC is the system clock and FOSCE=1, executing the STOP instruction will halt OSC, put the MCU into a low-power mode and clear the 6-bit POD counter. The 7-bit divider is not initialized. Exiting STOP with external IRQ re-starts the oscillator; however, execution begins immediately using XOSC. When the POD counter overflows, FTUP is set signaling that OSC is stable and OSC can be used as the system clock. The stabilization time will vary between 8064 and 8192 counts.

### **XOSC WITH FOSCE=0**

If XOSC is the system clock, clearing FOSCE will stop OSC and preset the 7-bit divider plus the 6-bit POD counter to \$0078. Execution will continue with XOSC, and when FOSCE is set again, OSC will re-start. When the POD counter overflows, FTUP is set signaling that OSC is stable and OSC can be used as the system clock. The stabilization time will be 8072 counts.

BHC05G3 (705G4) Sp**Errescale**, Semiconductor, Inc.

### **XOSC WITH FOSCE=0 AND STOP**

If XOSC is the system clock and FOSCE is cleared, further power reduction can be achieved by executing the STOP instruction. In this case, OSC is stopped, the 7-bit divider plus the 6-bit POD counter are preset to \$0078 (since FOSCE=0) and execution is halted. Exiting STOP with external IRQ does not re-start the OSC; however, execution begins immediately using XOSC. OSC may be re-started by setting FOSCE, and when the POD counter overflows, FTUP be will set signaling that OSC is stable and can be used as the system clock. The stabilization time will be 8072 counts.

### 1.4.1.3 OSC CLOCK DIVIDER AND POD COUNTER

The OSC clock is divided by a 7-bit counter which is used for the system clock, time base, and POD counter. Clocks divided by 2, 4, and 64 are available for the system clock selections and a clock divided by 128 is provided for the time base and POD counter.

The POD counter is a 6 bit-clock counter that is driven by the OSC divided by 128. The overflow of this counter is used for setting FTUP bit, release of power-on delay (POD), and resuming operation from stop mode.

The 7-bit divider plus the 6-bit POD counter are initialized to \$0078 by the following conditions.

- Power-on detection

- When FOSCE bit is cleared

### 1.4.1.4 SYSTEM CLOCK CONTROL

The system clock is provided for all internal modules except time base.

Both OSC and XOSC are available as the system clock source. The divide ratio is selected by the SYS1 and SYS0 bits in the MISC register.

By default OSC divided by two is selected on reset.

|                  |                  |                                                                                | FREQUENCY (HZ)            |                                   |                  |

|------------------|------------------|--------------------------------------------------------------------------------|---------------------------|-----------------------------------|------------------|

| SYS1             | SYS0             | DIVIDE RATIO                                                                   | OSC=<br>4.0M              | OSC=<br>4.1943M                   | XOSC=<br>32.768K |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | OSC DIVIDED BY 2<br>OSC DIVIDED BY 4<br>OSC DIVIDED BY 64<br>XOSC DIVIDED BY 2 | 2.0M<br>1.0M<br>62.5K<br> | 2.0972M<br>1.0486M<br>65.536K<br> | <br><br>16.384K  |

### Table 1-1: System Clock Frequency

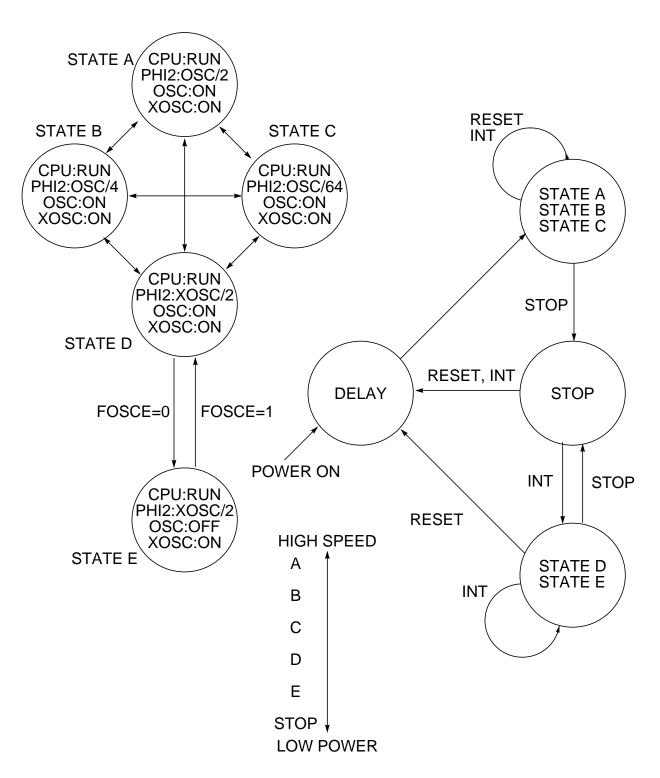

### 1.4.1.5 STOP AND WAIT MODES

During stop mode, the main oscillator (OSC) is shut down and the clock pass from the second oscillator (XOSC) is disconnected so that all modules except time base are halted. Entering stop mode clears FTUP flag in the MISC register and initializes the POD counter. The stop mode is exited by the RESET, IRQ1/2, KWI, SPI1/2 (slave mode), or TB interrupt (TBCLK=0).

If OSC is selected as the system clock source during stop mode, CPU resumes after the overflow of the POD counter and this overflow sets FTUP status flag.

If XOSC is selected as system clock source during stop mode, no stop recovery time is required for exiting stop mode because XOSC never stops and re-start of main oscillator depends on FOSCE bit.

During wait mode, only the CPU clocks are halted and the peripheral modules are bit affected. The wait mode is exited by RESET or any interrupts.

| BEFORE RESET     |                    |                   |          | EXIT STOP            |                    |

|------------------|--------------------|-------------------|----------|----------------------|--------------------|

| CPU CLOCK SOURCE | STOP               | FOSCE             | POWER ON | EXTERNAL<br>RESET    | MODE BY            |

|                  |                    |                   | WAIT     |                      |                    |

| OSC (OSC ON)     | OUT                | 1                 |          | NO WAIT              |                    |

| OSC (OSC OFF)    | OUT<br>IN<br>IN *2 | 0 *1<br>1<br>0 *2 |          | WAIT<br>WAIT<br>WAIT | WAIT<br>WAIT       |

| XOSC (OSC ON)    | OUT                | 1                 |          | NO WAIT              |                    |

| XOSC (OSC OFF)   | OUT<br>IN<br>IN    | 0<br>1<br>0       |          | WAIT<br>WAIT<br>WAIT | NO WAIT<br>NO WAIT |

### Table 1-2: Recovery Time Requirements

\*1 THIS CASE HAS NO MEANING FOR THE APPLICATIONS

\*2 THIS CASE NEVER OCCURS

Figure 1-7: Clock State and STOP/POD Delay Diagram

### 1.4.1.6 **TIME BASE**

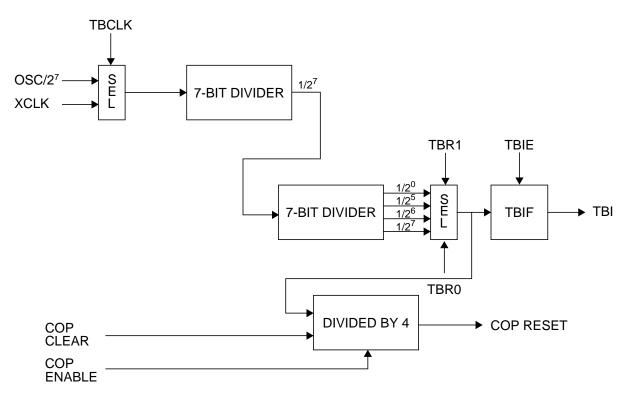

Time base is a 14-bit up counter which is clocked by XOSC input or OSC input divided by 128. The TBCLK bit in the TBCR1 register selects the clock source.

This divider is initialized to \$0078 only on power-on delay. After counting 8072 clocks, STUP bit in the MISC register is set.

Figure 1-8: Time Base Clock Divider

The divided clocks from the time base are used as follows:

- STUP Time base divider is initialized to \$0078 by the power-on detection. When the count reaches 8072, the STUP flag in the MISC register is set. Once STUP flag is set, it is never cleared until power down.

- TBI Time base interrupt may be generated at every 0.5, 0.25, 0.125, or 0.0039 seconds with 32.768 KHz crystal at XOSC pins.

Time base interrupt flag (TBIF) is set at every period and interrupt is requested if the enable bit (TBIE) is set. The clock divided by 128, 4096, 8192, or 16,384 is used to set TBIF, and this clock is selected by the TBR1 and TBRO bits in the TBCR2 register.

|                  |                  |                                                                                                   | FREQUENCY (HZ)              |                             | HZ)                         |

|------------------|------------------|---------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|

| TBR1             | TBR0             | DIVIDE RATIO                                                                                      | OSC=<br>4.0M                | OSC=<br>4.1943M             | XOSC=<br>32.768K            |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | TBCLK DIVIDED BY 128<br>TBCLK DIVIDED BY 4096<br>TBCLK DIVIDED BY 8192<br>TBCLK DIVIDED BY 16,384 | 244<br>7.63<br>3.81<br>1.91 | 256<br>8.00<br>4.00<br>2.00 | 256<br>8.00<br>4.00<br>2.00 |

Table 1-3: TB Interrupt Frequency

COP

The computer operating properly (COP) watchdog timer is controlled by the COPE and COPC bits in the TBCR2 register.

The COP uses the same clock as TBI that is selected by the TBR1 and TBR0 bits. The TBI is divided by four and overflow of this divider generates COP timeout reset if the COP enable (COPE) bit is set. The COP timeout reset has the same vector address as POD and external RESET. To prevent the COP timeout, the COP divider is cleared by writing a one to the COP clear (COPC) bit.

When the time base divider is driven by the OSC clock, the clock for the divider is suspended during stop mode or when FOSCE is 0. This may cause COP period stretching or no COP timeout reset when processing errors occur. To avoid these problems, it is recommended that XOSC clock be used for the COP functions.

When the time base (COP) divider is driven by the XOSC clock, the divider does not stop counting and the COPC bit must be triggered to prevent the COP timeout.

|                  |                  |                            | COP PERIOD (MILLI-SECOND)   |                            |                             |                            |                             |  |

|------------------|------------------|----------------------------|-----------------------------|----------------------------|-----------------------------|----------------------------|-----------------------------|--|

|                  |                  | OSC=4.0MHz                 |                             | OSC=4.1                    | 943MHz                      | XOSC=32                    | 2.768KHz                    |  |

| TBR1             | TBR0             | MIN                        | МАХ                         | MIN                        | МАХ                         | MIN                        | МАХ                         |  |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 12.3<br>393<br>786<br>1573 | 16.4<br>524<br>1048<br>2097 | 11.7<br>375<br>750<br>1500 | 15.6<br>500<br>1000<br>2000 | 11.7<br>375<br>750<br>1500 | 15.6<br>500<br>1000<br>2000 |  |

### Table 1-4: COP Timeout Period

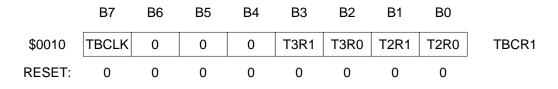

### 1.4.1.7 TIME BASE CONTROL REGISTER 1 (TBCR1)

READ: anytime

WRITE: anytime (Only one-time write is allowed on bit 7 after reset.)

### TBCLK Time Base Clock

The TBCLK bit selects time base clock source. This bit is cleared at reset. After reset, write to this bit is allowed only once.

0 - XOSC clock is selected

1 - OSC clock divided by 128 is selected

### BITS 6-4 Reserved

These bits are not used and always read as zero.

### T3R1/0 Prescale Rate or Clock select bits for PWM

These 2 bits select the clock for the PWM. (See 8.5.5 TIMER BASE CONTROL REGISTER 1 (TBCR1).)

### T2R1/0 Preschool Rate Select bits for Timer 2

These 2 bits select the timer 2 clock rate. (See **8.5.5 TIMER BASE CONTROL REGISTER 1 (TBCR1)**.)

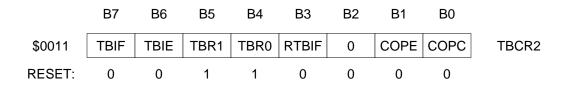

### 1.4.1.8 TIME BASE CONTROL REGISTER 2 (TBCR2)

READ: anytime (Bits 3 and 0 are write-only bits and always read as zero.)

WRITE: anytime (Bit 7 is a read-only bit and write has no effect; bit 1 is a one-time write bit.)

BHC05G3 (705G4) Sp**Erressale**, Semiconductor, Inc.

### TBIF Time Base Interrupt Flag

The TBIF bit is set every timeout interval of the time base. This is a read-only bit and is cleared by writing a one to the RTBIF bit. Reset clears the TBIF bit. Time base interrupt period between reset and first TBIF depends on the time elapsed during reset, since the time base divider is not initialized by reset.

### TBIE Time Base Interrupt Enable

The TBIE bit enables the time base interrupt capability. If TBIF = 1 and TBIE = 1, the time base interrupt is generated.

- 0 TB interrupt is disabled

- 1 TB interrupt requested when TBIF = 1

### TBR1/0Time Base Interrupt Rate Select

The TBR1 and TBR0 bits select one of four rates for the time base interrupt period. The TB interrupt rate is also related to the COP reset period. These bits are set to one by reset.

|                  |                  |                                                                                                   | FREQUENCY (HZ)              |                             | HZ)                         |

|------------------|------------------|---------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|

| TBR1             | TBR0             | DIVIDE RATIO                                                                                      | OSC=<br>4.0M                | OSC=<br>4.1943M             | XOSC=<br>32.768K            |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | TBCLK DIVIDED BY 128<br>TBCLK DIVIDED BY 4096<br>TBCLK DIVIDED BY 8192<br>TBCLK DIVIDED BY 16,384 | 244<br>7.63<br>3.81<br>1.91 | 256<br>8.00<br>4.00<br>2.00 | 256<br>8.00<br>4.00<br>2.00 |

### RTBIF Reset TB Interrupt Flag

The RTBIF bit is a write-only bit and always read as zero. Writing a one to this bit clears the TBIF bit and writing zero to this bit has no effect.

### BIT 2 Reserved

This bit is not used and always read as zero.

### COPE COP Enable

When the COPE bit is 1, COP reset function is enabled. This bit is cleared by the reset (including COP reset) and write to this bit is allowed only one time after reset.

### COPC COP Clear

Writing a one to COPC bit clears the 2-bit divider to prevent COP timeout. (The COP timeout period depends on the TB interrupt rate.) This bit is write-only and returns to zero when read.

### 1.4.1.9 MISCELLANEOUS REGISTER (MISC)

|        | B7   | B6   | B5 | B4 | B3   | B2   | B1    | B0   |      |

|--------|------|------|----|----|------|------|-------|------|------|

| \$003E | FTUP | STUP | 0  | 0  | SYS1 | SYS0 | FOSCE | OPTM | MISC |

| RESET: | *    | *    | 0  | 0  | 0    | 0    | 1     | 0    |      |

- READ: anytime

- WRITE: Bits 7-4: no effect Bits 3-1: anytime (Software must take care of changing these bits.) Bit 0: anytime

### FTUP OSC Time Up Flag

Power-on detection and clearing FOSCE bit clears this bit. This bit is set by the overflow of the POD counter. The external reset does not affect this bit.

### READ:

- 0 during POD or OSC shut down

- 1 OSC clock is available for the system clock

### STUP XOSC Time Up Flag