# 68HC705RC17

# **General Release Specification**

May 20, 1997

CSIC MCU Design Center Austin, Texas

### **General Release Specifiation**

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

General Release Specification

MC68HC705RC17 - Rev. 2.0

# General Release Specification — MC68HC705RC17

# **List of Sections**

| Section 1. General Description                     |

|----------------------------------------------------|

| Section 2. Memory                                  |

| Section 3. Central Processor Unit (CPU)            |

| Section 4. Interrupts                              |

| Section 5. Resets                                  |

| Section 6. Low-Power Modes 51                      |

| Section 7. Parallel Input/Output (I/O)             |

| Section 8. Core Timer 59                           |

| Section 9. Carrier Modulator Transmitter (CMT) 65  |

| Section 10. Phase-Locked Loop (PLL) Synthesizer 83 |

| Section 11. EPROM 89                               |

| Section 12. Instruction Set                        |

| Section 13. Electrical Specifications              |

| Section 14. Mechanical Specifications 121          |

| Section 15. Ordering Information                   |

|                                                    |

MC68HC705RC17 - Rev. 2.0

List of Sections

General Release Specification

MC68HC705RC17 — Rev. 2.0

# General Release Specification — MC68HC705RC17

# **Table of Contents**

### **Section 1. General Description**

| 1.1    | Contents                                           |

|--------|----------------------------------------------------|

| 1.2 l  | ntroduction                                        |

| 1.3 F  | Features                                           |

| 1.4    | Options                                            |

| 1.5    | Signal Description                                 |

| 1.5.1  | V <sub>DD</sub> and V <sub>SS</sub>                |

| 1.5.2  | IRQ/V <sub>PP</sub> (Maskable Interrupt Request)20 |

| 1.5.3  | OSC1 and OSC2                                      |

| 1.5.4  | RESET                                              |

| 1.5.5  | <u>LPRST</u>                                       |

| 1.5.6  | IRO                                                |

| 1.5.7  | Port A (PA0–PA7)                                   |

| 1.5.8  | Port B (PB0–PB7)                                   |

| 1.5.9  | Port C (PC0–PC1 and PC4–PC7)22                     |

| 1.5.10 | XFC                                                |

| 1.5.11 | V <sub>DDSYN</sub>                                 |

|        |                                                    |

|        | Section 2. Memory                                  |

| 2.1    | Contents                                           |

| 2.2 l  | ntroduction                                        |

| 2.3 N  | Memory Map25                                       |

| 2.3.1  | EPROM                                              |

| 2.3.2  | EPROM Security                                     |

| 2.3.3  | RAM                                                |

| 2.3.4  | Bootloader ROM                                     |

| 2.4 I  | nput/Output Programming                            |

MC68HC705RC17 - Rev. 2.0

## Table of Contents

|                               | Section 3. Central Processor Unit (CPU)                           |

|-------------------------------|-------------------------------------------------------------------|

| 3.1                           | Contents                                                          |

| 3.2                           | Introduction                                                      |

| 3.3                           | CPU Registers                                                     |

| 3.4                           | Accumulator                                                       |

| 3.5                           | Index Register                                                    |

| 3.6                           | Condition Code Register                                           |

| 3.7                           | Stack Pointer                                                     |

| 3.8                           | Program Counter                                                   |

|                               | Section 4. Interrupts                                             |

| 4.1                           | Contents                                                          |

| 4.2                           | Introduction                                                      |

| 4.3                           | CPU Interrupt Processing38                                        |

| 4.4                           | Reset Interrupt Sequence39                                        |

| 4.5                           | Software Interrupt (SWI)39                                        |

| 4.6                           | Hardware Interrupts                                               |

| 4.7                           | External Interrupt (IRQ/Port B Keyscan)                           |

| 4.8                           | External Interrupt Timing42                                       |

| 4.9                           | Carrier Modulator Transmitter Interrupt (CMT)42                   |

| 4.10                          | Core Timer Interrupt                                              |

|                               | Section 5. Resets                                                 |

| 5.1                           | Contents                                                          |

| 5.2                           | Introduction                                                      |

| 5.3                           | External Reset (RESET)46                                          |

| 5.4                           | Low-Power External Reset (\( \overline{LPRST} \))48               |

| 5.5                           | Internal Resets                                                   |

| 5.5.1<br>5.5.2                | Power-On Reset (POR)48 Computer Operating Properly Reset (COPR)49 |

| 5.5.2.                        |                                                                   |

| General Release Specification | MC68HC705RC17 — Rev. 2.0                                          |

| MC68HC705RC17 - | – Rev. 2.0         | General Release Specification                  |

|-----------------|--------------------|------------------------------------------------|

|                 | 9.3                | Overview                                       |

|                 | 9.2                | Introduction                                   |

|                 | 9.1                | Contents                                       |

|                 |                    | Section 9. Carrier Modulator Transmitter (CMT) |

|                 | 0.0                | Timer builing wait wode                        |

|                 | 8.6                | Timer During Wait Mode                         |

|                 | 8.5                | Computer Operating Properly (COP) Reset        |

|                 | 8.4                | Core Timer Control and Status Register         |

|                 | 8.3                | Core Timer Control and Status Register         |

|                 | 8.1<br>8.2         | Contents            Introduction               |

|                 | 0 1                |                                                |

|                 |                    | Section 8. Core Timer                          |

|                 | 7.6                | Input/Output (I/O) Programming                 |

|                 | 7.5                | Port C                                         |

|                 | 7.4                | Port B                                         |

|                 | 7.3                | Port A                                         |

|                 | 7.2                | Introduction                                   |

|                 | 7.1                | Contents                                       |

|                 |                    | Section 7. Parallel Input/Output (I/O)         |

|                 | 6.5                | Low-Power Reset                                |

|                 | 6.4                | Wait Mode                                      |

|                 | 6.3                | Stop Mode                                      |

|                 | 6.2                | Introduction                                   |

|                 | 6.1                | Contents                                       |

|                 |                    | Section 6. Low-Power Modes                     |

|                 | 5.5.3              | Illegal Address50                              |

|                 | 5.5.2.4            |                                                |

|                 | 5.5.2.2<br>5.5.2.3 | 3                                              |

|                 | 5529               | COR During Wait Mode                           |

## Table of Contents

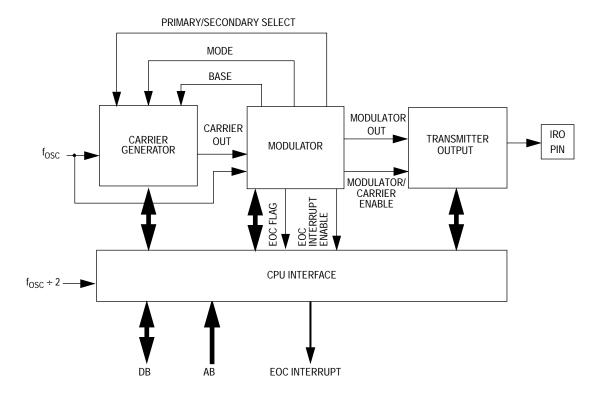

|                             | 9.4    | Carrier Generator                              | .68   |

|-----------------------------|--------|------------------------------------------------|-------|

|                             | 9.4.1  | Time Counter                                   | .69   |

|                             | 9.4.2  | Carrier Generator Data Registers               | .70   |

|                             | 9.5    | Modulator                                      | .72   |

|                             | 9.5.1  | Time Mode                                      | .73   |

|                             | 9.5.2  | FSK Mode                                       | .75   |

|                             | 9.5.3  | Extended Space Operation                       | .76   |

|                             | 9.5.3. |                                                |       |

|                             | 9.5.3. | <b>.</b>                                       |       |

|                             | 9.5.4  | Modulator Period Data Registers                | .81   |

|                             | S      | ection 10. Phase-Locked Loop (PLL) Synthesizer |       |

|                             | 10.1   | Contents                                       | .83   |

|                             | 10.2   | Introduction                                   | .83   |

|                             | 10.3   | Phase-Locked Loop Control Register             | .85   |

|                             | 10.4   | Operation During Stop Mode                     | .87   |

|                             | 10.5   | Noise Immunity                                 | .87   |

|                             |        | Section 11. EPROM                              |       |

|                             | 11.1   | Contents                                       | .89   |

|                             | 11.2   | Introduction                                   | .89   |

|                             | 11.3   | EPROM                                          | .89   |

|                             | 11.4   | Bootloader                                     | .90   |

|                             | 11.4.1 | Bootloader Functions                           | .90   |

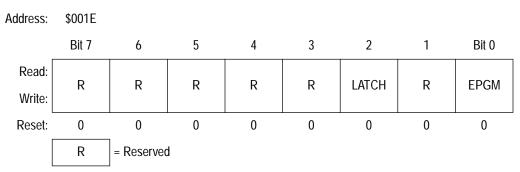

|                             | 11.4.2 | Programming Register                           | .91   |

|                             | 11.4.3 | Mask Option Registers (MOR1 and MOR2)          | .94   |

|                             |        | Section 12. Instruction Set                    |       |

|                             | 12.1   | Contents                                       | .97   |

|                             | 12.2   | Introduction                                   | .98   |

|                             | 12.3   | Addressing Modes                               | .98   |

|                             | 12.3.1 |                                                |       |

|                             | 12.3.2 | Immediate                                      | .99   |

|                             | 12.3.3 | Direct                                         | .99   |

| General Release Specificati | ion    | MC68HC705RC17 — Rev                            | . 2.0 |

**Table of Contents**

**Table of Contents**

| 12.3.4 |                                                 |

|--------|-------------------------------------------------|

| 12.3.5 |                                                 |

| 12.3.6 | •                                               |

| 12.3.7 | •                                               |

| 12.3.8 | Relative                                        |

| 12.4   | Instruction Types                               |

| 12.4.1 | Register/Memory Instructions                    |

| 12.4.2 |                                                 |

| 12.4.3 | •                                               |

| 12.4.4 |                                                 |

| 12.4.5 |                                                 |

| 12.5   | Instruction Set Summary108                      |

| 12.6   | Opcode Map                                      |

|        |                                                 |

|        | Section 13. Electrical Specifications           |

| 13.1   | Contents                                        |

| 13.2   | Introduction115                                 |

| 13.3   | Maximum Ratings116                              |

| 13.4   | Operating Range117                              |

| 13.5   | Thermal Characteristics                         |

| 13.6   | DC Electrical Characteristics (5.0 Vdc)118      |

| 13.7   | DC Electrical Characteristics (3.3 Vdc)119      |

| 13.8   | Control Timing (3.3 Vdc and 5.0 Vdc)            |

|        |                                                 |

|        | Section 14. Mechanical Specifications           |

| 14.1   | Contents                                        |

| 14.2   | Introduction                                    |

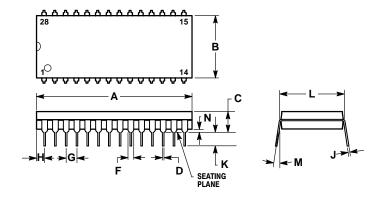

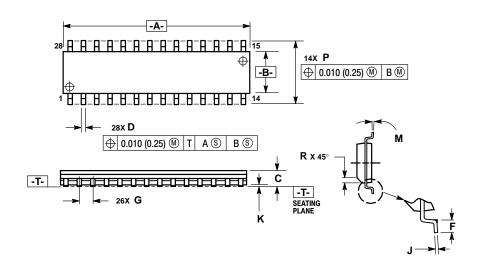

| 14.3   | 28-Pin Plastic Dual In-Line Package             |

|        | (Case 710-02)                                   |

| 14.4   | 28-Pin Small Outline Integrated Circuit Package |

|        | (Case 751F-04)                                  |

MC68HC705RC17 - Rev. 2.0

## Table of Contents

### **Section 15. Ordering Information**

| 15.1 | Contents             | 123 |

|------|----------------------|-----|

| 15.2 | Introduction         | 123 |

| 15.3 | Ordering Information | 123 |

General Release Specification

MC68HC705RC17 - Rev. 2.0

# General Release Specification — MC68HC705RC17

# **List of Figure**

| Title P                                            | age                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MC68HC705RC17 Block Diagram                        | .17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 28-Pin SOIC Pinout                                 | .19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 28-Pin PDIP Pinout                                 | .19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Oscillator Connections                             | .21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MC68HC705RC17 Memory Map                           | .26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I/O Registers                                      | .27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Programming Model                                  | .32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Stacking Order                                     | .32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Interrupt Processing Flowchart                     | .40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| IRQ Function Block Diagram                         | .41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Reset Block Diagram                                | .46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Reset and POR Timing Diagram                       | .47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Stop Recovery Timing Diagram                       | .52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

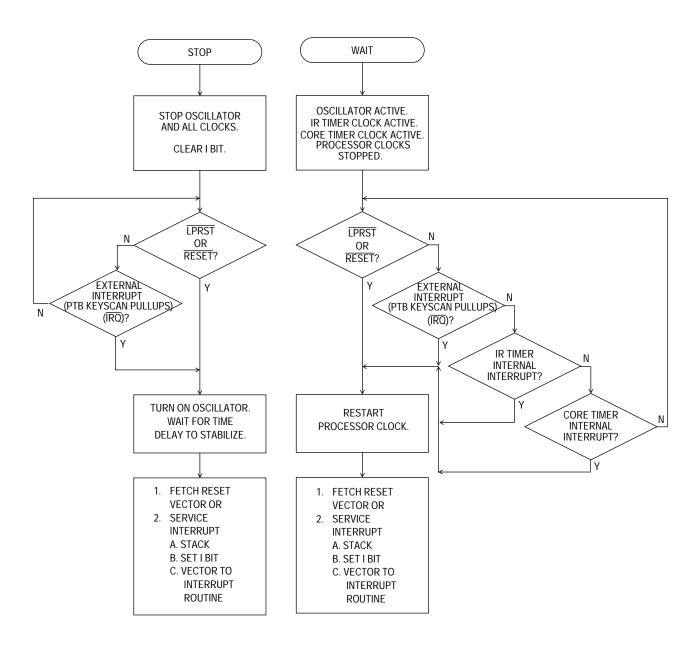

| Stop/Wait Flowchart                                | .53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Port B Pullup Option                               | .56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| I/O Circuitry                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Core Timer Block Diagram                           | .60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Core Timer Control and Status Register (CTCSR)     | .61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Core Timer Counter Register (CTCR)                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

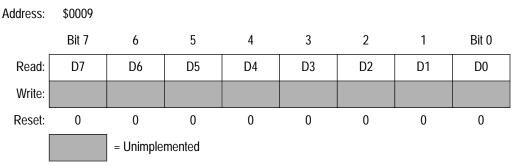

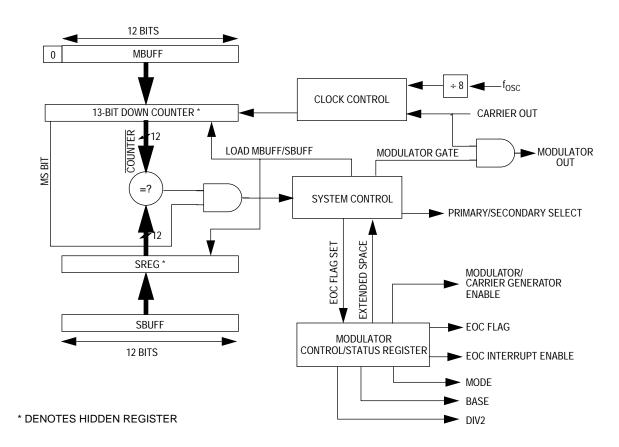

| Carrier Modulator Transmitter Module Block Diagram | .67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Carrier Generator Block Diagram                    | .68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| General Release Specific                           | ation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                    | MC68HC705RC17 Block Diagram 28-Pin SOIC Pinout 28-Pin PDIP Pinout Oscillator Connections  MC68HC705RC17 Memory Map I/O Registers  Programming Model Stacking Order  Interrupt Processing Flowchart. IRQ Function Block Diagram  Reset Block Diagram Reset and POR Timing Diagram  Stop Recovery Timing Diagram Stop/Wait Flowchart  Port B Pullup Option I/O Circuitry  Core Timer Block Diagram  Core Timer Control and Status Register (CTCSR) Core Timer Counter Register (CTCR)  Carrier Modulator Transmitter Module Block Diagram. |

# List of Figure

| Figure | Title                                        | Page |

|--------|----------------------------------------------|------|

| 9-3    | Carrier Data Register                        |      |

|        | (CHR1, CLR1, CHR2, and CLR2)                 |      |

| 9-4    | Modulator Block Diagram                      |      |

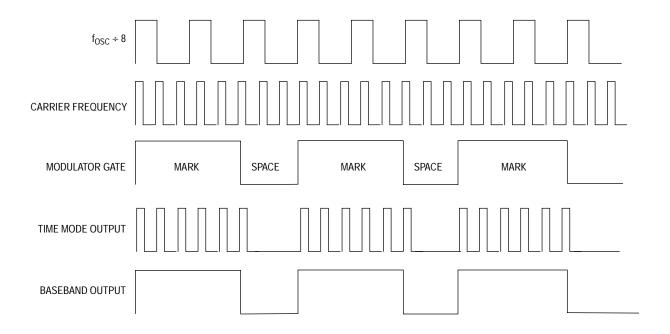

| 9-5    | CMT Operation in Time Mode                   |      |

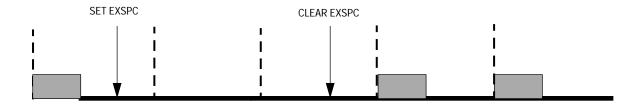

| 9-6    | Extended Space Operation                     |      |

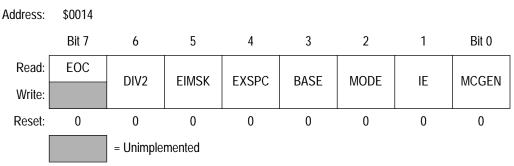

| 9-7    | Modulator Control and Status Register (MCSR) |      |

| 9-8    | Modulator Data Registers                     |      |

|        | (MDR1, MDR2, and MDR3)                       | 81   |

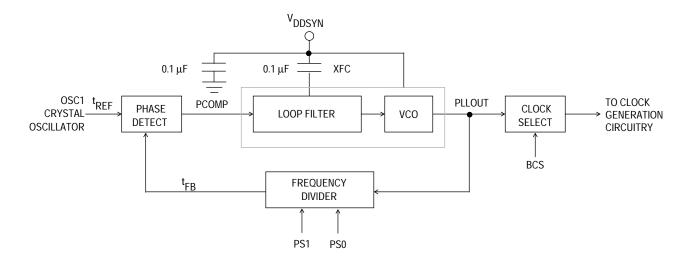

| 10-1   | PLL Circuit                                  |      |

| 10-2   | Phase-Locked Loop Control Register (PLLCR)   |      |

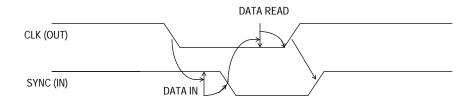

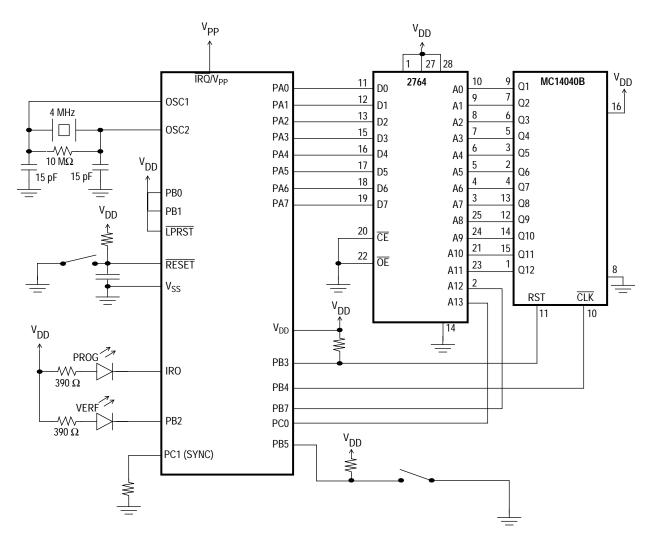

| 11-1   | Programmer Interface to Host                 |      |

| 11-2   | Programming Register (PROG)                  | 91   |

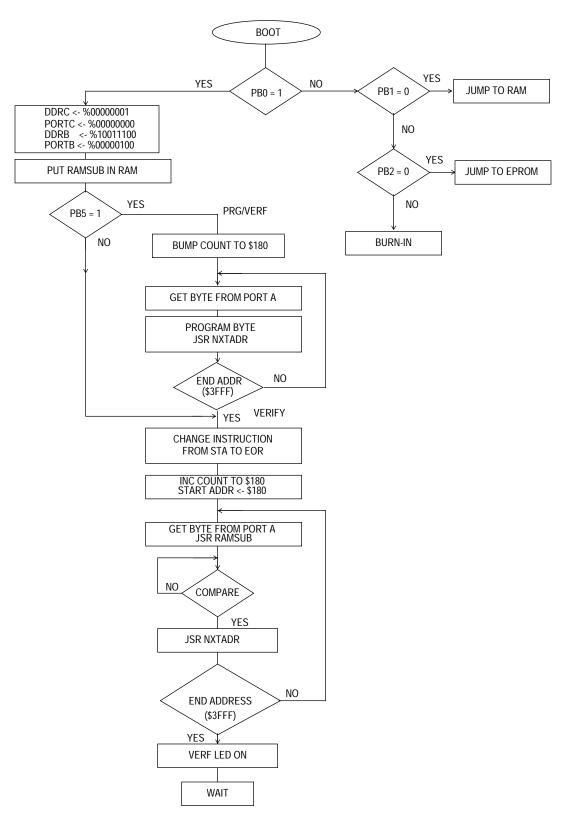

| 11-3   | MC68HC705RC17 Bootloader Flowchart           | 92   |

| 11-4   | MC68HC705RC17 Programming Circuit            |      |

| 11-5   | Mask Option Register 1 (MOR1)                | 94   |

| 11-6   | Mask Option Register 2 (MOR2)                | 94   |

# General Release Specification — MC68HC705RC17

# **List of Tables**

| Table                                                | Title Page                                                                                                                                                                                    |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4-1                                                  | Vector Address for Interrupts and Reset                                                                                                                                                       |

| 5-1                                                  | COP Watchdog Timer Recommendations                                                                                                                                                            |

| 7-1                                                  | I/O Pin Functions                                                                                                                                                                             |

| 8-1                                                  | RTI and COP Rates at 4.096-MHz Oscillator62                                                                                                                                                   |

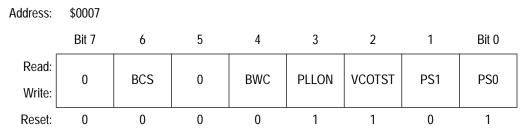

| 10-1                                                 | PS1 and PS0 Speed Selects with 32.768-kHz Crystal 86                                                                                                                                          |

| 11-1                                                 | Bootloader Functions                                                                                                                                                                          |

| 12-1<br>12-2<br>12-3<br>12-4<br>12-5<br>12-6<br>12-7 | Register/Memory Instructions102Read-Modify-Write Instructions103Jump and Branch Instructions105Bit Manipulation Instructions106Control Instructions107Instruction Set Summary108Opcode Map114 |

| 15-1                                                 | MC Order Numbers                                                                                                                                                                              |

MC68HC705RC17 - Rev. 2.0

List of Tables

reescale Semiconductor, Inc.

General Release Specification

MC68HC705RC17 — Rev. 2.0

#### General Release Specification — MC68HC705RC17

# Section 1. General Description

#### 1.1 Contents

| 1.2    | Introduction                                     |

|--------|--------------------------------------------------|

| 1.3    | Features                                         |

| 1.4    | Options                                          |

| 1.5    | Signal Description18                             |

| 1.5.1  | V <sub>DD</sub> and V <sub>SS</sub>              |

| 1.5.2  | IRQ/V <sub>PP</sub> (Maskable Interrupt Request) |

| 1.5.3  | OSC1 and OSC2                                    |

| 1.5.4  | RESET21                                          |

| 1.5.5  | <u>LPRST</u> 21                                  |

| 1.5.6  | IRO                                              |

| 1.5.7  | Port A (PA0–PA7)                                 |

| 1.5.8  | Port B (PB0–PB7)                                 |

| 1.5.9  | Port C (PC0–PC1 and PC4–PC7)22                   |

| 1.5.10 | XFC                                              |

| 1.5.11 | V <sub>DDSYN</sub>                               |

#### 1.2 Introduction

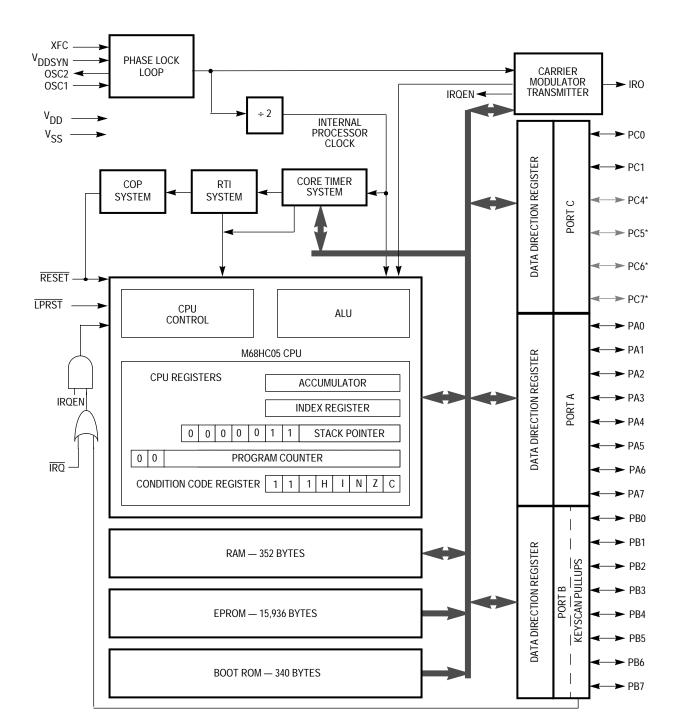

The MC68HC705RC17 is a general-purpose, low-cost addition to the M68HC05 Family of microcontroller units (MCUs) and is suitable for remote control applications. It contains the HC05 central processing unit (CPU) core, including the 14-stage core timer with real-time interrupt (RTI), computer operating properly (COP) watchdog systems, and a programmable phase-lock loop (PLL) synthesizer. On-chip peripherals include a carrier modulator transmitter. The 16-Kbyte memory map has 15,936 bytes of user EPROM, 340 bytes of boot ROM, and 352 bytes of RAM. There are 18 input-output (I/O) lines (eight having keyscan logic and pullups) and a low-power reset pin.

MC68HC705RC17 - Rev. 2.0

### **General Description**

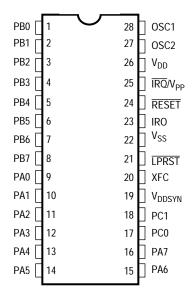

The MC68HC705RC17 is available in 28-pin small outline integrated circuit (SOIC) or plastic dual in-line package (PDIP) packages. Four additional I/O lines are available for bond out in higher pin count packages.

**NOTE:** Consult the factory for availability of higher pin count packages.

#### 1.3 Features

#### Features of the MC68HC705RC17 include:

- Low Cost

- HC05 Core

- 28-Pin SOIC or DIP Packages

- On-Chip Oscillator with 32.768-kHz Crystal/Ceramic Resonator

- Phase-Locked Loop (PLL) Synthesizer with Programmable Speed

- 15,936 Bytes of User ROM

- 64 Bytes of Burn-In ROM

- 352 Bytes of On-Chip RAM

- 14-Stage Core Timer with Real-Time Interrupt (RTI) and Computer Operating Properly (COP) Watchdog Circuits

- Carrier Modulator Transmitter Supporting Baseband, Pulse Length Modulator (PLM), and Frequency Shift Keying (FSK) Protocols

- Low-Power Reset Pin

- 18 Bidirectional I/O Lines (Four Additional I/O Lines Available for Bond Out in Higher Pin Count Packages)

- Programmable Pullups and Interrupt on Eight Port Pins (PB0–PB7)

- High-Current Infrared (IR) Drive Pin

- High-Current Port Pin (PC0)

General Release Specification

MC68HC705RC17 — Rev. 2.0

General Description Features

<sup>\*</sup> Marked pins are available only in higher pin count (>28) packages.

Figure 1-1. MC68HC705RC17 Block Diagram

MC68HC705RC17 — Rev. 2.0

### **General Description**

- Power-Saving Stop and Wait Modes

- Programmable Options:

- COP Watchdog Timer

- STOP Instruction Disable

- Edge-Sensitive or Edge- and Level-Sensitive Interrupt Trigger

- Port B Pullups for Keyscan

- Illegal Address Reset

- ROM Security

**NOTE:** A line over a signal name indicates an active-low signal. For example, RESET is active low.

### 1.4 Options

The options on the MC68HC705RC17 are handled with 11 EPROM bits in two separate mask option register (MOR1 and MOR 2). These options are:

- Eight Port B Pullups

- IRQ Sensitivity

- COP Enable/Disable

- STOP Enable/Disable

The factory will program these options in the ROM versions of this device.

### 1.5 Signal Description

Pinout for the 28-pin small outline integrated circuit (SOIC) package is shown in **Figure 1-2**. Pinout for the 28-pin plastic dual in-line (PDIP) package is shown in **Figure 1-3**. The signals are described in the following subsections.

**NOTE:** Consult the factory for availability of higher pin count packages.

General Release Specification

MC68HC705RC17 — Rev. 2.0

#### 1.5.1 $V_{DD}$ and $V_{SS}$

Power is supplied to the microcontroller's digital circuits using these two pins.  $V_{DD}$  is the positive supply and  $V_{SS}$  is ground.

Figure 1-2. 28-Pin SOIC Pinout

Figure 1-3. 28-Pin PDIP Pinout

### **General Description**

#### 1.5.2 IRQ/V<sub>PP</sub> (Maskable Interrupt Request)

This pin supplies the EPROM with the required programming voltage. In addition, this pin serves as the input for external interrupts. Triggering sensitivity is programmable using MOR1. The options are:

- Negative edge-sensitive triggering only

- 2. Both negative edge-sensitive and level-sensitive triggering

The MCU completes the current instruction before it responds to the interrupt request. When  $\overline{IRQ}$  goes low for at least one  $t_{ILIH}$ , a logic 1 is latched internally to signify that an interrupt has been requested. When the MCU completes its current instruction, the interrupt latch is tested. If the interrupt latch contains a logic 1 and the interrupt mask bit (I bit) in the condition code register is clear, the MCU then begins the interrupt sequence.

If the option is selected to include level-sensitive triggering, the  $\overline{IRQ}$  input requires an external resistor to  $V_{DD}$  for wired-OR operation.

The IRQ pin contains an internal Schmitt trigger as part of its input to improve noise immunity.

Refer to **Section 4. Interrupts** for more detail.

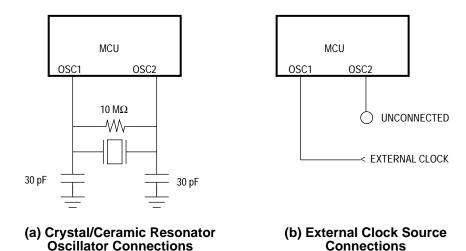

#### 1.5.3 OSC1 and OSC2

These pins provide control input for an on-chip clock oscillator circuit. A crystal, a ceramic resonator, or an external signal connects to these pins to provide a system clock. The oscillator frequency is two times the internal bus rate.

**Figure 1-4** shows the recommended circuit when using a crystal. The crystal and components should be mounted as close as possible to the input pins to minimize output distortion and startup stabilization time.

A ceramic resonator may be used in place of the crystal in cost-sensitive applications. **Figure 1-4 (a)** shows the recommended circuit for using a ceramic resonator. The manufacturer of the particular ceramic resonator being considered should be consulted for specific information.

General Release Specification

MC68HC705RC17 - Rev. 2.0

General Description Signal Description

An external clock should be applied to the OSC1 input with the OSC2 pin not connected (see **Figure 1-4 (b)**). This setup can be used if the user does not want to run the CPU with a crystal.

**NOTE:** The PLL design requires a 32.768-kHz external frequency for proper operation.

Figure 1-4. Oscillator Connections

1.5.4 **RESET**

This active-low pin is used to reset the MCU to a known startup state by pulling RESET low. The RESET pin contains an internal Schmitt trigger as part of its input to improve noise immunity. See Section 5. Resets.

1.5.5 **LPRST**

The <u>LPRST</u> pin is an active-low pin and is used to put the MCU into low-power reset mode. In low-power reset mode the MCU is held in reset with all processor clocks halted. See <u>Section 5</u>. Resets.

MC68HC705RC17 - Rev. 2.0

### **General Description**

#### 1.5.6 IRO

The IRO pin is the high-current source and sink output of the carrier modulator transmitter subsystem which is suitable for driving infrared (IR) LED biasing logic. See **Section 9. Carrier Modulator Transmitter (CMT)**.

#### 1.5.7 Port A (PA0-PA7)

These eight I/O lines comprise port A. The state of any pin is software programmable and all port A lines are configured as inputs during power-on or reset. For detailed information on I/O programming, see Section 7. Parallel Input/Output (I/O).

#### 1.5.8 Port B (PB0-PB7)

These eight I/O lines comprise port B. The state of any pin is software programmable and all port B lines are configured as inputs during power-on or reset. Each port B I/O line has a mask optionable pullup for keyscan. For detailed information on I/O programming, see **Section 7**. **Parallel Input/Output (I/O)**.

#### 1.5.9 Port C (PC0-PC1 and PC4-PC7)

These six I/O lines comprise port C. PC0 is a high-current pin. PC4 through PC7 are available only in higher pin count (>28) packages. The state of any pin is software programmable and all port C lines are configured as input during power-on or reset. For detailed information on I/O programming, see Section 7. Parallel Input/Output (I/O).

#### **NOTE:**

Only two bits of port C are bonded out in 28-pin packages for the MC68HC705RC17, although port C is truly a 6-bit port. Since pins PC4–PC7 are unbonded, software should include the code to set their respective data direction register locations to outputs to avoid floating inputs.

General Release Specification

MC68HC705RC17 - Rev. 2.0

General Description Signal Description

1.5.10 XFC

This pin provides a means for connecting an external filter capacitor to the synthesizer phase-locked loop filter. (For additional information concerning this capacitor, refer to **Section 10. Phase-Locked Loop (PLL) Synthesizer**.)

$1.5.11 V_{DDSYN}$

This pin provides a separate power connection to the PLL synthesizer which should be at the same potential as  $V_{DD}$ .

**NOTE:**

Any unused inputs, I/O ports, and no connects should be tied to an appropriate logic level (either  $V_{DD}$  or  $V_{SS}$ ). Although the I/O ports of the MC68HC705RC17 do not require termination, termination is recommended to reduce the possibility of static damage.

# **General Description**

### General Release Specification — MC68HC705RC17

# Section 2. Memory

#### 2.1 Contents

| 2.2   | Introduction             |

|-------|--------------------------|

| 2.3   | Memory Map               |

| 2.3.1 | EPROM28                  |

| 2.3.2 | EPROM Security28         |

| 2.3.3 | RAM29                    |

| 2.3.4 | Bootloader ROM           |

| 2.4   | Input/Output Programming |

#### 2.2 Introduction

This section describes the organization of the on-chip memory.

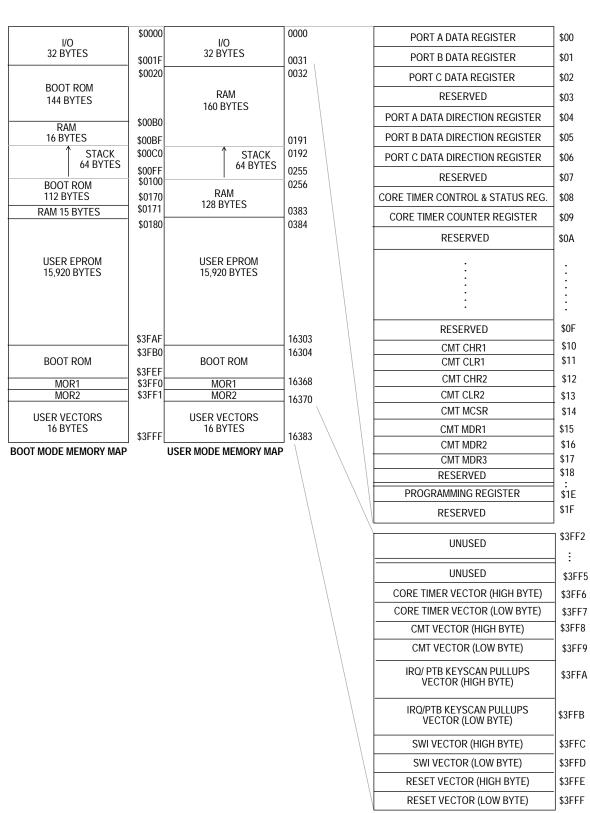

### 2.3 Memory Map

The MC68HC705RC17 has a 16-Kbyte memory map consisting of user EPROM, RAM, bootloader ROM, and input/output (I/O).

**Figure 2-1** is a memory map for the MC68HC705RC17. **Figure 2-2** is a more detailed memory map of the I/O register section.

#### Memory

Figure 2-1. MC68HC705RC17 Memory Map

Memory Memory Map

| Addr | Register Name                     | Bit 7 | 6      | 5     | 4     | 3     | 2      | 1     | Bit 0 |

|------|-----------------------------------|-------|--------|-------|-------|-------|--------|-------|-------|

| \$00 | Port A Data Register              | PA7   | PA6    | PA5   | PA4   | PA3   | PA2    | PA1   | PA0   |

| \$01 | Port B Data Register              | PB7   | PB6    | PB5   | PB4   | PB3   | PB2    | PB1   | PB0   |

| \$02 | Port C Data Register              | PC7   | PC6    | PC5   | PC4   |       |        | PC1   | PC0   |

| \$03 | Reserved                          | R     | R      | R     | R     | R     | R      | R     | R     |

| \$04 | Port A Data Direction Register    | DDRA7 | DDRA6  | DDRA5 | DDRA4 | DDRA3 | DDRA2  | DDRA1 | DDRA0 |

| \$05 | Port B Data Direction Register    | DDRB7 | DDRB6  | DDRB5 | DDRB4 | DDRB3 | DDRB2  | DDRB1 | DDRB0 |

| \$06 | Port C Data Direction Register    | DDRC7 | DDRC6  | DDRC5 | DDRC4 |       |        | DDRC1 | DDRC0 |

| \$07 | PLL Control Register              | 0     | BCS    | 0     | BWC   | PLLON | VCOTST | PS1   | PS0   |

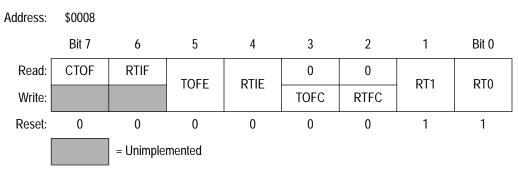

| \$08 | Timer Control and Status Register | CTOF  | RTIF   | TOFE  | RTIE  | TOFC  | RTFC   | RT1   | RT0   |

| \$09 | Timer Counter Register            | D7    | D6     | D5    | D4    | D3    | D2     | D1    | D0    |

| \$0A | Reserved                          | R     | R      | R     | R     | R     | R      | R     | R     |

| \$0B | Reserved                          | R     | R      | R     | R     | R     | R      | R     | R     |

| \$0C | Reserved                          | R     | R      | R     | R     | R     | R      | R     | R     |

| \$0D | Reserved                          | R     | R      | R     | R     | R     | R      | R     | R     |

| \$0E | Reserved                          | R     | R      | R     | R     | R     | R      | R     | R     |

| \$0F | Reserved                          | R     | R      | R     | R     | R     | R      | R     | R     |

| \$10 | CMT Timer CHR1                    | IROLN | CMTPOL | PH5   | PH4   | PH3   | PH2    | PH1   | PH0   |

| \$11 | CMT Timer CLR1                    | IROLP | 0      | PL5   | PL4   | PL3   | PL2    | PL1   | PL0   |

| \$12 | CMT Timer CHR2                    | 0     | 0      | SH5   | SH4   | SH3   | SH2    | SH1   | SH0   |

| \$13 | CMT Timer CLR2                    | 0     | 0      | SL5   | SL4   | SL3   | SL2    | SL1   | SL0   |

| \$14 | CMT Timer MCSR                    | EOC   | DIV2   | EIMSK | EXSPC | BASE  | MODE   | ΙE    | MCGEN |

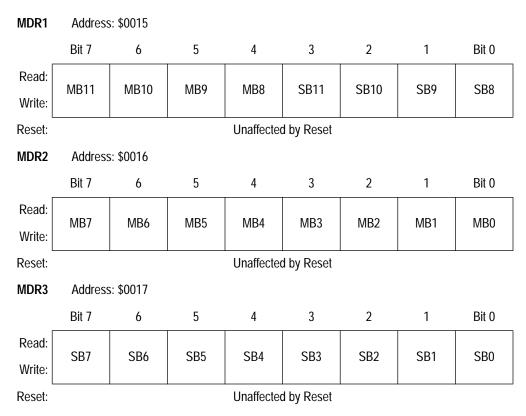

| \$15 | CMT Timer MDR1                    | MB11  | MB10   | MB9   | MB8   | SB11  | SB10   | SB9   | SB8   |

| \$16 | CMT Timer MDR2                    | MB7   | MB6    | MB5   | MB4   | MB3   | MB2    | MB1   | MB0   |

| \$17 | CMT Timer MDR3                    | SB7   | SB6    | SB5   | SB4   | SB3   | SB2    | SB1   | SB0   |

= Unimplemented R = Reserved

Figure 2-2. I/O Registers (Sheet 1 of 2)

MC68HC705RC17 - Rev. 2.0

#### Memory

| Addr | Register Name | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0 |

|------|---------------|-------|---|---|---|---|---|---|-------|

| \$18 | Reserved      | R     | R | R | R | R | R | R | R     |

| \$19 | Reserved      | R     | R | R | R | R | R | R | R     |

| \$1A | Reserved      | R     | R | R | R | R | R | R | R     |

| \$1B | Reserved      | R     | R | R | R | R | R | R | R     |

| \$1C | Reserved      | R     | R | R | R | R | R | R | R     |

| \$1D | Reserved      | R     | R | R | R | R | R | R | R     |

| \$1E | Reserved      | R     | R | R | R | R | R | R | R     |

| \$1F | Reserved      | R     | R | R | R | R | R | R | R     |

R = Reserved

Figure 2-2. I/O Registers (Sheet 2 of 2)

#### 2.3.1 EPROM

The user EPROM consists of 15,936 bytes of EPROM from \$0180 to \$3FAF and 14 bytes of user vectors from \$3FF2 to \$3FFF.

The bootloader ROM and vectors are located from \$0020 to \$00AF and \$0100 to \$170 in boot mode only, and from \$3FB0 to \$3FEF in both boot mode and burn-in mode.

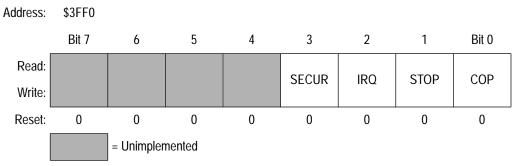

Ten of the user vectors, \$3FF6 thorough \$3FFF, are dedicated to reset and interrupt vectors. The four remaining locations, \$3FF2 through \$3FF5, are general-purpose user EPROM locations. The mask option registers (MOR1 and MOR2) are located at \$3FF0 and \$3FF1.

#### 2.3.2 EPROM Security

The MC68HC705RC17 contains special circuitry to prevent accessing the EPROM in non-user mode. Emulation will not be affected by this change.

Security is controlled by a security bit in the MOR register. It is intended to be programmed while the users are programming their code. This will inhibit reading of the EPROM in all modes other than user mode.

General Release Specification

MC68HC705RC17 — Rev. 2.0

Memory Input/Output Programming

#### 2.3.3 RAM

The user RAM consists of 352 bytes of a shared stack area. The RAM starts at address \$0020 and ends at address \$017F. The stack begins at address \$00FF. The stack pointer can access 64 bytes of RAM in the range \$00FF to \$00C0.

#### **NOTE:**

Using the stack area for data storage or temporary work locations requires care to prevent it from being overwritten due to stacking from an interrupt or subroutine call.

#### 2.3.4 Bootloader ROM

Addresses \$0020 to \$00AF, \$0100 to \$0170, and \$3FB0 to \$3FEF are reserved ROM addresses that contain the instructions for the bootloader functions. (See **Section 11. EPROM**.)

### 2.4 Input/Output Programming

In user mode, 18 lines are arranged as three 8-bit I/O ports. These ports are programmable as either inputs or outputs under software control of the data direction registers. For detailed information, refer to **Section 7.**Parallel Input/Output (I/O).

Memory

### General Release Specification — MC68HC705RC17

# Section 3. Central Processor Unit (CPU)

#### 3.1 Contents

| 3.2 | Introduction31            |

|-----|---------------------------|

| 3.3 | CPU Registers             |

| 3.4 | Accumulator               |

| 3.5 | Index Register33          |

| 3.6 | Condition Code Register33 |

| 3.7 | Stack Pointer             |

| 3.8 | Program Counter           |

#### 3.2 Introduction

This section describes the registers of the MC68HC705RC17's central processor unit (CPU).

#### **Central Processor Unit (CPU)**

### 3.3 CPU Registers

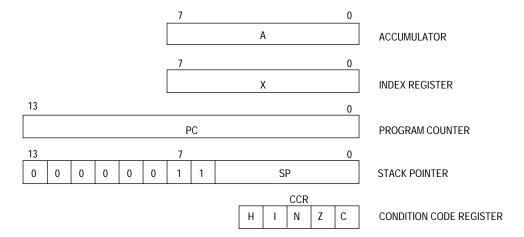

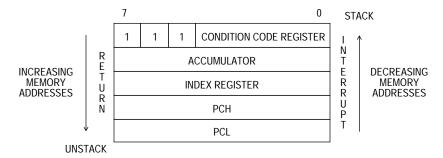

The MCU contains five registers as shown in **Figure 3-1**. The interrupt stacking order is shown in **Figure 3-2**.

Figure 3-1. Programming Model

NOTE: Since the stack pointer decrements during pushes, the PCL is stacked first, followed by PCH, etc. Pulling from the stack is in the reverse order.

Figure 3-2. Stacking Order

Central Processor Unit (CPU)

Accumulator

#### 3.4 Accumulator

The accumulator (A) is a general-purpose 8-bit register used to hold operands and results of arithmetic calculations or data manipulations.

### 3.5 Index Register

The index register (X) is an 8-bit register used for the indexed addressing value to create an effective address. The index register may also be used as a temporary storage area.

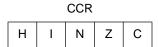

### 3.6 Condition Code Register

The condition code register (CCR) is a 5-bit register in which the H, N, Z, and C bits are used to indicate the results of the instruction just executed, and the I bit is used to enable or disable interrupts. These bits can be individually tested by a program, and specific actions can be taken as a result of their state. Each bit is explained in the following paragraphs.

#### Half Carry (H)

This bit is set during ADD and ADC operations to indicate that a carry occurred between bits 3 and 4.

#### Interrupt (I)

When this bit is set, the timer and external interrupt are masked (disabled). If an interrupt occurs while this bit is set, the interrupt is latched and processed as soon as the I bit is cleared.

MC68HC705RC17 - Rev. 2.0

#### **Central Processor Unit (CPU)**

#### Negative (N)

When set, this bit indicates that the result of the last arithmetic, logical, or data manipulation was negative.

#### Zero (Z)

When set, this bit indicates that the result of the last arithmetic, logical, or data manipulation was zero.

#### Carry/Borrow (C)

When set, this bit indicates that a carry or borrow out of the arithmetic logical unit (ALU) occurred during the last arithmetic operation. This bit is also affected during bit test and branch instructions and during shifts and rotates.

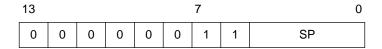

#### 3.7 Stack Pointer

The stack pointer (SP) contains the address of the next free location on the stack. During an MCU reset or the reset stack pointer (RSP) instruction, the stack pointer is set to location \$00FF. The stack pointer is then decremented as data is pushed onto the stack and incremented as data is pulled from the stack.

When accessing memory, the eight most significant bits are permanently set to 00000011. These eight bits are appended to the six least significant register bits to produce an address within the range of \$00FF to \$00C0. Subroutines and interrupts may use up to 64 (decimal) locations. If 64 locations are exceeded, the stack pointer wraps around and loses the previously stored information. A subroutine call occupies two locations on the stack; an interrupt uses five locations.

Central Processor Unit (CPU)

Program Counter

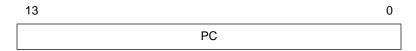

### 3.8 Program Counter

The program counter (PC) is a 13-bit register that contains the address of the next byte to be fetched.

**NOTE:**

The HC05 CPU core is capable of addressing 16-bit locations. For this implementation, however, the addressing registers are limited to a 16-Kbyte memory map.

Central Processor Unit (CPU)

General Release Specification

MC68HC705RC17 — Rev. 2.0

### General Release Specification — MC68HC705RC17

# Section 4. Interrupts

#### 4.1 Contents

| 4.2  | Introduction                                    |

|------|-------------------------------------------------|

| 4.3  | CPU Interrupt Processing38                      |

| 4.4  | Reset Interrupt Sequence39                      |

| 4.5  | Software Interrupt (SWI)39                      |

| 4.6  | Hardware Interrupts                             |

| 4.7  | External Interrupt (IRQ/Port B Keyscan)         |

| 4.8  | External Interrupt Timing42                     |

| 4.9  | Carrier Modulator Transmitter Interrupt (CMT)42 |

| 4.10 | Core Timer Interrupt                            |

#### 4.2 Introduction

The MCU can be interrupted four different ways:

- 1. Non-maskable software interrupt instruction (SWI)

- 2. External asynchronous interrupt (IRQ/port B keyscan)

- 3. Internal carrier modulator transmitter interrupt

- 4. Internal core timer interrupt

### Interrupts

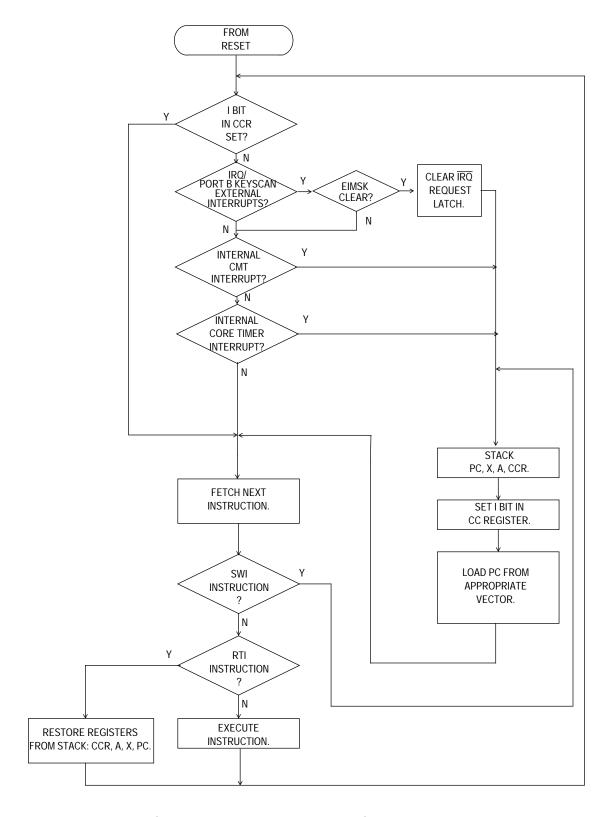

### 4.3 CPU Interrupt Processing

Interrupts cause the processor to save register contents on the stack and to set the interrupt mask (I bit) to prevent additional interrupts. Unlike reset, hardware interrupts do not cause the current instruction execution to be halted, but are considered pending until the current instruction is complete.

If interrupts are not masked (I bit in the CCR is clear) and the corresponding interrupt enable bit is set, the processor will proceed with interrupt processing. Otherwise, the next instruction is fetched and executed. If an interrupt occurs, the processor completes the current instruction, stacks the current CPU register state, sets the I bit to inhibit further interrupts, and finally checks the pending hardware interrupts. If more than one interrupt is pending following the stacking operation, the interrupt with the highest vector location shown in **Table 4-1** will be serviced first. The SWI is executed the same as any other instruction, regardless of the I-bit state.

When an interrupt is to be processed, the CPU fetches the address of the appropriate interrupt software service routine from the vector table at locations \$3FF6 through \$3FFF as defined in Table 4-1.

Table 4-1. Vector Address for Interrupts and Reset

| Register         | Flag<br>Name | Interrupt                               | CPU<br>Interrupt | Vector<br>Address |  |  |

|------------------|--------------|-----------------------------------------|------------------|-------------------|--|--|

| N/A              | N/A          | Reset                                   | RESET            | \$3FFE-\$3FFF     |  |  |

| N/A              | N/A          | Software Interrupt                      | SWI              | \$3FFC-\$3FFD     |  |  |

| N/A              | N/A          | External Interrupts*                    | IRQ              | \$3FFA-\$3FFB     |  |  |

| MCSR             | EOC          | End-of-Cycle Interrupt                  | CMT              | \$3FF8-\$3FF9     |  |  |

| CTCSR CTOF, RTIF |              | Real-Time Interrupt Core Timer Overflow | CORE<br>TIMER    | \$3FF6-\$3FF7     |  |  |

<sup>\*</sup>External interrupts include IRQ and port B keyscan sources.

Interrupts

Reset Interrupt Sequence

The M68HC05 CPU does not support interruptible instructions. The maximum latency to the first instruction of the interrupt service routine must include the longest instruction execution time plus stacking overhead.

Latency = (Longest instruction execution time + 10)  $x t_{cvc}$  seconds

An return from interrupt (RTI) instruction is used to signify when the interrupt software service routine is completed. The RTI instruction causes the register contents to be recovered from the stack and normal processing to resume at the next instruction that was to be executed when the interrupt took place. **Figure 4-1** shows the sequence of events that occurs during interrupt processing.

### 4.4 Reset Interrupt Sequence

The reset function is not in the strictest sense an interrupt; however, it is acted upon in a similar manner as shown in **Figure 4-1**. A low-level input on the RESET pin or an internally generated RST signal causes the program to vector to its starting address, which is specified by the contents of memory locations \$3FFE and \$3FFF. The I bit in the condition code register is also set. The MCU is configured to a known state during this type of reset.

## 4.5 Software Interrupt (SWI)

The SWI is an executable instruction and a nonmaskable interrupt since it is executed regardless of the state of the I bit in the CCR. If the I bit is zero (interrupts enabled), the SWI instruction executes after interrupts that were pending before the SWI was fetched or before interrupts generated after the SWI was fetched. The interrupt service routine address is specified by the contents of memory locations \$3FFC and \$3FFD.

MC68HC705RC17 — Rev. 2.0

### **Interrupts**

Figure 4-1. Interrupt Processing Flowchart

General Release Specification

MC68HC705RC17 — Rev. 2.0

Interrupts

Hardware Interrupts

### 4.6 Hardware Interrupts

All hardware interrupts except RESET are maskable by the I bit in the CCR. If the I bit is set, all hardware interrupts (internal and external) are disabled. Clearing the I bit enables the hardware interrupts. The three types of hardware interrupts are explained in the following sections.

### 4.7 External Interrupt (IRQ/Port B Keyscan)

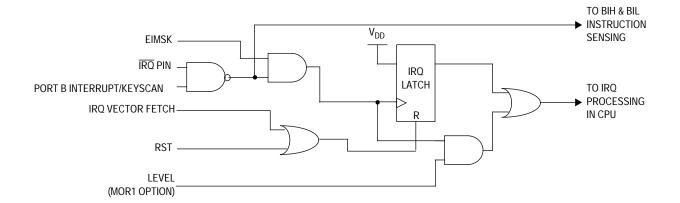

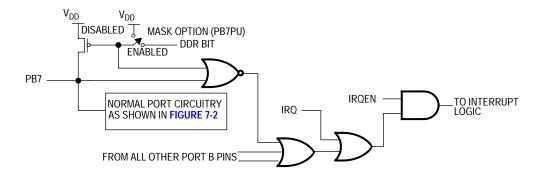

The IRQ pin provides an asynchronous interrupt to the CPU. A block diagram of the IRQ function is shown in **Figure 4-2**.

#### NOTE:

The BIH and BIL instructions will apply to the level on the  $\overline{IRQ}$  pin itself and to the output of the logic OR function with the port B IRQ interrupts. The states of the individual port B pins can be checked by reading the appropriate port B pins as inputs.

The IRQ pin is one source of an external interrupt. All port B pins (PB0 through PB7) act as other external interrupt sources if the pullup/interrupt feature is enabled as specified by the user.

Figure 4-2. IRQ Function Block Diagram

MC68HC705RC17 - Rev. 2.0

### Interrupts

When edge sensitivity is selected for the IRQ interrupt, it is sensitive to these cases:

- 1. Falling edge on the IRQ pin

- 2. Falling edge on any port B pin with pullup/interrupt enabled

When edge and level sensitivity is selected for the IRQ interrupt, it is sensitive to these cases:

- 1. Low level on the IRQ pin

- 2. Falling edge on the IRQ pin

- 3. Falling edge or low level on any port B pin with pullup/interrupt enabled

External interrupts also can be masked by setting the EIMSK bit in the MSCR register of the IR remote timer. See **9.5.4 Modulator Period Data Registers** for details.

### 4.8 External Interrupt Timing

If the interrupt mask bit (I bit) of the CCR is set, all maskable interrupts (internal and external) are disabled. Clearing the I bit enables interrupts. The interrupt request is latched immediately following the falling edge of the  $\overline{IRQ}$  source. It is then synchronized internally and serviced as specified by the contents of \$3FFA and \$3FFB.

Either a level-sensitive and edge-sensitive trigger or an edge-sensitive-only trigger is available via the mask programmable option for the  $\overline{\text{IRQ}}$  pin.

# 4.9 Carrier Modulator Transmitter Interrupt (CMT)

A CMT interrupt occurs when the end-of-cycle flag (EOC) and the end-of-cycle interrupt enable (EOCIE) bits are set in the modulator control and status register (MCSR). This interrupt will vector to the interrupt service routine located at the address specified by the contents of memory locations \$3FF8 and \$3FF9.

General Release Specification

MC68HC705RC17 — Rev. 2.0

Interrupts

Core Timer Interrupt

## 4.10 Core Timer Interrupt

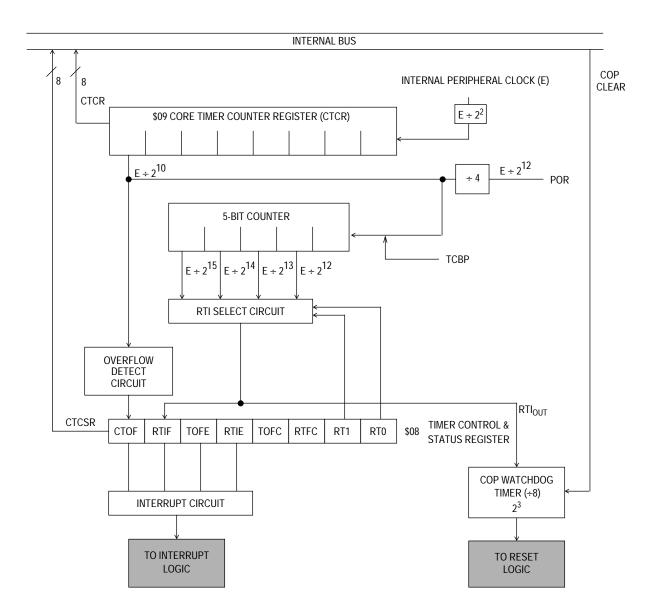

This timer can create two types of interrupts. A timer overflow interrupt occurs whenever the 8-bit timer rolls over from \$FF to \$00 and the enable bit TOFE is set. A real-time interrupt occurs whenever the programmed time elapses and the enable bit RTIE is set. Either of these interrupts vectors to the same interrupt service routine, located at the address specified by the contents of memory locations \$3FF6 and \$3FF7.

MC68HC705RC17 - Rev. 2.0

Interrupts

### General Release Specification — MC68HC705RC17

### Section 5. Resets

#### 5.1 Contents

| 5.2     | Introduction45                             |

|---------|--------------------------------------------|

| 5.3     | External Reset (RESET)46                   |

| 5.4     | Low-Power External Reset (LPRST)           |

| 5.5     | Internal Resets                            |

| 5.5.1   | Power-On Reset (POR)48                     |

| 5.5.2   | Computer Operating Properly Reset (COPR)49 |

| 5.5.2.  | Resetting the COP49                        |

| 5.5.2.2 | COP During Wait Mode                       |

| 5.5.2.3 | COP During Stop Mode                       |

| 5.5.2.4 | 4 COP Watchdog Timer Considerations50      |

| 5.5.3   | Illegal Address                            |

### 5.2 Introduction

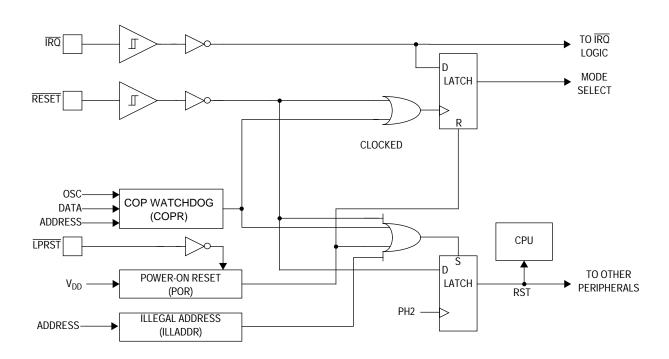

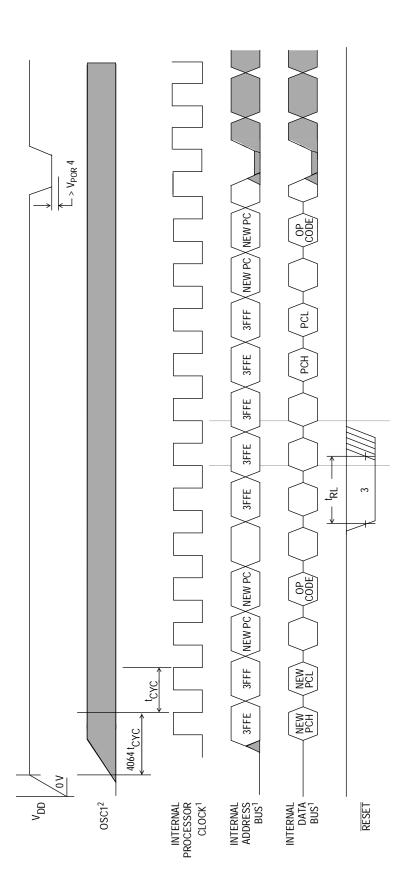

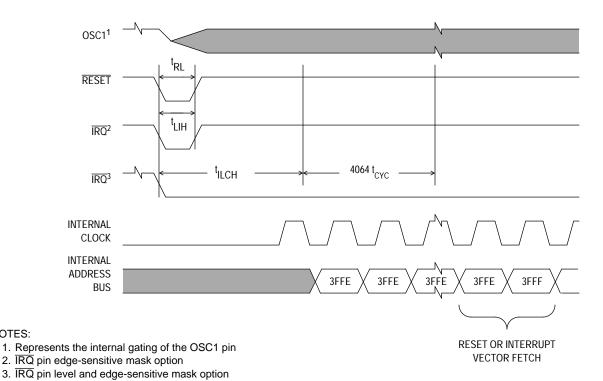

The MCU can be reset from five sources: two external inputs and three internal restart conditions. The  $\overline{RESET}$  and  $\overline{LPRST}$  pins are inputs as shown in **Figure 5-1**. All the internal peripheral modules will be reset by the internal reset signal (RST). Refer to **Figure 5-2** for reset timing detail.

Resets

### 5.3 External Reset (RESET)

The RESET pin is one of the two external sources of a reset. This pin is connected to a Schmitt trigger input gate to provide an upper and lower threshold voltage separated by a minimum amount of hysteresis. This external reset occurs whenever the RESET pin is pulled below the lower threshold and remains in reset until the RESET pin rises above the upper threshold. This active-low input will generate the RST signal and reset the CPU and peripherals. Termination of the external RESET input or the internal COP watchdog reset are the only reset sources that can alter the operating mode of the MCU.

**NOTE:** Activation of the RST signal is generally referred to as reset of the device, unless otherwise specified.

Figure 5-1. Reset Block Diagram

The LPRST pin resets the CPU like the RESET pin. However, 4064 POR cycles are executed first, before the reset vector address appears

The next rising edge of the internal processor clock following the rising edge of RESET initiates the reset sequence.

OSC1 line is not meant to represent frequency. It is only used to represent time.

1. Internal timing signal and bus information are not available externally.

$V_{\text{DD}}$  must fall to a level lower than  $V_{\text{POR}}$  to be recognized as a power-on reset.

2, 6, 4, 7,

on the internal address bus. (See 5.3 External Reset (RESET).)

Figure 5-2. Reset and POR Timing Diagram

Resets

## 5.4 Low-Power External Reset (LPRST)

The  $\overline{LPRST}$  pin is one of the two external sources of a reset. This external reset occurs whenever the  $\overline{LPRST}$  pin is pulled below the lower threshold and remains in reset until the  $\overline{LPRST}$  pin rises. This active-low input will, in addition to generating the RST signal and resetting the CPU and peripherals, halt all internal processor clocks. The MCU will remain in this low-power reset condition as long as a logic 0 remains on LPRST. When a logic 1 is applied to LPRST, processor clocks will be re-enabled with the MCU remaining in reset until the 4064 internal processor clock cycle ( $t_{cyc}$ ) oscillator stabilization delay is completed. If any other reset function is active at the end of this 4064-cycle delay, the RST signal remains in the reset condition until the other reset condition(s) end.

#### 5.5 Internal Resets

The three internally generated resets are the initial power-on reset function, the COP watchdog timer reset, and the illegal address detector. Termination of the external reset input, external LPRST input, or the internal COP watchdog timer are the only reset sources that can alter the operating mode of the MCU. The other internal resets do not have any effect on the mode of operation when their reset state ends.

#### 5.5.1 Power-On Reset (POR)

The internal POR is generated on power-up to allow the clock oscillator to stabilize. The POR is strictly for power turn-on conditions and is not able to detect a drop in the power supply voltage (brown-out). There is an oscillator stabilization delay of 4064 internal processor bus clock cycles (PH2) after the oscillator becomes active.

The POR generates the RST signal that resets the CPU. If any other reset function is active at the end of this 4064-cycle delay, the RST signal remains in the reset condition until the other reset condition(s) ends.

Resets

Internal Resets

### 5.5.2 Computer Operating Properly Reset (COPR)

The MCU contains a watchdog timer that automatically times out if not reset (cleared) within a specific time by a program reset sequence. If the COP watchdog timer is allowed to time out, an internal reset is generated to reset the MCU. Regardless of an internal or external reset, the MCU comes out of a COP reset according to the standard rules of mode selection.

The COP reset function is enabled or disabled by a mask option and is verified during production testing.

#### 5.5.2.1 Resetting the COP

Writing a 0 to the COP bit prevents a COP reset. This action resets the counter and begins the time out period again. The COP bit is bit 0 of address \$3FF0. A read of address \$3FF0 returns user data programmed at that location.

### 5.5.2.2 COP During Wait Mode

The COP continues to operate normally during wait mode. The software should pull the device out of wait mode periodically and reset the COP by writing to the COPF bit to prevent a COP reset.

### 5.5.2.3 COP During Stop Mode

When the stop enable mask option is selected, stop mode disables the oscillator circuit and thereby turns the clock off for the entire device. When stop is executed, the COP counter will hold its current state. If a reset is used to exit stop mode, the COP counter is reset and held until 4064 POR cycles are completed at which time counting will begin. If an external IRQ is used to exit stop mode, the COP counter does not wait for the completion of the 4064 POR cycles but does count these cycles. Therefore, it is recommended that the COP is fed before executing the STOP instruction.

MC68HC705RC17 - Rev. 2.0

Resets

### Freescale Semiconductor, Inc.

### 5.5.2.4 COP Watchdog Timer Considerations

The COP watchdog timer is active in all modes of operation if enabled by a mask option. If the COP watchdog timer is selected by a mask option, any execution of the STOP instruction (either intentionally or inadvertently due to the CPU being disturbed) causes the oscillator to halt and prevents the COP watchdog timer from timing out. If the COP watchdog timer is selected by a mask option, the COP resets the MCU when it times out. Therefore, it is recommended that the COP watchdog be **disabled** for a system that must have intentional uses of the wait mode for periods longer than the COP time out period.

The recommended interactions and considerations for the COP watchdog timer, STOP instruction, and WAIT instruction are summarized in **Table 5-1**.

**Table 5-1. COP Watchdog Timer Recommendations**

| IF the Following Conditions Exist:      | THEN the COP Watchdog Timer          |  |  |  |

|-----------------------------------------|--------------------------------------|--|--|--|

| Wait Time                               | Should Be:                           |  |  |  |

| Wait Time <b>Less than</b> COP Time Out | Enable or Disable COP by Mask Option |  |  |  |

| Wait Time <b>More than</b> COP Time Out | Disable COP by Mask Option           |  |  |  |

| Any Length Wait Time                    | Disable COP by Mask Option           |  |  |  |

#### 5.5.3 Illegal Address

An illegal address reset is generated when the CPU attempts to fetch an instruction from I/O address space (\$0000 to \$001F).

### General Release Specification — MC68HC705RC17

### Section 6. Low-Power Modes

#### 6.1 Contents

| 6.2 | Introduction5   |

|-----|-----------------|

| 6.3 | Stop Mode       |

| 6.4 | Wait Mode5      |

| 6.5 | Low-Power Reset |

#### 6.2 Introduction

This section describes the low-power modes.

### 6.3 Stop Mode

The STOP instruction places the MCU in its lowest power-consumption mode. In stop mode, the internal oscillator is turned off, halting all internal processing, including timer operation.

During the stop mode, the CTCSR (\$08) bits are altered to remove any pending timer interrupt request and to disable any further timer interrupts. The timer prescaler is cleared. The I bit in the CCR is cleared to enable external interrupts. All other registers and memory remain unaltered. All input/output lines remain unchanged.

The processor can be brought out of stop mode only by an external interrupt or RESET. Refer to Figure 6-1.

### **NOTE:**

If an external interrupt is pending when stop mode is entered, then stop mode will be exited immediately.

MC68HC705RC17 - Rev. 2.0

### **Low-Power Modes**

Figure 6-1. Stop Recovery Timing Diagram

#### NOTE:

The EIMSK bit of the carrier modulator transmitter MCSR (modulator control and status register) is not cleared automatically by the execution of a STOP instruction. Care should be taken to clear this bit before entering stop mode.

#### 6.4 Wait Mode

NOTES:

The WAIT instruction places the MCU in a low power-consumption mode, but wait mode consumes more power than stop mode. All CPU action is suspended, but the core timer, the oscillator, and any enabled module remain active. Any interrupt or reset will cause the MCU to exit wait mode. The user must shut off subsystems to reduce power consumption. Wait current specifications assume CPU operation only and do not include current consumption by any other subsystems.

General Release Specification

MC68HC705RC17 — Rev. 2.0

During wait mode, the I bit in the CCR is cleared to enable interrupts. All other registers, memory, and input/output lines remain in their previous states. The timer may be enabled to allow a periodic exit from wait mode.

**NOTE:** For minimum current consumption, the phase-locked loop (PLL) should be disabled or turned off before entering wait mode.

Figure 6-2. Stop/Wait Flowchart

MC68HC705RC17 - Rev. 2.0

### **Low-Power Modes**

### 6.5 Low-Power Reset

Low-power reset mode is entered when a logic 0 is detected on the LPRST pin. When in this mode (as long as LPRST is held low), the MCU is held in reset and all internal clocks are halted. Applying a logic 1 to LPRST will cause the part to exit low-power reset mode and begin counting out the 4064-cycle oscillator stabilization period. Once this time has elapsed, the MCU will begin operation from the reset vectors (\$3FFE-\$3FFF).

### General Release Specification — MC68HC705RC17

# Section 7. Parallel Input/Output (I/O)

#### 7.1 Contents

| 7.2 | Introduction5                  |

|-----|--------------------------------|

| 7.3 | Port A                         |

| 7.4 | Port B                         |

| 7.5 | Port C                         |

| 7.6 | Input/Output (I/O) Programming |

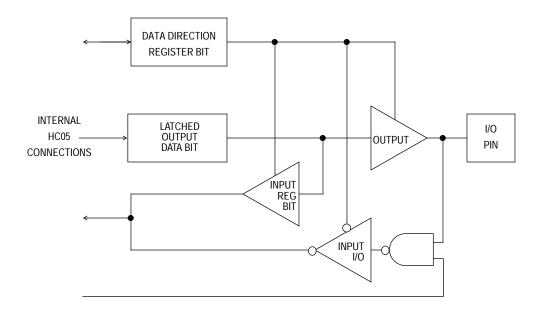

#### 7.2 Introduction

In user mode, 18 lines are arranged as one 2-bit and two 8-bit I/O ports. These ports are programmable as either inputs or outputs under software control of the data direction registers.

#### **NOTE:**

To avoid a glitch on the output pins, write data to the I/O port data register before writing a 1 to the corresponding data direction register.

Four extra I/O ports are available on higher pin count packages. Consult factory for availability.

### Parallel Input/Output (I/O)

#### **7.3 Port A**

Port A is an 8-bit bidirectional port which does not share any of its pins with other subsystems. The port A data register is at \$0000 and the data direction register (DDR) is at \$0004. Reset does not affect the data register, but clears the data direction register, thereby returning the ports to inputs. Writing a 1 to a DDR bit sets the corresponding port bit to output mode.

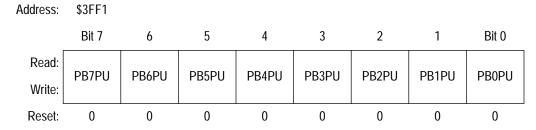

#### 7.4 Port B

Port B is an 8-bit bidirectional port which does not share any of its pins with other subsystems. The address of the port B data register is \$0001 and the data direction register (DDR) is at address \$0005. Reset does not affect the data register, but clears the data direction register, thereby returning the ports to inputs. Writing a 1 to a DDR bit sets the corresponding port bit to output mode. Each of the port B pins has a mask programmable pullup device that can be enabled. When the pullup device is enabled, this pin will also become an interrupt pin. The edge or edge and level sensitivity of the  $\overline{IRQ}$  pin will also pertain to the enabled port B pins. Care needs to be taken when using port B pins that have the pullup enabled. Before switching from an output to an input, the data should be preconditioned to a logic 1 or the I bit should be set in the condition code register to prevent an interrupt from occurring.

**NOTE:** When a port B pin is configured as an output, its corresponding keyscan interrupt is disabled, regardless of its mask option.

Figure 7-1. Port B Pullup Option

General Release Specification

MC68HC705RC17 — Rev. 2.0

Parallel Input/Output (I/O)

Port C

#### 7.5 Port C