Freescale Semiconductor, Inc.

# 68HC705V8

## **SPECIFICATION**

## **REV 2.1**

## (General Release)

© August 12, 1994

MCU System Design Group Oak Hill, Texas

For More Information On This Product, Go to: www.freescale.com

# **TABLE OF CONTENTS**

| <b>SECTION 1</b> | GENERAL DESCRIPTION                 | .1 |

|------------------|-------------------------------------|----|

| 1.1              | FEATURES                            | 1  |

| 1.2              | MASK OPTIONS                        | 2  |

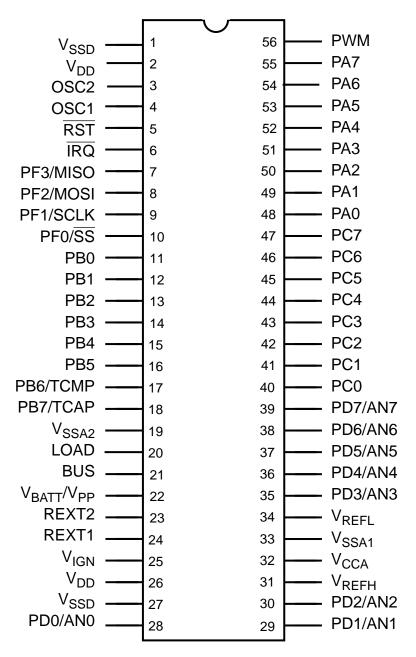

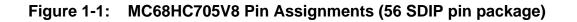

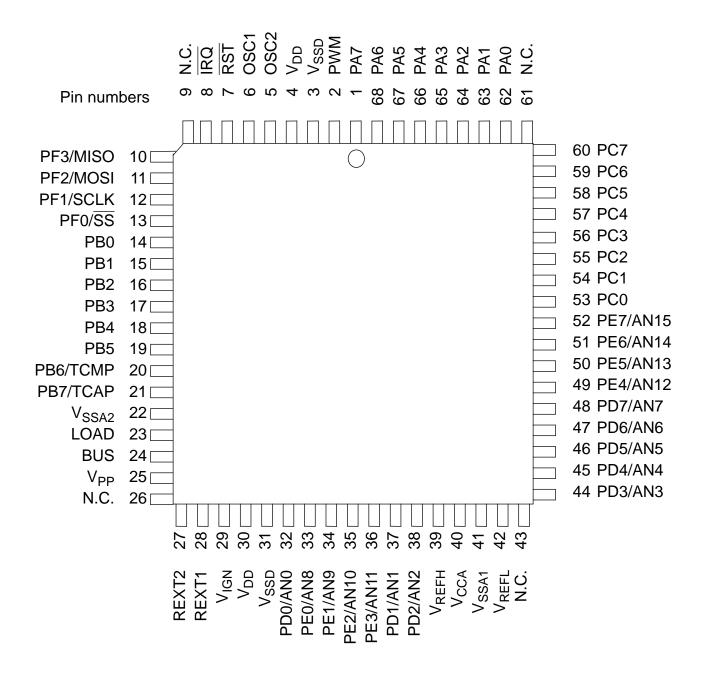

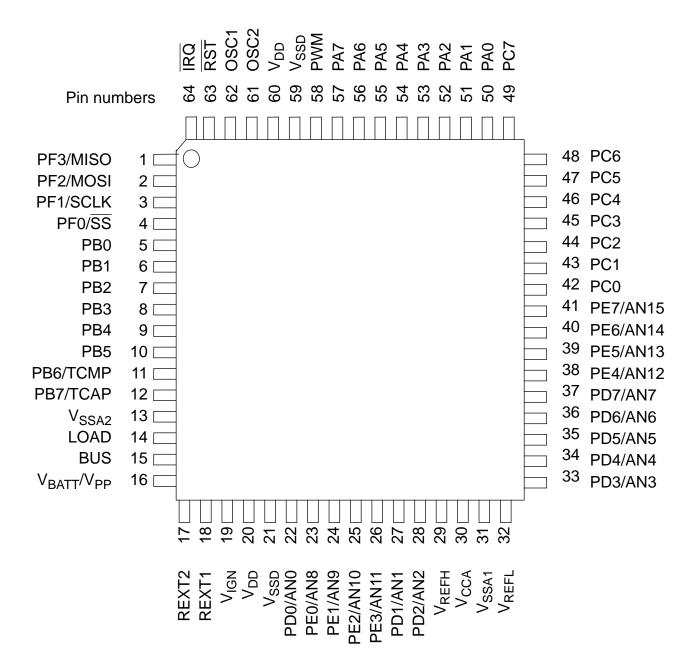

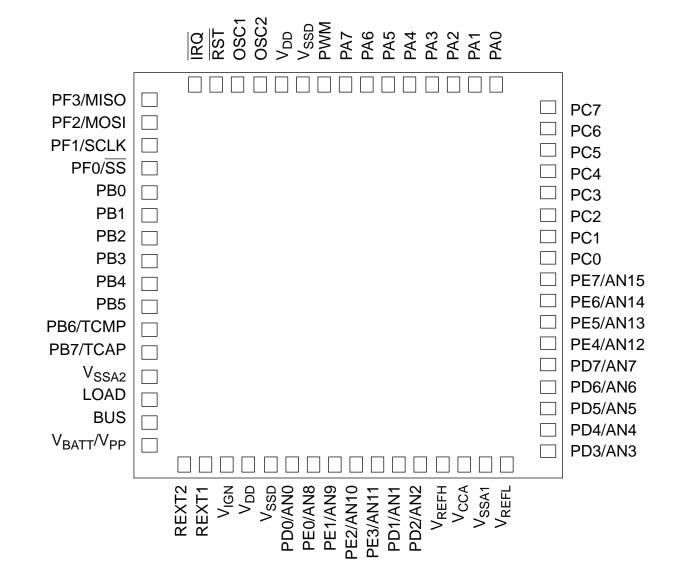

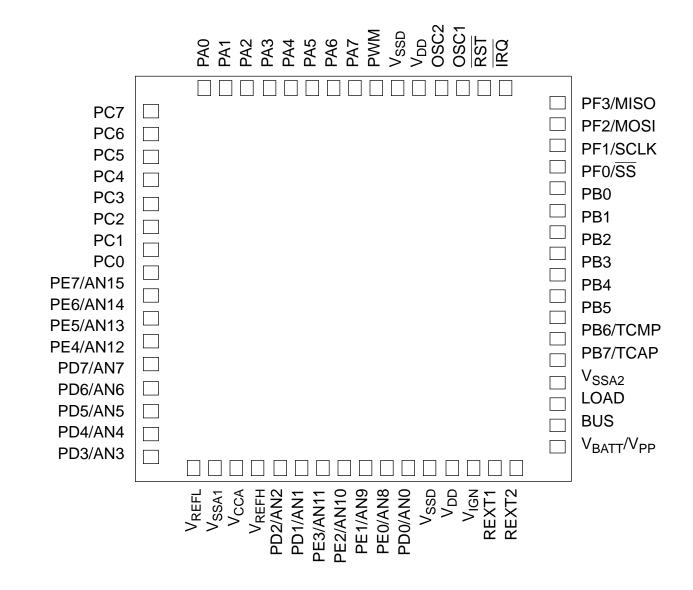

| 1.3              | PIN ASSIGNMENTS                     | 2  |

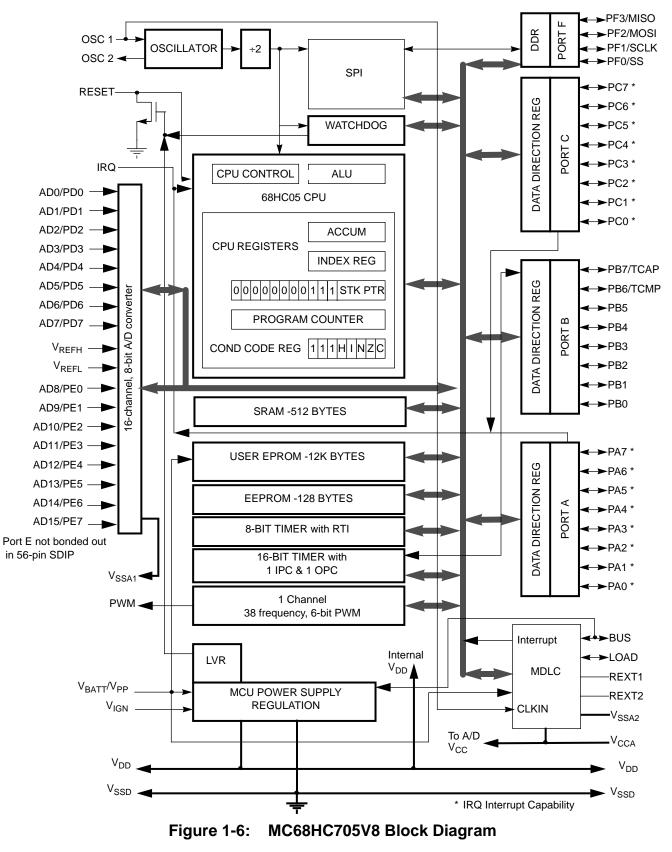

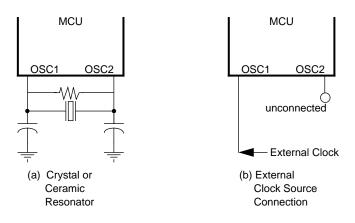

| 1.4              | MCU STRUCTURE                       |    |

| 1.5              | FUNCTIONAL PIN DESCRIPTION          | 9  |

| 1.5.1            |                                     |    |

| 1.5.2            | 33                                  |    |

| 1.5.3            | 55AT                                |    |

| 1.5.4            | 33AZ                                |    |

| 1.5.5            | CCA                                 |    |

| 1.5.6            |                                     |    |

| 1.5.7            | )                                   | 10 |

| 1.5.8            |                                     |    |

| 1.5.9            |                                     |    |

| 1.5.1            |                                     | 11 |

| 1.5.1<br>1.5.1   |                                     |    |

| 1.5.1            |                                     |    |

| 1.5.1            |                                     |    |

| 1.5.1            |                                     |    |

| 1.5.1            |                                     |    |

| 1.5.1            |                                     |    |

| SECTION 2        | MEMORY MAP                          |    |

|                  |                                     |    |

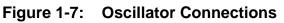

| 2.1              | SINGLE-CHIP MODE MEMORY MAP         |    |

| 2.2              | I/O AND CONTROL REGISTERS           |    |

| 2.3              | RAM                                 |    |

| 2.4              | BOOTROM                             |    |

| 2.5              | EPROM                               |    |

| 2.6              | EEPROM                              | 17 |

| <b>SECTION 3</b> | EPROM AND EEPROM                    | 23 |

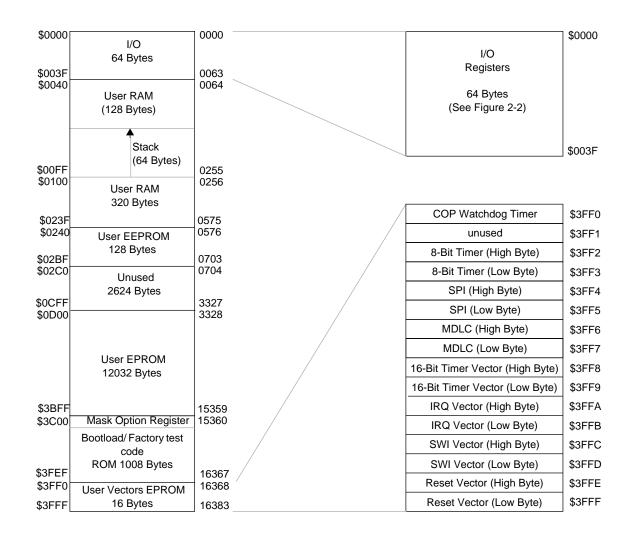

| 3.1              | EPROM BOOTLOADER                    | 23 |

| 3.1.1            | BOOTLOADER FUNCTIONS                | 23 |

| 3.2              | EPROM PROGRAMMING                   |    |

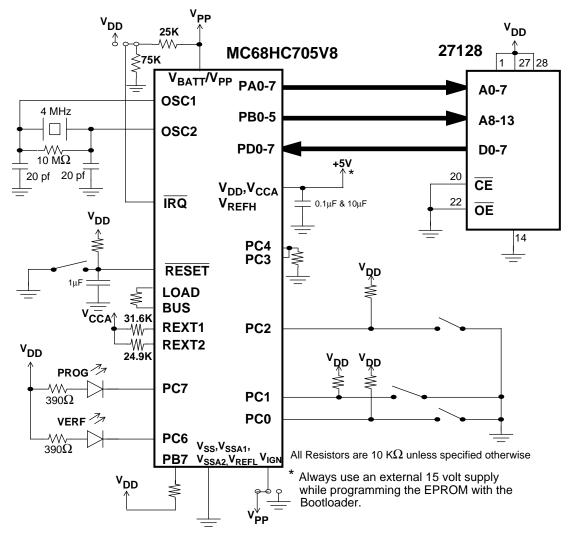

| 3.2.1            | PROGRAMMING REGISTER \$0D           | 24 |

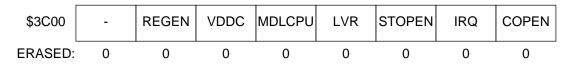

| 3.3              | MASK OPTION REGISTER (MOR) \$3C00   |    |

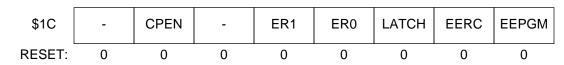

| 3.4              | EEPROM PROGRAMMING REGISTER \$1C    |    |

| 3.4.1            |                                     |    |

| 3.4.2            |                                     |    |

| 3.4.3            |                                     |    |

| 3.4.4            | EERC - EEPROM RC Oscillator Control | 28 |

| 3.4.5<br>3.5                                                                                                                                                                  | EEPGM - EEPROM Programming Power Enable<br>OPERATION IN STOP AND WAIT                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>SECTION 4</b>                                                                                                                                                              | CPU CORE                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31                                                                                                                                              |

| 4.1                                                                                                                                                                           | REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31                                                                                                                                              |

| 4.1.1                                                                                                                                                                         | ACCUMULATOR (A)                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |

| 4.1.2                                                                                                                                                                         | INDEX REGISTER (X)                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31                                                                                                                                              |

| 4.1.3                                                                                                                                                                         | STACK POINTER (SP)                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                 |

| 4.1.4                                                                                                                                                                         | PROGRAM COUNTER (PC)                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |

| 4.1.5                                                                                                                                                                         | CONDITION CODE REGISTER (CCR)                                                                                                                                                                                                                                                                                                                                                                                                                                          | 32                                                                                                                                              |

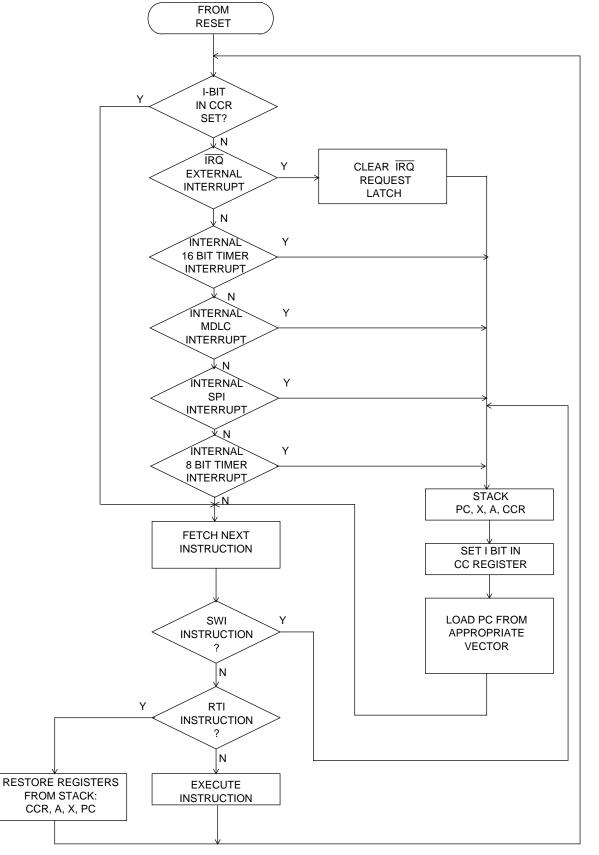

| <b>SECTION 5</b>                                                                                                                                                              | INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35                                                                                                                                              |

| 5.1                                                                                                                                                                           | CPU INTERRUPT PROCESSING                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                 |

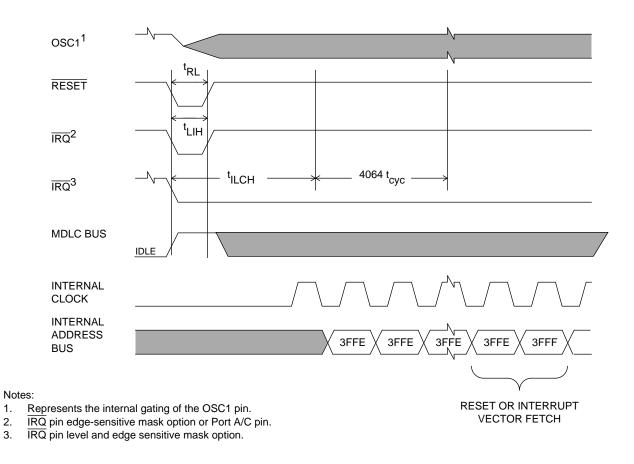

| 5.2                                                                                                                                                                           | RESET INTERRUPT SEQUENCE                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                 |

| 5.3                                                                                                                                                                           | SOFTWARE INTERRUPT (SWI)                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                 |

| 5.4                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |

| 5.5                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |

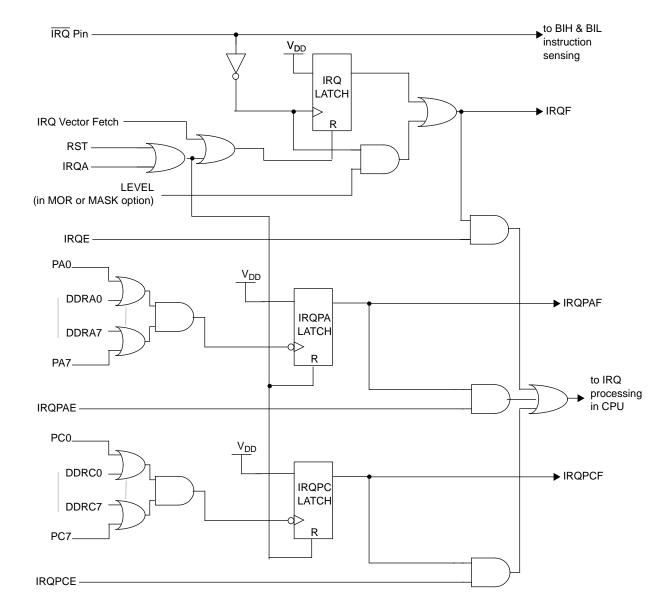

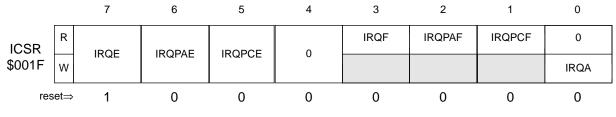

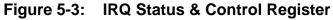

| 5.5.1<br>5.5.2                                                                                                                                                                | IRQ CONTROL/STATUS REGISTER (ICSR) \$1F<br>EXTERNAL INTERRUPT TIMING                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                 |

| 5.5.2                                                                                                                                                                         | 16-BIT TIMER INTERRUPT                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                 |

| 5.7                                                                                                                                                                           | MDLC INTERRUPT                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                 |

| 5.8                                                                                                                                                                           | SPI INTERRUPT                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                 |

| 5.9                                                                                                                                                                           | 8-BIT TIMER INTERRUPT                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                 |

|                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |

| <b>SECTION 6</b>                                                                                                                                                              | RESETS                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45                                                                                                                                              |

| <b>SECTION 6</b> 6.1                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                 |

|                                                                                                                                                                               | RESETS<br>EXTERNAL RESET (RESET)<br>INTERNAL RESETS                                                                                                                                                                                                                                                                                                                                                                                                                    | 45                                                                                                                                              |

| 6.1                                                                                                                                                                           | EXTERNAL RESET (RESET)                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45<br>46                                                                                                                                        |

| 6.1<br>6.2<br>6.2.1<br>6.2.2                                                                                                                                                  | EXTERNAL RESET (RESET)<br>INTERNAL RESETS<br>POWER-ON RESET (POR)<br>OPERATION IN STOP AND WAIT                                                                                                                                                                                                                                                                                                                                                                        | 45<br>46<br>46<br>46                                                                                                                            |

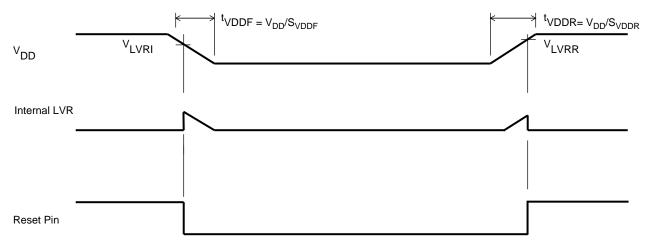

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3                                                                                                                                         | EXTERNAL RESET (RESET)<br>INTERNAL RESETS<br>POWER-ON RESET (POR)<br>OPERATION IN STOP AND WAIT<br>COMPUTER OPERATING PROPERLY RESET (COPF                                                                                                                                                                                                                                                                                                                             | 45<br>46<br>46<br>46<br>R) 48                                                                                                                   |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                                                                                                | EXTERNAL RESET (RESET)<br>INTERNAL RESETS<br>POWER-ON RESET (POR)<br>OPERATION IN STOP AND WAIT<br>COMPUTER OPERATING PROPERLY RESET (COPF<br>LOW-VOLTAGE RESET (LVR)                                                                                                                                                                                                                                                                                                  | 45<br>46<br>46<br>46<br>R) 48<br>49                                                                                                             |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5                                                                                                                       | EXTERNAL RESET (RESET)<br>INTERNAL RESETS<br>POWER-ON RESET (POR)<br>OPERATION IN STOP AND WAIT<br>COMPUTER OPERATING PROPERLY RESET (COPF<br>LOW-VOLTAGE RESET (LVR)<br>ILLEGAL ADDRESS                                                                                                                                                                                                                                                                               | 45<br>46<br>46<br>R) 48<br>49<br>50                                                                                                             |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                                                                                                | EXTERNAL RESET (RESET)<br>INTERNAL RESETS<br>POWER-ON RESET (POR)<br>OPERATION IN STOP AND WAIT<br>COMPUTER OPERATING PROPERLY RESET (COPF<br>LOW-VOLTAGE RESET (LVR)                                                                                                                                                                                                                                                                                                  | 45<br>46<br>46<br>R) 48<br>49<br>50                                                                                                             |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5                                                                                                                       | EXTERNAL RESET (RESET)<br>INTERNAL RESETS<br>POWER-ON RESET (POR)<br>OPERATION IN STOP AND WAIT<br>COMPUTER OPERATING PROPERLY RESET (COPF<br>LOW-VOLTAGE RESET (LVR)<br>ILLEGAL ADDRESS                                                                                                                                                                                                                                                                               | 45<br>46<br>46<br>46<br>R) 48<br>49<br>50<br>50                                                                                                 |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>SECTION 7<br>7.1                                                                                 | EXTERNAL RESET (RESET)<br>INTERNAL RESETS<br>POWER-ON RESET (POR)<br>OPERATION IN STOP AND WAIT<br>COMPUTER OPERATING PROPERLY RESET (COPF<br>LOW-VOLTAGE RESET (LVR)<br>ILLEGAL ADDRESS<br>DISABLED STOP INSTRUCTION<br><b>POWER SUPPLY AND REGULATION</b><br>INTERNAL POWER SUPPLY.                                                                                                                                                                                  | 45<br>46<br>46<br>R)48<br>49<br>50<br><b>50</b><br><b>51</b>                                                                                    |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br><b>SECTION 7</b><br>7.1<br>7.1.1                                                                 | EXTERNAL RESET (RESET)<br>INTERNAL RESETS<br>POWER-ON RESET (POR)<br>OPERATION IN STOP AND WAIT<br>COMPUTER OPERATING PROPERLY RESET (COPF<br>LOW-VOLTAGE RESET (LVR)<br>ILLEGAL ADDRESS<br>DISABLED STOP INSTRUCTION<br><b>POWER SUPPLY AND REGULATION</b><br>INTERNAL POWER SUPPLY<br>PRIMARY 5V REGULATOR                                                                                                                                                           | 45<br>46<br>46<br>R)48<br>49<br>50<br>50<br><b>51</b><br>51                                                                                     |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br><b>SECTION 7</b><br>7.1<br>7.1.1<br>7.1.1<br>7.1.2                                               | EXTERNAL RESET (RESET)<br>INTERNAL RESETS<br>POWER-ON RESET (POR)<br>OPERATION IN STOP AND WAIT<br>COMPUTER OPERATING PROPERLY RESET (COPF<br>LOW-VOLTAGE RESET (LVR)<br>ILLEGAL ADDRESS<br>DISABLED STOP INSTRUCTION<br><b>POWER SUPPLY AND REGULATION</b><br>INTERNAL POWER SUPPLY<br>PRIMARY 5V REGULATOR<br>SECONDARY REGULATOR                                                                                                                                    | 45<br>46<br>46<br>R)48<br>50<br>50<br><b>51</b><br>51<br>51                                                                                     |

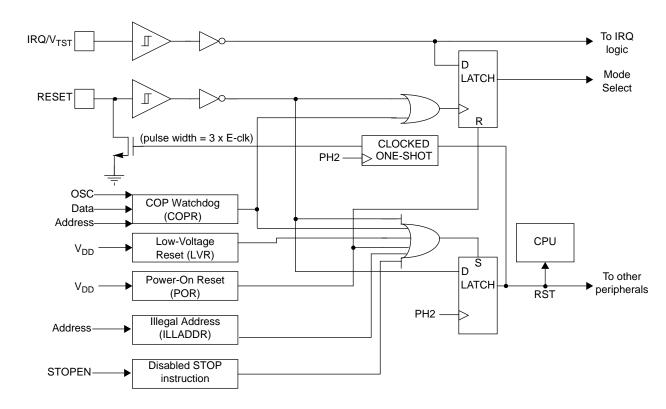

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>SECTION 7<br>7.1<br>7.1.1<br>7.1.2<br>7.2                                                                 | EXTERNAL RESET (RESET)<br>INTERNAL RESETS<br>POWER-ON RESET (POR)<br>OPERATION IN STOP AND WAIT<br>COMPUTER OPERATING PROPERLY RESET (COPF<br>LOW-VOLTAGE RESET (LVR)<br>ILLEGAL ADDRESS<br>DISABLED STOP INSTRUCTION<br><b>POWER SUPPLY AND REGULATION</b><br>INTERNAL POWER SUPPLY<br>PRIMARY 5V REGULATOR<br>SECONDARY REGULATOR<br>MISCELLANEOUS REGISTER                                                                                                          | 45<br>46<br>46<br>R)48<br>50<br>50<br><b>51</b><br>51<br>51<br>51<br>51                                                                         |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br><b>SECTION 7</b><br>7.1<br>7.1.1<br>7.1.2<br>7.2<br>7.2.1                                                 | EXTERNAL RESET (RESET)<br>INTERNAL RESETS<br>POWER-ON RESET (POR)<br>OPERATION IN STOP AND WAIT<br>COMPUTER OPERATING PROPERLY RESET (COPF<br>LOW-VOLTAGE RESET (LVR)<br>ILLEGAL ADDRESS<br>DISABLED STOP INSTRUCTION<br><b>POWER SUPPLY AND REGULATION</b><br>INTERNAL POWER SUPPLY<br>PRIMARY 5V REGULATOR<br>SECONDARY REGULATOR<br>MISCELLANEOUS REGISTER<br>IGNS - Ignition status bit                                                                            | 45<br>46<br>46<br>R)48<br>49<br>50<br>50<br><b>51</b><br>51<br>51<br>51<br>52<br>52                                                             |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br><b>SECTION 7</b><br>7.1<br>7.1.1<br>7.1.2<br>7.2<br>7.2.1<br>7.2.1<br>7.2.2                               | EXTERNAL RESET (RESET)<br>INTERNAL RESETS<br>POWER-ON RESET (POR)<br>OPERATION IN STOP AND WAIT<br>COMPUTER OPERATING PROPERLY RESET (COPF<br>LOW-VOLTAGE RESET (LVR)<br>ILLEGAL ADDRESS<br>DISABLED STOP INSTRUCTION<br><b>POWER SUPPLY AND REGULATION</b><br>INTERNAL POWER SUPPLY<br>PRIMARY 5V REGULATOR<br>SECONDARY REGULATOR<br>MISCELLANEOUS REGISTER<br>IGNS - Ignition status bit<br>OCE - Output compare enable                                             | 45<br>46<br>46<br>R)48<br>50<br>50<br><b>51</b><br>51<br>51<br>51<br>52<br>52<br>52                                                             |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br><b>SECTION 7</b><br>7.1<br>7.1.1<br>7.1.2<br>7.2<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3                        | EXTERNAL RESET (RESET)<br>INTERNAL RESETS<br>POWER-ON RESET (POR)<br>OPERATION IN STOP AND WAIT<br>COMPUTER OPERATING PROPERLY RESET (COPF<br>LOW-VOLTAGE RESET (LVR)<br>ILLEGAL ADDRESS<br>DISABLED STOP INSTRUCTION<br><b>POWER SUPPLY AND REGULATION</b><br>INTERNAL POWER SUPPLY<br>PRIMARY 5V REGULATOR<br>SECONDARY REGULATOR<br>MISCELLANEOUS REGISTER<br>IGNS - Ignition status bit<br>OCE - Output compare enable<br>PDC - Power Down Control                 | 45<br>46<br>46<br>R)48<br>49<br>50<br>50<br><b>51</b><br>51<br>51<br>51<br>51<br>52<br>52<br>52<br>52                                           |

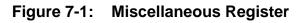

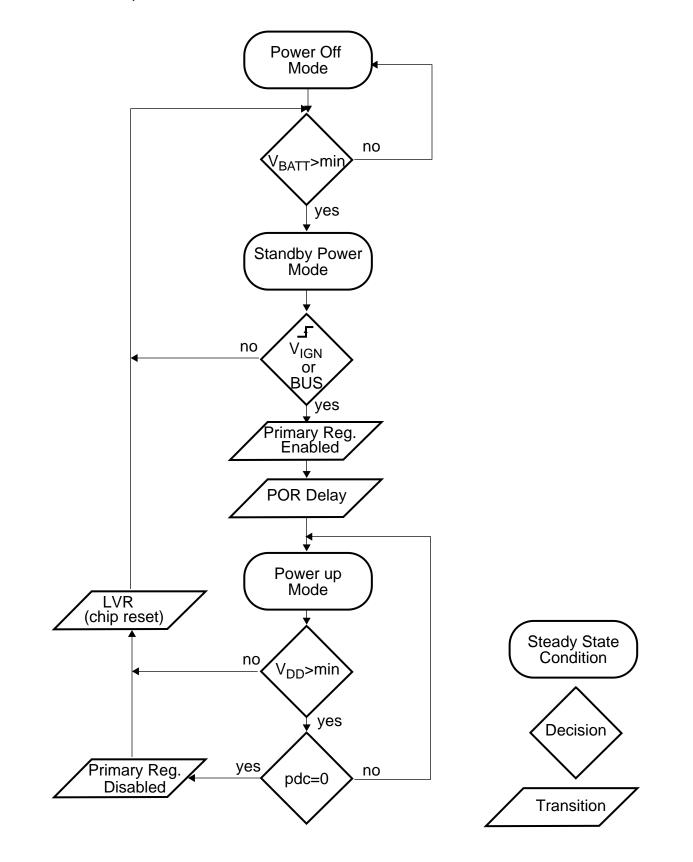

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br><b>SECTION 7</b><br>7.1<br>7.1.1<br>7.1.2<br>7.2<br>7.2.1<br>7.2.1<br>7.2.3<br>7.3                        | EXTERNAL RESET (RESET)<br>INTERNAL RESETS<br>POWER-ON RESET (POR)<br>OPERATION IN STOP AND WAIT<br>COMPUTER OPERATING PROPERLY RESET (COPF<br>LOW-VOLTAGE RESET (LVR)<br>ILLEGAL ADDRESS<br>DISABLED STOP INSTRUCTION<br><b>POWER SUPPLY AND REGULATION</b><br>INTERNAL POWER SUPPLY<br>PRIMARY 5V REGULATOR<br>SECONDARY REGULATOR<br>MISCELLANEOUS REGISTER<br>IGNS - Ignition status bit<br>OCE - Output compare enable<br>PDC - Power Down Control<br>POWER MODING | 45<br>46<br>46<br>R)48<br>49<br>50<br>50<br><b>51</b><br>51<br>51<br>51<br>51<br>52<br>52<br>52<br>52<br>52<br>52                               |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br><b>SECTION 7</b><br>7.1<br>7.1.1<br>7.1.2<br>7.2<br>7.2.1<br>7.2.1<br>7.2.2<br>7.2.3<br>7.3<br>7.3<br>7.4 | EXTERNAL RESET (RESET)<br>INTERNAL RESETS                                                                                                                                                                                                                                                                                                                                                                                                                              | 45<br>46<br>46<br>R)48<br>50<br>50<br><b>51</b><br>51<br>51<br>51<br>51<br>52<br>52<br>52<br>52<br>52<br>52<br>53<br>53                         |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br><b>SECTION 7</b><br>7.1<br>7.1.1<br>7.1.2<br>7.2<br>7.2<br>7.2.1<br>7.2.2<br>7.2.3<br>7.3<br>7.4<br>7.4.1 | EXTERNAL RESET (RESET)<br>INTERNAL RESETS                                                                                                                                                                                                                                                                                                                                                                                                                              | 45<br>46<br>46<br>R)48<br>49<br>50<br>50<br><b>51</b><br>51<br>51<br>51<br>51<br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>53<br>55<br>56       |

| 6.1<br>6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br><b>SECTION 7</b><br>7.1<br>7.1.1<br>7.1.2<br>7.2<br>7.2.1<br>7.2.1<br>7.2.2<br>7.2.3<br>7.3<br>7.3<br>7.4 | EXTERNAL RESET (RESET)<br>INTERNAL RESETS                                                                                                                                                                                                                                                                                                                                                                                                                              | 45<br>46<br>46<br>R)48<br>49<br>50<br>50<br><b>51</b><br>51<br>51<br>51<br>51<br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>55<br>56<br>59 |

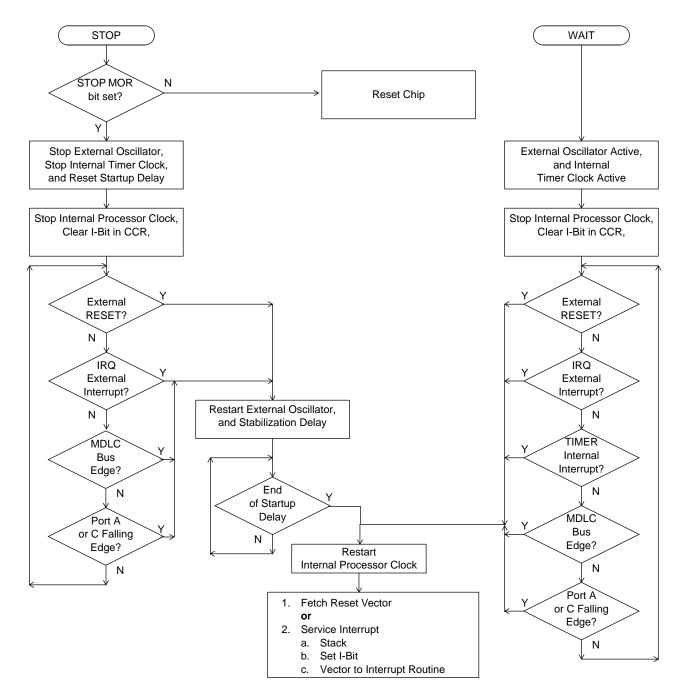

| SECTION 8         | LOW-POWER MODES                                               | 63 |

|-------------------|---------------------------------------------------------------|----|

| 8.1               | STOP INSTRUCTION                                              | 63 |

| 8.1.1             | STOP MODE                                                     |    |

| 8.1.2             | WAIT INSTRUCTION                                              | 65 |

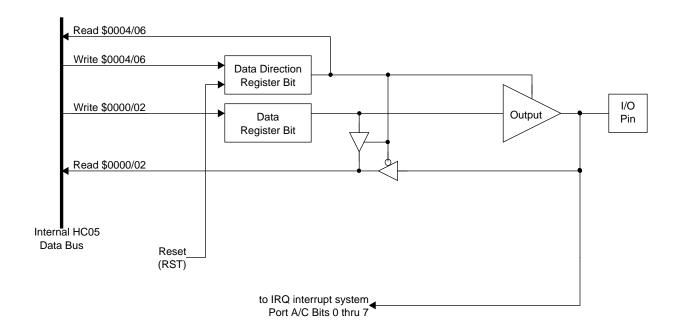

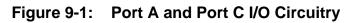

| <b>SECTION 9</b>  | PARALLEL I/O                                                  | 67 |

| 9.1               | PORT A AND PORT C                                             |    |

| 9.1.1             | PORT A/C DATA REGISTERS                                       |    |

| 9.1.2             | PORT A/C DATA DIRECTION REGISTER                              |    |

| 9.1.3             | PORT A/C I/O PIN INTERRUPTS                                   |    |

| 9.2               |                                                               |    |

| 9.2.1             | PORT B DATA REGISTER                                          |    |

| 9.2.2<br>9.3      | PORT B DATA DIRECTION REGISTER<br>PORT D AND PORT E           |    |

| 9.3<br>9.4        | PORT D AND PORT E                                             |    |

| 9.4               | PORT F DATA REGISTER                                          |    |

| 9.4.2             | PORT F DATA DIRECTION REGISTER                                |    |

| ••••=             |                                                               |    |

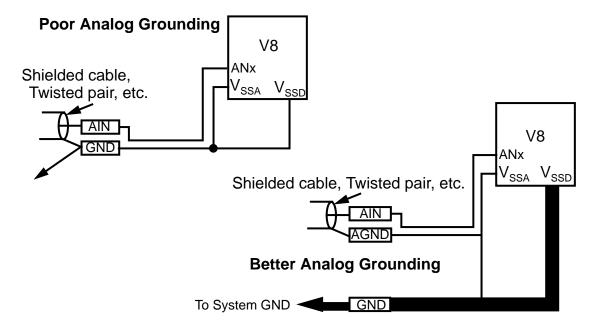

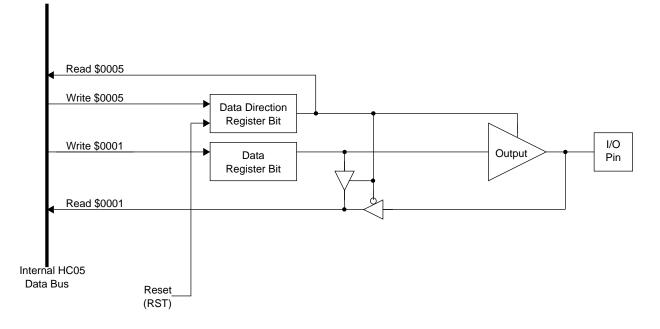

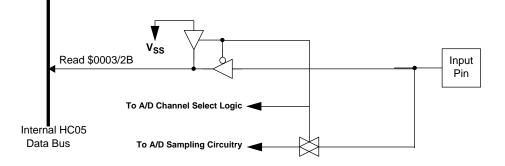

| <b>SECTION 10</b> | A/D CONVERTER                                                 | 71 |

| 10.1              | ANALOG SECTION                                                |    |

| 10.1.1            |                                                               |    |

| 10.1.2            |                                                               | 71 |

| 10.1.3            |                                                               |    |

| 10.2              | CONVERSION PROCESS                                            |    |

| 10.3<br>10.4      |                                                               |    |

| 10.4              | A/D STATUS AND CONTROL REGISTER (ADSCR)<br>A/D DATA REGISTERS |    |

| 10.5              | A/D DATA REGISTERS                                            |    |

| 10.7              | A/D DURING STOP MODE                                          |    |

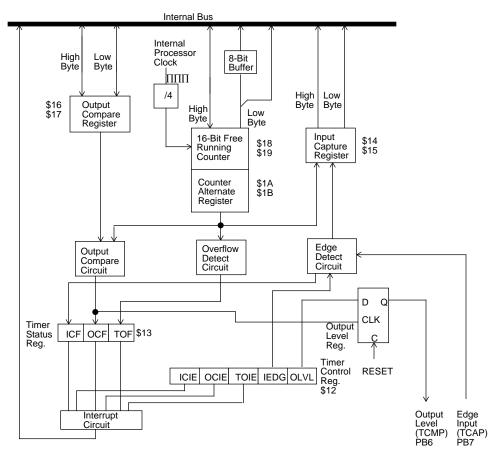

|                   | 16-BIT TIMER                                                  |    |

|                   | COUNTER REGISTER - \$18:\$19, \$1A:\$1B                       |    |

| 11.1              | OUTPUT COMPARE REGISTER - \$16:\$17                           |    |

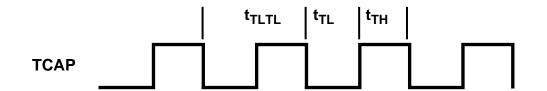

| 11.3              | INPUT CAPTURE REGISTER - \$14:\$15                            |    |

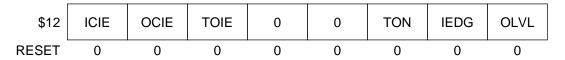

| 11.4              | TIMER CONTROL REGISTER (TCR) - \$12                           |    |

| 11.4.1            |                                                               |    |

| 11.4.2            |                                                               |    |

| 11.4.3            |                                                               |    |

| 11.4.4            | TON - Timer On                                                | 78 |

| 11.4.5            | 1 5                                                           |    |

| 11.4.6            |                                                               |    |

| 11.5              | TIMER STATUS REGISTER (TSR) - \$13                            |    |

| 11.5.1            |                                                               |    |

| 11.5.2            | 1 1 5                                                         |    |

| 11.5.3<br>11.5.4  | 5                                                             |    |

| 11.5.4            | + DIIS U-4 - INUL USEU                                        |    |

| 11.6                                                                                                                                                                                                           | TIMER DURING WAIT MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 11.7                                                                                                                                                                                                           | TIMER DURING STOP MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80                                                                                                                            |

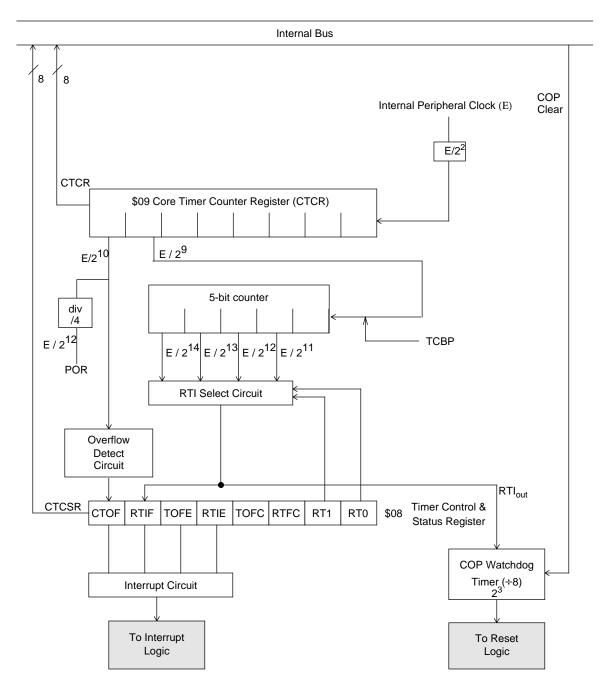

| <b>SECTION 12</b>                                                                                                                                                                                              | CORE TIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 81                                                                                                                            |

| 12.1                                                                                                                                                                                                           | CORE TIMER CTRL & STATUS REGISTER (CTCSR) \$08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                               |

| 12.1.1                                                                                                                                                                                                         | CTOF - Core Timer Over Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 82                                                                                                                            |

| 12.1.2                                                                                                                                                                                                         | 1 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                               |

| 12.1.3                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                               |

| 12.1.4                                                                                                                                                                                                         | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                               |

| 12.1.5                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                               |

| 12.1.6                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                               |

| 12.1.7                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 83                                                                                                                            |

| 12.2                                                                                                                                                                                                           | COMPUTER OPERATING PROPERLY (COP) RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                               |

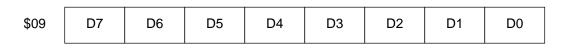

| 12.3<br>12.4                                                                                                                                                                                                   | CORE TIMER COUNTER REGISTER (CTCR) \$09<br>TIMER DURING WAIT MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                               |

|                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                               |

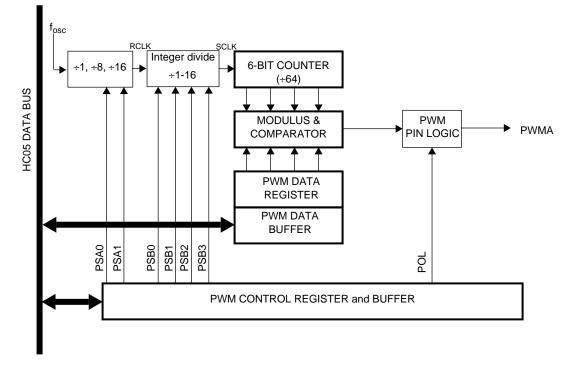

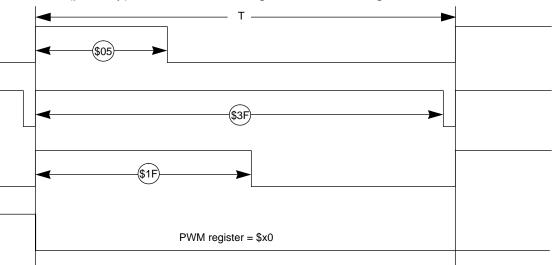

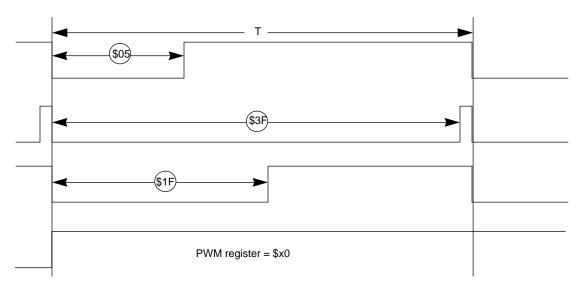

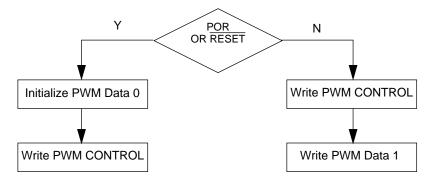

| <b>SECTION 13</b>                                                                                                                                                                                              | PULSE WIDTH MODULATOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                               |

| 13.1                                                                                                                                                                                                           | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                               |

| 13.2                                                                                                                                                                                                           | REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                               |

| 13.2.1                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                               |

| 13.2.2                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                               |

| 13.3                                                                                                                                                                                                           | PWM DURING WAIT MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                               |

| 13.4                                                                                                                                                                                                           | PWM DURING STOP MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                               |

| 13.5                                                                                                                                                                                                           | PWM DURING RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 88                                                                                                                            |

|                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                               |

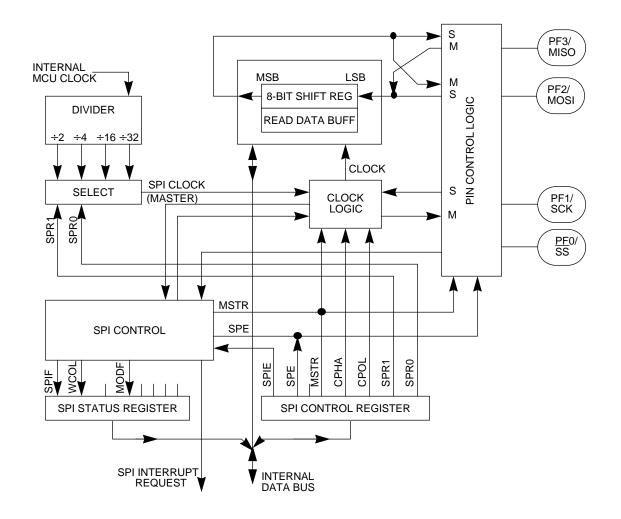

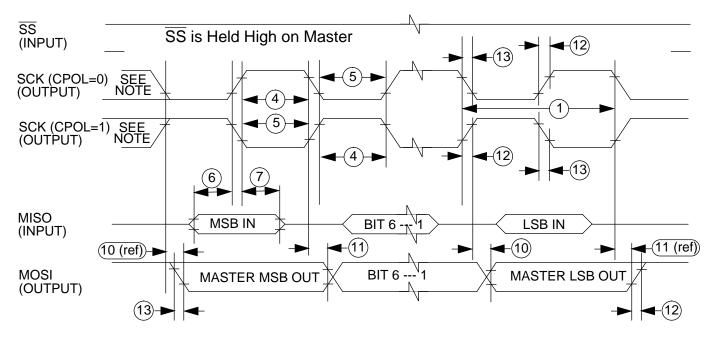

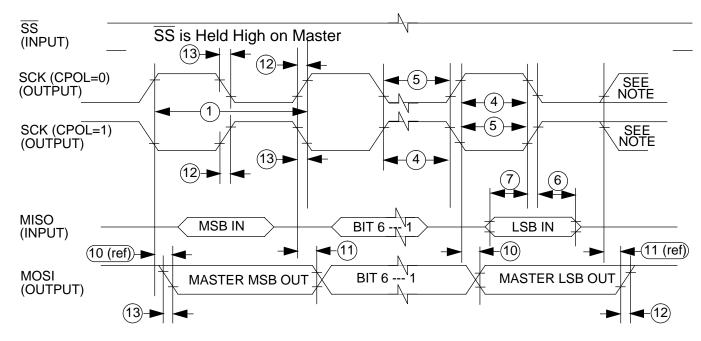

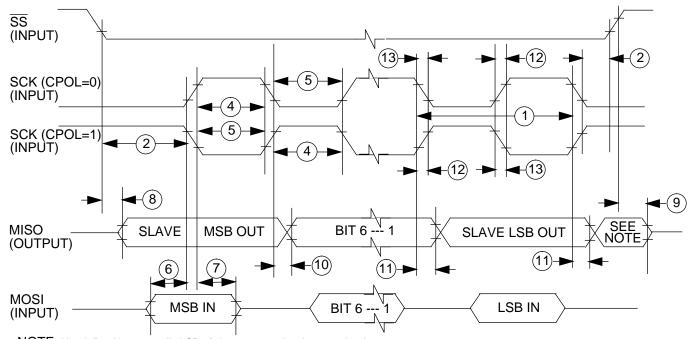

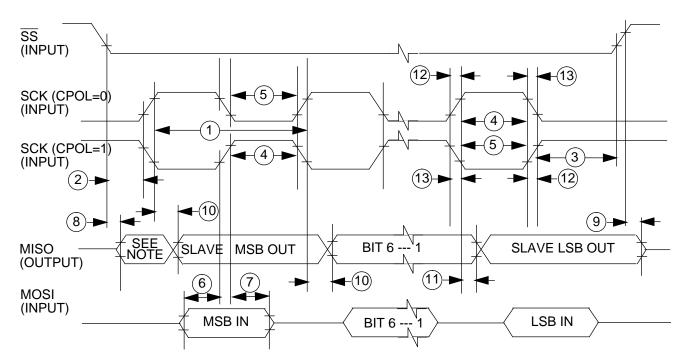

| SECTION 14                                                                                                                                                                                                     | SERIAL PERIPHERAL INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 89                                                                                                                            |

|                                                                                                                                                                                                                | SERIAL PERIPHERAL INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 89                                                                                                                            |

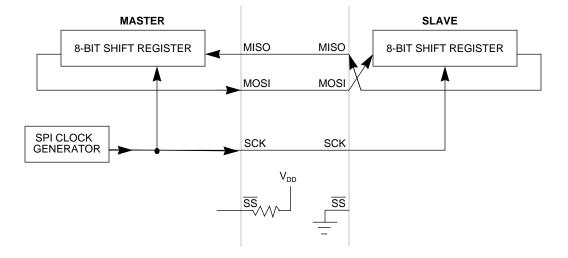

| <b>SECTION 14</b>                                                                                                                                                                                              | SERIAL PERIPHERAL INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 89<br>90                                                                                                                      |

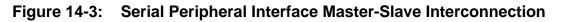

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2                                                                                                                                                                         | SERIAL PERIPHERAL INTERFACE<br>SPI SIGNAL DESCRIPTION<br>Master In Slave Out (MISO/PF3)<br>Master Out Slave In (MOSI/PF2)                                                                                                                                                                                                                                                                                                                                                                                                                            | 89<br>90<br>90                                                                                                                |

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3                                                                                                                                                               | SERIAL PERIPHERAL INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 89<br>90<br>90<br>90                                                                                                          |

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4                                                                                                                                                     | SERIAL PERIPHERAL INTERFACE<br>SPI SIGNAL DESCRIPTION<br>Master In Slave Out (MISO/PF3)<br>Master Out Slave In (MOSI/PF2)<br>Serial Clock (SCK/PF1)<br>Slave Select (SS/PF0)                                                                                                                                                                                                                                                                                                                                                                         | 89<br>90<br>90<br>90<br>91                                                                                                    |

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>14.2                                                                                                                                             | SERIAL PERIPHERAL INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 89<br>90<br>90<br>90<br>91<br>91                                                                                              |

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>14.2<br>14.3                                                                                                                                     | SERIAL PERIPHERAL INTERFACE<br>SPI SIGNAL DESCRIPTION<br>Master In Slave Out (MISO/PF3)<br>Master Out Slave In (MOSI/PF2)<br>Serial Clock (SCK/PF1)<br>Slave Select (SS/PF0)<br>FUNCTIONAL DESCRIPTION<br>SPI REGISTERS                                                                                                                                                                                                                                                                                                                              | 89<br>90<br>90<br>90<br>91<br>91<br>93                                                                                        |

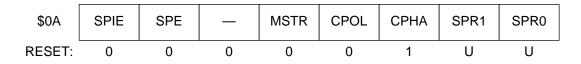

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>14.2<br>14.3<br>14.3                                                                                                                             | SERIAL PERIPHERAL INTERFACE<br>SPI SIGNAL DESCRIPTION<br>Master In Slave Out (MISO/PF3)<br>Master Out Slave In (MOSI/PF2)<br>Serial Clock (SCK/PF1)<br>Slave Select (SS/PF0)<br>FUNCTIONAL DESCRIPTION<br>SPI REGISTERS<br>Serial Peripheral Control Register (SPCR)                                                                                                                                                                                                                                                                                 | 89<br>90<br>90<br>90<br>91<br>93<br>93                                                                                        |

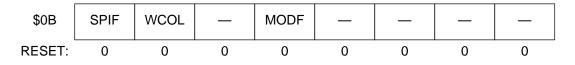

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>14.2<br>14.3<br>14.3.1<br>14.3.1<br>14.3.2                                                                                                       | SERIAL PERIPHERAL INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 89<br>90<br>90<br>91<br>91<br>93<br>93<br>94                                                                                  |

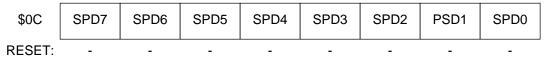

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>14.2<br>14.3<br>14.3.1<br>14.3.2<br>14.3.3                                                                                                       | SERIAL PERIPHERAL INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 89<br>90<br>90<br>91<br>91<br>93<br>93<br>94<br>95                                                                            |

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>14.2<br>14.3<br>14.3<br>14.3.1<br>14.3.2<br>14.3.3<br>14.4                                                                                       | SERIAL PERIPHERAL INTERFACE<br>SPI SIGNAL DESCRIPTION<br>Master In Slave Out (MISO/PF3)<br>Master Out Slave In (MOSI/PF2)<br>Serial Clock (SCK/PF1)<br>Slave Select (SS/PF0)<br>FUNCTIONAL DESCRIPTION<br>SPI REGISTERS<br>Serial Peripheral Control Register (SPCR)<br>Serial Peripheral Status Register (SPSR)<br>Serial Peripheral Data I/O Register (SPDR)<br>SPI IN STOP MODE                                                                                                                                                                   | 89<br>90<br>90<br>91<br>91<br>93<br>93<br>93<br>95<br>96                                                                      |

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>14.2<br>14.3<br>14.3.1<br>14.3.2<br>14.3.3                                                                                                       | SERIAL PERIPHERAL INTERFACE<br>SPI SIGNAL DESCRIPTION<br>Master In Slave Out (MISO/PF3)<br>Master Out Slave In (MOSI/PF2)<br>Serial Clock (SCK/PF1)<br>Slave Select (SS/PF0)<br>FUNCTIONAL DESCRIPTION<br>SPI REGISTERS<br>Serial Peripheral Control Register (SPCR)<br>Serial Peripheral Status Register (SPSR)<br>Serial Peripheral Data I/O Register (SPDR)<br>SPI IN STOP MODE<br>SPI IN STOP MODE                                                                                                                                               | 89<br>90<br>90<br>91<br>91<br>93<br>93<br>93<br>94<br>95<br>96<br>96                                                          |

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>14.2<br>14.3<br>14.3<br>14.3.1<br>14.3.2<br>14.3.3<br>14.4                                                                                       | SERIAL PERIPHERAL INTERFACE<br>SPI SIGNAL DESCRIPTION<br>Master In Slave Out (MISO/PF3)<br>Master Out Slave In (MOSI/PF2)<br>Serial Clock (SCK/PF1)<br>Slave Select (SS/PF0)<br>FUNCTIONAL DESCRIPTION<br>SPI REGISTERS<br>Serial Peripheral Control Register (SPCR)<br>Serial Peripheral Status Register (SPSR)<br>Serial Peripheral Data I/O Register (SPDR)<br>SPI IN STOP MODE                                                                                                                                                                   | 89<br>90<br>90<br>91<br>91<br>93<br>93<br>93<br>94<br>95<br>96<br>96                                                          |

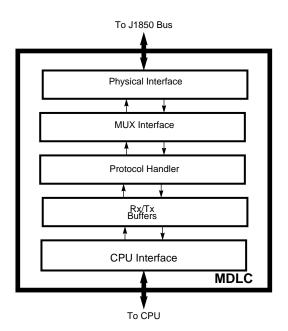

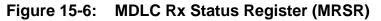

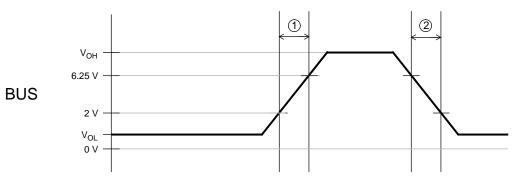

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>14.2<br>14.3<br>14.3<br>14.3.1<br>14.3.2<br>14.3.3<br>14.4<br>14.5<br>SECTION 15<br>15.1                                                         | SERIAL PERIPHERAL INTERFACE<br>SPI SIGNAL DESCRIPTION<br>Master In Slave Out (MISO/PF3)<br>Master Out Slave In (MOSI/PF2)<br>Serial Clock (SCK/PF1)<br>Slave Select (SS/PF0)<br>FUNCTIONAL DESCRIPTION<br>SPI REGISTERS<br>Serial Peripheral Control Register (SPCR)<br>Serial Peripheral Status Register (SPSR)<br>Serial Peripheral Data I/O Register (SPDR)<br>SPI IN STOP MODE<br>SPI IN STOP MODE<br>SPI IN WAIT MODE<br>MESSAGE DATA LINK CONTROLLER.<br>OUTLINE                                                                               | 89<br>90<br>90<br>91<br>91<br>93<br>93<br>93<br>94<br>95<br>96<br>96<br>97<br>98                                              |

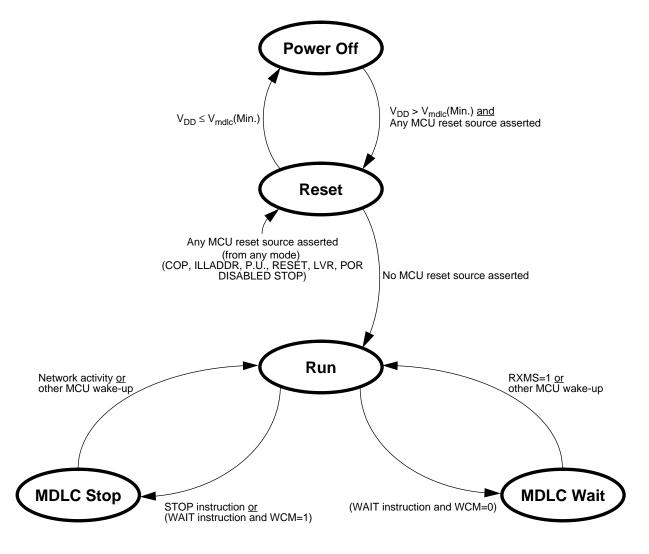

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>14.2<br>14.3<br>14.3<br>14.3.1<br>14.3.2<br>14.3.3<br>14.4<br>14.5<br>SECTION 15<br>15.1<br>15.1                                                 | SERIAL PERIPHERAL INTERFACE<br>SPI SIGNAL DESCRIPTION<br>Master In Slave Out (MISO/PF3)<br>Master Out Slave In (MOSI/PF2)<br>Serial Clock (SCK/PF1)<br>Slave Select (SS/PF0)<br>FUNCTIONAL DESCRIPTION<br>SPI REGISTERS<br>Serial Peripheral Control Register (SPCR)<br>Serial Peripheral Status Register (SPSR)<br>Serial Peripheral Data I/O Register (SPDR)<br>SPI IN STOP MODE<br>SPI IN STOP MODE<br>SPI IN WAIT MODE<br>MESSAGE DATA LINK CONTROLLER<br>OUTLINE<br>MDLC OPERATING MODES.                                                       | 89<br>90<br>90<br>91<br>93<br>93<br>93<br>93<br>95<br>96<br>96<br>96<br>98<br>98<br>99                                        |

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>14.2<br>14.3<br>14.1.4<br>14.2<br>14.3<br>14.3<br>14.3.1<br>14.3.2<br>14.3.3<br>14.4<br>14.5<br>SECTION 15<br>15.1<br>15.1.1<br>15.1.1<br>15.1.2 | SERIAL PERIPHERAL INTERFACE<br>SPI SIGNAL DESCRIPTION<br>Master In Slave Out (MISO/PF3)<br>Master Out Slave In (MOSI/PF2)<br>Serial Clock (SCK/PF1)<br>Slave Select (SS/PF0)<br>FUNCTIONAL DESCRIPTION<br>SPI REGISTERS<br>Serial Peripheral Control Register (SPCR)<br>Serial Peripheral Status Register (SPSR)<br>Serial Peripheral Data I/O Register (SPDR)<br>SPI IN STOP MODE<br>SPI IN STOP MODE<br>SPI IN WAIT MODE<br>MESSAGE DATA LINK CONTROLLER<br>MDLC OPERATING MODES<br>MODE DESCRIPTIONS                                              | 89<br>90<br>90<br>91<br>91<br>93<br>93<br>93<br>93<br>95<br>96<br>96<br>96<br>98<br>99<br>99<br>99                            |

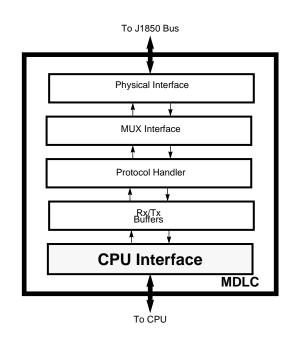

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>14.2<br>14.3<br>14.3<br>14.3.1<br>14.3.2<br>14.3.3<br>14.4<br>14.5<br>SECTION 15<br>15.1<br>15.1.1<br>15.1.2<br>15.2                             | SERIAL PERIPHERAL INTERFACE<br>SPI SIGNAL DESCRIPTION<br>Master In Slave Out (MISO/PF3)<br>Master Out Slave In (MOSI/PF2)<br>Serial Clock (SCK/PF1)<br>Slave Select (SS/PF0)<br>FUNCTIONAL DESCRIPTION<br>SPI REGISTERS<br>Serial Peripheral Control Register (SPCR)<br>Serial Peripheral Status Register (SPSR)<br>Serial Peripheral Data I/O Register (SPDR)<br>SPI IN STOP MODE<br>SPI IN STOP MODE<br>SPI IN WAIT MODE<br>MESSAGE DATA LINK CONTROLLER<br>MDLC OPERATING MODES<br>MODE DESCRIPTIONS<br>MDLC CPU INTERFACE                        | 89<br>90<br>90<br>91<br>91<br>93<br>93<br>93<br>93<br>95<br>96<br>96<br>96<br>98<br>99<br>99<br>99<br>99                      |

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>14.2<br>14.3<br>14.1.4<br>14.2<br>14.3<br>14.3.1<br>14.3.2<br>14.3.3<br>14.4<br>14.5<br>SECTION 15<br>15.1<br>15.1.1<br>15.1.2<br>15.2<br>15.2.1 | SERIAL PERIPHERAL INTERFACE<br>SPI SIGNAL DESCRIPTION<br>Master In Slave Out (MISO/PF3)<br>Master Out Slave In (MOSI/PF2)<br>Serial Clock (SCK/PF1)<br>Slave Select (SS/PF0)<br>FUNCTIONAL DESCRIPTION<br>SPI REGISTERS<br>Serial Peripheral Control Register (SPCR)<br>Serial Peripheral Status Register (SPSR)<br>Serial Peripheral Data I/O Register (SPDR)<br>SPI IN STOP MODE<br>SPI IN STOP MODE<br>SPI IN WAIT MODE<br>MESSAGE DATA LINK CONTROLLER.<br>OUTLINE<br>MDLC OPERATING MODES<br>MODE DESCRIPTIONS<br>MDLC CPU INTERFACE<br>OUTLINE | 89<br>90<br>90<br>91<br>91<br>93<br>93<br>93<br>93<br>93<br>95<br>96<br>96<br>96<br>96<br>98<br>99<br>99<br>101<br>101        |

| SECTION 14<br>14.1<br>14.1.1<br>14.1.2<br>14.1.3<br>14.1.4<br>14.2<br>14.3<br>14.3<br>14.3.1<br>14.3.2<br>14.3.3<br>14.4<br>14.5<br>SECTION 15<br>15.1<br>15.1.1<br>15.1.2<br>15.2                             | SERIAL PERIPHERAL INTERFACE<br>SPI SIGNAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 89<br>90<br>90<br>91<br>91<br>93<br>93<br>93<br>93<br>93<br>95<br>96<br>96<br>96<br>96<br>98<br>99<br>99<br>101<br>101<br>102 |

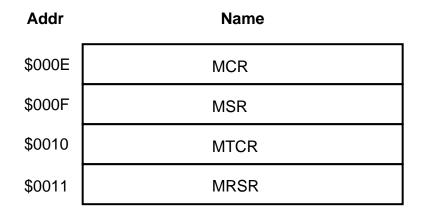

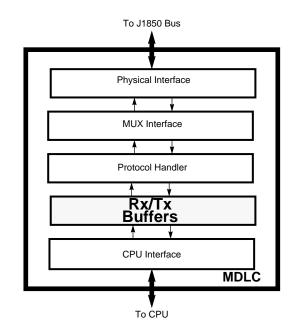

|                      | 15.2.4  | MDLC TX CONTROL REGISTER (MTCR) \$101       | 106 |

|----------------------|---------|---------------------------------------------|-----|

|                      | 15.2.5  | MDLC RX STATUS REGISTER (MRSR) \$111        |     |

|                      | 15.3    | MDLC Rx/Tx BUFFERS1                         | 108 |

|                      | 15.3.1  | OUTLINE1                                    | 108 |

|                      | 15.3.2  | RX BUFFERS1                                 | 110 |

|                      | 15.3.3  | TX BUFFER1                                  | 111 |

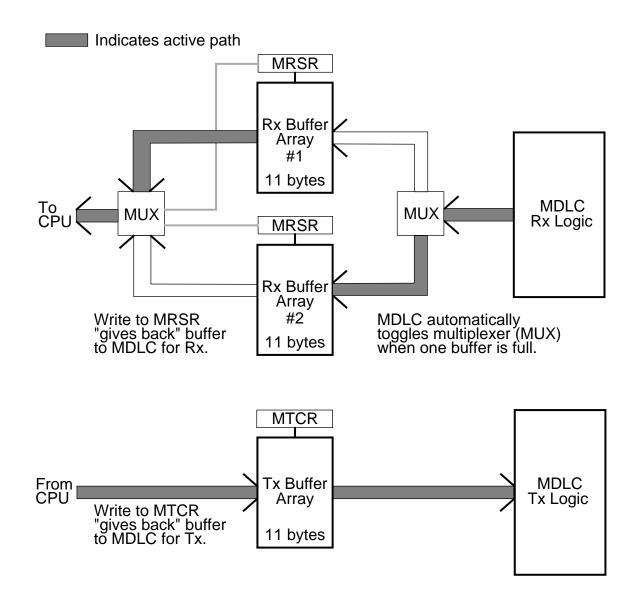

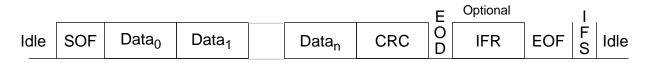

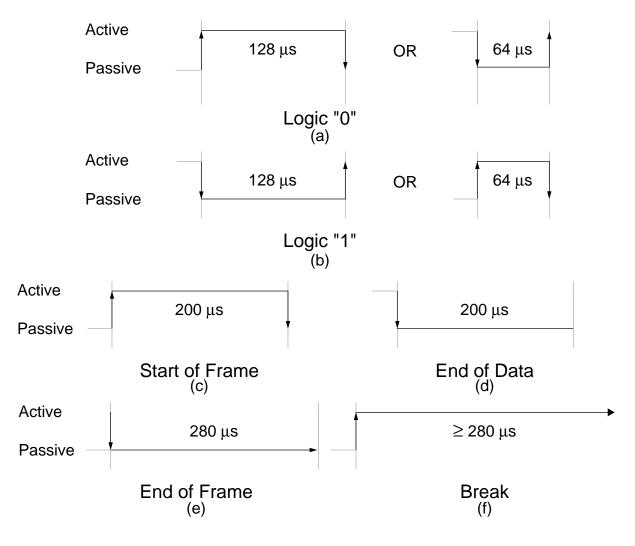

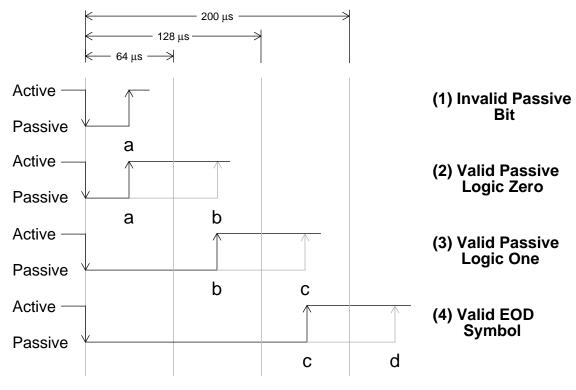

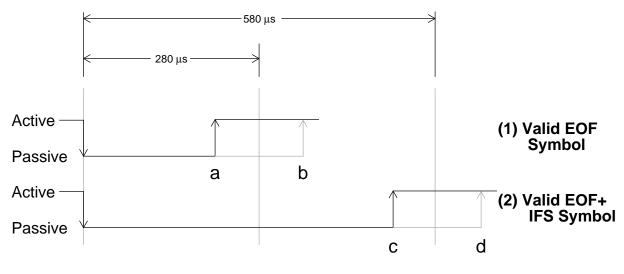

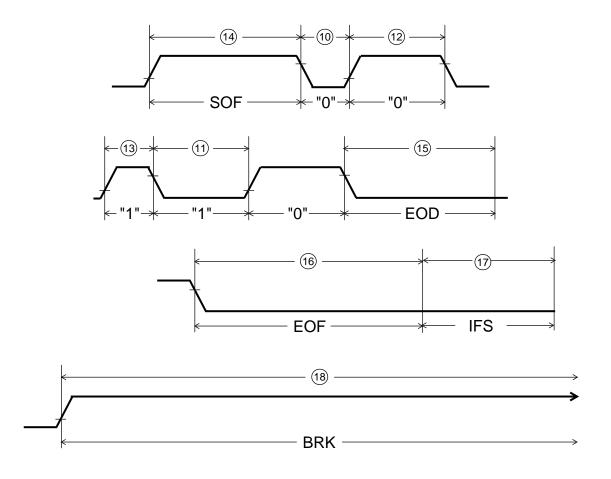

|                      | 15.4    | MDLC PROTOCOL HANDLER1                      | 113 |

|                      | 15.4.1  | OUTLINE1                                    | 113 |