#### **Product Preview**

MC14SM5567/D Rev. 0, 4/2002

MC14SM5567 PCM Codec-Filter

# Freescale Semiconductor, Inc.

The MC14SM5567 is a per channel PCM Codec-Filter, designed to operate in both synchronous and asynchronous applications. This device performs the voice digitization and reconstruction as well as the band limiting and smoothing required for (A-Law) PCM systems.

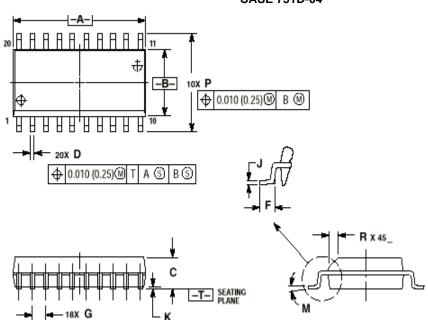

DW SUFFIX SOG PACKAGE CASE 751D

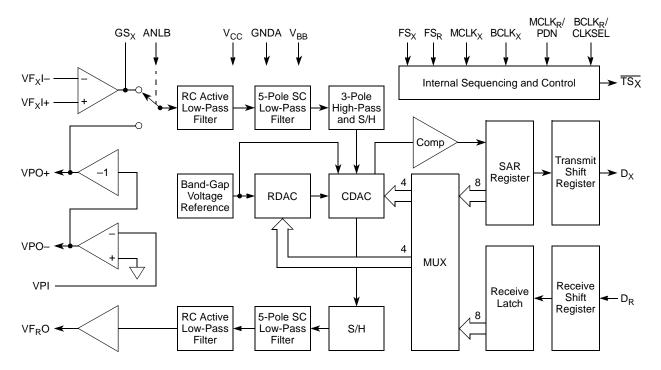

This device has an input operational amplifier whose output is the input to the encoder section. The encoder section immediately low-pass filters the analog signal with an RC filter to eliminate very-high-frequency noise

from being modulated down to the pass band by the switched capacitor filter. From the active R-C filter, the analog signal is converted to a differential signal. From this point, all analog signal processing is done differentially. This allows processing of an analog signal that is twice the amplitude allowed by a single-ended design, which reduces the significance of noise to both the inverted and non-inverted signal paths. Another advantage of this differential design is that noise injected via the power supplies is a common mode signal that is cancelled when the inverted and non-inverted signals are recombined. This dramatically improves the power supply rejection ratio.

After the differential converter, a differential switched capacitor filter band passes the analog signal from 200 Hz to 3400 Hz before the signal is digitized by the differential compressing A/D converter.

The decoder accepts PCM data and expands it using a differential D/A converter. The output of the D/A is low-pass filtered at 3400 Hz and sinX/X compensated by a differential switched capacitor filter. The signal is then filtered by an active R-C filter to eliminate the out-of-band energy of the switched capacitor filter.

This device accepts both long- and short-frame industry standard clock formats.

- Fully Differential Analog Circuit Design for Lowest Noise

- Extended Temperature Range of -40° to 85°C

- Transmit Band-Pass and Receive Low-Pass Filters On-Chip

- Active R-C Pre-Filtering and Post-Filtering

- A-Law Companding

- On-Chip Precision Voltage Reference (2.5 V)

- Typical Power Dissipation of 40 mW, Power Down of 1.0 mW at ±5 V

- Push-Pull Power Drivers with External Gain Adjust

- Analog Loopback

- 20-Pin SOG Package

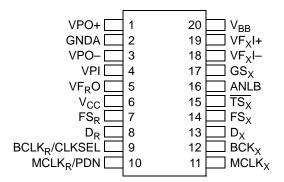

# Freescale Semiconductor, Inc. PIN ASSIGNMENTS

# FUNCTIONAL BLOCK DIAGRAM

# Freescale Semiconductor, Inc. DEVICE DESCRIPTION

A codec-filter is used for digitizing and reconstructing the human voice. This device was developed primarily for the telephone network to facilitate voice switching and transmission. Once the voice is digitized, it may be switched by digital switching methods or transmitted long distance (T1, microwave, satellites, etc.) without degradation. The name codec is an acronym from COder (for the A/D used to digitize voice) and DECoder (for the D/A used for reconstructing voice). A codec is a single device that does both the A/D and D/A conversions.

To digitize intelligible voice requires a signal-to-distortion ratio of about 30 dB over a dynamic range of about 40 dB. This can be accomplished with a linear 13-bit A/D and D/A, but will far exceed the required signal-to-distortion ratio at amplitudes greater than 40 dB below the peak amplitude. This excess performance is at the expense of data per sample. Methods of data reduction are implemented by compressing the 13-bit linear scheme to companded 8-bit schemes. There are two companding schemes used: Mu-255 Law specifically in North America, and A-Law specifically in Europe. These companding schemes are accepted world wide. These companding schemes follow a segmented or piecewise-linear curve formatted as sign bit, three chord bits, and four step bits. For a given chord, all 16 of the steps have the same voltage weighting. As the voltage of the analog input increases, the four step bits double their voltage weighting. This results in an effective resolution of six bits (sign + chord + four step bits) across a 42 dB dynamic range (seven chords above zero, by 6 dB per chord). Table 3 shows the linear quantization levels to PCM words for the A-Law companding scheme.

In a sampling environment, Nyquist theory says that to properly sample a continuous signal, it must be sampled at a frequency higher than twice the signal's highest frequency component. Voice contains spectral energy above 3 kHz, but its absence is not detrimental to intelligibility. To reduce the digital data rate, which is proportional to the sampling rate, a sample rate of 8 kHz was adopted, consistent with a band width of 3 kHz. This sampling requires a low-pass filter to limit the high frequency energy above 3 kHz from distorting the in-band signal. The telephone line is also subject to 50/60 Hz power line coupling, which must be attenuated from the signal by a high-pass filter before the A/D converter.

The D/A process reconstructs a staircase version of the desired in-band signal, which has spectral images of the in-band signal modulated about the sample frequency and its harmonics. These spectral images, called aliasing components, need to be attenuated to obtain the desired signal. The low-pass filter used to attenuate these aliasing components is typically called a reconstruction or smoothing filter.

The MC14SM5567 PCM Codec-Filter, incorporating A-law companding, has the codec, both presampling and reconstruction filters, and a precision voltage reference on-chip, and requires no external components.

# Freescale Semiconductor, Inc. PIN DESCRIPTION

# DIGITAL

#### FS<sub>R</sub> Receive Frame Sync

This is an 8 kHz enable that must be synchronous with  $BCLK_R$ . Following a rising  $FS_R$  edge, a serial PCM word at  $D_R$  is clocked by  $BCLK_R$  into the receive data register.  $FS_R$  also initiates a decode on the previous PCM word. In the absence of  $FS_X$ , the length of the  $FS_R$  pulse is used to determine whether the I/O conforms to the Short Frame Sync or Long Frame Sync convention.

#### D<sub>R</sub> Receive Digital Data Input

## BCLK<sub>R</sub>/CLKSEL Receive Data Clock and Master Clock Frequency Selector

If this input is a clock, it must be between 128 kHz and 4.096 MHz, and synchronous with  $FS_R$ . In synchronous applications this pin may be held at a constant level; then  $BCLK_X$  is used as the data clock for both the transmit and receive sides, and this pin selects the assumed frequency of the master clock (see Table 1).

# MCLK<sub>R</sub>/PDN Receive Master Clock and Power-Down Control

Because of the shared DAC architecture used on this device, only one master clock is needed. Whenever  $FS_X$  is clocking,  $MCLK_X$  is used to derive all internal clocks, and the  $MCLK_R/PDN$  pin merely serves as a power-down control. If  $MCLK_R/PDN$  pin is held low or is clocked (and at least one of the frame syncs is present), the part is powered up. If this pin is held high, the part is powered down. If  $FS_X$  is absent but  $FS_R$  is still clocking, the device goes into receive half-channel mode, and  $MCLK_R$  (if clocking) generates the internal clocks.

#### MCLK<sub>X</sub> Transmit Master Clock

This clock is used to derive the internal sequencing clocks; it must be 1.536, 1.544, or 2.048 MHz.

## BCLK<sub>X</sub> Transmit Data Clock

$BCLK_X$  may be any frequency between 128 kHz and 4.096 MHz, but it should be synchronous with  $MCLK_X$ .

## D<sub>X</sub> Transmit Digital Data Output

This output is controlled by  $FS_X$  and  $BCLK_X$  to output the PCM data word; otherwise this pin is in a high-impedance state.

## FS<sub>X</sub> Transmit Frame Sync

This is an 8 kHz enable that must be synchronous with  $BCLK_X$ . A rising  $FS_X$  edge initiates the transmission of a serial PCM word, clocked by  $BCLK_X$ , out of  $D_X$ . If the  $FS_X$  pulse is high for more than eight  $BCLK_X$  periods, the  $D_X$  and  $TS_X$  outputs will remain in a low-impedance state until  $FS_X$  is brought low. The length of the  $FS_X$  pulse is used to determine whether the transmit and receive digital I/O conforms to the Short Frame Sync or to the Long Frame Sync convention.

#### TS<sub>X</sub> Transmit Time Slot Indicator

This is an open-drain output that goes low whenever the  $D_X$  output is in a low-impedance state (that is, during the transmit time slot when the PCM word is being output) for enabling a PCM bus driver.

## ANLB

## Analog Loopback Control Input

When held high, this pin causes the input of the transmit RC active filter to be disconnected from  $GS_X$  and connected to VPO+ for analog loopback testing. This pin is held low in normal operation.

# ANALOG

#### GS<sub>X</sub> Gain-Setting Transmit

This output of the transmit gain-adjust operational amplifier is internally connected to the encoder section of the device. It must be used in conjunction with  $VF_XI$ - and  $VF_XI$ + to set the transmit gain for a maximum signal amplitude of 2.5 V peak. This output can drive a 600- $\Omega$  load to a 2.5-V peak.

# VF<sub>X</sub>I–

## Voice-Frequency Transmit Input (Inverting)

This is the inverting input of the transmit gain-adjust operational amplifier.

# VF<sub>X</sub>I+ Voice-Frequency Transmit Input (Non-Inverting)

This is the non-inverting input of the transmit gain-adjust operational amplifier.

#### VF<sub>R</sub>O Voice-Frequency Receive Output

This receive analog output is capable of driving a 600- $\Omega$  load to a 2.5-V peak.

# VPI

## **Voltage Power Input**

This is the inverting input to the first receive power amplifier. Both of the receive power amplifiers can be powered down by connecting this input to  $V_{BB}$ .

## VPO-

## **Voltage Power Output (Inverted)**

This inverted output of the receive push-pull power amplifiers can drive 300  $\Omega$  to a 3.3-V peak.

## VPO+

## Voltage Power Output (Non-Inverted)

This non-inverted output of the receive push-pull power amplifier pair can drive 300  $\Omega$  to a 3.3-V peak.

## **POWER SUPPLY**

#### GNDA Analog Ground

This terminal is the reference level for all signals, both analog and digital, and is 0 V.

## V<sub>CC</sub> Positive Power Supply

V<sub>CC</sub> is typically 5 V.

# V<sub>BB</sub> Negative Power Supply

V<sub>BB</sub> is typically –5 V.

# Freescale Semiconductor, Inc. FUNCTIONAL DESCRIPTION

# ANALOG INTERFACE AND SIGNAL PATH

The transmit portion of this codec-filter includes a low-noise gain setting amplifier capable of driving a 600- $\Omega$  load. Its output is fed to a three-pole anti-aliasing pre-filter. This pre-filter incorporates a two-pole Butterworth active low-pass filter, and a single passive pole. This pre-filter is followed by a single ended-to-differential converter that is clocked at 256 kHz. All subsequent analog processing utilizes fully differential circuitry. The next section is a fully-differential, five-pole switched capacitor low-pass filter with a 3.4-kHz pass band. After this filter is a three-pole switched-capacitor high-pass filter having a cutoff frequency of about 200 Hz. This high-pass stage has a transmission zero at dc that eliminates any dc coming from the analog input or from accumulated operational amplifier offsets in the preceding filter stages. The last stage of the high-pass filter is an autozeroed sample and hold amplifier.

One bandgap voltage reference generator and digital-to-analog converter (DAC) are shared by the transmit and receive sections. The autozeroed, switched-capacitor band gap reference generates precise positive and negative reference voltages that are independent of temperature and power supply voltage. A binary-weighted capacitor array (CDAC) forms the chords of the companding structure, while a resistor string (RDAC) implements the linear steps within each chord. The encode process uses the DAC, the voltage reference, and a frame-by-frame autozeroed comparator to implement a successive-approximation conversion algorithm. All of the analog circuitry involved in the data conversion—the voltage reference, RDAC, CDAC, and comparator—are implemented with a differential architecture.

The receive section includes the DAC described above, a sample and hold amplifier, a five-pole 3400-Hz switched capacitor low-pass filter with sinX/X correction, and a two-pole active smoothing filter to reduce the spectral components of the switched capacitor filter. The output of the smoothing filter is a power amplifier that is capable of driving a 600- $\Omega$  load. This device adds a pair of power amplifiers that are connected in a push-pull configuration; two external resistors set the gain of both of the complementary outputs. The output of the second amplifier may be internally connected to the input of the transmit anti-aliasing filter by bringing the ANLB pin high. The power amplifiers can drive unbalanced 300- $\Omega$  loads or a balanced 600- $\Omega$  load; they may be powered down independent of the rest of the chip by tying the VPI pin to V<sub>BB</sub>.

# **MASTER CLOCKS**

Since the codec-filter design has a single DAC architecture, only one master clock is used. In normal operation (both frame syncs clocking), the  $MCLK_X$  is used as the master clock, regardless of whether the  $MCLK_R/PDN$  pin is clocking or low. The same is true if the part is in transmit half-channel mode (FS<sub>X</sub> clocking, FS<sub>R</sub> held low). But if the codec-filter is in the receive half-channel mode, with FS<sub>R</sub> clocking and FS<sub>X</sub> held low,  $MCLK_R$  is used for the internal master clock if it is clocking; if  $MCLK_R$  is low, then  $MCLK_X$  is still used for the internal master clock. Since only one of the master clocks is used at any given time, they need not be synchronous.

The master clock frequency must be 1.536, 1.544, or 2.048 MHz. The frequency that the codec-filter expects, depends on the state of the  $BCL_R/CLKSEL$  pin. The allowable options are shown in Table 1. When a level (rather than a clock) is provided for  $BCLK_R/CLKSEL$ ,  $BCLK_X$  is used as the bit clock for both transmit and receive.

| BCLK <sub>R</sub> /CLKSEL | Master Clock<br>Frequency Expected<br>(MHz) |

|---------------------------|---------------------------------------------|

| Clocked, 1, Open          | 2.048                                       |

| 0                         | 1.536/1.544                                 |

#### Table 1. Master Clock Frequency Determination

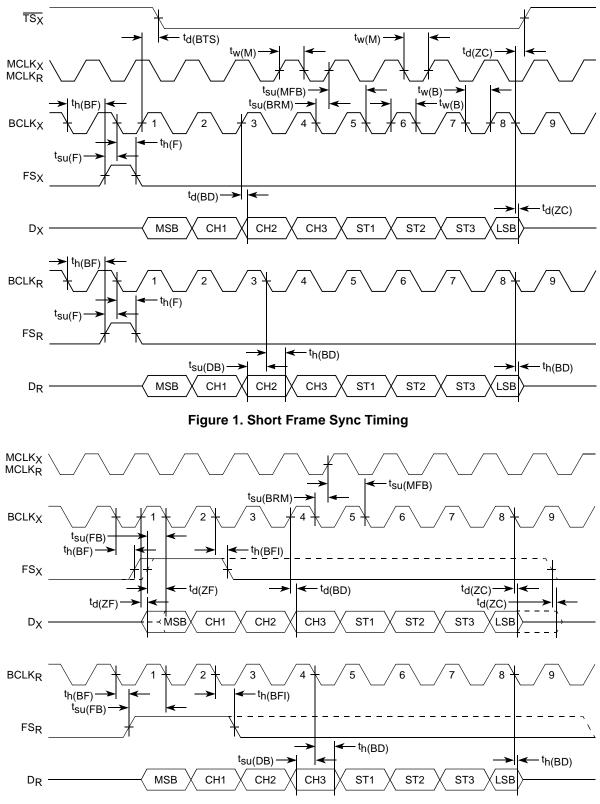

# FRAME SYNCS AND DIGITAL I/O

This codec-filter can accommodate both of the industry standard timing formats. The Long Frame Sync mode is used by the Motorola MC145500 family of codec-filters and the UDLT family of digital loop transceivers. The Short Frame Sync mode is compatible with the IDL (Interchip Digital Link) serial format used in the Motorola ISDN family and by other companies in their telecommunication devices. This codec-filter uses the length of the transmit frame sync (FS<sub>X</sub>) to determine the timing format for both transmit and receive unless the part is operating in the receive half-channel mode.

In the Long Frame Sync mode, the frame sync pulses must be at least three-bit clock periods long. The  $D_X$  and  $\overline{TS_X}$  outputs are enabled by the logical ANDing of  $FS_X$  and  $BCLK_X$ ; when both are high, the sign bit appears at the  $D_X$  output. The next seven rising edges of  $BCLK_X$  clock out the remaining seven bits of the PCM word. The  $D_X$  and  $\overline{TS_X}$  outputs return to a high-impedance state on the falling edge of the eighth bit clock or the falling edge of  $FS_X$ , whichever comes later. The receive PCM word is clocked into  $D_R$  on the eight falling BCLK<sub>R</sub> edges following an  $FS_R$  rising edge.

For Short Frame Sync operation, the frame sync pulses must be one-bit clock period long. On the first BCLK<sub>X</sub> rising edge after the falling edge of BCLK<sub>X</sub> has latched FS<sub>X</sub> high, the D<sub>X</sub> an  $\overline{TS_X}$  outputs are enabled and the sign bit is presented on D<sub>X</sub>. The next seven rising edges of BCLK<sub>X</sub> clock out the remaining seven bits of the PCM word; on the eighth BCLK<sub>X</sub> falling edge, the D<sub>X</sub> and  $\overline{TS_X}$  outputs return to a high-impedance state. On the second falling BCLK<sub>R</sub> edge following an FS<sub>R</sub> rising edge, the receive sign bit is clocked into D<sub>R</sub>. The next seven BCLK<sub>R</sub> falling edges clock in the remaining seven bits of the receive PCM word.

Table 2 shows the coding format of the transmit and receive PCM words.

| Level        | Sign Bits | Chord Bits | Step Bits |

|--------------|-----------|------------|-----------|

| + Full Scale | 1         | 010        | 1010      |

| + Zero       | 1         | 101        | 0101      |

| – Zero       | 0         | 101        | 0101      |

| – Full Scale | 0         | 010        | 1010      |

Table 2. PCM Data Format

# HALF-CHANNEL MODES

In addition to the normal full-duplex operating mode, this codec-filter can operate in both transmit and receive half- channel modes. Transmit half-channel mode is entered by holding  $FS_R$  low. The  $VF_RO$  output goes to analog ground but remains in a low-impedance state (to facilitate a hybrid interface); PCM data at  $D_R$  is ignored. Holding  $FS_X$  low while clocking  $FS_R$ , puts this device in the receive half-channel mode. In this state, the transmit input operational amplifier continues to operate, but the rest of the transmit circuitry is disabled; the  $D_X$  and  $\overline{TS_X}$  outputs remain in a high-impedance state. MCLK<sub>R</sub> is used as the internal

master clock if it is clocking. If  $MCLK_R$  is not clocking, then  $MCLK_X$  is used for the internal master clock, but in that case it should be synchronous with  $FS_R$ . If  $BCLK_R$  is not clocking,  $BCLK_X$  will be used for the receive data, just as in the full-channel operating mode. In receive half-channel mode only, the length of the  $FS_R$  pulse is used to determine whether Short Frame Sync or Long Frame Sync timing is used at  $D_R$ .

# **POWER-DOWN**

Holding both  $FS_X$  and  $FS_R$  low causes the part to go into the power-down state. Power-down occurs approximately 2 ms after the last frame sync pulse is received. An alternative way to put this device in power-down is to hold the MCLK<sub>R</sub>/PDN pin high. When the chip is powered down, the  $D_X$ ,  $\overline{TS_X}$ , and  $GS_X$ outputs are high impedance, the VF<sub>R</sub>O, VPO–, and VPO+ operational amplifiers are biased with a trickle current so that their respective outputs remain stable at analog ground. To return the chip to the power-up state, MCLK<sub>R</sub>/PDN must be low or clocking and at least one of the frame sync pulses must be present. The  $D_X$  and  $\overline{TS_X}$  outputs will remain in a high-impedance state until the second FS<sub>X</sub> pulse after power-up.

| Rating                    |                                                              | Symbol                                                            | Value                                    | Unit |

|---------------------------|--------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------|------|

| DC Supply Voltage         | $V_{CC}$ to $V_{BB}$<br>$V_{CC}$ to GNDA<br>$V_{BB}$ to GNDA |                                                                   | -0.5 to 13<br>-0.3 to 7.0<br>-7.0 to 0.3 | V    |

| Voltage on Any Analog Ir  |                                                              | V <sub>BB</sub> – 0.3 to<br>V <sub>CC</sub> + 0.3                 | V                                        |      |

| Voltage on Any Digital In |                                                              | $\frac{\text{GNDA} - 0.3 \text{ to}}{\text{V}_{\text{CC}} + 0.3}$ | V                                        |      |

| Operating Temperature     | T <sub>A</sub>                                               | -40 to 85                                                         | °C                                       |      |

| Storage Temperature       |                                                              | T <sub>stg</sub>                                                  | -85 to 150                               | °C   |

ABSOLUTE MAXIMUM RATINGS (Voltage Referenced to GNDA)

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid applications of any voltage higher than maximum rated voltages to this high-impedance circuit. For proper operation, it is recommended that V<sub>in</sub> and V<sub>out</sub> be constrained to the range  $V_{SS} \leq (V_{in} \text{ or } V_{out}) \leq V_{DD}$ . Unused inputs must always be tied to an appropriate logic level (e.g., V<sub>BB</sub>, GNDA, or V<sub>CC</sub>).

#### **POWER SUPPLY** ( $T_A = -40^\circ$ to $85^\circ$ C)

| Characteristic                     |                                    | Min          | Тур        | Мах          | Unit |

|------------------------------------|------------------------------------|--------------|------------|--------------|------|

| DC Supply Voltage                  | V <sub>CC</sub><br>V <sub>BB</sub> | 4.75<br>4.75 | 5.0<br>5.0 | 5.25<br>5.25 | V    |

| Active Power Dissipation (No Load) | VPI = V <sub>BB</sub>              |              | 45<br>40   | 70<br>60     | mW   |

| Power-Down Dissipation (No Load)   | VPI = V <sub>BB</sub>              |              | 2.0<br>1.0 | 5.0<br>3.0   | mW   |

#### **DIGITAL LEVELS** ( $V_{CC} = 5 V \pm 5\%$ , $V_{BB} = -5 V \pm 5\%$ , GNDA = 0 V, $T_A = -40^{\circ}$ to $85^{\circ}$ C)

| Characteristic                         |                                                                          | Symbol          | Min                          | Мах | Unit |

|----------------------------------------|--------------------------------------------------------------------------|-----------------|------------------------------|-----|------|

| Input Low Voltage                      |                                                                          | V <sub>IL</sub> | —                            | 0.6 | V    |

| Input High Voltage                     |                                                                          | V <sub>IH</sub> | 2.2                          | _   | V    |

| Output Low Voltage D <sub>x</sub>      | $c \text{ or } \overline{\text{TS}_{X}}, I_{\text{OL}} = 3.2 \text{ mA}$ | V <sub>OL</sub> | —                            | 0.4 | V    |

| Output High Voltage                    | $D_X$ , $I_{OH} = -3.2 \text{ mA}$<br>$I_{OH} = -1.6 \text{ mA}$         | V <sub>OH</sub> | 2.4<br>V <sub>CC</sub> – 0.5 | _   | V    |

| Input Low Current                      | $\text{GNDA} \leq \text{V}_{\text{in}} \leq \text{V}_{\text{CC}}$        | Ι <sub>ΙL</sub> | -10                          | 10  | μA   |

| Input High Current                     | $\text{GNDA} \leq \text{V}_{\text{in}} \leq \text{V}_{\text{CC}}$        | Ι <sub>ΙΗ</sub> | -10                          | 10  | μA   |

| Output Current in High-Impedance State | $GNDA \leq D_X \leq V_{CC}$                                              | I <sub>OZ</sub> | -10                          | 10  | μA   |

#### ANALOG ELECTRICAL CHARACTERISTICS

(V\_{CC} = 5 V ±5%, V\_{BB} = -5 V ±5%, VF\_XI- Connected to GS\_X, T\_A = -40° to 85°C)

| Characteri                                                                                                            | stic                                                              | Min    | Тур   | Max        | Unit |

|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------|-------|------------|------|

| Input Current (–2.5 $\leq$ V <sub>in</sub> $\leq$ 2.5 V)                                                              | VF <sub>X</sub> I+, VF <sub>X</sub> I                             |        | ±0.05 | ±0.2       | μΑ   |

| AC Input Impedance to GNDA (1 kH                                                                                      | lz) VF <sub>X</sub> I+, VF <sub>X</sub> I                         | - 10   | 20    | —          | MΩ   |

| Input Capacitance                                                                                                     | VF <sub>X</sub> I+, VF <sub>X</sub> I                             |        | _     | 10         | pF   |

| Input Offset Voltage of $GS_X$ Op Amp                                                                                 | vF <sub>X</sub> I+, VF <sub>X</sub> I                             |        | —     | ±25        | mV   |

| Input Common Mode Voltage Range                                                                                       | e VF <sub>X</sub> I+, VF <sub>X</sub> I                           | 2.5    | —     | 2.5        | V    |

| Input Common Mode Rejection Rati                                                                                      | o VF <sub>X</sub> I+, VF <sub>X</sub> I                           |        | 65    | —          | dB   |

| Unity Gain Bandwidth of $GS_X$ Op Ar                                                                                  | np (R <sub>load</sub> ≥10 kΩ)                                     | _      | 1000  | —          | kHz  |

| DC Open Loop Gain of GS <sub>X</sub> Op Am                                                                            | p ( $R_{load} \ge 10 \ k\Omega$ )                                 | 75     | _     | —          | dB   |

| Output Load Capacitance for GS <sub>X</sub> C                                                                         | Dp Amp                                                            | 0      | —     | 100        | pF   |

| Output Voltage Range for $GS_X$                                                                                       | $R_{load}$ = 10 kΩ to GND<br>$R_{load}$ = 600 Ω to GND            |        | _     | 3.5<br>2.8 | V    |

| Output Current (-2.8 V $\leq$ V <sub>out</sub> $\leq$ 2.8                                                             | V) GS <sub>X</sub> , VF <sub>R</sub>                              | O ±5.0 | _     | —          | mA   |

| Output Impedance VF <sub>R</sub> O (0 to 3.4 k                                                                        | Hz)                                                               | _      | 1     | —          | Ω    |

| Output Load Capacitance for VF <sub>R</sub> O                                                                         |                                                                   | 0      | —     | 500        | pF   |

| VF <sub>R</sub> O Output DC Offset Voltage Re                                                                         | ferenced to GNDA                                                  | -      | _     | ±100       | mV   |

| Power Drivers                                                                                                         |                                                                   |        | ·     |            |      |

| Input Current (-1 V $\leq$ VPI $\leq$ 1 V)                                                                            | VF                                                                | ์ – เ  | ±0.05 | ±0.5       | μΑ   |

| Input Resistance (-1 V $\leq$ VPI $\leq$ 1 V)                                                                         | VF                                                                | ๆ 5    | 10    | _          | MΩ   |

| Input Offset Voltage (VPI Connected                                                                                   | d to VPO–) VF                                                     | י –    | —     | ±50        | mV   |

| Output Resistance, Inverted Unity G                                                                                   | ain VPO+ or VPO                                                   |        | 1     | —          | Ω    |

| Unity Gain Bandwidth, Open Loop                                                                                       | VPO                                                               |        | 400   | —          | kHz  |

| Load Capacitance ( $\infty \ \Omega \ge R_{load} \ge 30$                                                              | 00 Ω)<br>VPO+ or VPO– to GND                                      | A 0    | _     | 1000       | pF   |

| Gain from VPO- to VPO+ (R <sub>load</sub> = 3<br>at VPO- = 1.77 Vrms, +3 dBm0)                                        | 00 Ω, VPO+ to GNDA Lev                                            | el —   | -1    | _          | V/V  |

| Maximum 0 dBm0 Level for Better t<br>Linearity Over the Range –10 dBm0<br>+3 dBm0 (For R <sub>load</sub> between VPO+ | 0 to $R_{load} = 1200$ s                                          | Ω 3.5  |       |            | Vrms |

| Power Supply Rejection of V <sub>CC</sub> or V<br>(VPO– Connected to VPI)<br>VPO+ or VPO– to GNDA                     | и <sub>вв</sub> 0 to 4 kH:<br>4 to 50 kH                          |        | -     | —          | dB   |

| Differential Power Supply Rejection<br>(VPO– Connected to VPI)                                                        | of V <sub>CC</sub> or V <sub>BB</sub><br>VPO+ to VPO–, 0 to 50 kH | z 50   |       | _          | dB   |

#### ANALOG TRANSMISSION PERFORMANCE

$(V_{CC} = 5 V \pm 5\%, V_{BB} = -5 V \pm 5\%, GNDA = 0 V, 0 dBm0 = 1.2276 Vrms = 4 dBm @ 600 \Omega, FS_X = FS_R = 8 kHz, BCLK_X = MCLK_X = 2.048 MHz Synchronous Operation, VF_XI- Connected to GS_X, T_A = -40° to 85°C Unless Otherwise Noted)$

| Characteristic                                                                                                                                           | End-t                                                   | o-End                                                   | A                                  | /D                                                           | D                                                              | /A                                        | Unit  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------|------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------|-------|

| Characteristic                                                                                                                                           | Min                                                     | Max                                                     | Min                                | Max                                                          | Min                                                            | Max                                       | Unit  |

| Absolute Gain (0 dBm0 @ 1.02 kHz, $T_A = 25^{\circ}C$ , $V_{CC} = 5 V$ , $V_{BB} = -5 V$ )                                                               |                                                         | —                                                       | -0.25                              | -0.25                                                        | -0.25                                                          | 0.25                                      | dB    |

| Absolute Gain Variation with Temperature 0 to 70°C -40° to 85°C                                                                                          |                                                         |                                                         |                                    | ±0.03<br>±0.06                                               |                                                                | ±0.03<br>±0.06                            | dB    |

| Absolute Gain Variation with Power Supply (V <sub>CC</sub> = 5 V, $\pm$ 5%, V <sub>BB</sub> = -5 V, $\pm$ 5%)                                            | -                                                       | _                                                       | -                                  | ±0.02                                                        | _                                                              | ±0.02                                     | dB    |

| Gain vs Level Tone     3 to -40 dBm0       (Relative to -10 dBm0, 1.02 kHz)     -40 to -50 dBm0       -50 to -55 dBm0                                    | 8.0– C                                                  | 0.4<br>0.8<br>1.6                                       | -0.2<br>-0.4<br>-0.8               | 0.2<br>0.4<br>0.8                                            | -0.2<br>-0.4<br>-0.8                                           | 0.2<br>0.4<br>0.8                         | dB    |

| Gain vs Level Pseudo Noise CCITT G.712-10 to -40 dBm0(A-Law Relative to -10 dBm0)-40 to -50 dBm0-50 to -55 dBm0                                          | - I C                                                   |                                                         | -0.25<br>-0.30<br>-0.45            | 0.25<br>0.30<br>0.45                                         | -0.25<br>-0.30<br>-0.45                                        | 0.25<br>0.30<br>0.45                      | dB    |

| Total Distortion With Pseudo Noise CCITT G.714 -3 dBm(<br>-6 to -27 dBm)<br>-34 dBm<br>-40 dBm)<br>-55 dBm)                                              | 035033.1028.2                                           |                                                         | 28<br>35.5<br>33.5<br>28.5<br>13.5 |                                                              | 28.5<br>36<br>34.2<br>30<br>15                                 |                                           | dB    |

| Idle Channel Noise (For End-End and A/D, Note 1)<br>(A-Law, Psophometric Weighted)                                                                       | -                                                       | -70                                                     | _                                  | -70                                                          | _                                                              | -83                                       | dBm0p |

| Frequency Response (Relative to 1.02 kHz @ 0 dBm0) 15 H:<br>50 H:<br>60 H:<br>200 H:<br>300 to 3000 H:<br>3300 H:<br>3400 H:<br>4000 H:<br>4600 H:       | z —<br>z —<br>z —<br>z —0.3<br>z —0.70<br>z —1.6<br>z — | -40<br>-30<br>-26<br>-<br>0.3<br>0.3<br>0<br>-28<br>-60 |                                    | -40<br>-30<br>-26<br>-0.4<br>0.15<br>0.15<br>0<br>-14<br>-32 | -0.15<br>-0.15<br>-0.15<br>-0.15<br>-0.35<br>-0.35<br>-0.8<br> | 0<br>0<br>0.15<br>0.15<br>0<br>-14<br>-30 | dB    |

| In-Band Spurious 300 to 3000 H:<br>(1.02 kHz @ 0 dBm0, Transmit and Receive)                                                                             | z   —                                                   | -48                                                     | -                                  | -48                                                          | _                                                              | -48                                       | dBm0  |

| Out-of-Band Spurious at VF <sub>R</sub> O (300 – 3400 Hz @ 0 dBm0 In)<br>4600 to 7600 Hz<br>7600 to 8400 Hz<br>8400 to 100,000 Hz                        | z 🛛 —                                                   | -30<br>-40<br>-30                                       |                                    |                                                              |                                                                | -30<br>-40<br>-30                         | dB    |

| Idle Channel Noise Selective (8 kHz, Input = GNDA, 30 Hz<br>Bandwidth)                                                                                   | _                                                       | -70                                                     | _                                  | _                                                            |                                                                | -70                                       | dBm0  |

| Absolute Delay (1600 Hz)                                                                                                                                 | —                                                       | —                                                       | —                                  | 315                                                          | -                                                              | 215                                       | μs    |

| Group Delay Referenced to 1600 Hz 500 to 600 Hz<br>600 to 800 H<br>800 to 1000 H<br>1000 to 1600 H<br>1600 to 2600 H<br>2600 to 2800 H<br>2800 to 3000 H | z —<br>z —<br>z —<br>z —<br>z —                         |                                                         |                                    | 220<br>145<br>75<br>40<br>75<br>105<br>155                   | -40<br>-40<br>-30<br>                                          | —<br>—<br>90<br>125<br>175                | μs    |

| Crosstalk of 1020 Hz @ 0 dBm0 from A/D or D/A (Note 2)                                                                                                   |                                                         |                                                         |                                    | -75                                                          | _                                                              | -75                                       | dB    |

#### **ANALOG TRANSMISSION PERFORMANCE (continued)**

$(V_{CC} = 5 V \pm 5\%, V_{BB} = -5 V \pm 5\%, GNDA = 0 V, 0 dBm0 = 1.2276 Vrms = 4 dBm @ 600 \Omega, FS_X = FS_R = 8 kHz, BCLK_X = MCLK_X = 2.048 MHz Synchronous Operation, VF_XI- Connected to GS_X, T_A = -40° to 85°C Unless Otherwise Noted)$

| Characteristic                                                                                              | End-to-End |     | A/D |     | D   | Unit |      |

|-------------------------------------------------------------------------------------------------------------|------------|-----|-----|-----|-----|------|------|

|                                                                                                             |            | Max | Min | Max | Min | Max  | onne |

| Intermodulation Distortion of Two Frequencies of Amplitudes<br>–4 to –21 dBm0 from the Range 300 to 3400 Hz | —          | -41 |     | -41 |     | -41  | dB   |

#### NOTES:

1. Extrapolated from a 1020 Hz @ -50 dBm0 distortion measurement to correct for encoder enhancement.

2. Selectively measured while the A/D is stimulated with 2667 Hz @ -50 dBm0.

#### DIGITAL SWITCHING CHARACTERISTICS

( $V_{CC} = 5 V \pm 5\%$ ,  $V_{BB} = -5 V \pm 5\%$ , GNDA = 0 V, All Signals Referenced to GNDA;  $T_A = -40^{\circ}$  to 85°C,  $C_{load} = 150 \text{ pF}$  Unless Otherwise Noted)

| Characteristic                                                                                             | Symbol               | Min | Тур            | Max  | Unit |

|------------------------------------------------------------------------------------------------------------|----------------------|-----|----------------|------|------|

| Master Clock Frequency MCLK <sub>X</sub> or MCLK <sub>R</sub>                                              | f <sub>M</sub>       | —   | 1.536          | —    | MHz  |

|                                                                                                            |                      | _   | 1.544<br>2.048 | _    |      |

| Minimum Pulse Width High or Low MCLK <sub>x</sub> or MCLK <sub>R</sub>                                     | t <sub>w(M)</sub>    | 100 |                |      | ns   |

| Minimum Pulse Width High or Low BCLK <sub>x</sub> or BCLK <sub>B</sub>                                     | t <sub>w(B)</sub>    | 50  |                |      | ns   |

| Minimum Pulse Width Low FS <sub>X</sub> or FS <sub>R</sub>                                                 | t <sub>w(FL)</sub>   | 50  |                |      | ns   |

| Rise Time for all Digital Signals                                                                          | t <sub>r</sub>       | _   | _              | 50   | ns   |

| Fall Time for all Digital Signals                                                                          | t <sub>f</sub>       | _   |                | 50   | ns   |

| Bit Clock Data Rate BCLK <sub>X</sub> or BCLK <sub>R</sub>                                                 | f <sub>B</sub>       | 128 |                | 4096 | kHz  |

| Setup Time from BCLK <sub>X</sub> Low to MCLK <sub>R</sub> High                                            | t <sub>su(BRM)</sub> | 50  | _              | _    | ns   |

| Setup Time from MCLK <sub>X</sub> High to BCLK <sub>X</sub> Low                                            | t <sub>su(MFB)</sub> | 20  | —              |      | ns   |

| Hold Time from $BCLK_X$ (BCLK <sub>R</sub> ) Low to $FS_X$ (FS <sub>R</sub> ) High                         | t <sub>h(BF)</sub>   | 20  | _              | _    | ns   |

| Setup Time for $FS_X$ (FS <sub>R</sub> ) High to BCLK <sub>X</sub> (BCLK <sub>R</sub> ) Low for Long Frame | t <sub>su(FB)</sub>  | 80  | _              | —    | ns   |

| Delay Time from $BCLK_X$ High to $D_X$ Data Valid                                                          | t <sub>d(BD)</sub>   | 20  | 60             | 140  | ns   |

| Delay Time from $BCLK_X$ High to $\overline{TS_X}$ Low                                                     | t <sub>d(BTS)</sub>  | 20  | 50             | 140  | ns   |

| Delay Time from the Eighth $BCLK_X$ Low of $FS_X$ Low to $D_X$ Output Disabled                             | t <sub>d(ZC)</sub>   | 50  | 70             | 140  | ns   |

| Delay Time to Valid Data from $FS_X$ or $BCLK_X$ , Whichever is Later                                      | t <sub>d(ZF)</sub>   | 20  | 60             | 140  | ns   |

| Setup Time from D <sub>R</sub> Valid to BCLK <sub>X</sub> Low                                              | t <sub>su(DB)</sub>  | 0   | —              | —    | ns   |

| Hold Time from BCLK <sub>R</sub> Low to D <sub>R</sub> Invalid                                             | t <sub>h(BD)</sub>   | 50  | —              | —    | ns   |

| Setup Time from $FS_X(FS_R)$ High to $BCLK_X(BCLK_R)$ Low in Short Frame                                   | t <sub>su(F)</sub>   | 50  | —              | —    | ns   |

| Hold Time from $BCLK_X$ ( $BCLK_R$ ) Low to $FS_X$ ( $FS_R$ ) Low in Short Frame                           | t <sub>h(F)</sub>    | 50  | —              | —    | ns   |

| Hold Time from Second Period of $BCLK_X$ ( $BCLK_R$ ) Low to $FS_X$ ( $FS_R$ ) Low in Long Frame           | t <sub>h(BFI)</sub>  | 50  | —              | —    | ns   |

Figure 2. Long Frame Sync Timing

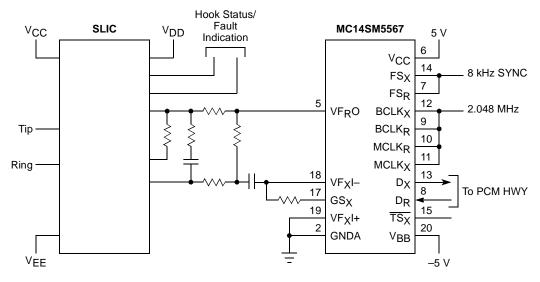

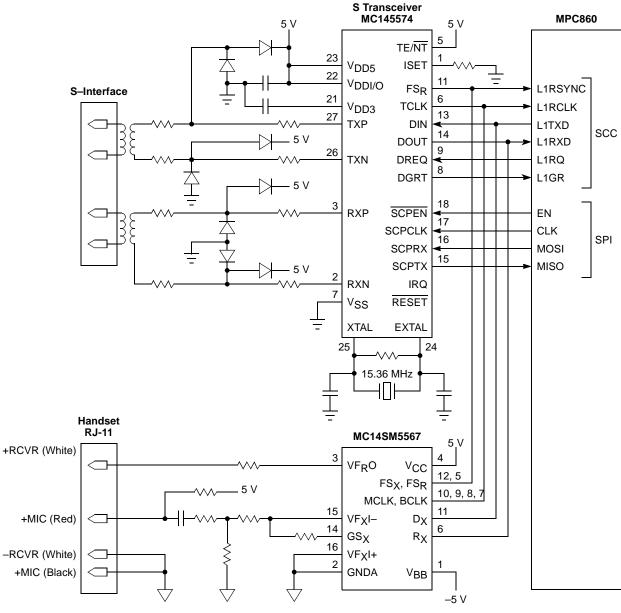

Figure 3. Single Party Channel Unit

Figure 4. ISND Voice/Data Terminal

|              |                 |              | Normalized              |      |       |       | Digital | Code |      |      |      | Normalized |

|--------------|-----------------|--------------|-------------------------|------|-------|-------|---------|------|------|------|------|------------|

| Chord<br>No. | No. of<br>Steps | Step<br>Size | Encode<br>Decision      | 1    | 2     | 3     | 4       | 5    | 6    | 7    | 8    | Decode     |

| 110.         | Oteps           | 0120         | Levels                  | Sign | Chord | Chord | Chord   | Step | Step | Step | Step | Levels     |

|              |                 |              | — 4096 —<br>3968 —      | 1    | 0     | 1     | 0       | 1    | 0    | 1    | 0    | 4032       |

| 7            | 16              | 128          | 2176 —                  |      |       |       | :       |      |      |      |      | :          |

|              |                 |              |                         | 1    | 0     | 1     | 0       | 0    | 1    | 0    | 1    | 2112       |

| 6            | 16              | 64           | — 2048 —<br>:<br>1088 — |      |       |       | ÷       |      |      |      |      | :          |

| 0            | 10              | 04           | - 1024                  | 1    | 0     | 1     | 1       | 0    | 1    | 0    | 1    | 1056       |

| 5            | 16              | 32           | - 1024<br>              |      |       |       | :       |      |      |      |      | :          |

| 5            | 10              | 52           | 512                     | 1    | 0     | 0     | 0       | 0    | 1    | 0    | 1    | 528        |

| 4            | 16              | 16           | - 512 -<br>:<br>272 -   |      |       |       | :       |      |      |      |      | :          |

| 4            | 10              | 10           | 256                     | 1    | 0     | 0     | 1       | 0    | 1    | 0    | 1    | 264        |

| 3            | 16              | 8            | - 236 -<br>:<br>136 -   |      |       |       | :       |      |      |      |      | :          |

| 5            | 10              | 0            | - 128 -                 | 1    | 1     | 1     | 0       | 0    | 1    | 0    | 1    | 132        |

| 2            | 16              | 4            | - 128 -<br>:<br>68 -    |      |       |       | :       |      |      |      |      | :          |

| 2            | 10              | -            | 64                      | 1    | 1     | 1     | 1       | 0    | 1    | 0    | 1    | 66         |

| 1            | 32              | 2            | - 04 -<br>:<br>2 -      |      |       |       | :       |      |      |      |      | :          |

| I            | 52              |              | 0                       | 1    | 1     | 0     | 1       | 0    | 1    | 0    | 1    | 1          |

#### **Table 3. A-Law Encode-Decode Characteristics**

#### NOTES:

Characteristics are symmetrical about analog zero with sign bit = 0 for negative analog values.

Digital code includes alternate bit inversion, as specified by CCITT.

**DW SUFFIX** SOG PACKAGE CASE 751D-04

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: MILLIMETER. 3. DIMENSIONS A AND B DO NOT INCLUDE

- MOLD PROTRUSION.

- 4. MAXIMUM MOLD PROTRUSION 0.150

- (0.006) PER SIDE. 5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 (0.005) TOTAL IN EXCESS OF D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIN | IETERS | INC   | HES   |

|-----|--------|--------|-------|-------|

| DIM | MIN    | MAX    | MIN   | MAX   |

| Α   | 12.65  | 12.95  | 0.499 | 0.510 |

| В   | 7.40   | 7.60   | 0.292 | 0.299 |

| С   | 2.35   | 2.65   | 0.093 | 0.104 |

| D   | 0.35   | 0.49   | 0.014 | 0.019 |

| F   | 0.50   | 0.90   | 0.020 | 0.035 |

| G   | 1.27   | BSC    | 0.050 | BSC   |

| J   | 0.25   | 0.32   | 0.010 | 0.012 |

| ĸ   | 0.10   | 0.25   | 0.004 | 0.009 |

| М   | 0      | 7      | 0     | 7     |

| Р   | 10.05  | 10.55  | 0.395 | 0.415 |

| R   | 0.25   | 0.75   | 0.010 | 0.029 |

#### **Table 4. Document Revision History**

| Rev. No. | Substantive Change(s) |

|----------|-----------------------|

| 0        | Initial release.      |

**Freescale Semiconductor, Inc.** THIS PAGE INTENTIONALLY LEFT BLANK

Home Page: www.freescale.com email: support@freescale.com USA/Europe or Locations Not Listed: Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH **Technical Information Center** Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com Japan: Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 2666 8080 support.japan@freescale.com Asia/Pacific: Freescale Semiconductor Hong Kong Ltd. **Technical Information Center** 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.