Technical Data

MC44CD02 Version 3.3

27 APR 2006

MC44CD02 Wideband

Zero-IF Direct

Conversion Receiver

Single Chip Wideband Zero-IF Direct Conversion Receiver Front-End IC for Hand Held Portable Convergence Terminals

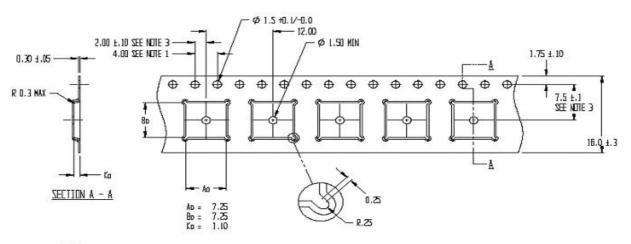

#### **Ordering Information**

| Device                                  | Temp Range     | Package |  |  |  |

|-----------------------------------------|----------------|---------|--|--|--|

| MC44CD02FC,R2                           | -30°C to +85°C | QFN48   |  |  |  |

| NOTE: For tape and reel, add R2 suffix. |                |         |  |  |  |

# MC44CD02 Data Sheet Version 3.3

Original Release Date: 18 OCT 2004 Revised: 27 APR 2006

WMSG EMEA Radio Product Division Freescale, Inc.

| Version Number | Revision Date | Description of Changes                                                                                                                                                                                                                                                                                                                                         |                                 |

|----------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 1.0            | 12/15/2004    | Initial version.                                                                                                                                                                                                                                                                                                                                               |                                 |

| 2.0            | 10/03/2005    | Major revision (filtering, WBD, packaging, clock, LOP, I2C)                                                                                                                                                                                                                                                                                                    | All pages                       |

| 3.0            | 11/28/2005    | All sections: typos and general comments updated First public release                                                                                                                                                                                                                                                                                          | All pages                       |

| 3.1            | 12/06/2005    | Added marking and shipping informations                                                                                                                                                                                                                                                                                                                        | p 79                            |

| 3.2            | 01/19/2006    | Corrected typo on pin#31/37 Corrected typo on startup time typical value (parameter 1.7)  Modified LO leakage parameter 2.6 in table A.4 into parameter 3.15 in table A.5  Correction of table 4-6 (120k and 470k swapped)  Added explanations on how to use the bit PADCTRL (2 write operations required)  Changed marking specification (no more DVB-H logo) | All pages                       |

| 3.3            | 04/27/2006    | Changed parameter 8.2 (LVDS common voltage) Detailed conditions for WBD calibration  Added parameter type 5.51 in table A-12 Added parameter type from 8.8 to 8.15 in table A-14                                                                                                                                                                               | p 73<br>p 39<br>p 71<br>p 73,74 |

| Intro                                                                                                        | oduction                                                                                                                                                                         | 7                    |

|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1.1                                                                                                          | Overview                                                                                                                                                                         | 7                    |

| 1.2                                                                                                          | Glossary                                                                                                                                                                         | 8                    |

| 1.3                                                                                                          | Features                                                                                                                                                                         | 10                   |

| 1.4                                                                                                          | Modes of Operation                                                                                                                                                               | 11                   |

| 1.5                                                                                                          | Block Diagram                                                                                                                                                                    | 11                   |

| Pin                                                                                                          | Description                                                                                                                                                                      | 13                   |

| 2.1                                                                                                          | MC44CD02 Pin Assignment & Package                                                                                                                                                | 13                   |

| 2.2                                                                                                          | MC44CD02 Pin List                                                                                                                                                                | 15                   |

|                                                                                                              |                                                                                                                                                                                  |                      |

|                                                                                                              | Communication And Registers                                                                                                                                                      | 17                   |

| I2C                                                                                                          | Communication And Registers  Overview                                                                                                                                            |                      |

| I2C                                                                                                          | Overview                                                                                                                                                                         | 17                   |

| 3.1<br>3.2<br>3.3                                                                                            | Overview                                                                                                                                                                         | 17                   |

| 3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5<br>3.3.6<br>3.3.7<br>3.3.8<br>3.3.9<br>3.3.10 | Overview  Memory Map  Register Descriptions  MODE — Mode Register PLLR1 — PLL Control Register #1 PLLR2 — PLL Control Register #2 WBDCR1— Wide Band Detector Control Register #1 | 17192021222224252729 |

| 3.3.15                                                             | #TLTST — Tracking Loop Test Register                                                                                                                                               | .31                                           |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Fun                                                                | ctional Description                                                                                                                                                                | 33                                            |

| 4.1                                                                | Modes Of Operation                                                                                                                                                                 | . 33                                          |

| 4.1.1<br>4.1.2<br>4.1.3                                            | Normal Operation Mode                                                                                                                                                              | .33                                           |

| 4.2                                                                | Filtering                                                                                                                                                                          | . 35                                          |

| 4.3                                                                | Control Loops                                                                                                                                                                      | . 35                                          |

| 4.3.1.<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.4.<br>4.3.4.              | AGC Loops  1 RF AGC Control Loop  2 Baseband AGC control loop  DC Offset Correction  Filter Tracking  Common Mode Voltages  1 I/Q Buffers Outputs  2 CLK_OUT Outputs  I/Q Mismatch | .36<br>.36<br>.36<br>.36<br>.36               |

| 4.4                                                                | Reference Clock Configuration                                                                                                                                                      | . 37                                          |

| 4.5                                                                | WBD Functional Description                                                                                                                                                         | . 38                                          |

| 4.5.3                                                              | General  Normal Mode                                                                                                                                                               | .38                                           |

| 4.6                                                                | OSC Functional Description                                                                                                                                                         | . 40                                          |

| 4.6.2.<br>4.6.2.<br>4.6.2.<br>4.6.2.<br>4.6.2.<br>4.6.2.<br>4.6.3. | General  Normal Mode                                                                                                                                                               | .40<br>.40<br>.40<br>.41<br>.41<br>.42<br>.42 |

| 4.7                                                                | PLL Functional Description                                                                                                                                                         | . 44                                          |

| _                  | General                                                      |                     |

|--------------------|--------------------------------------------------------------|---------------------|

|                    | Normal Mode                                                  |                     |

|                    | 1 PLL Characteristics                                        |                     |

| 4.7.2.4            | 2 Loop Filter Considerations                                 | <del>44</del><br>15 |

| 4.7.3              | Deep Sleep & Fower Down Mode                                 | 40                  |

| 4.0                | DEM Eurotional Description                                   | 46                  |

| 4.8                | REM Functional Description                                   | 40                  |

| 4.8.1              | General                                                      | 46                  |

| 4.8.2              | Normal Mode                                                  |                     |

| 4.8.3              | Deep Sleep & Power Down Mode                                 | 46                  |

|                    |                                                              |                     |

| 4.9                | LOP Functional Description                                   | 47                  |

| 404                | •                                                            |                     |

| 4.9.1              | General                                                      |                     |

| 4.9.2<br>4.9.3     | Normal Mode                                                  |                     |

| 4.9.3              | Deep Sleep & Fower Down Mode                                 | 47                  |

| 4 40               | MID Eurotional Decemention                                   | 40                  |

| 4.10               | MLP Functional Description                                   | 40                  |

| 4.10.1             | General                                                      | 48                  |

|                    | Normal Mode                                                  |                     |

| 4.10.3             | B Deep Sleep & Power Down Mode                               | 49                  |

|                    |                                                              |                     |

| Initia             | alization/Application Information                            | 50                  |

|                    | rr                                                           |                     |

| 5.1                | Reset Sources                                                | 50                  |

| J. 1               | Neset Sources                                                | 50                  |

| <b>5</b> 0         | Annella attantia la farma attan                              | F.4                 |

| 5.2                | Application Information                                      | 51                  |

| 5.2.1              | Application Schematic                                        | 51                  |

|                    | Bill Of Material                                             |                     |

| 5.2.3              | Applications Recommendations                                 | 54                  |

|                    | 1 ˙RF Inputs                                                 |                     |

| 5.2.3.2            |                                                              | 54                  |

| 5.2.3.             |                                                              |                     |

| 5.2.3.4            | 4 Crystal Oscillator                                         | 55                  |

| 5.2.3.             |                                                              | 56                  |

| 5.2.3.6            |                                                              |                     |

| 5.2.3.5<br>5.2.3.8 |                                                              | 5 <i>1</i>          |

| 5.2.3.9            |                                                              |                     |

| 5 2 3              | 10 Wideband Detector Response Time Calculation               | 50<br>58            |

| 5.2.3              | 11 Controlling The Gain Of An External LNA Using the LOP Pin | 50<br>59            |

| 5.2.0.             | 333 34 34 External Elift 30 g tilo Edi 1                     |                     |

| Pofo               | erences                                                      | 60                  |

| 1/616              | 71 GIIUG3                                                    | 00                  |

|                    |                                                              |                     |

|                    |                                                              |                     |

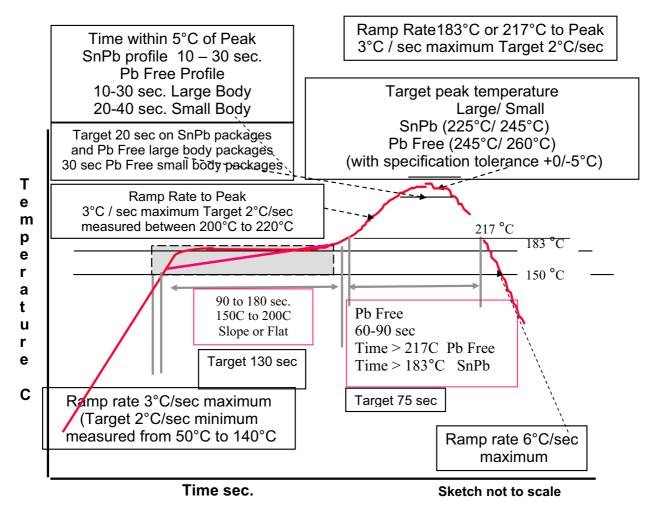

|             | MC44CD02 Thermal Specifications                   | .61 |

|-------------|---------------------------------------------------|-----|

| A.2         | MC44CD02 Moisture Sensitivity Level Consideration |     |

| A.3         | MC44CD02 ESD Specifications                       |     |

| A.4         | General MC44CD02 Electrical Specifications        |     |

| A.5         | MC44CD02 RF Performances                          | .64 |

| A.6         | RFLNA Electrical Specifications                   |     |

| <b>A</b> .7 | WBD Electrical Specifications                     | .68 |

| <b>A.8</b>  | MIXER Electrical Specifications                   | .69 |

| A.9         | PMA Electrical Specifications                     | .70 |

| A.10        | LPF Electrical Specifications                     | .71 |

| A.11        | OSC Electrical Specifications                     | .73 |

| A.12        | PLL Electrical Specifications                     | .75 |

| A.13        | REM Electrical Specifications                     | .76 |

| A.14        | LOP Electrical Specifications                     | .77 |

| A.15        | MLP Electrical Specifications                     | .78 |

| A.16        | RCI Electrical Specifications                     | .79 |

| Marki       | ng, Shipping Instructions & Case Outline          | 80  |

#### 1.1 Overview

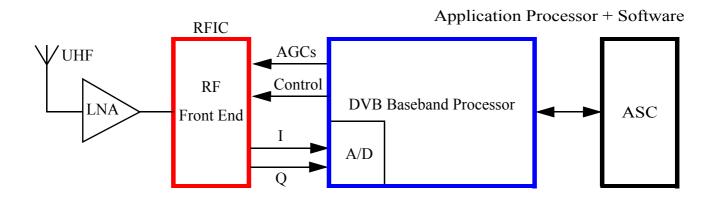

The MC44CD02 is a Single Chip Wideband Zero-IF Direct Conversion Receiver Front-End IC intended to be associated with an IQ baseband OFDM demodulator and an external LNA (see **Figure 1-1**).

Figure 1-1 Block Diagram of a DVB-H chipset

The MC44CD02 chip is targeted for terminals dedicated in Integrated Cellular Phones (Category 3 for Hand Held Portable Convergence Terminals). This category is described in the EICTA-TAC-MBRAI RF Specification (reference [1]), and exhibits the following attributes:

- Both cellular and DVB-H radios integrated in the terminal.

- Battery powered.

- Moved during reception.

- Low gain integrated antenna.

The system is based on DVB-H standard and shall be capable of correctly demodulating all modes specified in the EN 300 744 specification (reference [2]), except the code rates 5/6 and 7/8.

The MC44CD02 covers the UHF bands IV and V (470-862MHz) and is able to handle 6, 7 or 8 MHz bandwidth channels in this range.

This device is targeted to provide an optimum solution where the power consumption is the major constraint for small battery operated devices.

It is designed using the CDR1BiGCMOS process with the SiGe (HBT) option and electroplated copper inductors.

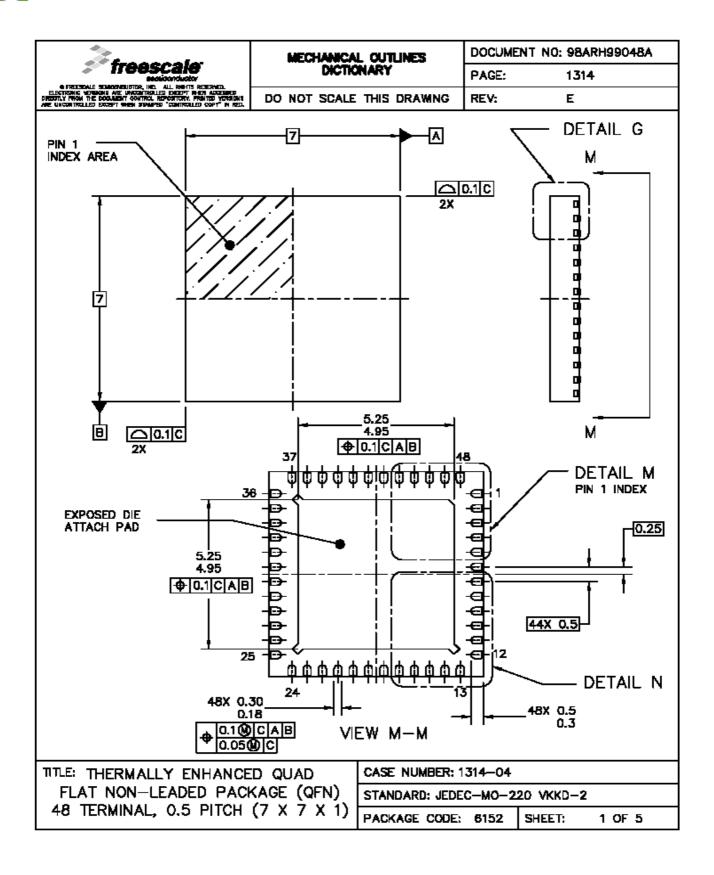

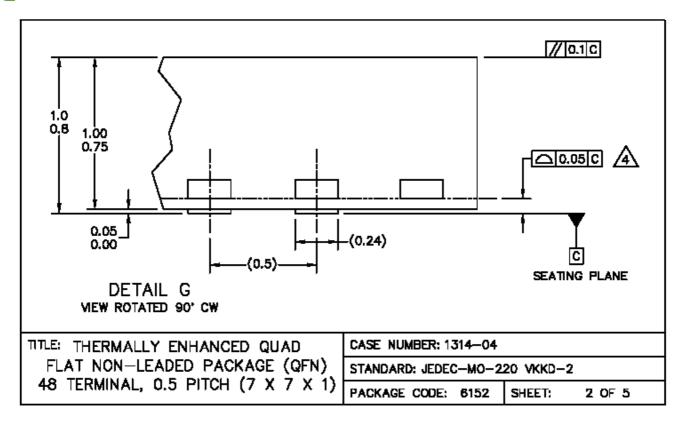

The MC44CD02 is available in a Lead-free 48 pin QFN package.

#### AAF

Baseband Anti Aliasing Filter.

#### ASC

Application Specific Controller, an external processor in charge of computing complex functions in the DVB-H system.

#### MC44CD02

The code name of the DVB-H RF front-end chip.

#### DVB-H

Digital Video Broadcast system, optimized for handheld applications. This category is described in the EICTA-TAC-MBRAI RF Specifications.

#### Deep-Sleep Mode

An operating mode characterized by the ENABLE pin held low leading to a power consumption reduced to a minimum.

#### EICTA-TAC

European Information, Communications and Consumer Electronics Industry Technology Association Result of the merge of EICTA (European Information and Communications Technology Industry Association and EACEM (European Association of Consumer Electronics Manufacturers).

#### *12C*

Inter IC bus, a bidirectional, serial data transfer protocol.

#### **LPF**

Baseband filter sub-module. The filter in charge of providing the I and Q components to the baseband processor during receive.

#### LVDS

Low Voltage Differential Signaling. LVDS is targeted for general purpose high speed applications requiring very low noise. This technology is defined by the ANSI/TIA/EIA-644 industry standard.

#### **MBRAI**

Mobile and Portable DVB-T Radio Access Interface Specification.

#### **MIXER**

The I and Q mixer sub-module.

#### **MLP**

The Multi-Level pin sub-module is dedicated to the configuration of the chip with regards to the reference clock frequency and the clock output signal shaping.

#### Normal Mode

An operating mode characterized by the ENABLE pin set, the SCAN\_MODE pin cleared and the TSTM bit cleared in the MODE register (address \$00).

Orthogonal Frequency Division Multiplexing.

#### OSC

The 36MHz or 26MHz crystal oscillator sub-module.

#### PLL

Phase Locked Loop sub-module.

#### **PMA**

Post Mixer Amplifier sub-module.

#### Power Down Mode

An operating mode characterized by the ENABLE pin set, the SCAN\_MODE pin cleared, the TSTM bit cleared and the PDM bit set in the MODE register (address \$00).

#### **RCI**

The Radio Control Interface sub-module.

#### **REM**

Reference Management (bias support) sub -module. The block in charge of delivering current/voltage references to the rest of the chip

#### **RFLNA**

RF Low Noise Amplifier sub-module.

#### **WBD**

Wide Band Detector sub-module, providing an estimation of the total power present in the UHF band.

The MC44CD02 is a Wide Band Zero-IF Direct Conversion Receiver Front-End IC. It receives the RF signal from an associated external LNA that provides a typical gain of about 10dB. Furthermore, this external LNA and its matching network will exhibit a total noise figure NF of 3.5dB maximum. The MC44CD02 provides I and Q terms to the associated baseband demodulator. The device is controlled through an I2C bus and provides interface signals to the baseband processor (RF wide band detector, reference clock). In addition, the MC44CD02 receives control signals for specific functions or features such as the internal LNA and baseband AGC controls.

The device exhibits the following features:

- Low power operation (2.775V, 98mA current drain, i.e. 270mW in normal mode)

- Power down and deep sleep battery saving modes of operation

- Full UHF range operation (470 to 862MHz)

- Multi standard RF operation (6, 7 and 8MHz bandwidth channels)

- Low external components count

- I2C bus controlled

- Integrated low phase noise PLL with 4GHz VCO and quadrature generator for precise I and Q local oscillator generation

- 166.67kHz synthesizer step size

- Integrated RF low noise amplifier (LNA) with gain control and differential inputs

- Integrated balanced I and Q down mixers

- Integrated post mixer amplifiers (PMA)

- Integrated I and Q baseband 8th order inverse Chebyshev low pass filters and amplifiers with gain controlIntegrated I and Q baseband 4th order Butterworth anti-aliasing (AAF) filter, with 6MHz 3dB cut-off frequency. Integrated filter tracking loop to cover the 6, 7 and 8MHz channel bandwidths, the AAF filter, and all process variations

- Integrated wide band RF power detector with output signal to the baseband demodulator

- 36MHz or 26MHz crystal oscillator with clock outputs (either custom LVDS or single-ended) toward the baseband demodulator

- A general purpose digital output which can possibly be used to control the gain of an external low noise amplifier

- Lead free QFN48 7x7, 0.5mm pitch exposed pad package

# **Modes of Operation**

This circuit supports three modes of operation.

- Normal The device operates normally.

- Power Down The device is turned OFF except for the crystal oscillator and associated reference clock buffers which are kept active. The integrated superfilter providing the supply to the VCO is also kept ON for PLL start-up purposes.

- Deep Sleep The device is fully disabled and the power consumption is reduced to a minimum.

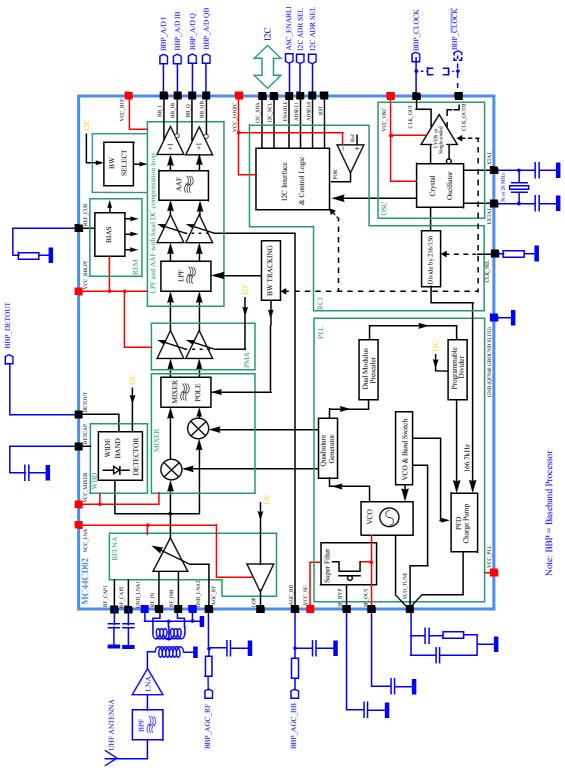

# 1.5 Block Diagram

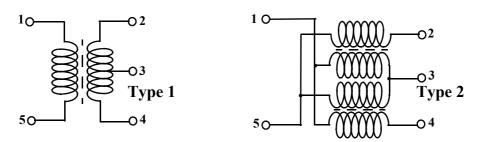

Following depicts the block diagram of the MC44CD02 chip and several external components. The receive path starts with an external LNA located very close to the UHF antenna which can also be equipped with a filter in charge for example to block the GSM interferers. Possibly the external LNA exhibits a switchable gain under control of the LOP pin. A UHF balun in charge of the single-ended to differential conversion as well as impedance transformation ( $50\Omega$  to  $200\Omega$ ) is connected to the two differential RF inputs (RF\_IN, RF\_INB).

The RF section of the MC44CD02 is comprised of an internal Low Noise Amplifier (LNA) with AGC, a set of quadrature mixers and an integrated 4GHz VCO controlled by a PLL.

The LNA with AGC is provided to cover the UHF bands IV and V (470-862 MHz). It drives the quadrature mixers that convert the RF signal to baseband quadrature I and Q. The output of the mixer connects directly to the post-mixer amplifier (PMA). Integrated capacitors are used to provide a primary low frequency filtering pole at the mixer output.

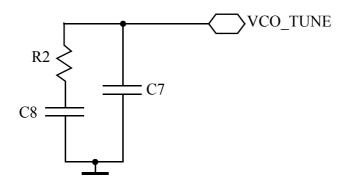

The local oscillator (LO) signal is provided by a fully integrated VCO running at four times the desired frequency that drives a divide-by-4 quadrature generator. A bank of three VCOs with sub-bands is actually used in conjunction with an automatic band switching system in order to cover the whole UHF IV and V bands with sufficient gain control. The frequency synthesis is made by means of an integer mode PLL with 1/6 MHz reference frequency. The VCO supply voltage is provided by an on-chip low noise voltage regulator ("super-filter").

The baseband section comprises two separate I and Q paths, each containing a post mixer amplifier PMA with a register controlled gain adjustment capability, a multiple channel programmable filter (8th order inverse Chebyshev) with AGC stages, an anti-aliasing filter (4th order Butterworth), and an output buffer. The baseband signal path has 9 filtering poles distributed between mixer pole (1 pole) and the channel filter poles (8 poles) for channel filtering, and 4 additional poles for anti-aliasing.

An integrated 36 or 26 MHz crystal oscillator provides the reference clock to the baseband demodulator.

The IC is controlled through an Inter IC (I2C) bus.

Figure 1-2 Simplified Block Diagram of the MC44CD02 Chip

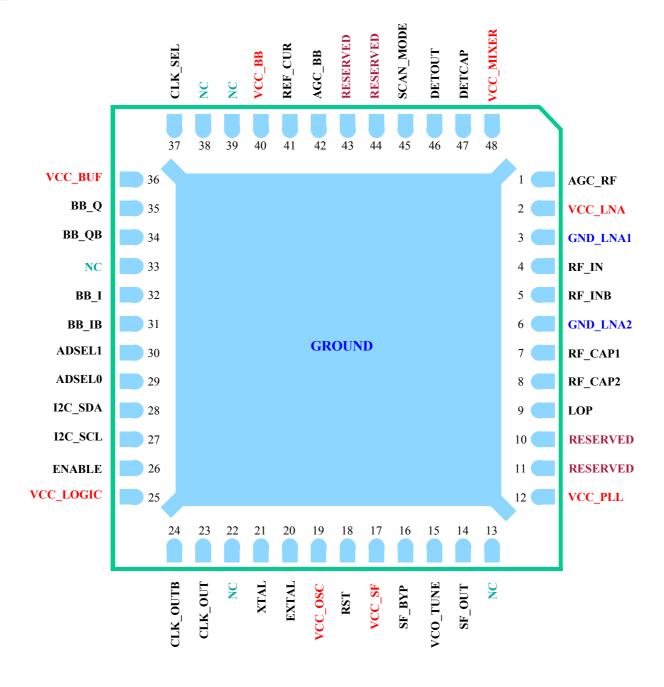

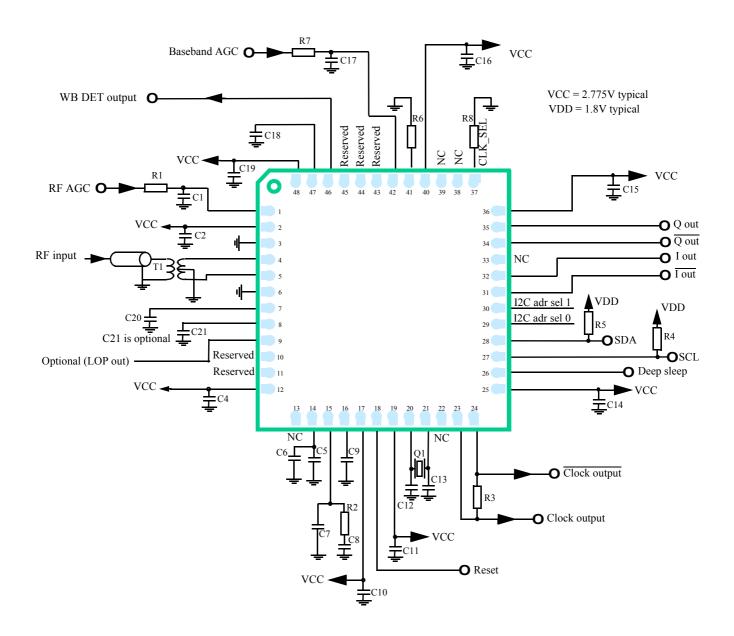

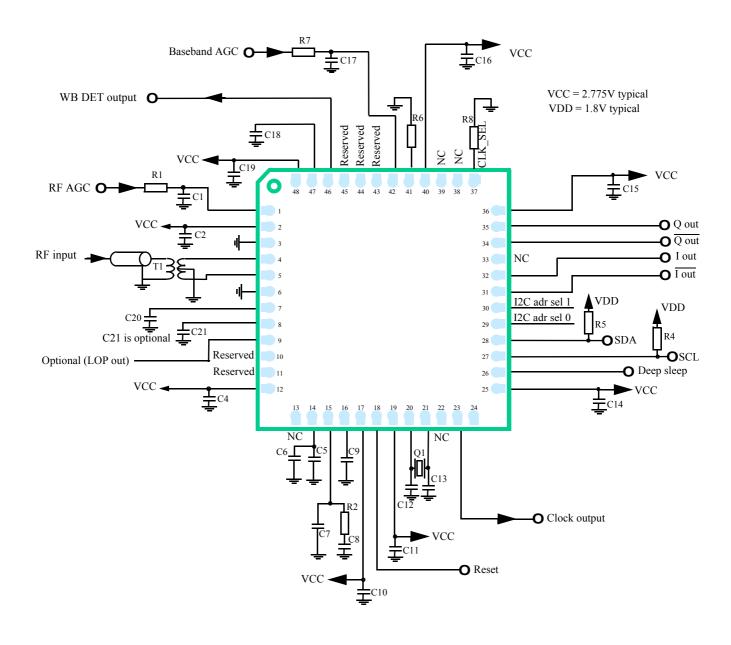

# 2.1 MC44CD02 Pin Assignment & Package

The MC44CD02 chip is mounted in a Quad Flat Pack No-Lead (QFN) 48 pin package with exposed die pad (QFN-EP version). This exposed flag ("slug") permits an improved ground connection. This housing exhibits a 7x7 mm<sup>2</sup> footprint and uses a 0.5mm pitch.

#### WARNING

Most of the internal ground pins as well as the substrate of the IC are connected to the exposed pad. The exposed pad must be grounded in the application.

The MC44CD02 pin assignment in the QFN48 package is shown in **Figure 2-1**.

Pins declared as «NC - Not connected» have no corresponding internal connection, and thus are submitted to no constraint at application level.

Pins declared as «RESERVED» are dedicated to test analysis and must be left floating at application level.

The reset pin 18 (RST), when not used, can be left uncommitted as it makes use of an internal pull-down resistor.

Figure 2-1 MC44CD02 QFN48 Package Bottom View Showing The Ground Slug

# MC44CD02 Pin List

Following Table 2-2 summarizes the description of every pin bonded in the QFN48 production package.

# Table 2-2 MC44CD02 QFN48 Pin List

| Pin Number | Pin Name  | Pin Description                       | Nature | Туре    |

|------------|-----------|---------------------------------------|--------|---------|

| 1          | AGC_RF    | RF LNA AGC control voltage            | 1      | Analog  |

| 2          | VCC_LNA   | LNA power supply                      | Р      | Supply  |

| 3          | GND_LNA1  | LNA ground (1)                        | Р      | Supply  |

| 4          | RF_IN     | RF input                              | 1      | Analog  |

| 5          | RF_INB    | RF input                              | 1      | Analog  |

| 6          | GND_LNA2  | LNA ground (2)                        | Р      | Supply  |

| 7          | RF_CAP1   | RFAGC decoupling capacitor pin        | С      | Analog  |

| 8          | RF_CAP2   | RFAGC decoupling capacitor pin        | С      | Analog  |

| 9          | LOP       | Logical Output Port                   | 0      | Digital |

| 10         | RESERVED  | Reserved                              | R      | Test    |

| 11         | RESERVED  | Reserved                              | R      | Test    |

| 12         | VCC_PLL   | PLL part supply                       | Р      | Supply  |

| 13         | NC        | Not connected                         | NC     | Open    |

| 14         | SF_OUT    | Super Filter output voltage           | С      | Analog  |

| 15         | VCO_TUNE  | VCO tuning voltage                    | I/O    | Analog  |

| 16         | SF_BYP    | Super Filter bypass capacitor         | С      | Analog  |

| 17         | VCC_SF    | Super Filter supply                   | Р      | Supply  |

| 18         | RST       | Reset                                 | I      | Digital |

| 19         | vcc_osc   | Crystal oscillator supply             | Р      | Supply  |

| 20         | EXTAL     | Crystal oscillator input              | 1      | Analog  |

| 21         | XTAL      | Crystal oscillator output             | 0      | Analog  |

| 22         | NC        | Not connected                         | NC     | Open    |

| 23         | CLK_OUT   | Reference clock buffered output       | 0      | Digital |

| 24         | CLK_OUTB  | Reference clock buffered output       | 0      | Digital |

| 25         | VCC_LOGIC | Control logic supply                  | Р      | Supply  |

| 26         | ENABLE    | Enable control pin for deep slep mode | 1      | Digital |

| 27         | I2C_SCL   | I2C clock                             | 1      | Digital |

| 28         | I2C_SDA   | I2C data                              | I/O    | Digital |

| 29         | ADSEL0    | I2C physical address selection bit 0  | 1      | Digital |

## Table 2-2 MC44CD02 QFN48 Pin List

| Pin Number      | Pin Name  | Pin Description                                                       | Nature | Туре     |

|-----------------|-----------|-----------------------------------------------------------------------|--------|----------|

| 30              | ADSEL1    | I2C physical address selection bit 1                                  | I      | Digiital |

| 31              | BB_IB     | l baseband output signal                                              | 0      | Analog   |

| 32              | BB_I      | I baseband output signal                                              | 0      | Analog   |

| 33              | NC        | Not connected                                                         | NC     | Open     |

| 34              | BB_QB     | Q baseband output signal                                              | 0      | Analog   |

| 35              | BB_Q      | Q baseband output signal                                              | 0      | Analog   |

| 36              | VCC_BUF   | Baseband buffers supply                                               | Р      | Supply   |

| 37              | CLK_SEL   | Multi-level pin for<br>Reference clock and Clock output Configuration | 1      | Analog   |

| 38              | NC        | Not connected                                                         | NC     | Open     |

| 39              | NC        | Not Connected                                                         | NC     | Open     |

| 40              | VCC_BB    | Baseband filter supply                                                | Р      | Supply   |

| 41              | REF_CUR   | Reference current                                                     | С      | Analog   |

| 42              | AGC_BB    | Baseband AGC control voltage                                          | I      | Analog   |

| 43              | RESERVED  | Reserved                                                              | R      | Test     |

| 44              | RESERVED  | Reserved                                                              | R      | Test     |

| 45              | SCAN_MODE | Scan chain mode entry                                                 | I      | Digital  |

| 46              | DETOUT    | Wideband detector output                                              | 0      | Analog   |

| 47              | DETCAP    | Wideband detector integration capacitor                               | С      | Analog   |

| 48              | VCC_MIXER | Mixer supply                                                          | Р      | Supply   |

| EXPOSED<br>FLAG | GND       | General Ground                                                        | Р      | Supply   |

# **Table 2-3 Pin Nature Description**

| Nature | Description                                                       |

|--------|-------------------------------------------------------------------|

| I      | Input                                                             |

| 0      | Output                                                            |

| I/O    | Input/Output                                                      |

| Р      | Power (VCC or GND)                                                |

| R      | Reserved                                                          |

| NC     | Internally not connected                                          |

| С      | Passive Components (loop filters, filtering or storage capacitor) |

# tion 3 I2C Communication And Registers

#### 3.1 Overview

This section describes MC44CD02's memory map and registers accessible through the I2C interface. The full control of the chip is accomplished via the 2-wires I2C-bus used as either slave-receiver or slave-transmitter. The MC44CD02 chip is fully compliant with the I2C-bus specification standard version 2.1. Up to 400kbit/s bus speed can be used in accordance with the I2C Fast-Mode specifications. The I2C interface stage is electrically 1.8V and 2.7V compliant.

The I2C interface of MC44CD02 cannot be used in deep-sleep mode. The address made of seven bits out of which the five most significant bits are set to 11000 as per the I2C requirements. Through a monitoring of the state of the pins ADSEL0 and ADSEL1, it is possible to modify the actual device I2C address out of four possible choices to accommodate systems where more than one MC44CD02 chip sits in the same bus (for antenna diversity reasons in mobile applications for example). The device address as a function of the ADSEL0 and ADSEL1 pins in case of both read and write operations is indicated in **Table 3-1**.

Table 3-1 MC44CD02's I2C Device Address vs. ADSEL1 & ADSEL0 Pins State

| <b>A6</b> | A5 | <b>A</b> 4 | <b>A</b> 3 | A2 | A1 = ADSEL1 | A0 = ADSEL0 | R/W | I2C Device<br>Address |

|-----------|----|------------|------------|----|-------------|-------------|-----|-----------------------|

| 1         | 1  | 0          | 0          | 0  | 0           | 0           | 0   | \$C0                  |

| 1         | 1  | 0          | 0          | 0  | 0           | 0           | 1   | \$C1                  |

| 1         | 1  | 0          | 0          | 0  | 0           | 1           | 0   | \$C2                  |

| 1         | 1  | 0          | 0          | 0  | 0           | 1           | 1   | \$C3                  |

| 1         | 1  | 0          | 0          | 0  | 1           | 0           | 0   | \$C4                  |

| 1         | 1  | 0          | 0          | 0  | 1           | 0           | 1   | \$C5                  |

| 1         | 1  | 0          | 0          | 0  | 1           | 1           | 0   | \$C6                  |

| 1         | 1  | 0          | 0          | 0  | 1           | 1           | 1   | \$C7                  |

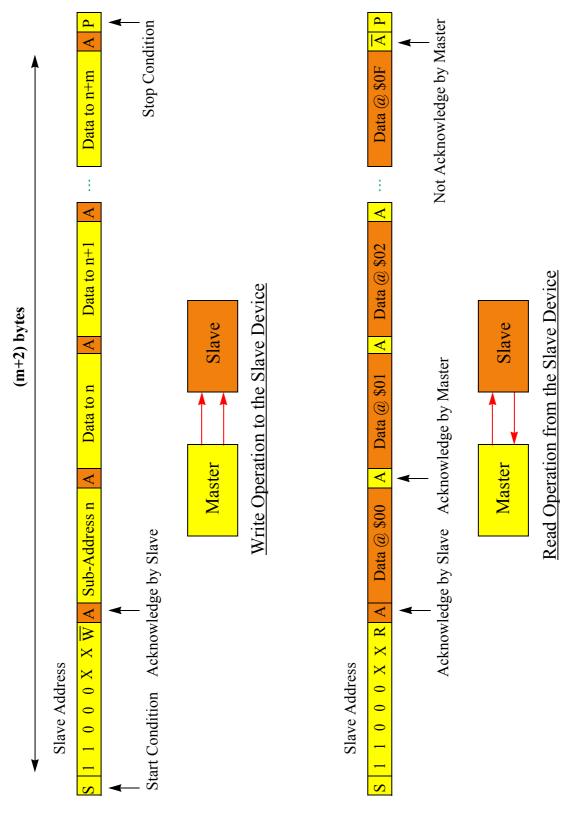

The MC44CD02 device supports the sub-addressing in order to speed up the write access of the register map. The read operation conforms to classical I2C practices. **Figure 3-2** depicts the write and read messages.

Figure 3-2 I2C Write & Read Operations

MC44CD02 contains a set of 16 registers in the \$00 to \$0F address space. The user registers constitute the bottom of the registers addressable space while test registers are placed at the higher sub-addresses. A summary of these registers is given in **Table 3-3** while their accessibility in normal mode is detailed in section **3.3**.

Table 3-3 MC44CD02 Register Map

| Register Name | Register<br>Address | Description                                       | Reset Value |

|---------------|---------------------|---------------------------------------------------|-------------|

| MODE          | \$00                | Mode Register                                     | \$00        |

| PLLR1         | \$01                | PLL Control Register #1                           | \$0F        |

| PLLR2         | \$02                | PLL Control Register #2                           | \$9C        |

| WBDCR1        | \$03                | Wide Band Detector Control Register #1            | \$00        |

| WBDCR2        | \$04                | Wide Band Detector Control Register #2            | \$00        |

| LNAOSCR       | \$05                | Low Noise Amplifier & Oscillator Control Register | \$20        |

| MISCR         | \$06                | Miscellaneous Control Register                    | \$00        |

| MDTST1        | \$07                | Reserved                                          | \$00        |

| MDTST2        | \$08                | Reserved                                          | \$00        |

| LPFTST        | \$09                | Reserved                                          | \$00        |

| PLLTST1       | \$0A                | Reserved                                          | \$00        |

| PLLTST2       | \$0B                | Reserved                                          | \$0D        |

| RFTST         | \$0C                | Reserved                                          | \$00        |

| TLTST         | \$0D                | Reserved                                          | \$00        |

| VTBSTA        | \$0E                | Reserved                                          | \$00        |

| TLSTA         | \$0F                | Reserved                                          | \$00        |

# **Register Descriptions**

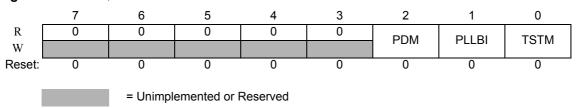

#### 3.3.1 MODE — Mode Register

The MODE register dictates MC44CD02's operating mode.

#### Register address \$00

Figure 3-4 MC44CD02 Mode Register (MODE)

Bits 2-0 of the MODE register are readable and writable anytime. Bits 7-3 cannot be written and always read "0".

#### PDM — Power Down Mode.

If the ENABLE pin is held high, this bit permits to place the MC44CD02 chip in power down mode with only the oscillator core and associated output clock drivers activated. This feature is used in case of time slice operation where the receiving of the DVB-H signals is pulsed with a low duty cycle to save power consumption. The ENABLE pin has precedence over the PDM control bit, which means that whenever the ENABLE pin is held low, the PDM bit state is cleared and the part placed in deep sleep mode.

- 1 = MC44CD02 chip is in power down mode if the ENABLE pin is asserted.

- 0 = MC44CD02 chip is in normal mode if the ENABLE pin is asserted.

## PLLBI — PLL Band Change Inhibit.

This bit permits to freeze the PLL VCO and associated sub-band in its current operating configuration. This feature is useful to rapidly regain lock after the circuit has been placed in a power saving mode.

- 1 = Band lock activated.

- 0 = Band lock de-activated (automatic VCO and sub-band searching is possible).

#### TSTM — Analog Test Mode.

The setting of the TSTM bit places the chip in test mode.

- 1 = Test mode is activated.

- 0 = Test mode is not activated.

Asserting the TSTM bit by itself does not produce any modification to MC44CD02's operation, it simply enables test functions to be activated and test outputs to be possibly observed. The reset values of the test bits are read at 0 in normal mode.

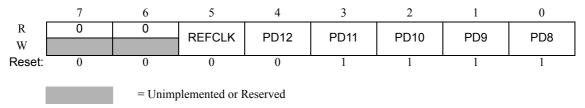

# PLLR1 — PLL Control Register #1

The PLLR1 register contains the ref clock bit along with the five most significant bits of the programmable divider

#### Register address \$01

Figure 3-5 PLL Control Register #1 (PLLR1)

In all mode, bits 5-0 of the PLLR1 register are readable and writable anytime. Bits 7-6 cannot be written and always read "0".

REFCLK— Sets the chip in line with the chosen reference clock frequency (either 36MHz or 26MHz reference clock).

Only active when the I2C bit PADCTRL (reg \$05) is set to 1 (otherwise, as PADCTRL=0, the reference clock frequency is controlled by the multi-level pin#37 CLK SEL).

1 = 26MHz

0 = 36MHz

PD12-8 — Programmable Divider MSBs.

These five bits are complemented by the 8 bits of the PLLR2 register to form the 13 bits used to define the programmable divider ratio, part of the PLL feedback divider. A sequential logic exists to transfer the register bits PD[12:0] into the programmable divider when this last has finish to count-down.

#### WARNING

Any change in the programmable divider ratio must be performed using two write operations in any order in any of the PLLR1 (5 MSBs) and PLLR2 (8 LSBs) registers. There is no need for the two write operations to take place within two consecutive cycles.

#### WARNING

It is forbidden to write PD<12:0>=\$0000 in the PLLR1 and PLLR2 registers as this value jeopardizes the programmable divider functioning.

If we call PD the decimal content of the 13 bits constituting the programmable divider ratio, the synthesized LO frequency is given by the following equation:

$$F_{LO}[MHz] = PD/6$$

ample, the reset values of the PLLR1 and PLLR2 registers lead to a synthesized LO frequency of 666MHz (PD=3996), which corresponds to the UHF channel 45 for countries using 8MHz channel bandwidth and zero offset<sup>1</sup>.

It is interesting to note that the VCO inside the PLL module runs at a frequency equals to 4\* FLO.

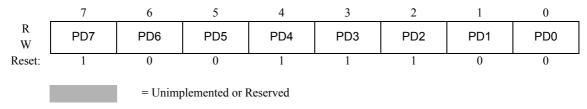

# 3.3.3 PLLR2 — PLL Control Register #2

The PLLR2 register contains the 8 LSBs of the programmable divider ratio.

#### Register address \$02

Figure 3-6 PLL Control Register #2 (PLLR2)

All bits in the PLLR2 register are readable and writable anytime. See description and warnings in the previous section.

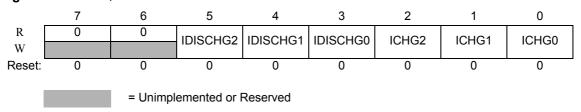

# 3.3.4 WBDCR1— Wide Band Detector Control Register #1

The WBDCR1 register contains bits to control the Wide Band Detector operation.

#### Register address \$03

Figure 3-7 Wide Band Detector Control Register #1 (WBDCR1)

In all modes, bit 5-0 in register WBDCR1 are readable and writable anytime. Bits 7-6 cannot be written and always read "0".

#### NOTES

1. The DVB-T signal may be shifted upward or downward from the ideal channel center frequency by an offset frequency of +/- 1/6 MHz.

'HG2-0 — Current Discharge selector.

These 3 bits set the amount of discharging current of the wide band detector as indicated in **Table 3-8**. They drive the decay rate of the WBD output for a given capacitor.

Table 3-8 Typical discharging current vs. IDISCHG[2:0]

| IDISCHG[2:0] | Value (uA)      |

|--------------|-----------------|

| 000          | 26.6            |

| 001          | 10.6            |

| 010          | 15.9            |

| 011          | 21.3            |

| 100          | 31.9            |

| 101          | 37.9            |

| 110          | 42.5            |

| 111          | output disabled |

ICHG2-0 — Current Charge selector.

These 3 bits control the level of charging current for the external capacitor as indicated in **Table 3-9**. This current controls the rise time of the WBD output.

Table 3-9 Typical charging current vs. ICHG[2:0]

| ICHG[2:0] | Value (uA) |

|-----------|------------|

| 000       | 836        |

| 001       | 790        |

| 010       | 744        |

| 011       | 698        |

| 100       | 880        |

| 101       | 924        |

| 110       | 967        |

| 111       | 1011       |

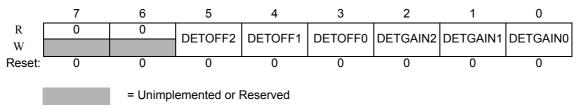

# WBDCR2 — Wide Band Detector Control Register #2

The WBDCR2 drives the detector transfer function offset and gain.

#### Register address \$04

Figure 3-10 Wide Band Detector Control Register #2 (WBDCR2)

In all modes, bit 5-0 in register WBDCR2 are readable and writable anytime. Bits 7-6 cannot be written and always read "0".

DETOFF2-0 — Detector Offset Adjustment.

Adjusts the output current of the detector transfer function as shown **Table 3-11**.

Table 3-11 Typical current sourced vs. DETOFF[2:0]

| DETOFF[2:0] | DC level (uA) |  |

|-------------|---------------|--|

| 000         | -10.9         |  |

| 001         | -7.3          |  |

| 010         | -3.6          |  |

| 011         | 0             |  |

| 100         | 3.9           |  |

| 101         | 7.7           |  |

| 110         | 11.6          |  |

| 111         | 15.4          |  |

DETGAIN2-0 — Detector Gain Adjustment.

Adjusts the detector transfer function gain as indicated **Table 3-12**.

Table 3-12 Typical detector gain vs. DETGAIN[2:0]

| DETGAIN[2:0] | Gain |

|--------------|------|

| 000          | 2.21 |

| 001          | 2.27 |

| 010          | 2.33 |

| 011          | 2.4  |

| 100          | 2.47 |

Table 3-12 Typical detector gain vs. DETGAIN[2:0]

| DETGAIN[2:0] | Gain |

|--------------|------|

| 101          | 2.55 |

| 110          | 2.64 |

| 111          | 2.74 |

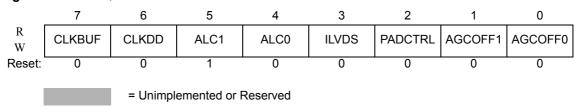

# 3.3.6 LNAOSCR — Low Noise Amplifier & Oscillator Control Register

The LNAOSCR register contains bits to adapt the RFAGC loop and to control the oscillator buffer.

#### Register address \$05

Figure 3-13 Low Noise Amplifier & Oscillator Control Register (LNAOSCR)

In all modes, bits 7-0 in register LNAOSCR are readable and writable anytime.

#### CLKBUF — Reference Clock Buffer Selector.

This bit selects either the single-ended or LVDS buffer. Only active when the I2C bit PADCTRL (reg \$05) is set to 1 (otherwise, as PADCTRL=0, the reference clock buffer selection is controlled by the multi-level pin#37 CLK\_SEL).

- 1 = The single-ended buffer is selected.

- 0 = The LVDS buffer is selected.

#### CLKDD — Reference Clock Output Driver Disable

In case the reference clock generated by the MC44CD02 chip is not used, the CLKDD bit can be set HIGH to switch OFF the corresponding output driver (pins CLK\_OUT, CLKOUTB), hence saving power consumption and minimizing radiated emissions.

- 1 = Reference clock output driver is disabled.

- 0 = Reference clock output driver is enable.

-0 — Amplitude Oscillator Control.

Determines according to **Table 3-14** the peak to peak sinewave clock amplitude at the XTAL pin.

Table 3-14 Crystal Oscillator Sine Wave Amplitude vs. ALC[1:0]

| ALC[1:0] | Sine Wave Amplitude (Vpp) |

|----------|---------------------------|

| 00       | -                         |

| 01       | -                         |

| 10       | 1                         |

| 11       | -                         |

ILVDS — Selects the LVDS buffer output current OR the Single-Ended buffer Clock Shape.

This bit can either selects the output current of the CLK\_OUT customized LVDS buffer if this buffer is selected or selects the single-ended buffer clock shape.

- 1 = The output current is set to 1mA if the LVDS buffer is selected (CLKBUF=0) or set the CMOS 1.8V square wave if the single-ended buffer is selected (CLKBUF=1).

- 0 = The output current is set to 500uA if the LVDS buffer is selected (CLKBUF=0) or set the sine like wave if the single-ended buffer is selected (CLKBUF=1).

PADCTRL — Gives priority either to the multi-level pin#37 CLK\_SEL or to the I2C to configure the MC44CD02 chip and its clock outputs with regards to the reference clock frequency and the application requirements.

- 1 = The I2C bits REFCLK (reg \$01) and CLKBUF (\$05) have priority.

- 0 = The multi-level pin#37 CLK\_SEL has priority.

#### WARNING

When using the PADCTRL bit, two I2C messages are needed to program the device properly because of the registers order.

First I2C message: Write PADCTRL=1.

Whatever value is written during the same message in REFCLK bit will be ignored.

Second I2C message: Rewrite PADCTRL=1. REFCLK value will be take into account.

)FF1-0 — AGC Loop Offset Selector.

These 2 bits control the offset of the AGC loop as indicated **Table 3-15**. Only the default value configuation (no offset) has to be used.

Table 3-15 AGC Loop Offset vs. AGCOFF[1:0]

| AGCOFF[1:0] | RFAGC Knee voltage shift relative to nominal (mV) |  |

|-------------|---------------------------------------------------|--|

| 00          | 0                                                 |  |

| 01          | NOT TO BE USED                                    |  |

| 10          | NOT TO BE USED                                    |  |

| 11          | NOT TO BE USED                                    |  |

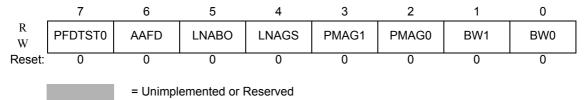

# 3.3.7 MISCR— Miscellaneous Control Register

The MISCR register contains bits controlling the post-mixer amplifier (PMA), the anti-aliasing lowpass filter and the Logical Output Port (LOP) state, and some PLL test feature.

#### Register address \$06

Figure 3-16 Miscellaneous Control Register (MISCR)

In all modes, bits 7-0 in register MISCR are readable and writable anytime.

PFDTST0 — PLL Test Feature.

Reverse the polarity of the reference clock signal driving the phase-frequency detector of the PLL.

AAFD — Anti-Aliasing Filter Disable.

The anti-aliasing filter is a sub-block of the whole baseband Low-pass Filter module.

- 1 = Anti-aliasing filter is disabled. Only the baseband channel low pass filter is activated, driving the baseband buffer towards the I/Q outputs.

- 0 = Anti-aliasing filter is enabled. The whole baseband filtering chain (channel low pass filter plus anti-aliasing filter), driving the baseband buffer towards the I/Q outputs.

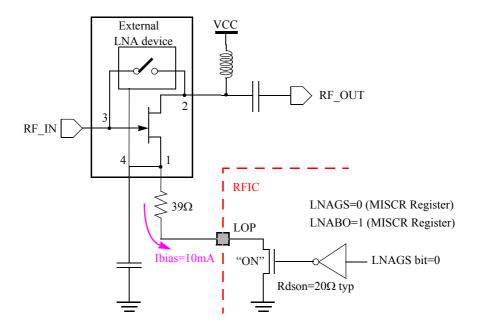

LNABO — Topology of the Logical Output Port.

- 1 = The LOP buffer exhibits an open-drain, pull-down output.

- 0 = The LOP buffer exhibits a CMOS output.

LNAGS — State of the Logical Output Port.

1 = Pad LOP receives a logical "1".

0 = Pad LOP receives a logical "0".

PMAG1-0 — Post Mixer Amplifier Gain Setting.

The Post-Mixer Amplifier gain as a function of the state of the PMAG bits is indicated in **Table 3-17**.

Table 3-17 PMA gain vs. PMAG[1:0]

| PMAG[1:0] | Gain (dB) |

|-----------|-----------|

| 00        | 14        |

| 01        | 10        |

| 10        | 12        |

| 11        | 14        |

0 —Low-Pass Filter Bandwidth Selector.

Set the low-pass filter nominal bandwidth to 6MHz, 7MHz or 8MHz according to **Table 3-18**.

Table 3-18 Filter nominal bandwidth BW[1:0]

| BW[1:0] | Nominal Bandwidth |  |

|---------|-------------------|--|

| 00      | - 8MHz            |  |

| 01      |                   |  |

| 10      | 7MHz              |  |

| 11      | 6MHz              |  |

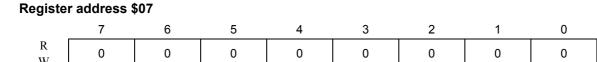

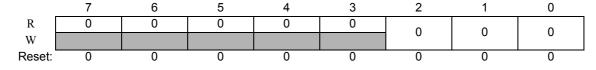

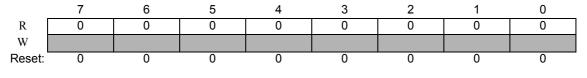

# 3.3.8 MDTST1 — Module Disable Test Register #1

MDTST1 is a register reserved for test purposes.

n

0

n

0

0

= Unimplemented or Reserved

n

0

Figure 3-19 Module Disable Test Register #1 (MDTST1)

In normal mode, the MDTST1 register read \$00 and cannot be written.

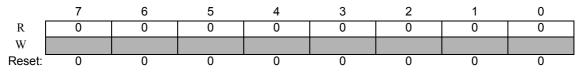

# 3.3.9 MDTST2 — Module Disable Test Register #2

MDTST2 is a register reserved for test purposes.

#### Register address \$08

Reset:

= Unimplemented or Reserved

Figure 3-20 Module Disable Test Register #2 (MDTST)bfddf

In normal mode, the MDTST2 register read \$00 and cannot be written.

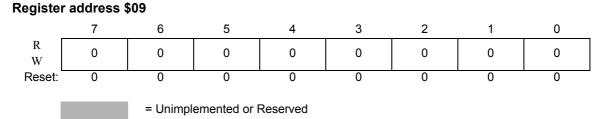

# 0 LPFTST — Baseband Low Pass Filter Test Register

LPFTST is a register reserved for test purposes

Figure 3-21 Baseband Low Pass Filter Test Register (LPFTST)

In normal mode, the LPFTST register reads \$00 and cannot be written.

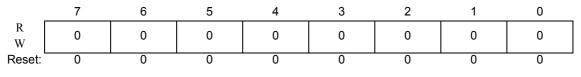

# 3.3.11 PLLTST1 — PLL Test Register #1

PLLTST1 is a register reserved for test purposes

# Register address \$0A 7 6 5 4 3 2 1 0 R W Reset: 0 0 0 0 0 0 0 0 0 = Unimplemented or Reserved

Figure 3-22 PLL Test Register #1 (PLLTST1)

In normal mode, register PLLTST1 reads \$00 and cannot be written.

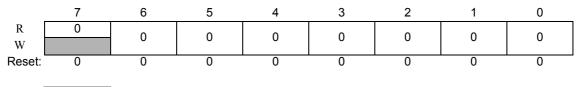

# 3.3.12 PLLTST2 — PLL Test Register #2

PLLTST2 is a register reserved for test purposes.

#### Register address \$0B 4 0 5 0 0 0 0 0 0 0 0 0 0 0 Reset: = Unimplemented or Reserved

Figure 3-23 PLL Test Register #2 (PLLTST2)

In normal mode, register PLLTST2 reads \$00 and cannot be written.

# 3 RFTST — RF Blocks Test Register

RFTST is a register reserved for test purposes.

#### Register address \$0C

= Unimplemented or Reserved

Figure 3-24 RF Blocks Test register (RFTST)

In normal mode, the RFTST register reads \$00 and cannot be written.

# 3.3.14 TLTST — Tracking Loop Test Register

TLTST is a register reserved for test purposes.

#### Register address \$0D

= Unimplemented or Reserved

Figure 3-25 Tracking Loop Test Register (TLTST)

In normal mode, the TLTST register read \$00 and cannot be written.

# 3.3.15 VTBSTA — VCO Tuning Band Status Register

VTBSTA is a register reserved for test purposes.

#### Register address \$0E

= Unimplemented or Reserved

Figure 3-26 VCO Tuning Band Status Register (VTBSTA)

In normal mode, the VTBSTA register reads \$00 and cannot be written.

# 6 TLSTA — Tracking Loop Status Register

TLSTA is a register reserved for test purposes.

#### Register address \$0F

= Unimplemented or Reserved

Figure 3-27 Tracking Loop Status Register (TLSTA)

In normal mode, the TLSTA register reads \$00 and cannot be written.

The following sub-sections address some general key points about the MC44CD02device operation, then detail the functional descriptions of each sub-block in their respective operating modes.

# 4.1 Modes Of Operation

The MC44CD02 device includes three different power modes controlled by a combination of hardware (ENABLE pin) and software (state of the PDM bit in the MODE register at I2C address \$00). The modes are summarized in **Table 4-1**. Furthermore, the PDM bit is automatically reset to 0 while entering in Deep Sleep mode. It is therefore impossible to switch from Deep Sleep to Power Down mode without going though the Normal mode. Finally, MC44CD02 device lasts 20ms to be stable when waking-up from Power Down mode to Normal mode, and 200ms when waking-up from Deep Sleep mode to Normal mode.

Table 4-1 Power Operating Mode vs. ENABLE & PDM States

| ENABLE Pin | PDM Bit        | Mode       |

|------------|----------------|------------|

| 0          | X <sup>1</sup> | Deep Sleep |

| 1          | 0              | Normal     |

| 1          | 1              | Power Down |

NOTES:

1. Don't Care.

# 4.1.1 Normal Operation Mode

This is the normal operating mode of the receiver where all the internal stages are activated. In this mode, the current consumption under typical conditions (VCC=2.775V and Temp.=27°C) is defined in the General MC44CD02 Electrical Specification, appendix A.3, ID 1.1.

#### 4.1.2 Power Down Mode

In this mode the MC44CD02 circuit will have very low current drain. The 36 or 26 MHz reference oscillator core and its buffers are activated to provide the clock signal to the baseband demodulator. The logic section remains powered such that the received channel settings remain stored in their corresponding I2C registers. Furthermore, the superfilter (that provides the supply voltage to the VCOs) is also activated, for VCO/PLL settling time purposes. However, all the others blocks are disabled.

In this mode, the current consumption under typical conditions (VCC=2.775V and Temp.=27°C) is defined in the General MC44CD02 Electrical Specification, appendix A.3, ID 1.2.

# Deep Sleep Mode

This mode is intended to have the lowest current drain. All stages are fully disabled except the power-on reset function which continuously monitors the voltage on the VCC\_LOGIC pin such as to produce a reset and then place the chip in a known configuration in case of power failure or brown-out. Furthermore, the logic section remains powered such that the received channel settings remain stored in their corresponding I2C registers.

The circuit enters into deep-sleep mode through the control of an external pin that has priority on the power down/normal mode selection as shown in **Table 4-1**.

In deep-sleep mode, the reset (external pin RST), and address select (external pins ADSEL0 and ADSEL1) functionalities are disabled. Those functionalities are available as the circuit is on Normal or Power down mode only.

In this mode, the current consumption under typical conditions (VCC=2.775V and Temp.=27°C) is defined in the General MC44CD02Electrical Specification, appendix A.3, ID 1.3.

The overall characteristic is composed by the analog filtering in the MC44CD02 (both channel filtering with programmable bandwidth, and anti-aliasing filtering), and a digital filtering in the baseband demodulator. Therefore the task of the MC44CD02 analog filter is to provide enough attenuation to the adjacent channel power in order not to saturate filtering stages in front of the baseband demodulator input and especially the Sigma-Delta AD converter, and to provide sufficient stop-band attenuation to cope with the baseband IC ADC sampling requirements. The final channel filtering is performed inside the baseband demodulator.

The system has to cope with different adjacent channel scenarii (adjacent upper channel vision carrier, adjacent lower channel sound carriers...). The adjacent channel can be an analog interferer (pattern S1) or a digital DVB-T adjacent channel interferer (pattern S2). These patterns are described in the reference [1] document. Those patterns define the channel filtering performance the MC44CD02 chip must perform.

Furthermore, the stopband attenuation specification was defined such that interferers beyond the Nyquist frequency, which will be folded into the wanted band during the A-to-D conversion and act like a noise contribution, do not hurt the required S/N ratio.

The MC44CD02 channel filtering section consists of a 8<sup>th</sup> order baseband channel low pass filter LPFs (inverse Chebyshev structure) with variable gain amplifiers.

A first stage of additional filtering lies in the mixer output pole (15 MHz).

The MC44CD02 supports three different channel bandwidths: 6, 7, and 8 MHz.

The inverse Chebyshev characteristic is chosen such has to have a limited amplitude ripple in the passband.

The channel filter is followed by the baseband anti-aliasing low pass filter AAFs (4th order Butterworth structure) to provide the required stop band attenuation.

The I/Q output signals are provided by output buffers for driving purposes. The I/Q signals must fulfill the following requirements:

- Differential signal amplitude: 1.4Vpp maximum;

- Baseband differential input resistance: 10kΩ minimum;

- Baseband input capacitance: 5pF maximum.Control Loops

# 4.3 Control Loops

# 4.3.1 AGC Loops

The non-interrupted mode of the OFDM modulation for DVB-H forces a quasi continuous control of the AGC correction loop.

The AGC system is split between RF AGC (in the LNA) and baseband AGC. Both those AGCs are controlled through two dedicated pins by analog signals provided by Sigma-Delta ( $\Sigma\Delta$ ) DACs at the baseband demodulator IC output.

output of the internal LNA, a broadband RF detector (WBD module) takes part to this AGC system by sensing strong signals into the whole UHF band, and sending the information to the baseband demodulator IC through a dedicated pin (DETOUT).

The AGC correction algorithms are left to the baseband demodulator IC.

The Post Mixer Amplifier (PMA) also exhibits gain control capabilities (through I2C programming), but this capability is not part of AGC system.

#### 4.3.1.1 RF AGC Control Loop

The AGC is directly controlled by an RC filtered pulse width modulated signal (filtered 1-bit $\Sigma\Delta$  output) provided by the baseband demodulator with the following properties:

- Voltage range: from 0.1V to 1.8V;

- Impedance: RC filter with 10 k $\Omega$  in series and 22 nF to ground.

#### 4.3.1.2 Baseband AGC control loop

AGC stages are inserted in the filtering chain in order to cover the overall dynamic range specifications. An AGC range of 35 dB minimum is required. Due to the large gain required in the baseband section, local DC offset correction loops for I and for Q are necessary to avoid saturation in cascaded stages. For this purpose each channel has its specific DC cancellation loop with an external storage capacitor.

The AGC is directly controlled by a RC filtered pulse width modulated signal (filtered 1-bit  $\Sigma\Delta$  output) provided by the baseband demodulator with the following properties:

- Voltage range: from 0.1V to 1.8V;

- Impedance: RC filter with  $10 \text{ k}\Omega$  in series and 22 nF to ground.

#### 4.3.2 DC Offset Correction

Despite the AC coupling on I/Q signals between the MC44CD02 device and the baseband processor, and due to the high gain level required at baseband stages, the baseband section includes local DC offset correction loops to avoid signal distortion. No interaction with the baseband demodulator IC is required.

# 4.3.3 Filter Tracking

The MC44CD02 chip supports multiple OFDM modulation bandwidths (6, 7, 8 MHz) via I2C programming. The filter calibration is ensured by an autonomous tracking bandwidth system derived from the crystal oscillator reference, with a maximum frequency drift of 6%.

# 4.3.4 Common Mode Voltages

## 4.3.4.1 I/Q Buffers Outputs

The MC44CD02 chip and the baseband-demodulator IC are AC coupled (1kHz). No common mode voltage control loop is thus necessary.

The MC44CD02 chip either delivers a custom LVDS clock reference or a single-ended clock reference to the baseband processor. The reference clock buffer mode is selected by I2C programming.

The LVDS delivery of the clock reference implies the flowing of differential currents carrying the frequency information. A resistor is used at the baseband inputs level to generate a differential, small amplitude clock voltage. The common mode voltage of the CLK\_OUT and CLK\_OUTB pins is derived from a very accurate bandgap reference voltage, and therefore requires no common mode feedback system to ensure proper interfacing between the two chips.

The single-ended buffer of the clock reference provides either a 1.8V CMOS signal or a sine-like 1.5Vpp signal with 0.9V common mode voltage on pin CLK\_OUT, while pin CLK\_OUTB remains open.

#### 4.3.5 I/Q Mismatch

The whole I/Q static mismatch compensation is performed in the baseband demodulator IC, not in the RF front-end chip.

# 4.4 Reference Clock Configuration

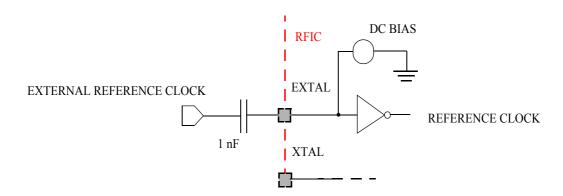

The MC44CD02 chip is able to handle two different reference clock frequencies, 26MHz and 36MHz. This reference frequency is either generated by means of crystal oscillator (using an external 26MHz or 36MHz crystal element connected between pin #20 EXTAL and pin #21 XTAL), or externally provided to the chip on its pin #20 EXTAL.

The MC44CD02 chip is also capable to provide two different clock output signal shapings (either LVDS or single-ended) to the baseband demodulator IC through the clock output pins #23 CLK\_OUT and #24 CLK\_OUTB.

At power on reset, a proper setting of the IC with regards to the reference clock frequency is suitable to fit the application requirements. Particularly, a correct power on reset configuration of the clock output signal is required, as this signal is potentially used to wake-up and clock the baseband demodulator IC.

Therefore, a multi-level pin (pin #37 CLK\_SEL) is dedicated to adequately preset the MC44CD02 chip and its clock output signal in the configuration required by the application. See the AAF (multi-level pin) module description chapter for more details.

# **WBD** Functional Description

#### 4.5.1 General

The purpose of this section is to detail the WBD module's modes of operation. The following modes and operations are described:

- 1. Normal Mode.

- 2. Deep Sleep & Power Down Mode.

#### 4.5.2 Normal Mode

The Normal mode corresponds to the WBD operating in the receive chain in a regular manner.

The UHF wideband detector helps to prevent the RF stages from saturating in presence of strong interferers (PAL / SECAM / DVB-T) in the UHF band. If saturation occurs, severe distortion of the on-channel signal would result. The detector provides a measurement of the peak signal level present at the internal LNA-with-AGC output, and feeds this information back to the baseband demodulator IC via an analog output signal. The baseband processor then analyzes both the in-band signal information and the wideband signal information, and eventually correct the AGC response accordingly at both RF and baseband stages.

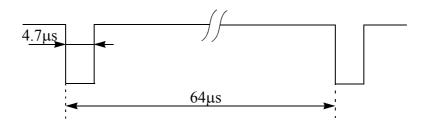

In any interferer case (PAL, SECAM, DVB-T interferers), the RF power detection with a peak detector is the more appropriate detection system. The detector requires a short "charge" time constant to rapidly detect the signal amplitude, but a long "discharge" time constant in order not to follow any AM modulation, which would cause AGC pumping.

The time constant will be defined in order to get a compromise between an analog TV signal detection and a DVB-T signal detection. A DVB-T signal can be considered as a pure noise signal where the peak-to-mean ration is given by the standard and limited to + 12 dB.

The cut-off frequency is defined by the sampling rate of the slow ADC integrated in the baseband demodulator. The effective sampling rate is in the order of 1 KHz that means that the cut-off frequency will stay below about 500 Hz which corresponds to a decay time of 2 ms. An external capacitor is used to generate such a long time constant. The combination between the value of this external capacitor and the discharging current of the MC44CD02 will define the time constant. This will be explained later on the application recommendations section.

The peak amplitude detection must be dimensioned according to the synchronization pulse of PAL modulated signals (**Figure 4-2**).

Figure 4-2 PAL Synchronization Signal

A cut-off frequency in the range of 500 Hz (2ms) is assumed, adequate for PAL modulated signals, and in agreement with the effective sampling rate of the baseband processor ADC. SECAM modulated signals are more problematic due to their positive modulation scheme, and may require additional signal processing in the baseband processor.

The decay rate is dimensioned according to the resolution of the baseband processor input ADC. 8 bits cover a range of about 2 volts, leading to a 1 LSB value of 8mV. Therefore, a decay rate of 5mV/2ms (2.5mV/ms) is appropriate.

The output signal dynamic must be dimensioned in order to take advantage of the 8-bits slow ADC resolution at the input of the baseband digital demodulator (effective sampling rate of 1 kHz / voltage range 0.1 V to 2.7 V / resistance  $20 \text{k}\Omega$  minimum). The linearization of the detector response will be performed inside the digital demodulator after the slow AD converter.

#### 4.5.3 WBD calibration procedure

Tuning is mandatory in order to guarantee that WBD meets error specification. This tuning concerns one of the registers (WBD Control Register 2, \$04 address) containing information about detection offset, and detector gain. Calibration algorithm is the following (frequency set at 666MHz, external LNA gain and RFAGC gain both set at their maximum values):

Step 1: With detector gain set to 3 (intermediate position) and -40dBm at the tuner input for maximum LNA gain condition, use detector offset bits to set the detection voltage output as close as possible to 1.6V.

Step 2: With this new setting of detector offset bits, keep tuning using the detector gain bits in order to set the detector output voltage as close as possible of the 1.6V target.

The I2C registers values found should be saved in system memory, and programmed into the tuner at start-up. This is normally a one time calibration routine that should occur in production.

### 4.5.4 Deep Sleep & Power Down Mode

The WBD module will be in low power mode (current consumption <1 µA) when

- ENABLE (pin 26) is held at logic low.

- ENABLE is held at logic high and the PDM bit (in the MODE register at I2C address \$00) is asserted.

# **OSC Functional Description**

#### 4.6.1 General

The purpose of this section is to detail the OSC module's modes of operation. The following modes and operations are described:

- 1. Normal Mode.

- 2. Power Down Mode.

- 3. Deep Sleep

#### 4.6.2 Normal Mode

The Normal Mode corresponds to the OSC module operating in a regular manner, i.e. in oscillation mode. The OSC module is set into normal mode once a high level is applied on the MC44CD02 input pin #26 ENABLE.

#### 4.6.2.1 Crystal Oscillator Principle

The OSC module is made of a 36 or 26 MHz crystal oscillator based on the Pierce architecture. The active part of the oscillator is integrated on chip (active device of the negative impedance and biasing), while the passive parts (feedback capacitors and 36 or 26 MHz crystal element) are external and connected around the input pins #20 EXTAL and #21 XTAL.

The start-up of the oscillator is sped up by the use of a boost mode. The principle is to increase the biasing current at start-up, and to reduce it for normal mode operation after a pre-defined number of clocks is counted. This system ensures proper start-up and oscillation amplitude.

The 36MHz or 26MHz sinusoïdal oscillation signal is buffered and turned into a 36MHz or 26MHz CMOS signal, to provide the clock for the digital core of the MC44CD02 chip, the input clock of the reference divider of the PLL (division ratio 216 or 156 to generate 166.66kHz), and the refence clock for the baseband demodulator chip through one of the clock output buffer (either custom LVDS buffer driving the output pins #23 CLK\_OUT and #24 CLK\_OUTB, or the single-ended buffer driving the output pin #23 CLK\_OUT).

#### 4.6.2.2 Recommended Crystal Characteristics

The selected crystals are the NX3225DA 36MHz (W-191-563) or 26MHz (W-191-653) quartz's from the NDK company . The following **Table 4-3** and **Table 4-4** summarize their key characteristics.

Table 4-3 36MHz NX3225DA Quartz Key Characteristics

| Feature              | Typical Value |

|----------------------|---------------|

| Operating Mode       | Fundamental   |

| Motional Inductance  | 4.90 mH       |

| Motional Capacitance | 3.99 fF       |

Table 4-3 36MHz NX3225DA Quartz Key Characteristics

| Feature                          | Typical Value |

|----------------------------------|---------------|

| Motional Resistance <sup>1</sup> | 50 Ω          |

| Case Capacitance                 | 1 pF          |

| Loading Capacitance              | 8 pF          |

#### NOTES:

Table 4-4 26MHz NX3225DA Quartz Key Characteristics

| Feature                          | Typical Value |

|----------------------------------|---------------|

| Operating Mode                   | Fundamental   |

| Motional Inductance              | 3.75 mH       |

| Motional Capacitance             | 10 fF         |

| Motional Resistance <sup>1</sup> | 50 Ω          |

| Case Capacitance                 | 1 pF          |

| Loading Capacitance              | 8 pF          |

#### NOTES:

#### 4.6.2.3 External Reference Clock

The EXTAL input pin of the OSC module can be used as the input gate for an external reference clock, that is then used as the reference clock for the whole chip including PLL. In that case, the OSC circuit does not behave anymore as a crystal oscillator (and the external crystal element and feedback capacitors must be removed from the application schematic - refer to the application information chapter of this document for additional details), but as as buffer for this reference clock.

Extreme care must be taken concerning the amplitude, duty-cycle, and jitter (phase noise) of the external reference clock not to impact digital core nor PLL performances. Constraints are detailled in the electrical specifications chapters of this document.

#### 4.6.2.4 Reference Clock Frequency

The MC44CD02 chip is able to handle two different reference clock frequencies 36MHz and 26MHz. Different modules of the chip (digital core, PLL, tracking loop filter, clock outputs...) need to be configured according to the reference clock frequency used.

As the I2C bit PADCTRL (reg \$05) is held at logic low, the chip configuration with regards to the clock frequency is set by the DC level applied on multi-level pin#37 CLK\_SEL (see the MLP Functional Description chapter for more details). As the I2C bit PADCTRL is turned high, the chip configuration is forced by the value of the I2C bit REFCLK (reg \$01).

<sup>1.</sup> Maximum value upon startup.

<sup>1.</sup> Maximum value upon startup.

set value of the I2C bit PADCTRL is 0, such as at power on reset, priority is given to the multi-level pin#37 CLK\_SEL to configure the MC44CD02 chip according to the reference clock frequency used.

#### 4.6.2.5 Reference Clock Ouput Interface

Two different clock buffers can be used for interfacing the 36MHz or 26MHz reference clock from the MC44CD02 chip to the baseband demodulator circuit. Both those buffers cannot be activated simultaneously.

As the I2C bit PADCTRL (reg \$05) is held at logic low, the clock buffer selection is set by the DC level applied on multi-level pin#37 CLK\_SEL (see the MLP Functional Description chapter for more details). As the I2C bit PADCTRL is turned high, the clock buffer selection is forced by the value of the I2C bit CLKBUF (see the I2C Communication and Registers chapter for more details).

The reset value of the I2C bit PADCTRL is 0, such as at power on reset, priority is given to the multi-level pin#37 CLK\_SEL to configure the clock buffer according to the application requirements.

#### 4.6.2.5.1 Custom LVDS interface

A custom Low Voltage Differential Signaling (LVDS) technology is used for interfacing the 36MHz or 26MHz reference clock from the MC44CD02chip to the baseband demodulator circuit. Such a technology allows low noise and low electromagnetic interference spreading over the radio board.

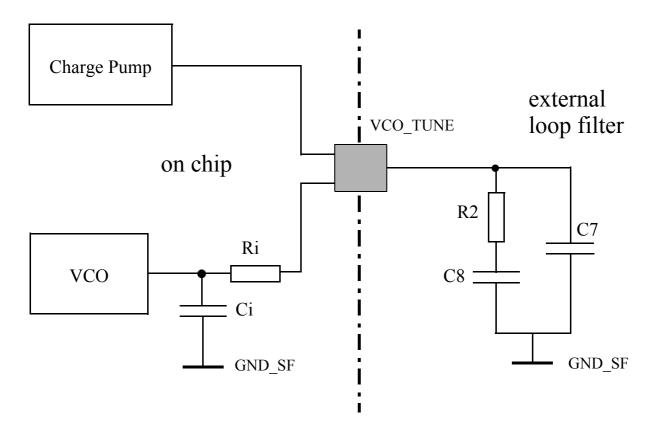

The LVDS buffer is selected as the I2C bit CLKBUF is set to 0.