# MC68HC05BS8 MC68HC705BS8

TECHNICAL DATA

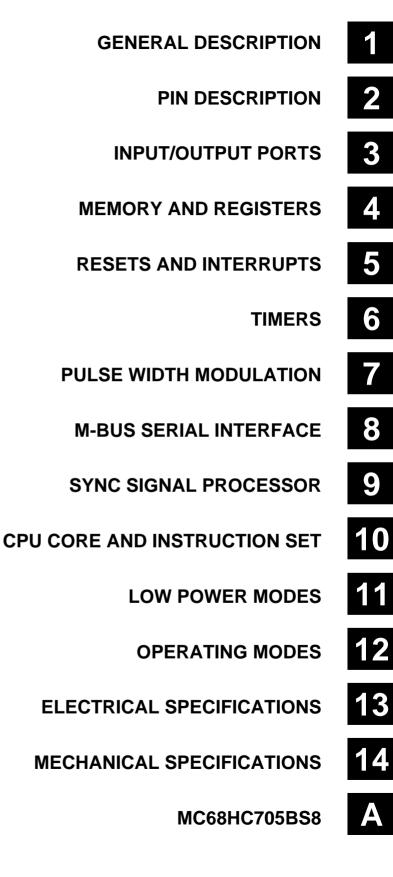

| NP |                              |  |  |  |

|----|------------------------------|--|--|--|

|    |                              |  |  |  |

| 2  | PIN DESCRIPTION              |  |  |  |

| 3  | INPUT/OUTPUT PORTS           |  |  |  |

| 4  | MEMORY AND REGISTERS         |  |  |  |

| 5  | RESETS AND INTERRUPTS        |  |  |  |

| 6  | TIMERS                       |  |  |  |

| 7  | PULSE WIDTH MODULATION       |  |  |  |

| 8  | M-BUS SERIAL INTERFACE       |  |  |  |

| 9  | SYNC SIGNAL PROCESSOR        |  |  |  |

| 10 | CPU CORE AND INSTRUCTION SET |  |  |  |

| 11 | LOW POWER MODES              |  |  |  |

| 12 | OPERATING MODES              |  |  |  |

| 13 | ELECTRICAL SPECIFICATIONS    |  |  |  |

| 14 | MECHANICAL SPECIFICATIONS    |  |  |  |

| Α  | MC68HC705BS8                 |  |  |  |

# MC68HC05BS8 MC68HC705BS8

High-density complementary metal oxide semiconductor (HCMOS) microcontroller unit

# Conventions

Register and bit mnemonics are defined in the paragraphs describing them.

An overbar is used to designate an active-low signal, eg: RESET.

Unless otherwise stated, blank cells in a register diagram indicate that the bit is either unused or reserved; shaded cells indicate that the bit is not described in the following paragraphs; 'u' is used to indicate an undefined state (on reset).

### CUSTOMER FEEDBACK QUESTIONNAIRE (MC68HC05BS8D/H)

Motorola wishes to continue to improve the quality of its documentation. We would welcome your feedback on the publication you have just received. Having used the document, please complete this card (or a photocopy of it, if you prefer).

1. How would you rate the quality of the document? Check one box in each category.

|    |                    | Excellent                               | Poor                  |                               | Excellent    |         |               | Poor |             |

|----|--------------------|-----------------------------------------|-----------------------|-------------------------------|--------------|---------|---------------|------|-------------|

|    | Organization       |                                         |                       | Tables                        |              |         |               |      |             |

|    | Readability        |                                         |                       | Table of contents             | Ē            |         | $\overline{}$ |      |             |

|    | Understandabili    | ty 🗍 🗍                                  |                       | Index                         |              |         |               |      |             |

|    | Accuracy           |                                         |                       | Page size/binding             |              |         |               |      |             |

|    | Illustrations      |                                         |                       | Overall impression            |              |         |               |      |             |

|    | Comments:          |                                         |                       |                               |              |         |               |      |             |

|    |                    |                                         |                       |                               |              |         |               |      |             |

| 2. | What is your int   | ended use for this de                   | ocument? If more th   | an one option applies, plea   | ase rank th  | iem (1, | 2, 3).        |      |             |

|    | Selection of dev   | vice for new applicati                  | ion 🔲                 | Other Please s                | specify:     |         |               |      |             |

|    | System design      |                                         |                       |                               |              |         |               |      |             |

|    | Training purpose   | es                                      |                       |                               |              |         |               |      |             |

|    |                    |                                         | _                     |                               |              |         |               |      |             |

| 3. | How well does t    | his manual enable y                     | ou to perform the ta  | ask(s) outlined in question 2 | 2?           |         |               |      |             |

|    |                    | Completely                              | Not at all            | Comments:                     |              |         |               |      |             |

|    |                    |                                         |                       |                               |              |         |               |      |             |

| 4. | How easy is it to  | o find the information                  | n you are looking for | ?                             |              |         |               |      |             |

|    |                    | Easy                                    | Difficult             | Comments:                     |              |         |               |      |             |

|    |                    |                                         |                       |                               |              |         |               |      |             |

|    |                    |                                         |                       |                               |              |         |               |      |             |

| 5. | Is the level of te | chnical detail in the                   | following sections s  | ufficient to allow you to und |              |         | device        |      |             |

|    | SECTION 1          | GENERAL DESCR                           |                       | Т                             | oo little de | tail    | _             | Too  | much detail |

|    |                    | PIN DESCRIPTION                         |                       |                               | ų            | 닏       | H٩.           | ų    | ų           |

|    |                    | INPUT/OUTPUT PO                         |                       |                               | H            | ų       | ų.            | ų    | ų           |

|    |                    | MEMORY AND RE                           |                       |                               | H            | ų       | ų.            | ų    | ų           |

|    |                    | RESETS AND INTE                         |                       |                               | ų            | 닏       | H٩.           | ų    | ų           |

|    |                    | TIMERS                                  |                       |                               |              | 닏       | H             |      | H           |

|    |                    | PULSE WIDTH MO                          |                       |                               |              | 닏       | H             | H    | L.          |

|    |                    | M-BUS SERIAL INT                        |                       |                               |              | 닏       | H             | H    |             |

|    |                    | SYNC SIGNAL PRO                         |                       |                               |              | 닏       | 븟             | 닏    |             |

|    |                    | CPU CORE AND IN                         |                       |                               |              |         |               |      |             |

|    |                    | LOW POWER MOD                           |                       |                               |              | 님       | ⊣             | H    |             |

|    | SECTION 12         | OPERATING MODE                          | ES                    |                               |              | H       | H             |      |             |

|    |                    | ELECTRICAL SPEC                         |                       |                               |              |         |               | H    |             |

|    | SECTION 14         | MECHANICAL SPE                          | CIFICATIONS           |                               |              |         |               |      |             |

|    |                    | MC68HC705BS8                            |                       |                               |              |         |               |      | H           |

|    | Comments:          |                                         |                       |                               | ·            | ليعا    |               |      | - <b></b>   |

| 6. |                    | any errors? If so, pl                   |                       |                               |              |         |               |      |             |

|    |                    | , , , , , , , , , , , , , , , , , , , , |                       |                               |              |         |               |      |             |

| 7. | From your point    | of view, is anything                    | missing from the do   | ocument? If so, please say    | what:        |         |               |      |             |

|    |                    |                                         |                       |                               |              |         |               |      |             |

| _   |                                                                                                                                                                                                                                                                         |                                                                          |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| 8.  | How could we improve this document?                                                                                                                                                                                                                                     |                                                                          |

| 11. | How would you rate Motorola's documentation?         Excellent       Poor         - In general                                                                                                                                                                          |                                                                          |

|     | – Second fold back along this line –                                                                                                                                                                                                                                    |                                                                          |

|     | By air mail by air mail by air main by a series   Fix stamp here Fix stamp here Fix stamp here Kotorola Semiconductors H.K. Ltd., 13/F, Prosperity Centre, 77-81 Container Port Road, Kwai Chung, N.T., HONG KONG. Kotorona Kana base base base base base base base bas | – cut along this line to remove –<br>– First fold back along this line – |

|     |                                                                                                                                                                                                                                                                         |                                                                          |

|     | – Third fold back along this line –                                                                                                                                                                                                                                     |                                                                          |

| 13. | Currently there is some discussion in the semiconductor industry regarding a move towards providing data sheets in ele form. If you have any opinion on this subject, please comment.                                                                                   | ctronic                                                                  |

| 14. | We would be grateful if you would supply the following information (at your discretion), or attach your card. Name: Phone No:                                                                                                                                           |                                                                          |

|     | Position: FAX No:                                                                                                                                                                                                                                                       |                                                                          |

|     | Company:                                                                                                                                                                                                                                                                |                                                                          |

|     | Address:                                                                                                                                                                                                                                                                |                                                                          |

|     | or helping us improve our documentation,<br>echnical Publications , Motorola Semiconductors H.K. Ltd., Hong Kong.                                                                                                                                                       | <u> </u>                                                                 |

X

# TABLE OF CONTENTS

Paragraph Number

TITLE

Page Number

### 1 GENERAL DESCRIPTION

| 1.1 Features | .1- | ·1 |

|--------------|-----|----|

|--------------|-----|----|

### 2 PIN DESCRIPTION

| 2.1 | Pin Descriptions | 2-1 |

|-----|------------------|-----|

| 2.2 | Pin Assignment   | 2-2 |

### 3 INPUT/OUTPUT PORTS

| 3.1 | Input/Output Programming                           | 3-1 |

|-----|----------------------------------------------------|-----|

|     | Port A, B, and C                                   |     |

|     | PB7 - RSPWM Counter Reset                          |     |

|     | PC0:5 - Keyboard Interrupts                        |     |

|     | PC6 and PC7 - Software Supported M-Bus SDA and SCL |     |

### 4

### MEMORY AND REGISTERS

| 4.1   | Registers               | 4-1 |

|-------|-------------------------|-----|

| 4.2   | RAM                     | 4-1 |

| 4.3   | ROM (MC68HC05BS8)       | 4-1 |

| 4.4   | EPROM (MC68HC705BS8)    | 4-1 |

| 4.5   | EEPROM                  | 4-2 |

| 4.5.1 | EEPROM Control Register | 4-2 |

| 4.5.2 | EEPROM Options Register | 4-3 |

| 4.5.3 | Read Procedure          | 4-3 |

| 4.5.4 | Erase Procedure         | 4-4 |

| 4.5.5 | Programming Procedure   | 4-4 |

Paragraph Number

### TITLE

### 5 RESETS AND INTERRUPTS

| 5.1     | RESETS                                  | 5-1  |

|---------|-----------------------------------------|------|

| 5.1.1   | Power-On Reset (POR)                    | 5-1  |

| 5.1.2   | RESET Pin                               |      |

| 5.1.3   | Low Voltage Reset (LVR)                 | 5-2  |

| 5.1.4   | Computer Operating Properly (COP) Reset | 5-3  |

| 5.2     | INTERRUPTS                              | 5-3  |

| 5.2.1   | Non-maskable Software Interrupt (SWI)   | 5-5  |

| 5.2.2   | Maskable Hardware Interrupts            | 5-5  |

| 5.2.2.1 | External Interrupt (IRQ)                | 5-5  |

| 5.2.2.2 | 2 Sync Signal Processor Interrupt       | 5-7  |

| 5.2.2.3 | 3 M-Bus Interrupts                      | 5-7  |

| 5.2.2.4 | Timer Interrupts                        | 5-8  |

| 5.2.2.5 | 5 Core Timer Interrupts                 | 5-9  |

| 5.2.2.6 | 6 Keyboard Interrupt                    | 5-10 |

|         |                                         |      |

# 6

# TIMERS

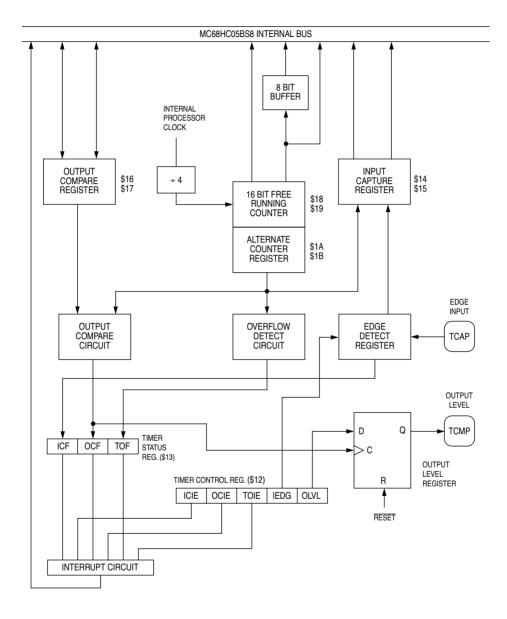

| 6.1   | PROGRAMMABLE TIMER                 | 6-1  |

|-------|------------------------------------|------|

| 6.1.1 | Counter                            | 6-3  |

| 6.1.2 | Output Compare Register            | 6-4  |

| 6.1.3 | Input Capture Registers            | 6-4  |

| 6.1.4 | Timer Control Register             | 6-5  |

| 6.1.5 | Timer Status Register (TSR)        | 6-6  |

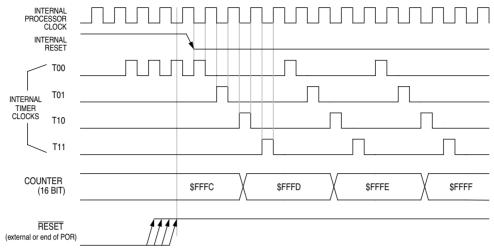

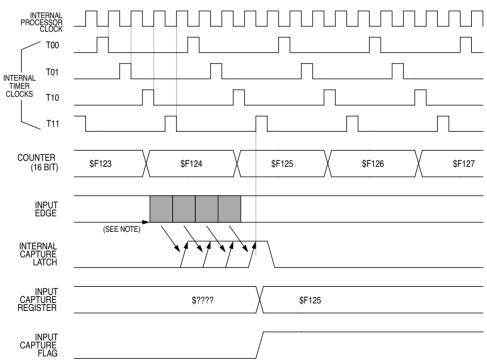

| 6.1.6 | Programmable Timer Timing Diagrams | 6-7  |

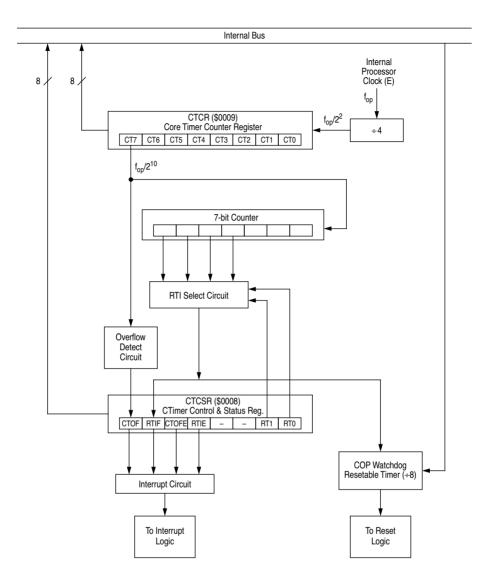

| 6.2   | CORE TIMER                         | 6-10 |

| 6.2.1 | CTimer Counter Register            | 6-10 |

| 6.2.2 | CTimer Control and Status Register | 6-10 |

| 6.2.3 | COP Watchdog Reset                 | 6-12 |

|       |                                    |      |

### 7 PULSE WIDTH MODULATION

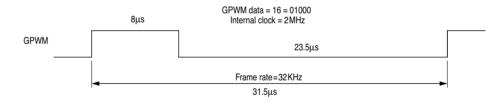

| General Purpose Pulse Width Modulator                     | 7-1                                                   |

|-----------------------------------------------------------|-------------------------------------------------------|

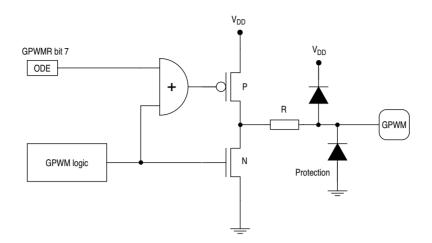

| General Purpose Pulse Width Modulator Register (GPWM)     | 7-2                                                   |

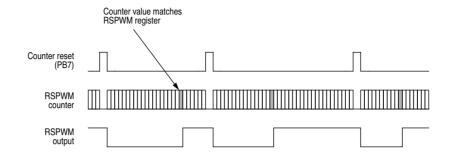

| Raster Positioning Pulse Width Modulator                  | 7-2                                                   |

| Raster Positioning Pulse Width Modulator Register (RSPWM) | 7-4                                                   |

|                                                           | General Purpose Pulse Width Modulator Register (GPWM) |

Paragraph Number

### TITLE

## 8

# M-BUS SERIAL INTERFACE

| 8.1   | M-Bus Interface Features                                         | 8-1  |

|-------|------------------------------------------------------------------|------|

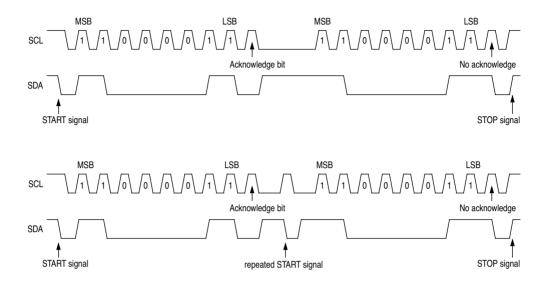

| 8.2   | M-Bus Protocol                                                   | 8-2  |

| 8.2.1 | START Signal                                                     | 8-3  |

| 8.2.2 | Slave Address Transmission                                       | 8-3  |

| 8.2.3 | Data Transfer                                                    |      |

| 8.2.4 | Repeated START Signal                                            | 8-4  |

| 8.2.5 | STOP Signal                                                      | 8-4  |

| 8.2.6 | Arbitration Procedure                                            |      |

| 8.2.7 | Clock Synchronization                                            | 8-5  |

| 8.2.8 | Handshaking                                                      | 8-5  |

| 8.3   | M-Bus Registers                                                  |      |

| 8.3.1 | M-Bus Address Register (MADR)                                    | 8-6  |

| 8.3.2 | M-Bus Frequency Register (MFDR)                                  | 8-6  |

| 8.3.3 | M-Bus Control Register (MCR)                                     | 8-7  |

| 8.3.4 | M-Bus Status Register (MSR)                                      |      |

| 8.3.5 | M-Bus Data I/O Register (MDR)                                    | 8-9  |

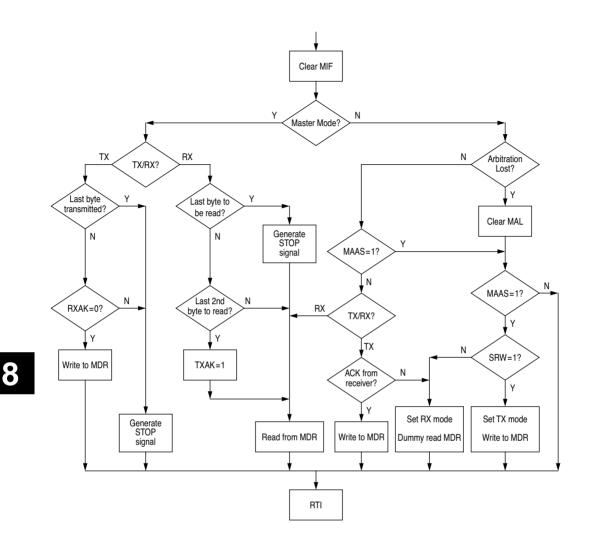

| 8.4   | Programming Considerations                                       | 8-11 |

| 8.4.1 | Initialization                                                   | 8-11 |

| 8.4.2 | Generation of a START Signal and the First Byte of Data Transfer | 8-11 |

| 8.4.3 | Software Responses after Transmission or Reception of a Byte     | 8-11 |

| 8.4.4 | Generation of the STOP Signal                                    |      |

| 8.4.5 | Generation of a Repeated START Signal                            | 8-13 |

| 8.4.6 | Slave Mode                                                       | 8-13 |

| 8.4.7 | Arbitration Lost                                                 | 8-13 |

| 8.5   | Software Supported M-Bus Interface                               | 8-14 |

|       |                                                                  |      |

### 9

## SYNC SIGNAL PROCESSOR

| Introduction                                    | .9-1                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

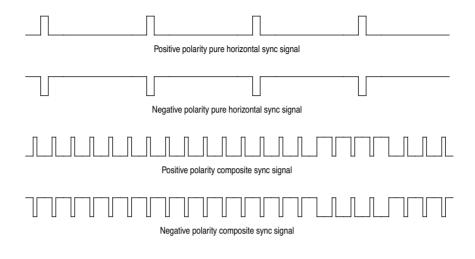

| Polarity Correction                             | .9-2                                                                                                                                                                                                                                                                                                          |

| Separate Vertical Sync Input                    | .9-2                                                                                                                                                                                                                                                                                                          |

| Separate Horizontal or Composite Sync Input     | .9-2                                                                                                                                                                                                                                                                                                          |

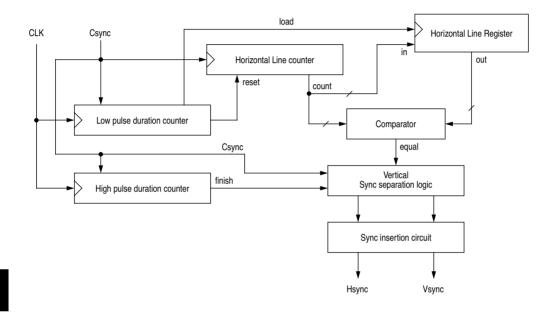

| Sync Detection                                  | .9-3                                                                                                                                                                                                                                                                                                          |

| Free-running Pseudo Sync Signal Generator       | .9-3                                                                                                                                                                                                                                                                                                          |

| Sync Separation                                 | .9-4                                                                                                                                                                                                                                                                                                          |

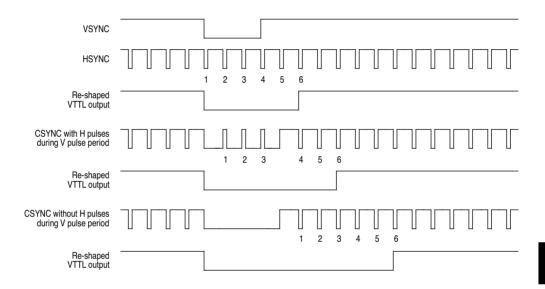

| Vertical Sync Pulse Reshaper                    | .9-5                                                                                                                                                                                                                                                                                                          |

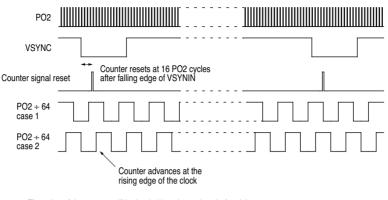

| Sync Signal Counters                            | .9-5                                                                                                                                                                                                                                                                                                          |

| VSYNC Interrupt                                 | .9-6                                                                                                                                                                                                                                                                                                          |

| Sampling Pulse Output                           | .9-7                                                                                                                                                                                                                                                                                                          |

| SSP Registers                                   | .9-7                                                                                                                                                                                                                                                                                                          |

| Sync Signal Control and Status Register (SSCSR) |                                                                                                                                                                                                                                                                                                               |

|                                                 | Polarity Correction<br>Separate Vertical Sync Input.<br>Separate Horizontal or Composite Sync Input.<br>Sync Detection<br>Free-running Pseudo Sync Signal Generator<br>Sync Separation<br>Vertical Sync Pulse Reshaper<br>Sync Signal Counters<br>VSYNC Interrupt.<br>Sampling Pulse Output.<br>SSP Registers |

| Paragraph<br>Number | TITLE                                | Page<br>Number |

|---------------------|--------------------------------------|----------------|

| 9.10.2              | Vertical Frequency Register (VFR)    | 9-9            |

| 9.10.3              | Line Frequency Registers (LFRs)      | 9-9            |

| 9.10.4              | Interrupt Line Count Register (ILCR) | 9-10           |

| 9.10.5              | Sampling Pulse Register (SPR)        | 9-10           |

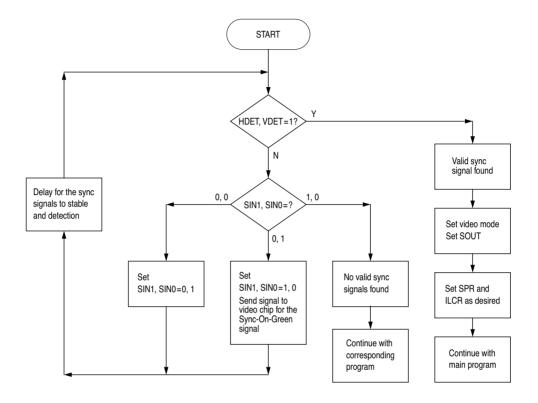

| 9.11                | System Operation                     |                |

### 10 CPU CORE AND INSTRUCTION SET

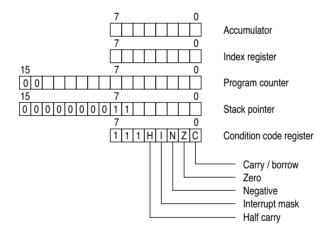

| 10.1    | Registers                     | 10-1  |

|---------|-------------------------------|-------|

| 10.1.1  |                               |       |

| 10.1.2  | Index register (X)            | 10-2  |

| 10.1.3  |                               |       |

| 10.1.4  |                               |       |

| 10.1.5  | Condition code register (CCR) | 10-2  |

| 10.2    | Instruction set               |       |

| 10.2.1  | Register/memory Instructions  | 10-4  |

| 10.2.2  |                               |       |

| 10.2.3  |                               |       |

| 10.2.4  |                               |       |

| 10.2.5  |                               |       |

| 10.2.6  |                               | -     |

| 10.3    | Addressing modes              |       |

| 10.3.1  |                               | -     |

| 10.3.2  |                               | -     |

| 10.3.3  | Direct                        | 10-11 |

| 10.3.4  |                               |       |

| 10.3.5  |                               |       |

| 10.3.6  |                               |       |

| 10.3.7  |                               |       |

| 10.3.8  |                               |       |

| 10.3.9  | Bit set/clear                 | 10-13 |

| 10.3.10 | 0 Bit test and branch         | 10-13 |

### 11 LOW POWER MODES

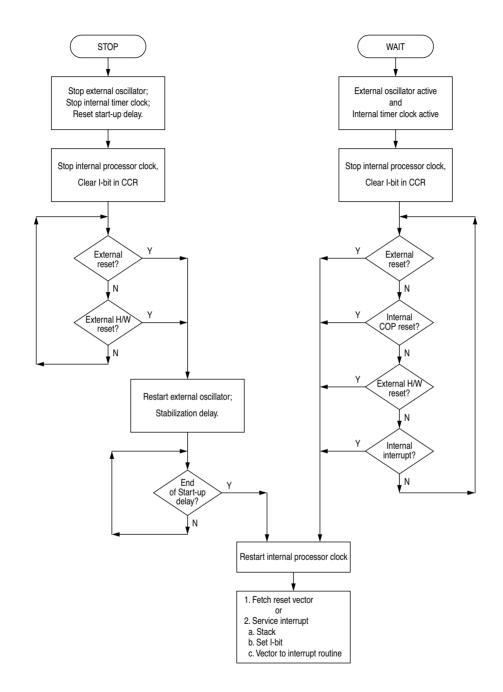

| 11.1 | STOP Mode                         | 11-1 |

|------|-----------------------------------|------|

| 11.2 | WAIT Mode                         | 11-1 |

| 11.3 | Data Retention Mode               | 11-3 |

| 11.4 | COP Watchdog Timer Considerations | 11-3 |

Paragraph Number

### TITLE

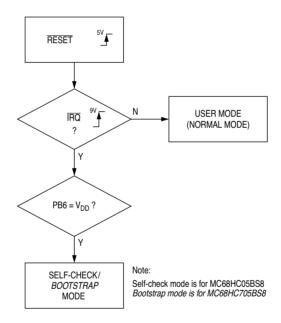

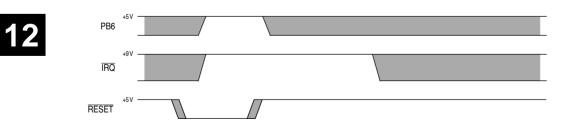

### 12 OPERATING MODES

| 12.1 | User Mode (Normal Operation) | 12-2 |

|------|------------------------------|------|

|      | Self-Check Mode              |      |

| 12.3 | Bootstrap Mode               | 12-4 |

### 13

## **ELECTRICAL SPECIFICATIONS**

| 13.1 | Maximum Ratings               | 13-1 |

|------|-------------------------------|------|

|      | Thermal Characteristics       |      |

|      | DC Electrical Characteristics |      |

| 13.4 | Control Timing                | 13-3 |

|      | Pulse Width Modulator Timing  |      |

|      | M-Bus Timing                  |      |

| 13.7 | Sync Signal Processor Timing  | 13-6 |

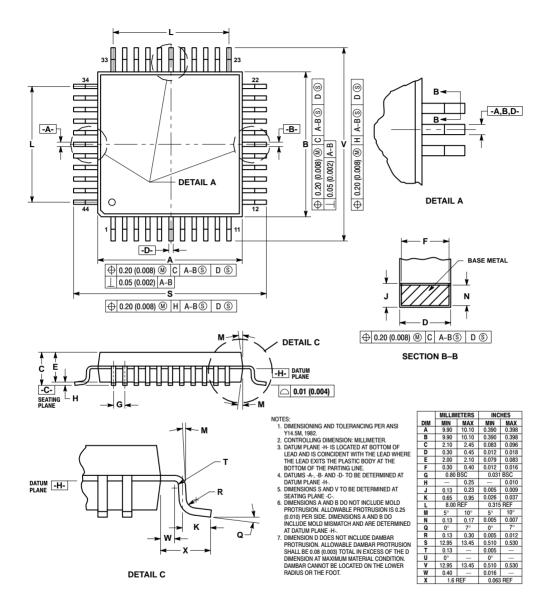

### 14 MECHANICAL SPECIFICATIONS

| 14.1 | 44-pin QFP Package | .14- | 2 |

|------|--------------------|------|---|

|      | ··· F···           |      |   |

### A MC68HC705BS8

| A.1   | Features                   | A-1 |

|-------|----------------------------|-----|

| A.2   | Memory Map                 | A-1 |

| A.3   | Modes of Operation         |     |

| A.3.1 | User Mode                  |     |

| A.3.2 |                            |     |

| A.4   | EPROM Programming          |     |

| A.4.1 |                            |     |

| A.4.2 | EPROM Programming Sequence |     |

| A.5   | Pin Assignments            | A-5 |

|       | Electrical Specifications  |     |

| A.6.1 | Maximum Ratings            | A-5 |

# THIS PAGE LEFT BLANK INTENTIONALLY

# LIST OF FIGURES

| Figure<br>Number | TITLE                                                | Page<br>Number |

|------------------|------------------------------------------------------|----------------|

| 1-1              | MC68HC05BS8/MC68HC705BS8 Block Diagram               | 1-2            |

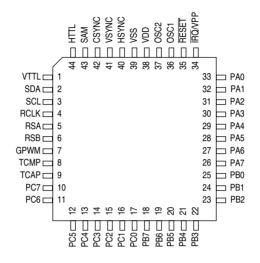

| 2-1              | Pin Assignment for 44-pin QFP Package                | 2-2            |

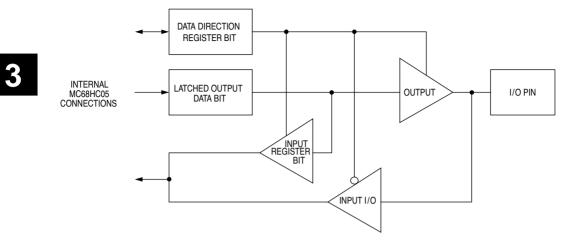

| 3-1              | Port I/O Circuitry                                   | 3-2            |

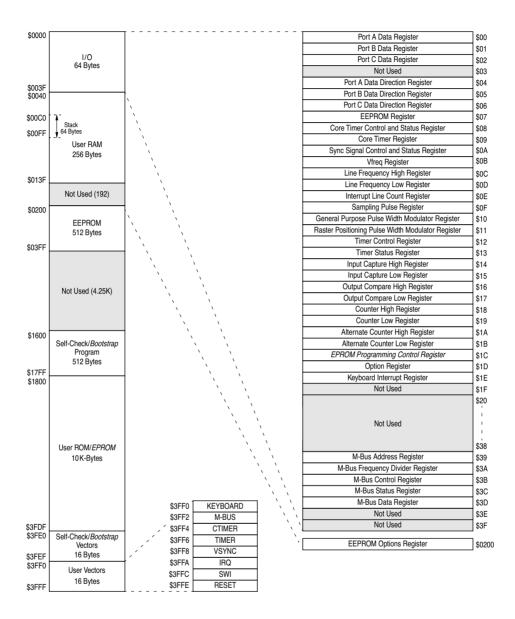

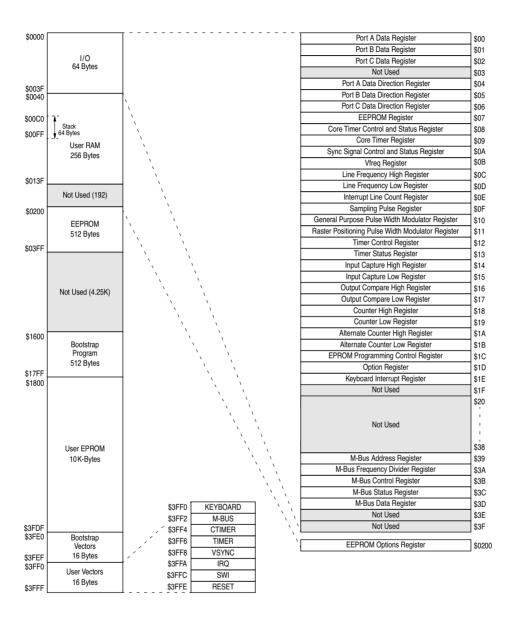

| 4-1              | Memory Map                                           |                |

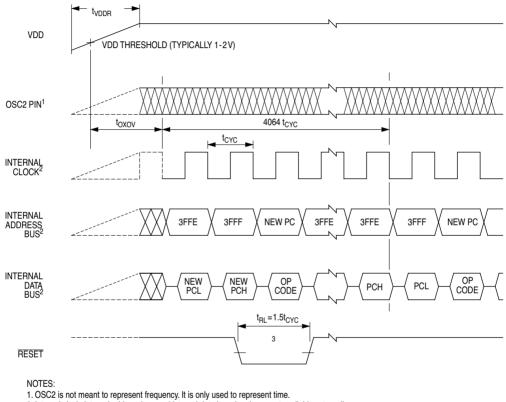

| 5-1              | Power-On Reset and RESET Timing                      | 5-2            |

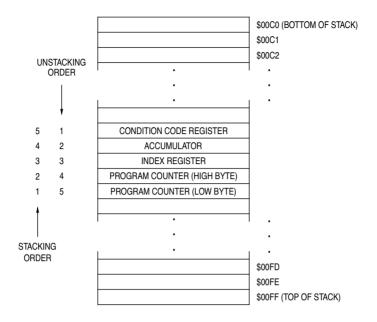

| 5-2              | Interrupt Stacking Order                             | 5-4            |

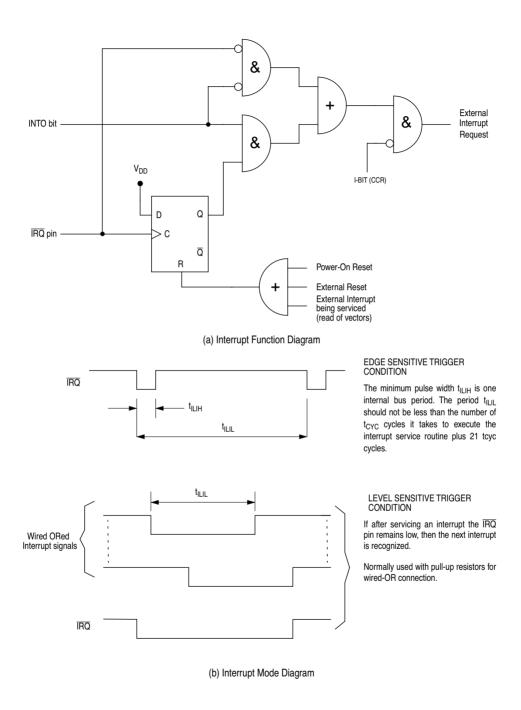

| 5-3              | External Interrupt Circuit and Timing                | 5-6            |

| 6-1              | Programmable Timer Block Diagram                     | 6-2            |

| 6-2              | Timer State Timing Diagram for Reset                 | 6-8            |

| 6-3              | Timer State Timing Diagram for Input Capture         | 6-8            |

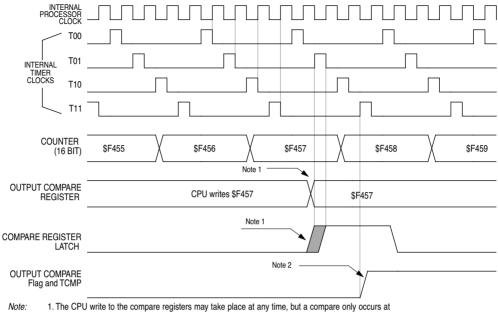

| 6-4              | Timer State Timing Diagram for Output Compare        | 6-9            |

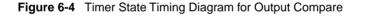

| 6-5              | Timer State Diagram for Timer Overflow               | 6-9            |

| 6-6              | Core Timer Block Diagram                             | 6-11           |

| 7-1              | GPWM Timing Example                                  | 7-1            |

| 7-2              | GPWM Output Configuration                            | 7-2            |

| 7-3              | RSPWM Timing Example                                 | 7-3            |

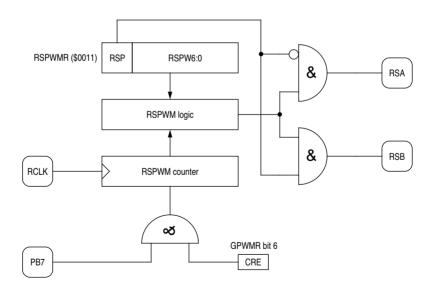

| 7-4              | RSPWM Block Diagram                                  | 7-3            |

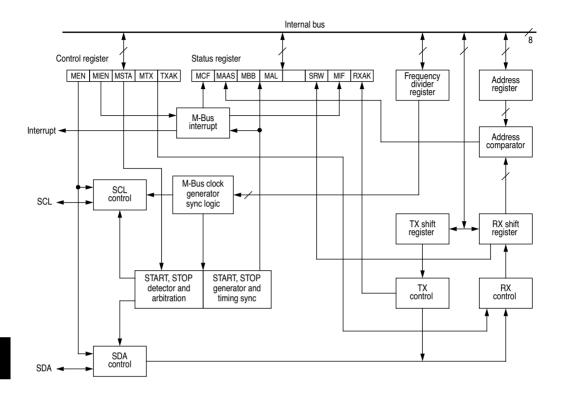

| 8-1              | M-Bus Interface Block Diagram                        | 8-2            |

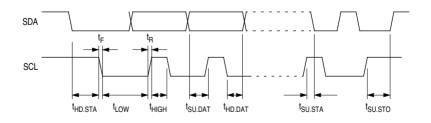

| 8-2              | M-Bus Transmission Signal Diagram                    | 8-3            |

| 8-3              | Clock Synchronization                                | 8-5            |

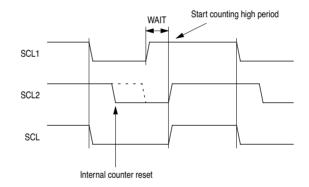

| 8-4              | Flowchart of M-Bus Interrupt Routine                 | 8-10           |

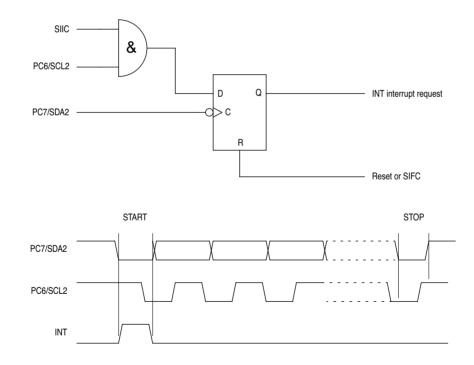

| 8-5              | Software Supported M-Bus Interrupt                   | 8-14           |

| 9-1              | Sync Signal Polarity Correction                      | 9-3            |

| 9-2              | Sync Separator                                       | 9-4            |

| 9-3              | VTTL Pulse Widths For Different Input Signal Formats | 9-5            |

| 9-4              | Vertical Frequency Counter Timing                    | 9-6            |

| 9-5              | Example of SSP operation                             | 9-11           |

| 10-1             | Programming model                                    | 10-1           |

| 10-2             | Stacking order                                       | 10-2           |

| 11-1             | STOP and WAIT Flowchart                              | 11-2           |

| 12-1             | Flowchart of Mode Entering                           | 12-1           |

| 12-2             | Self-Check Mode Timing                               |                |

| 12-3             | MC68HC05BS8 Self-Test Circuit                        | 12-3           |

| Figure<br>Number | TITLE                                  | Page<br>Number |

|------------------|----------------------------------------|----------------|

| 13-1             | PWM Timing                             | 13-4           |

| 13-2             | M-Bus Timing                           | 13-5           |

| 14-1             | 44-pin QFP Package (Case No. 824A-01)  | 14-2           |

| A-1              | MC68HC705BS8 Memory Map                |                |

| A-2              | Pin Assignments for 44-pin QFP package | A-5            |

# LIST OF TABLES

| Table<br>Number | TITLE                                         | Page<br>Number |

|-----------------|-----------------------------------------------|----------------|

| Number          | IIILE                                         | Number         |

| 3-1             | I/O Pin Functions                             | 3-1            |

| 4-1             | Erase Mode Select                             | 4-2            |

| 4-2             | Register Outline                              | 4-6            |

| 5-1             | Reset/Interrupt Vector Addresses              |                |

| 6-1             | COP Reset and RTI Rates                       | 6-12           |

| 8-1             | M-Bus Prescaler                               | 8-6            |

| 9-1             | Vertical Frame Frequencies                    | 9-9            |

| 10-1            | MUL instruction                               | 10-5           |

| 10-2            | Register/memory instructions                  | 10-5           |

| 10-3            | Branch instructions                           |                |

| 10-4            | Bit manipulation instructions                 | 10-6           |

| 10-5            | Read/modify/write instructions                | 10-7           |

| 10-6            | Control instructions                          | 10-7           |

| 10-7            | Instruction set                               | 10-8           |

| 10-8            | M68HC05 opcode map                            | 10-10          |

| 12-1            | Mode Selection                                | 12-2           |

| 12-2            | Self-Check Report                             | 12-4           |

| 13-1            | DC Electrical Characteristics for MC68HC05BS8 | 13-2           |

| 13-2            | Control Timing                                | 13-3           |

| 13-3            | M-Bus Interface Input Signal Timing           | 13-5           |

| 13-4            | M-Bus Interface Output Signal Timing          | 13-5           |

| 13-5            | Sync Signal Processor Timing                  | 13-6           |

| A-1             | MC68HC705BS8 Operating Mode Entry Conditions  | A-3            |

# THIS PAGE LEFT BLANK INTENTIONALLY

# **1** GENERAL DESCRIPTION

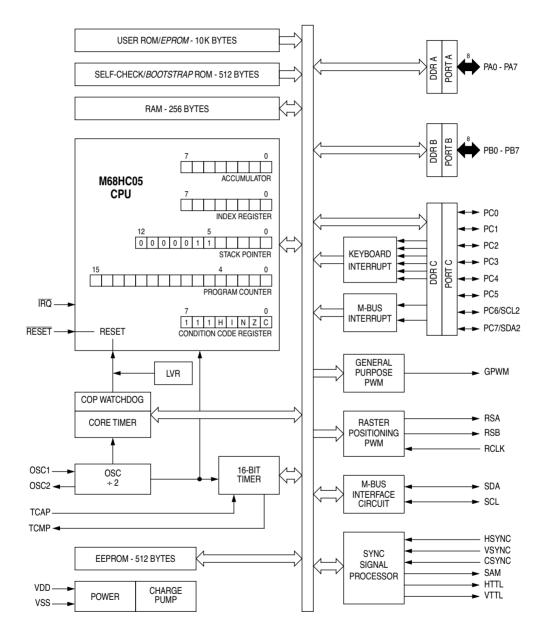

The MC68HC05BS8 HCMOS microcontroller is a member of the MC68HC05 Family of low-cost single-chip microcontrollers. It is particularly suitable as a multi-sync computer monitor controller. This 8-bit microcontroller unit (MCU) contains on-chip oscillator, CPU, RAM, ROM, EEPROM, I/O, Timers, COP Watchdog, M-Bus Serial Interface System, PWM, and Sync Signal Processor.

The MC68HC705BS8 is an EPROM version of the MC68HC05BS8. All references to the MC68HC05BS8 apply equally to the MC68HC705BS8, unless otherwise stated. *References specific to the MC68HC705BS8 are italicized in the text, and also, for quick reference, they are summarized in Appendix A.*

### 1.1 Features

- Fully static chip design featuring the industry standard 8-bit M68HC05 core

- Power saving Stop and Wait modes

- 256 bytes of RAM (64 bytes for stack)

- 10K-bytes of ROM for MC68HC05BS8 10K-bytes of EPROM for MC68HC705BS8

- 512 bytes of EEPROM

- 24 bidirectional I/O lines

- 6 keyboard interrupts

- Core timer with RTI and COP watchdog reset

- 2 M-Bus (I<sup>2</sup>C<sup>†</sup>) Serial Interfaces (one full H/W, one S/W with hardware support)

- Single channel 6-bit general purpose PWM Single channel 7-bit raster positioning PWM

- 16-bit programmable timer with one TCAP and one TCMP

- Sync signal processor

MC68HC05BS8

### **GENERAL DESCRIPTION**

<sup>†</sup> I<sup>2</sup>C-bus is a proprietary Philips interface bus

- Low voltage reset (LVR)

- Available in 44-pin QFP package

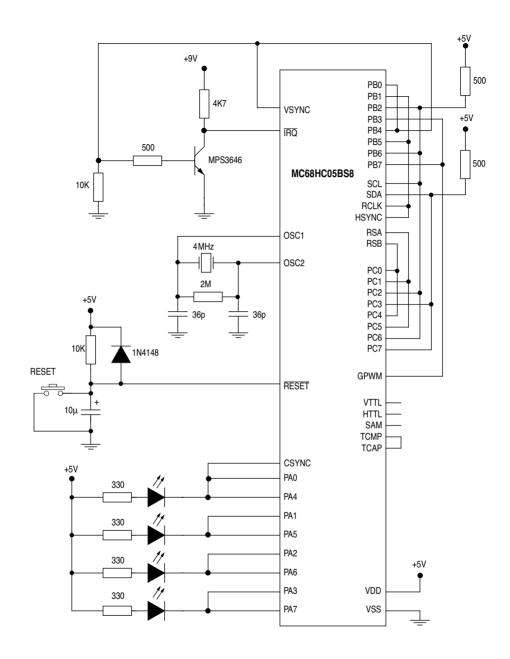

Figure 1-1 MC68HC05BS8/MC68HC705BS8 Block Diagram

# **2** PIN DESCRIPTION

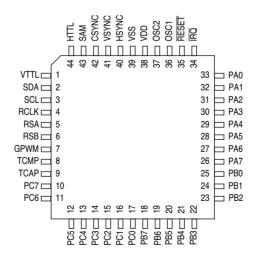

This section provides a description of the functional pins of the MC68HC05BS8 microcontroller.

# 2.1 Pin Descriptions

| PIN NAME   | 44-pin QFP<br>PIN No. | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                       |

|------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD, VSS   | 38, 39                | Power is supplied to the MCU using these pins. VDD is the positive power supply;<br>VSS is ground.                                                                                                                                                                                                                                                                                |

| IRQ/VPP    | 34                    | In the user mode this pin is the external hardware interrupt IRQ. Two choices of interrupt triggering sensitivity are available through the Option register:<br>1) negative-edge sensitive triggering, or<br>2) negative-level sensitive triggering.<br>In bootstrap mode on the MC68HC705BS8, this is the EPROM programming voltage input pin.                                   |

| RESET      | 35                    | The active low $\overline{\text{RESET}}$ input is not required for start-up, but can be used to reset the MCU internal state and provide an orderly software start-up procedure.                                                                                                                                                                                                  |

| OSC1, OSC2 | 36, 37                | MCU         These pins provide connections to the on-chip oscillator. The oscillator can be driven by an AT-crystal circuit or a ceramic resonator with a maximum frequency of 4.4MHz. OSC1 may also be driven by an external oscillator if an external crystal/resonator circuit is not used.       OSC1 OSC2         Example showing crystal connections.       36pF       36pF |

| PA0-PA7    | 33-26                 | These eight I/O lines comprise port A. The state of any pin is software programmable. All port A lines are configured as input during power-on or external reset.                                                                                                                                                                                                                 |

| PIN NAME     | 44-pin QFP<br>PIN No. | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PB0-PB7      | 25-18                 | These eight I/O lines comprise port B. The state of any pin is software<br>programmable. All port B lines are configured as input during power-on or external<br>reset.<br>PB7 is also used as the RSPWM counter reset input when PB7 is set as an input<br>pin and the counter reset enable bit is set in the GPWM register (bit 6 of \$0010).                                                                   |

| PC0-PC7      | 17-10                 | These eight I/O lines comprise port C. The state of any pin is software<br>programmable. All port C lines are configured as input during power-on or external<br>reset.<br>PC0-PC5 become keyboard interrupt input pins when the corresponding bits are<br>set in the Keyboard Interrupt register (\$001E).<br>PC6 and PC7 are SDA and SCL respectively, when used for the software<br>supported M-Bus Interface. |

| SDA, SCL     | 2, 3                  | These are the hardware M-Bus interface data and clock lines.                                                                                                                                                                                                                                                                                                                                                      |

| TCAP         | 9                     | This input pin controls the input capture function of the 16-bit free-running timer.                                                                                                                                                                                                                                                                                                                              |

| TCMP         | 8                     | This output pin indicates when a timer compare is successful.                                                                                                                                                                                                                                                                                                                                                     |

| GPWM         | 7                     | This is the output pin of the General purpose PWM.                                                                                                                                                                                                                                                                                                                                                                |

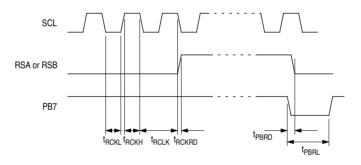

| RSA, RSB     | 5, 6                  | These are the two excursive outputs of the Raster Positioning PWM                                                                                                                                                                                                                                                                                                                                                 |

| RCLK         | 4                     | This is the input clock to drive the RSPWM counter.                                                                                                                                                                                                                                                                                                                                                               |

| HSYNC, VSYNC | 40, 41                | These two input pins are for the video sync signals from the host computer.                                                                                                                                                                                                                                                                                                                                       |

| CSYNC        | 42                    | This is the Composite sync signal input from the host computer.                                                                                                                                                                                                                                                                                                                                                   |

| SAM          | 43                    | This is the output of an sample signal from the Sync Signal Processor.                                                                                                                                                                                                                                                                                                                                            |

| HTTL, VTTL   | 44, 1                 | These are the output from the HSYNC and VSYNC inputs or the signals separated from CSYNC input.                                                                                                                                                                                                                                                                                                                   |

# 2.2 Pin Assignment

Figure 2-1 Pin Assignment for 44-pin QFP Package

# **3** INPUT/OUTPUT PORTS

The MC68HC05BS8 has 24 I/O lines, arranged as three 8-bit ports (Port A, B, and C). Each I/O line is individually programmable as either input or output, under the software control of the Data Direction registers. Port C also shares with keyboard interrupt and the software supported M-Bus functions.

To avoid glitches on the output pins, data should be written to the I/O Port Data register before writing "1"s to the corresponding Data Direction register bits to set the pins to output mode.

## 3.1 Input/Output Programming

Bidirectional port lines may be programmed as an input or an output under software control. The direction of the pins is determined by the state of the corresponding bit in the port data direction register (DDR). Each port has an associated DDR. Any I/O port pin is configured as an output if its corresponding DDR bit is set to a logic one. A pin is configured as an input if its corresponding DDR bit is cleared to a logic zero.

At power-on or reset, all DDRs are cleared, configuring all port pins as inputs. The data direction registers are capable of being written to or read by the MCU. During the programmed output state, a read of the data register actually reads the value of the output data latch and not the I/O pin. The operation of the standard port hardware is shown schematically in Figure 3-1.

This is summarized in Table 3-1 which shows the effect of reading from or writing to an I/O pin in various circumstances.

| R/W                                                                       | DDR | I/O Pin Function                                                          |  |  |  |  |

|---------------------------------------------------------------------------|-----|---------------------------------------------------------------------------|--|--|--|--|

| 0                                                                         | 0   | The I/O pin is in input mode. Data is written into the output data latch. |  |  |  |  |

| 0 1 Data is written into the output data latch and output to the I/O pin. |     |                                                                           |  |  |  |  |

| 1                                                                         | 0   | The state of the I/O pin is read.                                         |  |  |  |  |

| 1                                                                         | 1   | The I/O pin is in an output mode. The output data latch is read.          |  |  |  |  |

### Table 3-1I/O Pin Functions

Note:  $R/\overline{W}$  is an internal signal.

3

Figure 3-1 Port I/O Circuitry

### 3.2 Port A, B, and C

These are standard M68HC05 bidirectional I/O ports, each comprising a data register and a data direction register. All three are 8-bit ports.

Reset does not affect the state of the data registers, but clears the data direction registers, thereby returning all port pins to input mode. Writing a "1" to any DDR sets the corresponding port pin to output mode.

### 3.3 PB7 - RSPWM Counter Reset

In addition to normal I/O function, PB7 can be software selectable to input a reset signal to the Raster Positioning Pulse Width Modulator counter. The reset pulse requires an active high signal.

### 3.4 PC0:5 - Keyboard Interrupts

Six keyboard interrupt inputs are available on port pins PC0 to PC5. Each pin is enabled for keyboard interrupt by setting the corresponding keyboard interrupt enable bit in the KBI register (bits 0 to 5 of \$001E). When the KBI bit is set, the corresponding port C pin will be configured as an input pin, regardless of the DDRC setting, an internal pull-up resistor is connected to the pin.

The interrupt signal is latched, and it should be cleared by writing a "1" to the KBIC bit in the KBI register (bit 6 of \$001E) in the interrupt service routine. This should be cleared after the key is debounced, otherwise unwanted keyboard interrupt signals may be generated.

The keyboard interrupt is negative-edge sensitive only, and the interrupt service routine is specified by the contents of the memory locations \$3FF0 and \$3FF1.

|              | Address | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | State<br>on reset |  |

|--------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------|--|

| KBI Register | \$001E  |       | KBIC  | KBE5  | KBE4  | KBE3  | KBE2  | KBE1  | KBE0  | 0000 0000         |  |

### **KBIC - Keyboard Interrupt Clear**

1 (set) – Clear keyboard interrupt latch.

### KBE5:0 - Keyboard Interrupt Enable 5:0

- 1 (set) Enable keyboard interrupt for the corresponding bit.

- 0 (clear) Disable keyboard interrupt for the corresponding bit.

### 3.5 PC6 and PC7 - Software Supported M-Bus SDA and SCL

PC6 and PC7 are used for SDA and SDL respectively when configured for the software supported M-Bus interface. This M-Bus interface is operated by software emulation, with hardware interrupt circuit connected to PC6 and PC7.

THIS PAGE LEFT BLANK INTENTIONALLY

# **4** MEMORY AND REGISTERS

The MC68HC05BS8/*MC68HC705BS8* has a 16K-byte memory map consisting of I/O registers, user ROM/*EPROM*, user RAM, EEPROM, self-check/*bootstrap* ROM as shown in Figure 4-1.

## 4.1 Registers

All the I/O, control and status registers of the MC68HC05BS8 are located within the first 64-byte block of the memory map (address \$0000 to \$003F).

### 4.2 RAM

The user RAM consists of 256 bytes of memory, from \$0040 to \$013F. This is shared with a 64 byte stack area. The stack begins at \$00FF and counts down to \$00C0.

*Note:* Using the stack area for data storage or temporary work locations requires care to prevent the data from being overwritten due to stacking from an interrupt or subroutine call.

# 4.3 ROM (MC68HC05BS8)

The user ROM consists of 10K-bytes of memory, from \$1800 to \$3FDF.

# 4.4 EPROM (MC68HC705BS8)

The user EPROM consists of 10K-bytes of memory, from \$1800 to \$3FDF.

MC68HC05BS8

## 4.5 EEPROM

The EEPROM consists of 512 bytes, from \$0200 to \$03FF. A charge pump is built on the chip for the operation of EEPROM. Programming and erasing are controlled by writing to the EEPROM Control register at address \$0007.

# 4.5.1 EEPROM Control Register

|       | Address | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | State<br>on reset |  |

|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------|--|

| EEPCR | \$0007  |       |       |       | EEOSC | EER1  | EER0  | EELAT | EEPGM | 0000 0000         |  |

### **EEOSC - EEPROM Charge Pump Oscillator Enable**

- (set) Internal oscillator turned on to clock the EEPROM charge pump. It requires a time t<sub>RCON</sub> to stabilize. (Min. 1μs).

- 0 (clear) Internal oscillator turned off. EEPROM charge pump clocked by internal bus clock.

### EER1, EER0 - EEPROM Erase Mode Select Bits

These two bits select one of the three erase modes. Refer to Table 4-1 below.

### Table 4-1 Erase Mode Select

| EER1 | EER0 | ERASE MODE                       |  |  |  |  |  |  |

|------|------|----------------------------------|--|--|--|--|--|--|

| 0    | 0    | No erase                         |  |  |  |  |  |  |

| 0    | 1    | Byte erase                       |  |  |  |  |  |  |

| 1    | 0    | Block erase (block 1 or block 2) |  |  |  |  |  |  |

| 1    | 1    | Bulk erase (block 1 and block 2) |  |  |  |  |  |  |

The EEPROM memory space is divided into two 256 byte blocks. Block 1 is located at address \$0200-\$02FF, and block 2 is located at \$0300-\$03FF. Providing the EELAT and EEPGM bits are "1", the EER1 and EER0 bits indicate whether the access to the EEPROM is for an erase or programming purpose. Block protect function applies on block 2 of the EEPROM memory space.

### **EELAT - EEPROM Programming Latch Control**

- 1 (set) EEPROM address and data bus configured for programming (writes to EEPROM cause address and data to be latched). EEPROM is in programming mode and cannot be read when this bit is set.

- 0 (clear) EEPROM address and data bus configured for normal reads. EER1, EER0, and EEPGM are forced to "0"s.

4-2

### **EEPGM - EEPROM Programming Power Enable**

- 1 (set) Programming power switched on to EEPROM array. If EELAT≠1 then EEPGM cannot be set.

- 0 (clear) Programming power switched off to EEPROM array.

## 4.5.2 EEPROM Options Register

|       | Address | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | State<br>on reset |

|-------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------|

| EEOPR | \$0200  |       |       |       |       |       |       | EEPRT | LVR   | unaffected        |

### EEPRT - EEPROM Protect

1 (set) – Block 2 (\$300-\$3FF) configured for read/write.

0 (clear) - Block 2 (\$300-\$3FF) configured for read only.

When this bit is erased to "1", writing to block 2 is not possible until the next external or power-on reset occurs.

### LVR - Low Voltage Reset

- 1 (set) Low voltage reset function is disabled.

- 0 (clear) Low voltage reset function is enabled.

This bit does not control any EEPROM operation, but enables/disables the LVR function. When enabled, and the MCU will reset if  $V_{DD}$  drops below  $V_{LVR}$ . When this bit is changed, its new value will have no effect until next external power-on reset.

### 4.5.3 Read Procedure

To read data from EEPROM, the EELAT bit must be cleared. EEPGM, EER1, and EER0 bits will be forced to zero. EEPROM is read as if it were normal ROM. The  $V_{PP}$  charge pump generator is off since EEPGM is zero. If a read is performed while ELAT is set, data will be read as \$FF.

# 4.5.4 Erase Procedure

There are three types of ERASE operation mode (see Table 4-1): byte erase, block erase, and bulk erase.

- 1) To perform byte erase operation, set EELAT=1, EER1=0, and EER0=1, write any data to the address to be erase, and set EEPGM for a time t<sub>EBYTE</sub>.

- To perform block erase operation, set EELAT=1, EER1=1, and EER0=0, write any data to any address in the block, and set EEPGM for a time t<sub>EBLOCK</sub>.

- To perform bulk erase operation, set EELAT=1, EER1=1, and EER0=0, write any data to any address in the EEPROM map, and set EEPGM for a time t<sub>EBULK</sub>.

- *Note:* Erase operation to any part of block 2 is not possible if the EEPRT bit is programmed to "0".

# 4.5.5 Programming Procedure

To program the content of EEPROM, set EELAT bits, write data to the desired address, and set the EEPGM bit. After the required programming delay  $t_{PROG}$ , EELAT must be cleared, which also resets EEPGM. During a programming operation, any access to the EEPROM will return \$FF. To program a second byte, EELAT must be cleared before it is set, or the programming will have no effect.

Figure 4-1 Memory Map

| Table 4-2 | Register | Outline |

|-----------|----------|---------|

|-----------|----------|---------|

| Register Name                  | Address | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | State<br>on reset |

|--------------------------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------|

| Port A data                    | \$0000  | PA7   | PA6   | PA5   | PA4   | PA3   | PA2   | PA1   | PA0   | unaffected        |

| Port B data                    | \$0001  | PB7   | PB6   | PB5   | PB4   | PB3   | PB2   | PB1   | PB0   | unaffected        |

| Port C data                    | \$0002  | PC7   | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   | unaffected        |

| Not used                       | \$0003  |       |       |       |       |       |       |       |       |                   |

| Port A data direction          | \$0004  | DDRA7 | DDRA6 | DDRA5 | DDRA4 | DDRA3 | DDRA2 | DDRA1 | DDRA0 | 0000 0000         |

| Port B data direction          | \$0005  | DDRB7 | DDRB6 | DDRB5 | DDRB4 | DDRB3 | DDRB2 | DDRB1 | DDRB0 | 0000 0000         |

| Port C data direction          | \$0006  | DDRC7 | DDRC6 | DDRC5 | DDRC4 | DDRC3 | DDRC2 | DDRC1 | DDRC0 | 0000 0000         |

| EEPROM control                 | \$0007  |       |       |       | EEOSC | EER1  | EER0  | EELAT | EEPGM | 0000 0000         |

| Core timer control and status  | \$0008  | CTOF  | RTIF  | CTOFE | RTIE  |       |       | RT1   | RT0   | 0000 0011         |

| Core timer                     | \$0009  | CT7   | CT6   | CT5   | CT4   | СТ3   | CT2   | CT1   | СТО   | 0000 0000         |

| Sync signal control and status | \$000A  | VPOL  | HPOL  | VDET  | HDET  | SOUT  | INSRT | SIN1  | SIN0  | 0000 0000         |

| Vfreq                          | \$000B  | VF7   | VF6   | VF5   | VF4   | VF3   | VF2   | VF1   | VF0   | 0000 0000         |

| Line frequency high            | \$000C  | VF8   |       |       |       | LF11  | LF10  | LF9   | LF8   | 0000 0000         |

| Line frequency low             | \$000D  | LF7   | LF6   | LF5   | LF4   | LF3   | LF2   | LF1   | LF0   | 0000 0000         |

| Interrupt line counter         | \$000E  | VSIE  | LC6   | LC5   | LC4   | LC3   | LC2   | LC1   | LC0   | 0000 0010         |

| Sampling pulse                 | \$000F  |       | SP6   | SP5   | SP4   | SP3   | SP2   | SP1   | SP0   | 0000 0010         |

| General PWM                    | \$0010  | ODE   | CRE   | GPW5  | GPW4  | GPW3  | GPW2  | GPW1  | GPW0  | 0000 0000         |

| Raster positioning PWM         | \$0011  | RSP   | RSPW6 | RSPW5 | RSPW4 | RSPW3 | RSPW2 | RSPW1 | RSPW0 | 0000 0000         |

| Timer control                  | \$0012  | ICIE  | OCIE  | TOIE  |       |       |       | IEDG  | OLVL  | 0000 00u1         |

| Timer status                   | \$0013  | ICF   | OCF   | TOF   |       |       |       |       |       | uuu0 0000         |

| Input capture high             | \$0014  | IC15  | IC14  | IC13  | IC12  | IC11  | IC10  | IC9   | IC8   | unaffected        |

| Input capture low              | \$0015  | IC7   | IC6   | IC5   | IC4   | IC3   | IC2   | IC1   | IC0   | unaffected        |

| Output compare high            | \$0016  | OC15  | OC14  | OC13  | OC12  | OC11  | OC10  | OC9   | OC8   | unaffected        |

| Output compare low             | \$0017  | 0C7   | OC6   | OC5   | OC4   | OC3   | OC2   | 0C1   | OC0   | unaffected        |

| Counter high                   | \$0018  | TC15  | TC14  | TC13  | TC12  | TC11  | TC10  | TC9   | TC8   | \$FF              |

| Counter low                    | \$0019  | TC7   | TC6   | TC5   | TC4   | TC3   | TC2   | TC1   | TC0   | \$FC              |

| Alternate counter high         | \$001A  | AC15  | AC14  | AC13  | AC12  | AC11  | AC10  | AC9   | AC8   | \$FF              |

| Alternate counter low          | \$001B  | AC7   | AC6   | CA5   | AC4   | AC3   | AC2   | AC1   | AC0   | \$FC              |

| EPROM programming control      | \$001C  |       |       | Rese  | erved |       |       | ELAT  | PGM   | 0000 0000         |

| Option                         | \$001D  | INTO  | COP   |       |       |       |       |       |       | 0100 0000         |

| Keyboard interrupt             | \$001E  |       | KBIC  | KBE5  | KBE4  | KBE3  | KBE2  | KBE1  | KBE0  | 0000 0000         |

| Not used                       | \$001F  |       |       |       |       |       |       |       |       |                   |

| Table 4-2 | Register Outline |

|-----------|------------------|

|-----------|------------------|

| Register Name           | Address                | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | State<br>on reset |

|-------------------------|------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------|

| Not used                | \$0020<br>to<br>\$0038 |       |       |       |       |       |       |       |       |                   |

| M-Bus address           | \$0039                 | MAD7  | MAD6  | MAD5  | MAD4  | MAD3  | MAD2  | MAD1  |       | 0000 000-         |

| M-Bus frequency divider | \$003A                 |       |       |       | FD4   | FD3   | FD2   | FD1   | FD0   | 0000 0000         |

| M-Bus control           | \$003B                 | MEN   | MIEN  | MSTA  | МТХ   | TXAK  |       | SIFC  | SIIC  | 0000 0000         |

| M-Bus status            | \$003C                 | MCF   | MASS  | MBB   | MAL   | SIF   | SRW   | MIF   | RXAK  | 1000 0001         |

| M-Bus data              | \$003D                 | MD7   | MD6   | MD5   | MD4   | MD3   | MD2   | MD1   | MD0   | undefined         |

| Not used                | \$003E                 |       |       |       |       |       |       |       |       |                   |

| Not used                | \$003F                 |       |       |       |       |       |       |       |       |                   |

| EEPROM options | \$0200 |  |  |  |  |  |  | EEPRT | LVR | unaffected |

|----------------|--------|--|--|--|--|--|--|-------|-----|------------|

|----------------|--------|--|--|--|--|--|--|-------|-----|------------|

# THIS PAGE LEFT BLANK INTENTIONALLY

# **5** RESETS AND INTERRUPTS

The section describes the reset and interrupt functions available on the MC68HC05BS8.

# 5.1 RESETS

The MC68HC05BS8 can be reset in four ways:

- by the initial power-on reset function, (POR)

- by an active low input to the RESET pin, (RESET)

- by a COP watchdog timer reset, (COPR)

- and by a Low Voltage Reset, (LVR)

Any of these resets will cause the program to go to its starting address, specified by the contents of memory locations \$3FFE and \$3FFF, and cause the interrupt mask (I-bit) of the Condition Code register to be set.

## 5.1.1 Power-On Reset (POR)

The power-on reset occurs when a positive transition is detected on the supply voltage,  $V_{DD}$ . The power-on reset is used strictly for power-up conditions, and should not be used to detect any drops in the power supply voltage. There is no provision for a power-down reset. The power-on circuitry provides for a 4064  $t_{CYC}$  delay from the time that the oscillator becomes active. If the external RESET pin is low at the end of the 4064  $t_{CYC}$  time out, the processor remains in the reset condition until RESET goes high. The user must ensure that  $V_{DD}$  has risen to a point where the MCU can operate properly prior to the time the 4064 POR cycles have elapsed. If there is doubt, the external RESET pin should remain low until such time that  $V_{DD}$  has risen to the minimum operating voltage specified.

# 5.1.2 RESET Pin

The  $\overline{\text{RESET}}$  input pin is used to reset the MCU to provide an orderly software start-up procedure. When using the external reset, the  $\overline{\text{RESET}}$  pin must stay low for a minimum of  $1.5t_{CYC}$ . The  $\overline{\text{RESET}}$  pin contains an internal Schmitt Trigger as part of its input to improve noise immunity.

2. Internal clock, internal address bus, and internal data bus signals are not available externally.

3. Next rising edge of internal clock after rising edge of RESET initiates reset sequence.

Figure 5-1 Power-On Reset and RESET Timing

# 5.1.3 Low Voltage Reset (LVR)

When the LVR function is enabled, an internal reset is generated if  $V_{DD}$  drops below  $V_{LVR}.$  (See Section 13 for value of  $V_{LVR}.)$

This LVR reset function is enabled/disabled by programming or erasing bit 0 in the EEPROM Options register (\$0200). Refer to Section 4.5.2.

# 5.1.4 Computer Operating Properly (COP) Reset

The MC68HC05BS8 contains a watchdog timer that automatically times out if this timer is not reset (cleared) within a specific amount of time by a program reset sequence.

*Note:* COP time-out is prevented by periodically writing a "0" to bit 0 of address \$3FF0.

If the watchdog timer is allowed to time-out, an internal reset is generated to reset the MCU. Because the internal reset signal is used, the MCU comes out of a COP reset in the same operating mode as it was in when the COP time-out was generated.

The COP reset function is enabled after a reset, and it can be disabled by writing a "0" to bit 6 in the Option register at address \$001D. Once disabled, it cannot be enabled except by a reset function.

See Section 6.2.3 for more information on the COP watchdog timer.

## 5.2 INTERRUPTS

The MC68HC05BS8 can be interrupted by different sources – six maskable hardware interrupt and one non-maskable software interrupt:

- Software Interrupt Instruction (SWI)

- External signal on the IRQ pin

- Sync Signal Processor (SSP)

- Programmable Timer (TIMER)

- Core Timer (CTIMER)

- M-Bus Interface (MBUS)

- Keyboard (KBI)

If the interrupt mask bit (I-bit) of the CCR is set, all maskable interrupts (internal and external) are disabled. Clearing the I-bit enables interrupts.

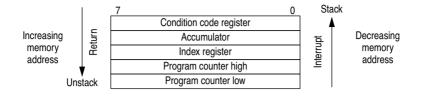

Interrupts cause the processor to save the register contents on the stack and to set the interrupt mask (I-bit) to prevent additional interrupts. The RTI instruction causes the register contents to be recovered from the stack and normal processing to resume.

Unlike reset, hardware interrupts do not cause the current instruction execution to be halted, but are considered pending until the current instruction is complete. The current instruction is the one already fetched and being operated on. When the current instruction is complete, the processor checks all pending hardware interrupts. If interrupts are not masked (CCR I-bit clear) the processor proceeds with interrupt processing; otherwise, the next instruction is fetched and executed. Table 5-1 shows the relative priority of all the possible interrupt sources.

#### **RESETS AND INTERRUPTS**

Figure 5-2 Interrupt Stacking Order

| Register | Flag Name | Interrupt                                                                         | CPU Interrupt | Vector Address              | Priority |

|----------|-----------|-----------------------------------------------------------------------------------|---------------|-----------------------------|----------|

| -        | -         | Reset                                                                             | RESET         | \$3FFE-\$3FFF               | highest  |

| -        | -         | Software                                                                          | SWI           | \$3FFC-\$3FFD               |          |

| -        | -         | External Interrupt                                                                | ĪRQ           | \$3FFA-\$3FFB               |          |

| SSCR     | -         | VSYNC                                                                             | SSP           | \$3FF8-\$3FF9               |          |

|          | TOF       | Timer Overflow                                                                    |               |                             |          |

| TSR      | OCF       | Output Compare                                                                    | TIMER         | \$3FF6-\$3FF7               |          |

|          | ICF       | Input Capture                                                                     |               |                             |          |

| CTCSR    | CTOF      | Core Timer Overflow                                                               | CTIMER        | \$3FF4-\$3FF5               |          |

| CICON    | RTIF      | Core Timer Interrupt                                                              |               | <b>0</b>                    |          |

| MSR      | MIF       | MiBuo                                                                             | MBUS          | \$3FF2-\$3FF3               | ]        |

| INIOR    | SIF       | VSYNC<br>Timer Overflow<br>Output Compare<br>Input Capture<br>Core Timer Overflow | WIBUS         | <b>₽3</b> ₽₽2 <b>-₽3₽₽3</b> |          |

| -        | -         | Keyboard                                                                          | KBI           | \$3FF0-\$3FF1               | lowest   |

# 5

MC68HC05BS8

## 5.2.1 Non-maskable Software Interrupt (SWI)

The software interrupt (SWI) is an executable instruction and a non-maskable interrupt: it is execute regardless of the state of the I-bit in the CCR. If the I-bit is zero (interrupt enabled), SWI is executed after interrupts that were pending when the SWI was fetched, but before interrupts generated after the SWI was fetched. The SWI interrupt service routine address is specified by the contents of memory locations \$3FFC and \$3FFD.

## 5.2.2 Maskable Hardware Interrupts

If the interrupt mask bit (I-bit) of the CCR is set, all maskable interrupts (internal and external) are masked. Clearing the I-bit allows interrupt processing to occur.

*Note:* The internal interrupt latch is cleared in the first part of the interrupt service routine; therefore, one external interrupt pulse could be latched and serviced as soon as the I-bit is cleared.

## 5.2.2.1 External Interrupt (IRQ)

The external interrupt  $\overline{IRQ}$  can be software configured for "negative-edge" or "negative-level" sensitive triggering by the INTO bit in the Option register.

|                 | Address | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | State<br>on reset |

|-----------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------|

| Option register | \$001D  | INTO  | COP   |       |       |       |       |       |       | 01                |

#### INTO

- 1 (set) Negative-edge sensitive triggering for IRQ.

- 0 (clear) Negative-level sensitive triggering for IRQ.

When the signal of the external interrupt pin,  $\overline{IRQ}$ , satisfies the condition selected, an external interrupt occurs. The actual processor interrupt is generated only if the interrupt mask bit of the condition code register is also cleared. When the interrupt is recognized, the current state of the processor is pushed onto the stack and the interrupt mask bit in the condition code register is set. This masks further interrupts until the present one is serviced. The service routine address is specified by the contents \$3FFA & \$3FFB.

The interrupt logic recognizes negative edge transitions and pulses (special case of negative edges) on the external interrupt line. Figure 5-3 shows both a block diagram and timing for the interrupt line ( $\overline{IRQ}$ ) to the processor. The first method is used if pulses on the interrupt line are spaced far enough apart to be serviced. The minimum time between pulses is equal to the number of cycles required to execute the interrupt service routine plus 21 cycles. Once a pulse occurs, the

#### **RESETS AND INTERRUPTS**

Figure 5-3 External Interrupt Circuit and Timing

next pulse should not occur until the MCU software has exited the routine (an RTI occurs). The second configuration shows several interrupt lines wired-OR to perform the interrupt at the processor. Thus, if the interrupt lines remain low after servicing one interrupt, the next interrupt is recognized.

*Note:* The internal interrupt latch is cleared in the first part of the service routine; therefore, one (and only one) external interrupt pulse could be latched during t<sub>ILIL</sub> and serviced as soon as the I-bit is cleared.

# 5.2.2.2 Sync Signal Processor Interrupt

The CPU will process an Sync Signal Processor VSYNC interrupt if the following conditions are satisfied:

- 1) the I-bit of the CCR is cleared,

- 2) the VSIE bit of the Interrupt Line Count register (ILCR) is set, and

- 3) the value of the horizontal line counter matches the value set in the ILCR.

This interrupt will vector to the interrupt service routine located at the address specified by the contents of \$3FF8 and \$3FF9. The VSYNC interrupt latch will be cleared automatically by fetching of these vectors.

Refer to Section 9 for detailed description of Sync Signal Processor.

## 5.2.2.3 M-Bus Interrupts

The hardware M-Bus interrupt is enabled when the M-Bus Interrupt Enable bit (MIEN) of M-Bus Control register is set, provided the interrupt mask bit of the Condition Code register is cleared. The interrupt service routine address is specified by the contents of memory location \$3FF2 and \$3FF3.

|                       | Address | bit 7 | bit 6 | bit 5 | bit 4 | bit 3 | bit 2 | bit 1 | bit 0 | State<br>on reset |   |

|-----------------------|---------|-------|-------|-------|-------|-------|-------|-------|-------|-------------------|---|

| M-Bus Status Register | \$001A  | MCF   | MAAS  | MBB   | MAL   | SIF   | SRW   | MIF   | RXAK  | 1000 0001         | ] |

#### **MIF - M-Bus Interrupt**

- 1 (set) An M-Bus interrupt has occurred.

- 0 (clear) An M-Bus interrupt has not occurred.

When this bit is set, an interrupt is generated to the CPU if MIEN is set. This bit is set when one of the following events occurs:

1) Completion of one byte of data transfer. It is set at the falling edge of the 9th clock - MCF set.

**.** . .

#### **RESETS AND INTERRUPTS**

- 2) A match of the calling address with its own specific address in slave mode MAAS set.

- 3) A loss of bus arbitration MAL set.

This bit must be cleared by software in the interrupt routine.

#### MCF - Data Transfer Complete

- 1 (set) A byte transfer has been completed.

- 0 (clear) A byte is being transfer.

#### **MAAS - Addressed as Slave**

- 1 (set) Currently addressed as a slave.

- 0 (clear) Not currently addressed.

Then CPU needs to check the SRW bit and set its MTX bit accordingly. Writing to the M-Bus Control register clears this bit.

#### **MAL - Arbitration Lost**

- 1 (set) Lost arbitration in master mode.

- 0 (clear) No arbitration lost.

#### SIF - Software M-Bus Interrupt