MC68HC05C9

# Addendum to MC68HC05C9 HCMOS Microcontroller Unit Technical Data

This addendum provides the following information:

- **CORRECTIONS/ADDITIONS** to the *MC68HC05C9 Technical Data* (Motorola document number MC68HC05C9/D);

- SECTION 15 ORDERING INFORMATION (replacement);

- **APPENDIX A**, containing data for the erasable, programmable, read-only memory (EPROM) version of the MC68HC05C9, the MC68HC705C9.

Specifications and information herein are subject to change without notice.

For More Information On This Product, Go to: www.freescale.com

Intentionally left blank

MC68HC05C9AD/D

## **Corrections/Additions** MC68HC05C9/D

Corrections and/or additions to MC68HC05C9 Technical Data are as follows:

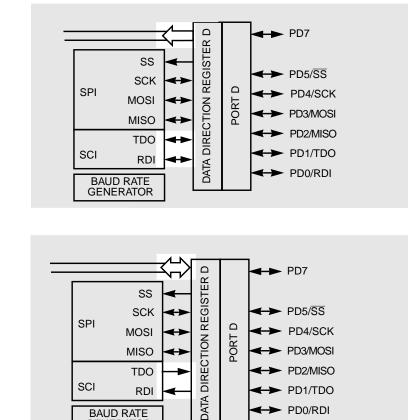

Page 1-3, Figure 1-2. MC68HC05C9 Block Diagram, correct Port D as follows:

From:

BAUD RATE GENERATOR

To:

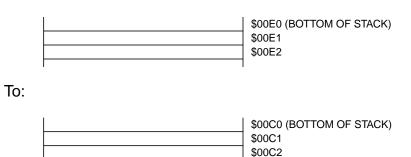

Page 3-3, **3.1.3 Stack Pointer**, from the second paragraph, correct as follows:

From: If subroutines and interrupts use more than 64 stack locations, the stack pointer wraps around to address \$00C0 and begins writing over the previously stored data.

PD0/RDI

To: If subroutines and interrupts use more than 64 stack locations, the stack pointer wraps around to address \$00FF and begins writing over the previously stored data.

MC68HC05C9AD/D

## Page 4-5, Figure 4-2. Interrupt Stacking Order, correct as follows:

From:

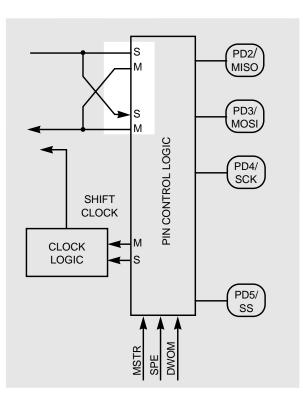

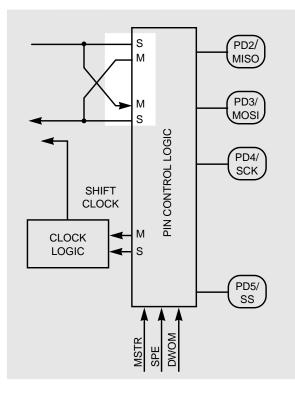

From:

MC68HC05C9AD/D

From:

To:

Page 12-9, **Table 12-7. Register/Memory Instructions**, add the following instruction:

EXCLUSIVE OR Accumulator with Memory Byte EOR

Page 12-10, **12.2.2. Read-Modify-Write Instructions**, add the following paragraph below the bulleted items:

For BSET and BCLR instructions, only direct addressing is valid. Also, because BSET and BCLR are read-modify-write instructions, they cannot be used with write-only registers. A read-modify-write operation will read undefined data, modify it as appropriate, and then write it back to the register. But because the original data is undefined, the data written back will be undefined.

Page 12-10, **Table 12-8. Read-Modify-Write Instructions**, add the following instructions:

| Clear Bit in Memory | BCLR |

|---------------------|------|

| Set Bit in Memory   | BSET |

MOTOROLA 6 MC68HC05C9AD/D

## Page 12-12, Table 12-11. Control Instructions, correct as follows:

From:

| Return from Subroutine | RTI |

|------------------------|-----|

To:

| Return from Interrupt  | RTI |

|------------------------|-----|

| Return from Subroutine | RTS |

Page 12-18, **Table 12-13. Opcode Map**, correct as follows (unshaded areas show corrections):

**Bit Manipulation**

To:

From:

Read-Modify-Write

From: To: From: To:

From: To:

| DIR                          | DIR                         | DIR                       | DIR                       | IX1               | IX1               | IX                       | IX                       |

|------------------------------|-----------------------------|---------------------------|---------------------------|-------------------|-------------------|--------------------------|--------------------------|

| HI 1                         | 1                           | 3                         | 3                         | 6                 | 6                 | 7                        | 7                        |

| LO 0001                      | 0001                        | 0011                      | 0011                      | 0110              | 0110              | 0111                     | 0111                     |

| 0 BSET0<br>0000 <u>2 DIR</u> | BSET0<br>2 DIR              | NEG <sup>5</sup><br>2 DIR | NEG<br>2 DIR              | NEG<br>2 IX1      | NEG<br>2 IX1      | NEG 5<br>1 IX            | NEG <sup>5</sup><br>1 IX |

| 1<br>0001 2 DIR              | BCLR0<br>2 DIR              |                           |                           |                   |                   |                          |                          |

| 2<br>0010 2 BSET1<br>2 DIR   | BSET1<br>2 DIR              |                           |                           |                   |                   |                          |                          |

| 3 BSCLR1<br>0011 2 DIR       | 5<br>BCLR1<br>2 DIR         | COM 2 DIR                 | COM<br>2 DIR              | 2 COM 6<br>2 IX1  | 2 COM 6<br>2 IX1  | COM 1 IX                 | COM 1 IX                 |

| 4<br>0100 2 DIR              | BSET2 <sup>5</sup><br>2 DIR | LSR<br>2 DIR              | LSR<br>2 DIR              | LSR<br>2 IX1      | 6<br>LSR<br>2 IX1 | LSR 5<br>1 IX            | LSR <sup>5</sup><br>1 IX |

| 5 BCLR2<br>0101 2 DIR        | BCLR2<br>2 DIR              |                           |                           |                   |                   |                          |                          |

| 6 BSET3<br>0110 2 DIR        | BSET3<br>2 DIR              | ROR 2 DIR                 | ROR<br>2 DIR              | 808<br>2 IX1      | 6<br>ROR<br>2 IX1 | ROR <sup>5</sup><br>1 IX | ROR 1 IX                 |

| 7<br>0111 2 BCLR3<br>2 DIR   | BCLR3<br>2 DIR              | ASR 2 DIR                 | ASR<br>2 DIR              | ASR 2 IX1         | 6<br>ASR<br>2 IX1 | ASR 5<br>1 IX            | ASR 5<br>1 IX            |

| 8<br>1000 <u>2 DIR</u>       | BSET4<br>2 DIR              | LSL<br>2 DIR              | 5<br>ASL/LSL<br>2 DIR     | 6<br>LSL<br>2 اX1 | ASL/LSL<br>2 IX1  | LSL 5<br>1 IX            | ASL/LSL<br>1 IX          |

| 9 BCLR4<br>1001 2 DIR        | 5<br>BCLR4<br>2 DIR         | ROL 2 DIR                 | ROL<br>2 DIR              | ROL               | 6<br>ROL<br>2 IX1 | ROL <sup>5</sup><br>1 IX | ROL <sup>5</sup><br>1 IX |

| A BSET5<br>1010 2 DIR        | BSET5<br>2 DIR              | DEC 2 DIR                 | DEC<br>2 DIR              | DEC               | DEC 6<br>2 IX1    | DEC 5<br>1 IX            | DEC <sup>5</sup><br>1 IX |

| B BCLR5<br>1011 2 DIR        | 5<br>BCLR5<br>2 DIR         |                           |                           |                   |                   |                          |                          |

| C BSET6<br>1100 2 DIR        | BSET6<br>2 DIR              | INC 2 DIR                 | INC<br>2 DIR              | INC<br>2 INH      | INC 2 IX1         | INC 5<br>1 IX            | INC 1 IX                 |

| D<br>BCLR6<br>1101 2 DIR     | BCLR6<br>2 DIR              | TST <sup>4</sup><br>2 DIR | TST <sup>4</sup><br>2 DIR | TST 6<br>2 INH    | 5<br>2 IX1        | TST 4<br>1 IX            | TST <sup>4</sup><br>1 IX |

| E BSET7<br>1110 2 DIR        | BSET7<br>2 DIR              |                           |                           |                   |                   |                          |                          |

| F 5<br>BCLR7<br>1111 2 DIR   | 5<br>BCLR7<br>2 DIR         | CLR<br>2 DIR              | CLR<br>2 DIR              | 6<br>CLR<br>2 INH | CLR<br>2 IX1      | CLR <sup>5</sup><br>1 IX | CLR <sup>5</sup><br>1 IX |

Page 13-10, **Table 13-6. Serial Peripheral Interface Timing (5.0 Vdc)**, correct reference at top of table as follows:

- From:  $V_{DD} = 5.0 \text{ Vdc} \pm 10\%$ ;  $V_{SS} = 0 \text{ Vdc}$ (Refer to Figures 13-11 and 13-12.)

- To:  $V_{DD} = 5.0 \text{ Vdc} \pm 10\%; V_{SS} = 0 \text{ Vdc}$ (Refer to Figures 13-9 and 13-10.)

Page 13-10, **Table 13-6. Serial Peripheral Interface Timing (5.0 Vdc)**, correct the SPI fall time as follows:

From:

13 Fall Time (20%

$$V_{DD}$$

to 20%  $V_{DD}$ ,  $C_L$  = 200 pF)

To:

| 13 | Fall Time (70% $V_{DD}$ to 20% $V_{DD}$ , $C_L$ = 200 pF) |  |  |

|----|-----------------------------------------------------------|--|--|

|    |                                                           |  |  |

Page 13-11, **Table 13-7. Serial Peripheral Interface Timing (3.3 Vdc)**, correct reference at top of table as follows:

- From:  $V_{DD} = 3.3 \text{ Vdc} \pm 10\%; V_{SS} = 0 \text{ Vdc}$ (Refer to Figures 13-11 and 13-12.)

- To:  $V_{DD} = 3.3 \text{ Vdc} \pm 0.3 \text{ Vdc}; V_{SS} = 0 \text{ Vdc}$ (Refer to Figures 13-9 and 13-10.)

Page 13-11, **Table 13-7. Serial Peripheral Interface Timing (3.3 Vdc)**, correct the SPI fall time as follows:

From:

| 13 | Fall Time (20% $V_{DD}$ to 20% $V_{DD}$ , C <sub>L</sub> = 200 pF) |  |  |

|----|--------------------------------------------------------------------|--|--|

|    |                                                                    |  |  |

To:

Page 13-12, a footnote has been added to **Figure 13-9. SPI Master Timing Diagram** figure title as follows:

From: Figure 13-9. SPI Master Timing Diagram

To: Figure 13-9. SPI Master Timing Diagram<sup>\*</sup>

<sup>\*</sup> Refer to **Table 13-6. Serial Peripheral Interface Timing (5.0 Vdc)** and **Table 13-7. Serial Peripheral Interface Timing (3.3 Vdc)** for the timing values corresponding to the circled numbers in the figure above.

Page 13-13, a footnote has been added to **Figure 13-10. SPI Master Timing Diagram** figure title as follows:

From: Figure 13-10. SPI Master Timing Diagram

To: Figure 13-10. SPI Master Timing Diagram<sup>\*</sup>

\* Refer to **Table 13-6. Serial Peripheral Interface Timing (5.0 Vdc)** and **Table 13-7. Serial Peripheral Interface Timing (3.3 Vdc)** for the timing values corresponding to the circled numbers in the figure above.

## SECTION 15 ORDERING INFORMATION

This section contains instructions for ordering custom-masked ROM MCUs.

## 15.1 MCU Ordering Forms

To initiate an order for a ROM-based MCU, first obtain the current ordering form for the MCU from a Motorola representative. Submit the following items when ordering MCUs:

- A current MCU ordering form that is **completely filled out** (Contact your Motorola sales office for assistance.)

- A copy of the customer specification if the customer specification deviates from the Motorola specification for the MCU

- Customer's application program on one of the media listed in 15.2 Application Program Media.

The current MCU ordering form is also available through the Motorola Freeware Bulletin Board Service (BBS). The telephone number is (512) 891-FREE. After making the connection, type bbs in lowercase letters. Then press the return key to start the BBS software.

### **15.2 Application Program Media**

Please deliver the application program to Motorola in one of the following media:

- Macintosh<sup>®1</sup> 3-1/2-inch diskette (double-sided 800K or double-sided high-density 1.4M)

- MS-DOS<sup>®2</sup> or PC-DOS<sup>™3</sup> 3-1/2-inch diskette (double-sided 720K or double-sided high-density 1.44M)

- MS-DOS<sup>®</sup> or PC-DOS<sup>™</sup> 5-1/4-inch diskette (double-sided double-density 360K or double-sided high-density 1.2M)

Use positive logic for data and addresses.

<sup>1.</sup> Macintosh is a registered trademark of Apple Computer, Inc.

<sup>2.</sup> MS-DOS is a registered trademark of Microsoft Corporation.

<sup>3.</sup> PC-DOS is a trademark of International Business Machines Corporation.

When submitting the application program on a diskette, clearly label the diskette with the following information:

- Customer name

- Customer part number

- Project or product name

- File name of object code

- Date

- · Name of operating system that formatted diskette

- Formatted capacity of diskette

On diskettes, the application program must be in Motorola's S-record format (S1 and S9 records), a character-based object file format generated by M6805 cross assemblers and linkers.

### NOTE

Begin the application program at the first user ROM location. Program addresses must correspond exactly to the available on-chip user ROM addresses as shown in the memory map. Write **\$00 in all non-user ROM locations or leave all non-user ROM locations blank**. Refer to the current MCU ordering form for additional requirements. Motorola may request pattern resubmission if non-user areas contain any non-zero code.

If the memory map has two user ROM areas with the same addresses, then write the two areas in separate files on the diskette. Label the diskette with both filenames.

In addition to the object code, a file containing the source code can be included. Motorola keeps this code confidential and uses it only to expedite ROM pattern generation in case of any difficulty with the object code. Label the diskette with the filename of the source code.

MOTOROLA 12

### **15.3 ROM Program Verification**

The primary use for the on-chip ROM is to hold the customer's application program. The customer develops and debugs the application program and then submits the MCU order along with the application program.

Motorola inputs the customer's application program code into a computer program that generates a listing verify file. The listing verify file represents the memory map of the MCU. The listing verify file contains the user ROM code and may also contain non-user ROM code, such as self-check code. Motorola sends the customer a computer printout of the listing verify file along with a listing verify form.

To aid the customer in checking the listing verify file, Motorola will program the listing verify file into customer-supplied blank preformatted Macintosh or DOS disks. All original pattern media are filed for contractual purposes and are not returned.

Check the listing verify file thoroughly, then complete and sign the listing verify form and return the listing verify form to Motorola. The signed listing verify form constitutes the contractual agreement for the creation of the custom mask.

### 15.4 ROM Verification Units (RVUs)

After receiving the signed listing verify form, Motorola manufactures a custom photographic mask. The mask contains the customer's application program and is used to process silicon wafers. The application program cannot be changed after the manufacture of the mask begins. Motorola then produces 10 MCUs, called RVUs, and sends the RVUs to the customer. RVUs are usually packaged in unmarked ceramic and tested to 5 Vdc at room temperature. RVUs are not tested to environmental extremes because their sole purpose is to demonstrate that the customer's user ROM pattern was properly implemented. The 10 RVUs are free of charge with the minimum order quantity. These units are not to be used for qualification or production. RVUs are not guaranteed by Motorola Quality Assurance.

### **15.5 MCU Order Numbers**

Table 15-1 shows the MCU order numbers for the available package types.

| Package Type                               | Operating<br>Temperature Range   | MC Order Number               |

|--------------------------------------------|----------------------------------|-------------------------------|

| 40-Pin Plastic Dual In-Line Package (PDIP) | 0 °C to 70 °C<br>–40 °C to 85 °C | MC68HC05C9P<br>MC68HC05C9CP   |

| 44-Lead Plastic-Leaded Chip Carrier (PLCC) | 0 °C to 70 °C<br>–40 °C to 85 °C | MC68HC05C9FN<br>MC68HC05C9CFN |

| 44-Pin Quad Flat Pack (QFP)                | 0 °C to 70 °C<br>–40 °C to 85 °C | MC68HC05C9FB<br>MC68HC05C9CFB |

| 42-Pin Shrink Dual In-Line Package (SDIP)  | 0 °C to 70 °C<br>–40 °C to 85 °C | MC68HC05C9B<br>MC68HC05C9CB   |

| Table 15-1. MCU Order Number |

|------------------------------|

|------------------------------|

NOTES:

P = Plastic dual-in-line package (PDIP)

FN = Plastic-leaded chip carrier (PLCC)

4. B = Shrink dual-in-line package (SDIP) 5. FB = Quad flat pack (QFP)

3. C = Extended temperature range (-40 to +85  $^{\circ}$ C)

### APPENDIX A MC68HC705C9

Appendix A introduces the MC68HC705C9, an erasable, programmable, readonly memory (EPROM) version of the MC68HC05C9. The technical data in *MC68HC05C9 Technical Data* applies to the MC68HC705C9 with the exceptions given in this appendix.

## A.1 GENERAL DESCRIPTION

### A.1.1 Features

- 15,932 Bytes of Erasable, Programmable, Read-Only Memory (EPROM)

- 240 Bytes of Bootstrap ROM

### A.1.2 Programmable Options

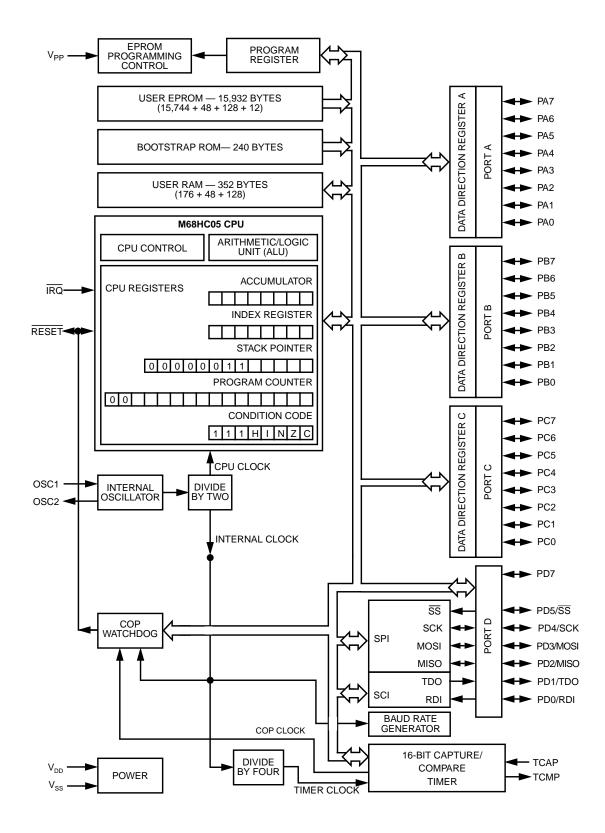

### A.1.3 Block Diagram

Figure A-2 shows the block diagram for the MC68HC705C9.

Figure A-2. MC68HC705C9 Block Diagram

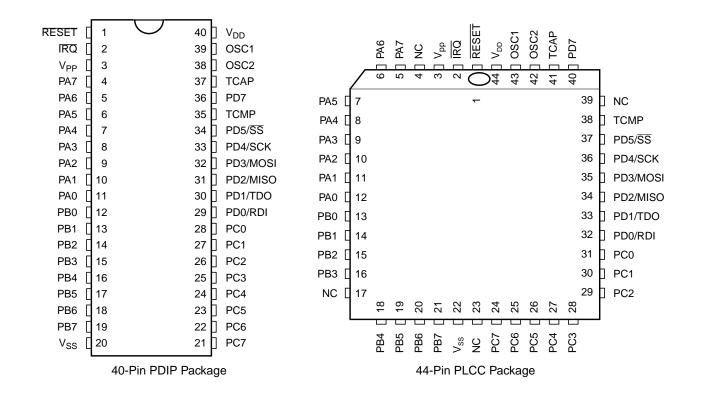

### A.1.4 Pin Assignments

The MC68HC705C9 is available in the plastic dual in-line package (PDIP) and plastic-leaded chip carrier (PLCC) packages. See **A.5 MECHANICAL SPECIFICATIONS**. Pin assignments are as follows:

Figure A-3. MC68HC705C9 Pin Assignments

## A.1.4.1 V<sub>PP</sub>

Programming power is supplied to the EPROM through the  $V_{PP}$  pin. The nominal programming voltage is 15 volts. The voltage level on the  $V_{PP}$  pin (pin 3), shown in Figure A-3, should never fall below  $V_{DD}$ .

## A.2 Memory

### A.2.1 Memory Map and Registers

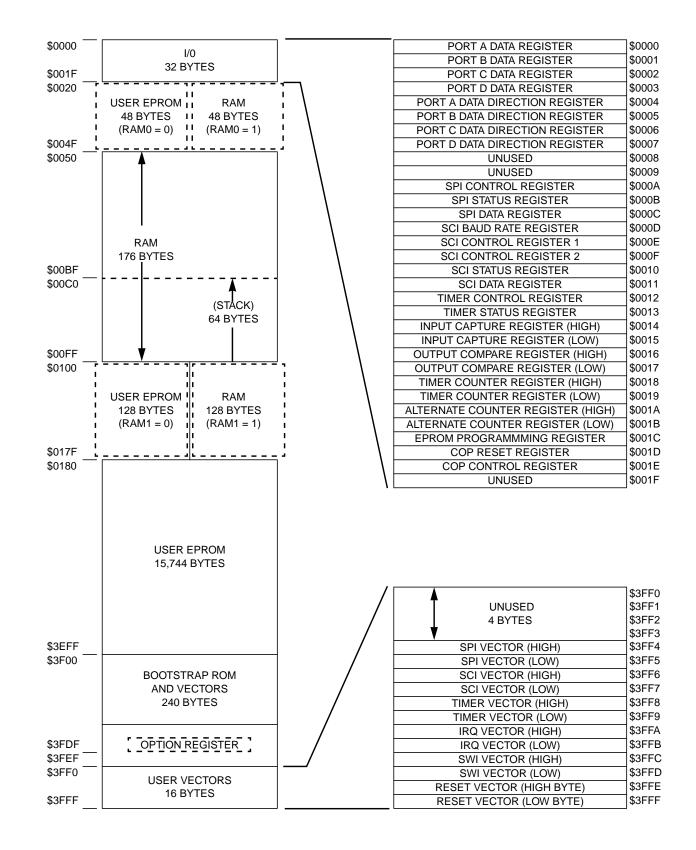

Figure A-4 is a memory map of the MC68HC705C9.

### Figure A-4. MC68HC705C9 Memory Map

MOTOROLA 18 MC68HC05C9AD/D

| \$0000 | PA7    | PA6   | PA5   | PA4   | PA3   | PA2   | PA1   | PA0   | Port A Data Register (PORTA)         |

|--------|--------|-------|-------|-------|-------|-------|-------|-------|--------------------------------------|

| \$0001 | PB7    | PB6   | PB5   | PB4   | PB3   | PB2   | PB1   | PB0   | Port B Data Register (PORTB)         |

| \$0002 | PC7    | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   | Port C Data Register (PORTC)         |

| \$0003 | PD7    |       | PD5   | PD4   | PD3   | PD2   | PD1   | PD0   | Port D Data Register (PORTD)         |

| \$0004 | DDRA7  | DDRA6 | DDRA5 | DDRA4 | DDRA3 | DDRA2 | DDRA1 | DDRA0 | Data Direction Register A (DDRA)     |

| \$0005 | DDRB7  | DDRB6 | DDRB5 | DDRB4 | DDRB3 | DDRB2 | DDRB1 | DDRB0 | Data Direction Register B (DDRB)     |

| \$0006 | DDRC7  | DDRC6 | DDRC5 | DDRC4 | DDRC3 | DDRC2 | DDRC1 | DDRC0 | Data Direction Register C (DDRC)     |

| \$0007 | DDRD7  |       | DDRD5 | DDRD4 | DDRD3 | DDRD2 | DDRD1 | DDRD0 | Data Direction Register D (DDRD)     |

| \$0008 |        |       |       |       |       |       |       |       | Unused                               |

| \$0009 |        |       |       |       |       |       |       |       | Unused                               |

| \$000A | SPIE   | SPE   | DWOM  | MSTR  | CPOL  | СРНА  | SPR1  | SPR2  | SPI Control Register (SPCR)          |

| \$000B | SPIF   | WCOL  |       | MODF  |       |       |       |       | SPI Status Register (SPSR)           |

| \$000C | SPD7   | SPD6  | SPD5  | SPD4  | SPD3  | SPD2  | SPD1  | SPD0  | SPI Data Register (SPDR)             |

| \$000D |        |       | SCP1  | SCP0  |       | SCR2  | SCR1  | SCR0  | SCI Baud Rate Register (BAUD)        |

| \$000E | R8     | Т8    |       | М     | WAKE  |       |       |       | SCI Control Register 1 (SCCR1)       |

| \$000F | TIE    | TCIE  | RIE   | ILIE  | TE    | RE    | RWU   | SBK   | SCI Control Register 2 (SCCR2)       |

| \$0010 | TDRE   | тс    | RDRF  | IDLE  | OR    | NF    | FE    |       | SCI Status Register (SCSR)           |

| \$0011 | SCD7   | SCD6  | SCD5  | SCD4  | SCD3  | SCD2  | SCD1  | SCD0  | SCI Data Register (SCDR)             |

| \$0012 | ICIE   | OCIE  | TOIE  | 0     | 0     | 0     | IEDG  | OLVL  | Timer Control Register (TCR)         |

| \$0013 | ICF    | OCF   | TOF   | 0     | 0     | 0     | 0     | 0     | Timer Status Register (TSR)          |

| \$0014 | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 | Input Capture Register High (ICRH)   |

| \$0015 | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 | Input Capture Register Low (ICRL)    |

| \$0016 | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 | Output Compare Register High (OCRH)  |

| \$0017 | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 | Output Compare Register Low (OCRL)   |

| \$0018 | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 | Timer Register High (TRH)            |

| \$0019 | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 | Timer Register Low (TRL)             |

| \$001A | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 | Alternate Timer Register High (ATRH) |

| \$001B | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 | Alternate Timer Register Low (ATRL)  |

| \$001C | 0      | 0     | LAT   | 0     | 0     | 0     | 0     | PGM   | Program Register (PROG)              |

| \$001D | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 | COP Reset Register (COPRST)          |

| \$001E |        |       |       | COPF  | CME   | COPE  | CM1   | CM0   | COP Control Register (COPCR)         |

| \$001F |        |       |       |       |       |       |       |       | Reserved                             |

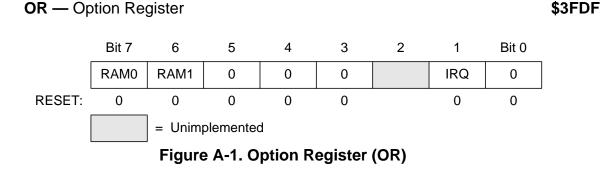

| \$3FDF | RAM0   | RAM1  | 0     | 0     | 0     |       | IRQ   | 0     | Option Register (OR)                 |

## Figure A-5. MC68HC705C9 Register and Control Bit Summary

MC68HC05C9AD/D

#### For More Information On This Product, Go to: www.freescale.com

### A.3 EPROM

This section describes how to program the MC68HC705C9.

### A.3.1 EPROM Programming

The EPROM can be programmed by either:

- Manipulating the control bits in the EPROM programming register to program the EPROM on a byte-by-byte basis;

- Activating the bootloader ROM to download the contents of an external memory to the on-chip EPROM.

## A.3.2 EPROM Program Register (PROG)

This read/write register, shown in Figure A-6, contains two bits used to control the programming of the EPROM bytes. This register is cleared on reset.

#### **PROG** — EPROM Program Register

#### \$001C

|        | Bit 7 | 6 | 5   | 4 | 3 | 2 | 1 | Bit 0 |

|--------|-------|---|-----|---|---|---|---|-------|

|        | 0     | 0 | LAT | 0 | 0 | 0 | 0 | PGM   |

| RESET: | 0     | 0 | 0   | 0 | 0 | 0 | 0 | 0     |

## Figure A-6. Programming Register

#### LAT – Latch Enable

This read/write bit controls the EPROM array's data and address bus latches to allow programming or normal CPU read operations.

- 1 = EPROM data and address bus latched for programming on the next byte write cycle

- 0 = EPROM data and address bus latched for normal CPU operations

#### PGM – Program

This read/write bit controls the application of the programming voltage  $V_{\text{PP}}$  to the EPROM array.

$$1 = V_{PP} \text{ on}$$

$$0 = V_{PP} \text{ off}$$

### NOTE

The PGM bit can be set only when the EPROM data and address buses are latched, that is, when LAT is set to ones.

Take the following steps to program a byte of EPROM:

- 1. Apply the programming voltage  $V_{\mbox{\tiny PP}}$  to the  $V_{\mbox{\tiny PP}}$  pin

- 2. Set the LAT bit

- 3. Write data to the EPROM address

- 4. Set the PGM bit for a time  $t_{PROG}$  to apply to the programming voltage

- 5. Clear the LAT bit

## CAUTION

The  $V_{PP}$  pin must be disconnected from  $V_{PP}$  (and connected to  $V_{DD}$  or left unconnected) before reading the contents of the EPROM.

## A.3.3 EPROM Erasing

The erased state of an EPROM byte is \$FF. EPROM devices can be erased by exposure to high-intensity ultraviolet (UV) light with a wavelength of 2537 Å. The recommended erasure dosage (UV intensity on a given surface area times exposure time) is 15 Ws/cm<sup>2</sup>. UV lamps should be used without shortwave filters, and the EPROM device should be positioned 2.5 cm from the UV source.

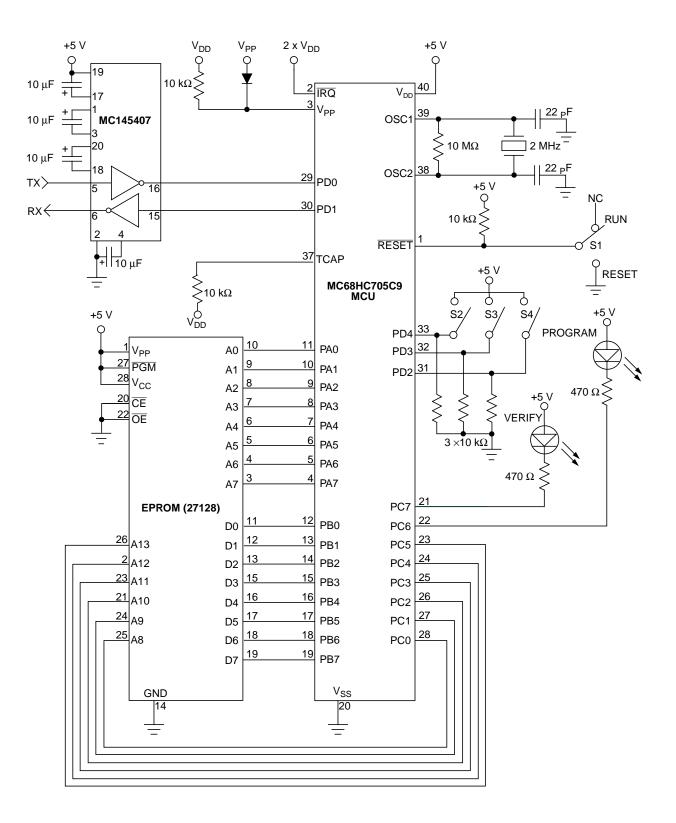

### A.3.4 Bootloader Mode

The bootloader ROM, located at addresses 3F00-3FEF, is selected by applying a voltage equal to two times  $V_{DD}$  to the IRQ pin during reset. The EPROM array is programmed using an industry-standard 16 Kbyte EPROM (27128) via the M68HC05 CPU and software in the on-board bootloader ROM. See **Figure A-7**. **Bootloader Circuit** for the recommended circuit diagram for the selfprogramming mode.

The following power-up sequence is essential:

With the MC68HC705C9 installed and the 27128 EPROM device installed in the programming board:

- 1. Apply the 5 volt supply

- 2. Apply the high voltage (2  $\times$  V<sub>DD</sub>) to  $\overline{IRQ}$

- 3. Apply the programming voltage to  $V_{PP}$

The above sequence must be reversed to power-down the device.

## NOTE

The erased state of the EPROM is \$FF.

The logical states of the PD2, PD3, and PD4 pins select the bootloader function, as Table A-1 shows.

| PD2 | PD3 | PD4 | Function               |

|-----|-----|-----|------------------------|

| 0   | 0   | 0   | Program and Verify     |

| 0   | 0   | 1   | Load RAM and Execute   |

| 0   | 1   | 0   | Verify Only            |

| 0   | 1   | 1   | Dump EPROM Contents    |

| 1   |     |     | Execute Program in RAM |

| Table A-1. Bootloader Fur | nction Selection |

|---------------------------|------------------|

|---------------------------|------------------|

Figure A-7. Bootloader Circuit

### A.3.5 Low Power Modes

In STOP mode, the resistor/capacitor (RC) oscillator in the EPROM array is switched off. In WAIT mode, however, the RC oscillator continues to operate, resulting in a higher WAIT  $I_{DD}$  than that of the ROM version, the MC68HC05C9.

### A.4 ELECTRICAL SPECIFICATIONS

### A.4.1 Maximum Ratings

This section contains electrical and timing specifications for the MC68HC705C9.

| Rating                                                                | Symbol          | Value                                                                                       | Unit   |

|-----------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------|--------|

| Supply Voltage                                                        | V <sub>DD</sub> | -0.3 to +7.0                                                                                | V      |

| Input Voltage<br>Normal Operation (Ports, OSC1)<br>IRQ and RESET      | V <sub>IN</sub> | $V_{SS} - 0.3 \text{ to } V_{DD} + 0.3$<br>$V_{SS} - 0.3 \text{ to } 2 \times V_{DD} + 0.3$ | V<br>V |

| Input Voltage<br>V <sub>PP</sub>                                      | V <sub>PP</sub> | $V_{SS}$ – 0.3 to 19                                                                        | V      |

| Storage Temperature Range                                             | T <sub>A</sub>  | -65 to +150                                                                                 | °C     |

| Current Drain Per Pin (Excluding $V_{DD}$ and $V_{SS}$ ) <sup>2</sup> | ۱ <sub>D</sub>  | 25                                                                                          | mA     |

Maximum values are not guaranteed operating values. All voltages are with respect to V<sub>ss</sub>.

Maximum drain per pin is for one pin at a time, limited by an external resistor.

## A.4.2 Thermal Characteristics

## Table A-3. Operating Temperature Range

| Rating                      | Symbol         | Value                                          | Unit |

|-----------------------------|----------------|------------------------------------------------|------|

| Operating Temperature Range | T <sub>A</sub> | Τ <sub>L</sub> to Τ <sub>H</sub><br>–40 to +85 | °C   |

## Table A-4. Thermal Characteristics

| Characteristic                                                                                  | Symbol | Value    | Unit |

|-------------------------------------------------------------------------------------------------|--------|----------|------|

| Thermal Resistance<br>Plastic Dual In-Line Package (PDIP)<br>Plastic-Leaded Chip Carrier (PLCC) | θJA    | 50<br>50 | °C/W |

## A.4.3 DC Electrical Characterics

$(V_{DD} = 5.0 \text{ Vdc} \pm 10\%, V_{SS} = 0, T_A = -40 \text{ to} + 85 \text{ }^{\circ}\text{C})$

**Table A-5. DC Electrical Characteristics**

| Characteristic                                                                                         | Symbol                              | Min                       | Typ <sup>1</sup> | Max                 | Unit           |

|--------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------|------------------|---------------------|----------------|

| Output Voltage<br>$I_{LOAD} = +25 \ \mu A$<br>$I_{LOAD} = -25 \ \mu A$                                 | V <sub>ol</sub><br>V <sub>oh</sub>  | <br>V <sub>DD</sub> – 0.1 |                  | 0.1                 | V<br>V         |

| Output High Voltage<br>I <sub>LOAD</sub> = -0.8 mA<br>PA7-PA0, PB7-PB0, PC7-PC0, PD7,<br>PD5-PD0, TCMP | V <sub>OH</sub>                     | V <sub>DD</sub> - 0.8     | _                | _                   | V              |

| Output Low Voltage<br>I <sub>LOAD</sub> = +1.6 mA<br>PA7–PA0, PB7–PB0, PC7–PC0, PD7,<br>PD5–PD0, TCMP  | V <sub>oL</sub>                     | _                         | _                | 0.4                 | V              |

| Input High Voltage<br>PA7–PA0, PB7–PB0, PC7–PC0, PD7,<br>PD5–PD0, IRQ, RESET, OSC1, TCAP               | V <sub>IH</sub>                     | $0.7 	imes V_{DD}$        | _                | _                   | V              |

| Input Low Voltage<br>PA7–PA0, PB7–PB0, PC7–PC0, PD7,<br>PD5–PD0, IRQ, RESET, OSC1, TCAP                | V <sub>IL</sub>                     | V <sub>SS</sub>           | _                | $0.2 \times V_{DD}$ | V              |

| Supply Current<br>Run <sup>2</sup><br>WAIT <sup>3</sup><br>STOP <sup>4</sup>                           | I <sub>DD</sub>                     |                           | 5.5<br>1<br>—    | 9.5<br>4.0<br>150   | mA<br>mA<br>μA |

| I/O Ports Hi-Z Leakage Current<br>PA7–PA0, PB7–PB0, PC7–PC0,<br>PD7, PD5–PD0                           | I <sub>IL</sub>                     | _                         | _                | ±10                 | μΑ             |

| Total Port B Sink Current to V <sub>SS</sub>                                                           | I <sub>ss</sub>                     | —                         | _                | 200                 | mA             |

| Data Retention Mode Voltage                                                                            | V <sub>RM</sub>                     | —                         | _                | 2.0                 | V              |

| Input Current<br>RESET, IRQ, TCAP, OSC1                                                                | I <sub>IN</sub>                     | —                         | _                | ±1                  | μA             |

| Capacitance<br>Ports (Input or Output)<br>RESET, IRQ                                                   | C <sub>OUT</sub><br>C <sub>IN</sub> | _                         | _                | 12<br>8             | pF<br>pF       |

1. Typical values reflect average measurements at midpoint of voltage range at 25 °C.

2. Run (operating)  $I_{DD}$  measured using external square wave clock source ( $f_{OSC}$  = 4.0 MHz) with all inputs 0.2 V from rail; no dc loads; less than 50 pF on all outputs;  $C_L$  = 20 pF on OSC2.

3. WAIT I<sub>DD</sub> measured using external square wave clock source ( $f_{OSC} = 4.0 \text{ MHz}$ ) with all inputs 0.2 V from rail; no dc loads; less than 50 pF on all outputs;  $C_L = 20 \text{ pF}$  on OSC2. All ports configured as inputs;  $V_{IL} = 0.2 \text{ V}$ ,  $V_{IH} = V_{DD} - 0.2 \text{ V}$ . Only the timer system active. OSC2 capacitance linearly affects WAIT I<sub>DD</sub>.

4. STOP I<sub>DD</sub> measured with OSC1 = V<sub>DD</sub>. All ports configured as inputs;  $V_{IL} = 0.2 \text{ V}$ ,  $V_{IH} = V_{DD} - 0.2 \text{ V}$ .

| Characteristic      | Symbol            | Min | Typ <sup>1</sup> | Max | Unit |

|---------------------|-------------------|-----|------------------|-----|------|

| EPROM               |                   |     |                  |     |      |

| Programming Voltage | V <sub>PP</sub>   | 15  | 15.5             | 16  | V    |

| Programming Current | I <sub>PP</sub>   | —   | 2                |     | mA   |

| Programming Time    | t <sub>PROG</sub> | 4   | —                | 20  | ms   |

| Table A-6. EPROM | <b>DC Electrical Charac</b> | teristics ( $T_A = 25 \circ C$ ) |

|------------------|-----------------------------|----------------------------------|

|                  |                             |                                  |

1. Typical values reflect average measurements at midpoint of voltage range at 25 °C.

## A.4.4 Control Timing

$(V_{DD} = 5.0 \text{ Vdc} \pm 10\%, V_{SS} = 0 \text{ Vdc}, T_A = -40 \text{ to } +85 \text{ °C.})$

| Characteristic                                                                   | Symbol                            | Min    | Max    | Unit             |

|----------------------------------------------------------------------------------|-----------------------------------|--------|--------|------------------|

| Oscillator Frequency<br>Crystal<br>External Clock                                | f <sub>osc</sub>                  | <br>dc | 4      | MHz<br>MHz       |

| Internal Operating Frequency (f <sub>OSC</sub> ÷ 2)<br>Crystal<br>External Clock | f <sub>OP</sub>                   | <br>dc | 2<br>2 | MHz<br>MHz       |

| Internal Clock Cycle Time                                                        | t <sub>CYC</sub>                  | 250    | _      | ns               |

| Crystal Oscillator Start-Up Time                                                 | t <sub>oxov</sub>                 | _      | 100    | ms               |

| RESET Pulse Width Low                                                            | t <sub>RL</sub>                   | 8      | _      | t <sub>CYC</sub> |

| Power-On Reset Delay                                                             | f <sub>PORL</sub>                 | 3968   | 3968   | t <sub>CYC</sub> |

| Interrupt Pulse Width Low (Edge-Triggered)                                       | t <sub>ILIH</sub>                 | 125    | _      | ns               |

| Interrupt Pulse Period                                                           | t <sub>ILIL</sub>                 | 1      | —      | t <sub>CYC</sub> |

| OSC1 Pulse Width                                                                 | t <sub>OH</sub> , t <sub>OL</sub> | 55     | _      | ns               |

### Table A-7. Control Timing

1. The minimum period  $t_{ILIL}$  should not be less than the number of cycles it takes to execute the interrupt service routine plus 21  $t_{CYC}$ .

#### NOTE

The MC68HC705C9 will operate down to dc. However, the power consumption of the EPROM is inversely proportional to frequency. Therefore, at frequencies below  $f_{OP} = 100$  kHz, the total power consumption may exceed the specification limits.

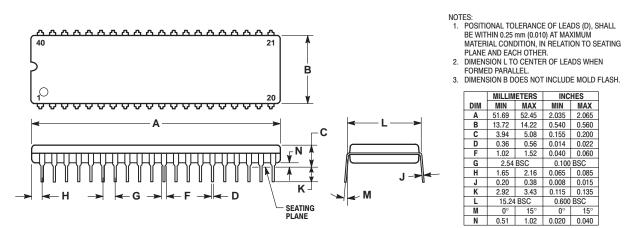

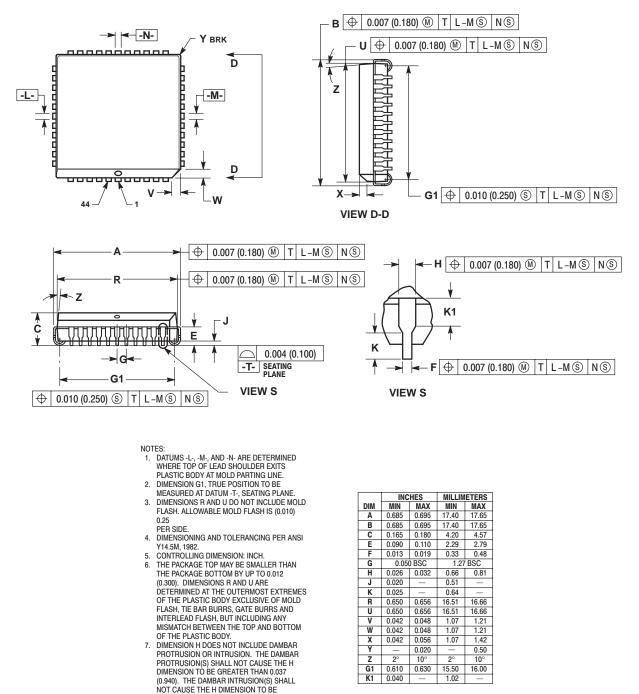

## A.5 MECHANICAL SPECIFICATIONS

This section describes the dimensions of the plastic dual-in-line package (PDIP) and plastic-leaded chip carrier package (PLCC).

## A.5.1 Plastic Dual-in-Line Package (PDIP)

Figure A-8. MC68HC705C9P (Case # 711-03)

## A.5.2 Plastic-Leaded Chip Carrier (PLCC)

Figure A-9. MC68HC705C9FN (Case # 777-02)

SMALLER THAN 0.025 (0.635).

Intentionally left blank

Home Page: www.freescale.com email: support@freescale.com **USA/Europe or Locations Not Listed:** Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 (800) 521-6274 480-768-2130 support@freescale.com Europe, Middle East, and Africa: Freescale Halbleiter Deutschland GmbH **Technical Information Center** Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com Japan: Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064, Japan 0120 191014 +81 2666 8080 support.japan@freescale.com Asia/Pacific: Freescale Semiconductor Hong Kong Ltd. **Technical Information Center** 2 Dai King Street Tai Po Industrial Estate, Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com For Literature Requests Only: Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 (800) 441-2447 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

RoHS-compliant and/or Pb- free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb- free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale.s Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.