#### Data Sheet Summary

MC68HC908JL8SM/D 3/2003

*MC68HC908JL8 MC68HC908JK8*

# **Freescale Semiconductor, Inc.**

#### Introduction

This document provides an overview of the MC68HC908JL8 and MC68HC908JK8 devices. For complete details refer to the *MC68HC908JL8 Data Sheet* (Motorola document order number MC68HC908JL8/D).

### **General Description**

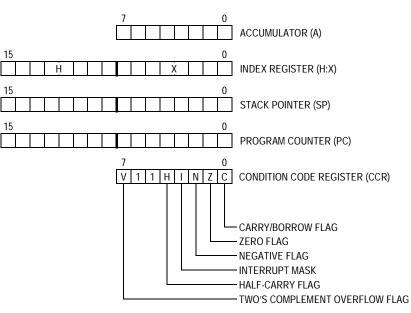

The MC68HC908JL8 is a member of the low-cost, high-performance M68HC08 Family of 8-bit microcontroller units (MCUs). The M68HC08 Family is a Complex Instruction Set Computer (CISC) with a Von Neumann architecture. All MCUs in the family use the enhanced M68HC08 central processor unit (CPU08) and are available with a variety of modules, memory sizes and types, and package types.

| MC Order Number | Operating Temperature Range | Package     |

|-----------------|-----------------------------|-------------|

| MC68HC908JK8CP  | −40 °C to +85 °C            | 20-pin PDIP |

| MC68HC908JK8MP  | −40 °C to +125 °C           | 20-ріпт Вії |

| MC68HC908JK8CDW | −40 °C to +85 °C            | 20-pin SOIC |

| MC68HC908JK8MDW | –40 °C to +125 °C           | 20-pin 3010 |

| MC68HC908JL8CP  | −40 °C to +85 °C            | 28-pin PDIP |

| MC68HC908JL8MP  | −40 °C to +125 °C           | 20-ріпт Вії |

| MC68HC908JL8CDW | −40 °C to +85 °C            | 28-pin SOIC |

| MC68HC908JL8MDW | –40 °C to +125 °C           | 28-pin 3010 |

| MC68HC908JL8CSP | −40 °C to +85 °C            | 32-pin SDIP |

| MC68HC908JL8MSP | –40 °C to +125 °C           | 52-pin SDIF |

| MC68HC908JL8CFA | −40 °C to +85 °C            | 32-pin LQFP |

| MC68HC908JL8MFA | –40 °C to +125 °C           |             |

#### Table 1. MC Order Numbers

### Features

Features include:

- High-performance M68HC08 architecture

- Fully upward-compatible object code with M6805, M146805, and M68HC05 Families

- Low-power design; fully static with stop and wait modes

- Maximum internal bus frequency:

- 8-MHz at 5V operating voltage

- 4-MHz at 3V operating voltage

- Oscillator options:

- Crystal or resonator

- RC oscillator

- 8,192 bytes user program FLASH memory with security<sup>(1)</sup> feature

- 256 bytes of on-chip RAM

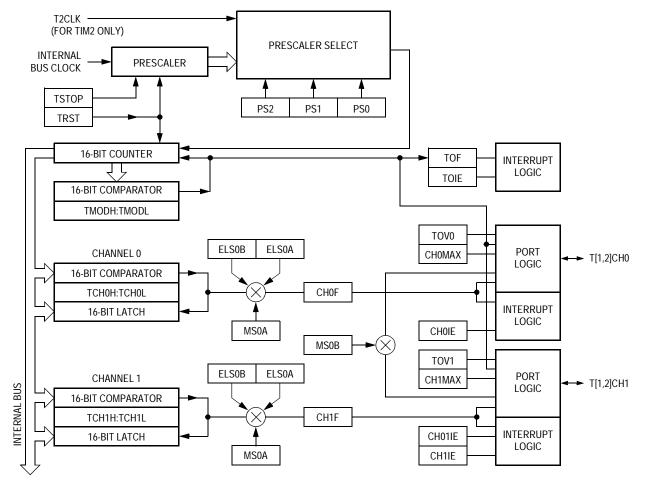

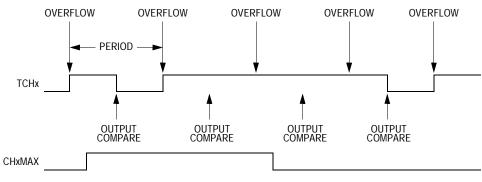

- Two 16-bit, 2-channel timer interface modules (TIM1 and TIM2) with selectable input capture, output compare, and PWM capability on each channel; external clock input option on TIM2

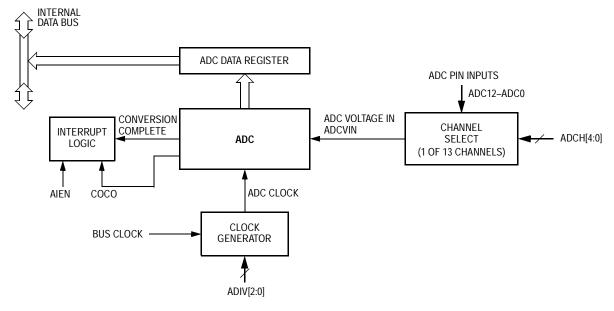

- 13-channel, 8-bit analog-to-digital converter (ADC)

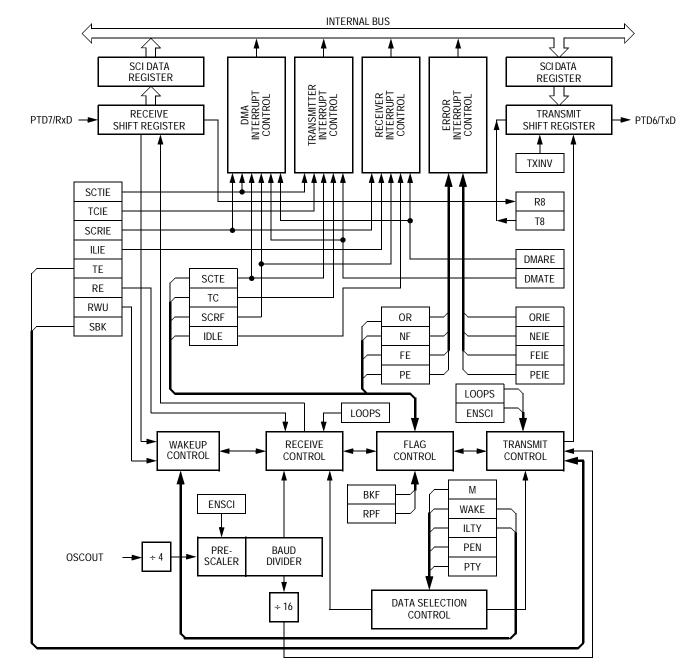

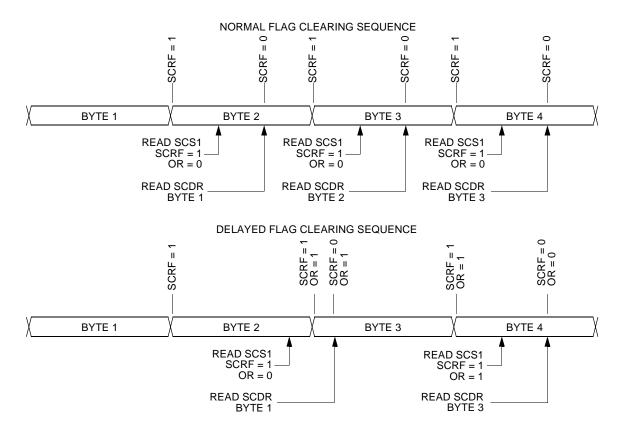

- Serial communications interface module (SCI)

- 26 general-purpose input/output (I/O) ports:

- 8 keyboard interrupt with internal pull-up

- 11 LED drivers (sink)

- $2 \times 25$ mA open-drain I/O with pull-up

- System protection features:

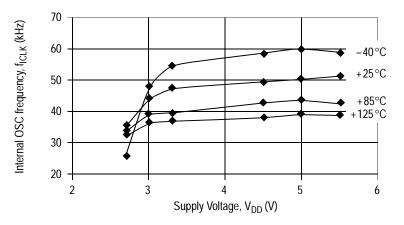

- Optional computer operating properly (COP) reset, driven by internal 64-kHz RC oscillator

- Optional low-voltage detection with reset and selectable trip points for 3V and 5V operation

- Illegal opcode detection with reset

- Illegal address detection with reset

- Master reset pin with internal pull-up and power-on reset

- IRQ with schmitt-trigger input and programmable pull-up

1. No security feature is absolutely secure. However, Motorola's strategy is to make reading or copying the FLASH difficult for unauthorized users.

- MC68HC908JL8 is available in these packages:

- 20-pin PDIP (MC68HC908JK8)

- 20-pin SOIC (MC68HC908JK8)

- 28-pin PDIP

- 28-pin SOIC

- 32-pin SDIP

- 32-pin LQFP

- Specific features of the MC68HC908JL8 in 28-pin packages are:

- 23 general-purpose I/Os only

- 7 keyboard interrupt with internal pull-up

- 10 LED drivers (sink)

- 12-channel ADC

- Timer I/O pins on TIM1 only

- Specific features of the MC68HC908JK8 are: (MC68HC908JL8 in 20-pin packages)

- 15 general-purpose I/Os only

- 1 keyboard interrupt with internal pull-up

- 4 LED drivers (sink)

- 10-channel ADC

- Timer I/O pins on TIM1 only

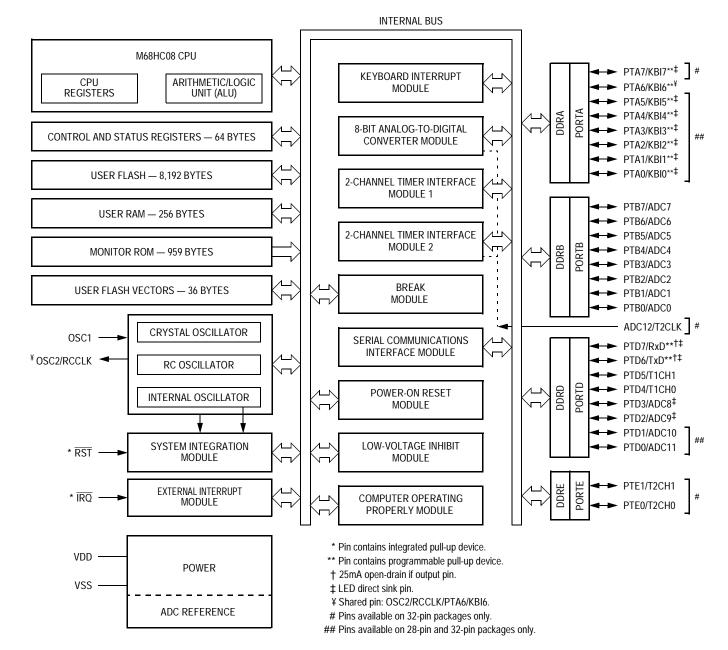

#### **MCU Block Diagram**

See Figure 1.

### Memory

The central processor unit (CPU08) can address 64 Kbytes of memory space. The memory map is shown in **Figure 3**.

Addresses \$0000–\$003F, shown in **Figure 4**, contain most of the control, status, and data registers.

The vector addresses are shown in Table 3.

Figure 1. Block Diagram

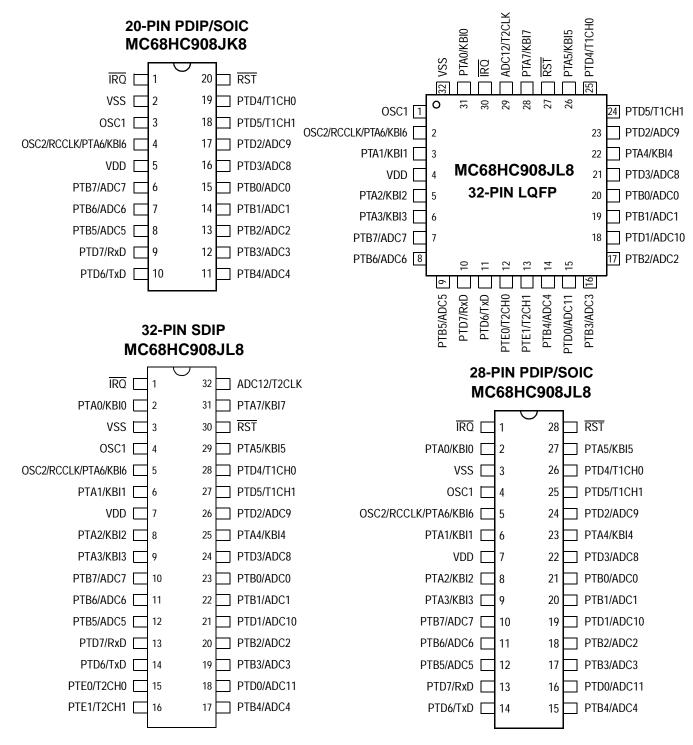

## **Pin Assignments**

Figure 2. MCU Pin Assignments

# **Pin Functions**

Table 2 provides a description of the pin functions.

### **Table 2. Pin Functions**

| PIN NAME    | PIN DESCRIPTION                                                                      | IN/OUT | VOLTAGE<br>LEVEL        |

|-------------|--------------------------------------------------------------------------------------|--------|-------------------------|

| VDD         | Power supply.                                                                        | In     | 5V or 3V                |

| VSS         | Power supply ground.                                                                 | Out    | 0V                      |

| RST         | Reset input, active low;<br>with internal pull-up and schmitt trigger input.         | In/Out | VDD                     |

| ĪRQ         | External IRQ pin; with programmable internal pull-up and schmitt trigger input.      | In     | VDD                     |

|             | Used for monitor mode entry.                                                         | In     | VDD to V <sub>TST</sub> |

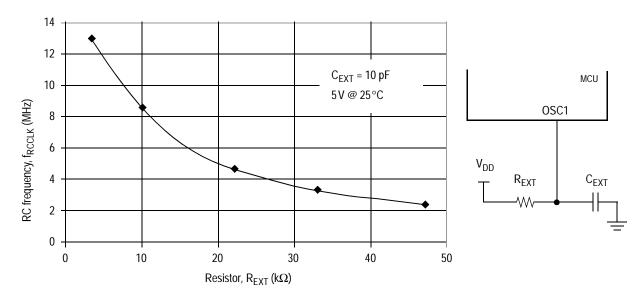

| OSC1        | Crystal or RC oscillator input.                                                      | In     | VDD                     |

|             | OSC2: crystal oscillator output; inverted OSC1 signal.                               | Out    | VDD                     |

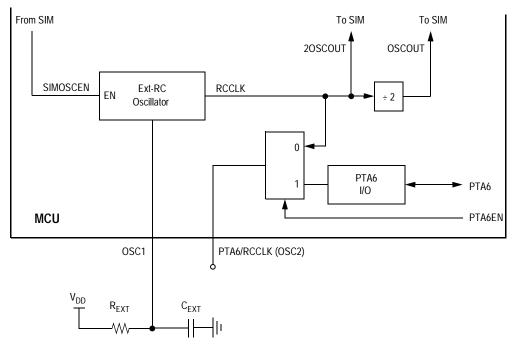

| OSC2/RCCLK  | RCCLK: RC oscillator clock output.                                                   | Out    | VDD                     |

|             | Pin as PTA6/KBI6 (see PTA0–PTA7).                                                    | In/Out | VDD                     |

|             | ADC12: channel-12 input of ADC.                                                      | In     | VSS to VDD              |

| ADC12/T2CLK | T2CLK: external input clock for TIM2.                                                | In     | VDD                     |

|             | 8-bit general purpose I/O port.                                                      | In/Out | VDD                     |

|             | Each pin has programmable internal pull-up when configured as input.                 | In     | VDD                     |

| PTA0-PTA7   | Pins as keyboard interrupts, KBI0–KBI7.                                              | In     | VDD                     |

|             | PTA0–PTA5 and PTA7 have LED direct sink capability.                                  | Out    | VSS                     |

|             | PTA6 as OSC2/RCCLK.                                                                  | Out    | VDD                     |

| PTB0-PTB7   | 8-bit general purpose I/O port.                                                      | In/Out | VDD                     |

| FIBU-FIBI   | Pins as ADC input channels, ADC0–ADC7.                                               | In     | VSS to VDD              |

|             | 8-bit general purpose I/O port;<br>with programmable internal pull-ups on PTD6–PTD7. | In/Out | VDD                     |

|             | PTD0–PTD3 as ADC input channels, ADC11–ADC8.                                         | Input  | VSS to VDD              |

|             | PTD2–PTD3 and PTD6–PTD7 have LED direct sink capability.                             | Out    | VSS                     |

| PTD0-PTD7   | PTD4 as T1CH0 of TIM1.                                                               | In/Out | VDD                     |

|             | PTD5 as T1CH1 of TIM1.                                                               | In/Out | VDD                     |

|             | PTD6–PTD7 have configurable 25mA open-drain output.                                  | Out    | VSS                     |

|             | PTD6 as TxD of SCI.                                                                  | Out    | VDD                     |

|             | PTD7 as RxD of SCI.                                                                  | In     | VDD                     |

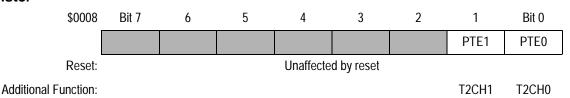

|             | 2-bit general purpose I/O port.                                                      | In/Out | VDD                     |

| PTE0-PTE1   | PTE0 as T2CH0 of TIM2.                                                               | In/Out | VDD                     |

|             | PTE1 as T2CH1 of TIM2.                                                               | In/Out | VDD                     |

| \$0000<br>↓ | I/O REGISTERS                              |

|-------------|--------------------------------------------|

| \$003F      | 64 BYTES                                   |

| \$0040<br>↓ | RESERVED                                   |

| \$005F      | 32 BYTES                                   |

| \$0060      | RAM                                        |

| ↓<br>\$015F | 256 BYTES                                  |

| \$0160      | UNIMPLEMENTED                              |

| ↓<br>\$DBFF | 55,968 BYTES                               |

| \$DC00      | FLASH MEMORY                               |

| ↓<br>\$FBFF | 8,192 BYTES                                |

| \$FC00      | MONITOR ROM                                |

| ↓<br>\$FDFF | 512 BYTES                                  |

| \$FE00      | BREAK STATUS REGISTER (BSR)                |

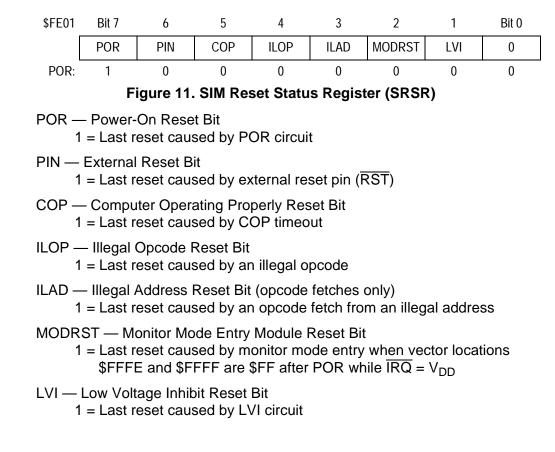

| \$FE01      | RESET STATUS REGISTER (RSR)                |

| \$FE02      | RESERVED                                   |

| \$FE03      | BREAK FLAG CONTROL REGISTER (BFCR)         |

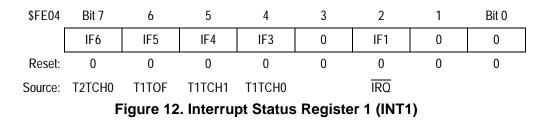

| \$FE04      | INTERRUPT STATUS REGISTER 1 (INT1)         |

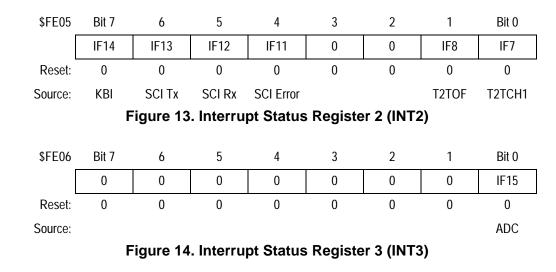

| \$FE05      | INTERRUPT STATUS REGISTER 2 (INT2)         |

| \$FE06      | INTERRUPT STATUS REGISTER 3 (INT3)         |

| \$FE07      | RESERVED                                   |

| \$FE08      | FLASH CONTROL REGISTER (FLCR)              |

| \$FE09<br>↓ | RESERVED                                   |

| \$FF0B      | NEOERVED                                   |

| \$FE0C      | BREAK ADDRESS HIGH REGISTER (BRKH)         |

| \$FE0D      | BREAK ADDRESS LOW REGISTER (BRKL)          |

| \$FE0E      | BREAK STATUS AND CONTROL REGISTER (BRKSCR) |

| \$FE0F      | RESERVED                                   |

| \$FE10<br>↓ | MONITOR ROM                                |

| \$FFCE      | 447 BYTES                                  |

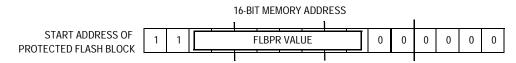

| \$FFCF      | FLASH BLOCK PROTECT REGISTER (FLBPR)       |

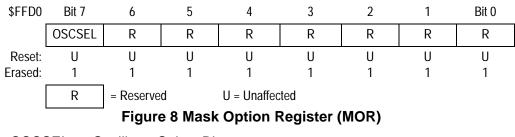

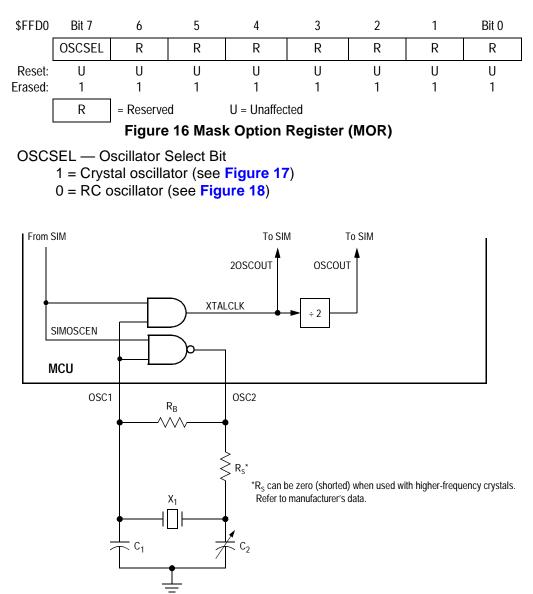

| \$FFD0      | MASK OPTION REGISTER (MOR)                 |

| \$FFD1<br>↓ | RESERVED                                   |

| ↓<br>\$FFDB | 11 BYTES                                   |

| \$FFDC      | USER FLASH VECTORS                         |

| ↓<br>\$FFFF | 36 BYTES                                   |

|             |                                            |

Figure 3. Memory Map

MC68HC908JL8SM/D

| Addr.   | Register      | Bit 7   | 6           | 5               | 4       | 3       | 2       | 1       | Bit 0        |

|---------|---------------|---------|-------------|-----------------|---------|---------|---------|---------|--------------|

| \$0000  | PTA           | PTA7    | PTA6        | PTA5            | PTA4    | PTA3    | PTA2    | PTA1    | PTA0         |

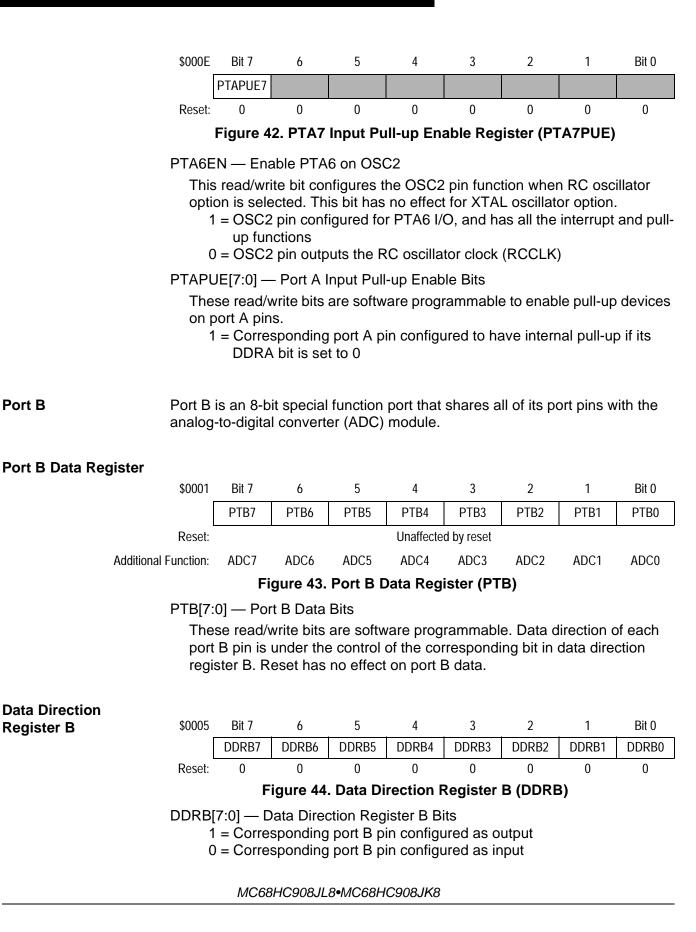

| \$0001  | PTB           | PTB7    | PTB6        | PTB5            | PTB4    | PTB3    | PTB2    | PTB1    | PTB0         |

| \$0002  | Unimplemented |         |             |                 |         |         |         |         |              |

| \$0003  | PTD           | PTD7    | PTD6        | PTD5            | PTD4    | PTD3    | PTD2    | PTD1    | PTD0         |

| \$0004  | DDRA          | DDRA7   | DDRA6       | DDRA5           | DDRA4   | DDRA3   | DDRA2   | DDRA1   | DDRA0        |

| \$0005  | DDRB          | DDRB7   | DDRB6       | DDRB5           | DDRB4   | DDRB3   | DDRB2   | DDRB1   | DDRB0        |

| \$0006  | Unimplemented |         |             |                 |         |         |         |         |              |

| \$0007  | DDRD          | DDRD7   | DDRD6       | DDRD5           | DDRD4   | DDRD3   | DDRD2   | DDRD1   | DDRD0        |

| \$0008  | PTE           |         |             |                 |         |         |         | PTE1    | PTE0         |

| \$0009  | Unimplemented |         |             |                 |         |         |         |         |              |

| \$000A  | PDCR          |         |             |                 |         | SLOWD7  | SLOWD6  | PTDPU7  | PTDPU6       |

| \$000B  | Unimplemented |         |             |                 |         |         |         |         |              |

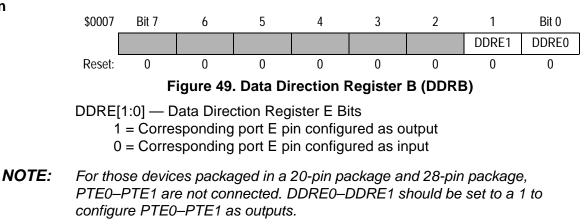

| \$000C  | DDRE          |         |             |                 |         |         |         | DDRE1   | DDRE0        |

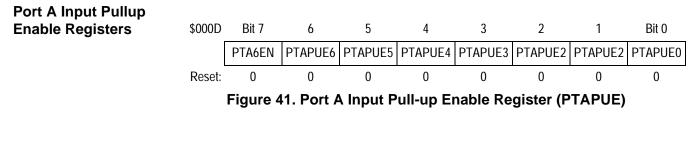

| \$000D  | PTAPUE        | PTA6EN  | PTAPUE6     | PTAPUE5         | PTAPUE4 | PTAPUE3 | PTAPUE2 | PTAPUE1 | PTAPUE0      |

| \$000E  | PTA7PUE       | PTAPUE7 |             |                 |         |         |         |         |              |

| \$000F- | Unimplemented |         |             |                 |         |         |         |         |              |

| \$0012  | Unimplemented |         |             |                 |         |         |         |         |              |

| \$0013  | SCC1          | LOOPS   | ENSCI       | TXINV           | М       | WAKE    | ILTY    | PEN     | PTY          |

| \$0014  | SCC2          | SCTIE   | TCIE        | SCRIE           | ILIE    | TE      | RE      | RWU     | SBK          |

| \$0015  | SCC3          | R8      | T8          | DMARE           | DMATE   | ORIE    | NEIE    | FEIE    | PEIE         |

| \$0016  | SCS1          | SCTE    | TC          | SCRF            | IDLE    | OR      | NF      | FE      | PE           |

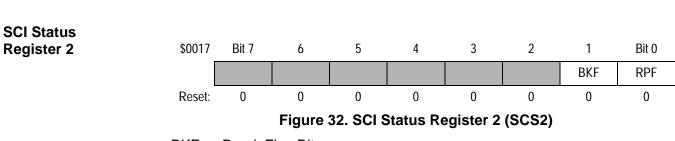

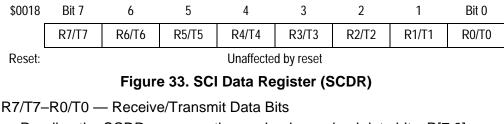

| \$0017  | SCS2          |         |             |                 |         |         |         | BKF     | RPF          |

| \$0018  | SCDR          | R7/T7   | R6/T6       | R5/T5           | R4/T4   | R3/T3   | R2/T2   | R1/T1   | R0/T0        |

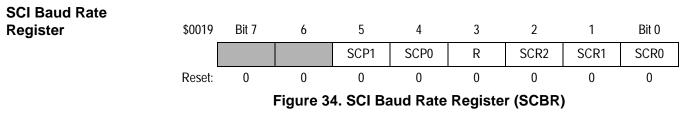

| \$0019  | SCBR          |         |             | SCP1            | SCP0    |         | SCR2    | SCR1    | SCR0         |

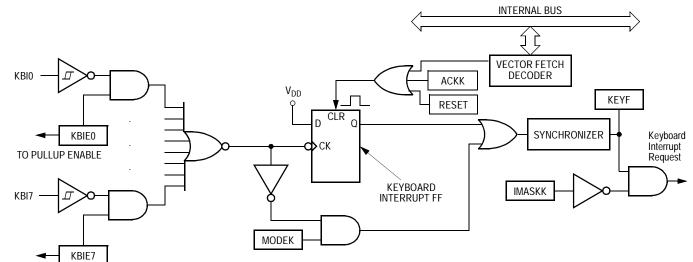

| \$001A  | KBSCR         |         |             |                 |         | KEYF    | ACKK    | IMASKK  | MODEK        |

| \$001B  | KBIER         | KBIE7   | KBIE6       | KBIE5           | KBIE4   | KBIE3   | KBIE2   | KBIE1   | KBIE0        |

| \$001C  | Unimplemented |         |             |                 |         |         |         |         |              |

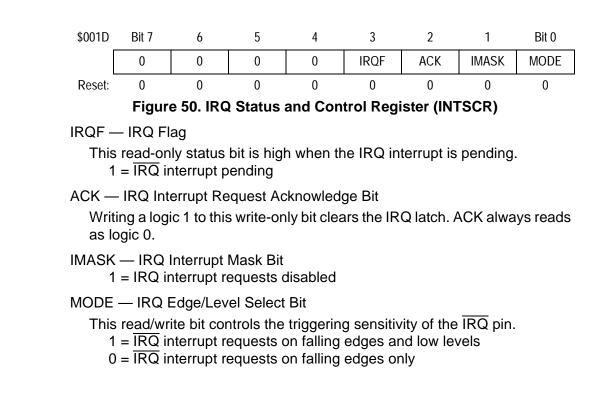

| \$001D  | INTSCR        |         |             |                 |         | IRQF    | АСК     | IMASK   | MODE         |

| \$001E  | CONFIG2       | IRQPUD  |             |                 | LVIT1   | LVIT0   |         |         | STOP_ICLKDIS |

| \$001F  | CONFIG1       | COPRS   |             |                 | LVID    | R       | SSREC   | STOP    | COPD         |

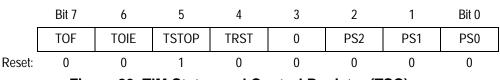

| \$0020  | T1SC          | TOF     | TOIE        | TSTOP           | TRST    | 0       | PS2     | PS1     | PS0          |

| \$0021  | T1CNTH        | Bit 15  | Bit 14      | Bit 13          | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8        |

| \$0022  | T1CNTL        | Bit 7   | Bit 6       | Bit 5           | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0        |

| \$0023  | T1MODH        | Bit 15  | Bit 14      | Bit 13          | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8        |

| \$0024  | T1MODL        | Bit 7   | Bit 6       | Bit 5           | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0        |

| \$0025  | T1SC0         | CH0F    | CHOIE       | MS0B            | MS0A    | ELS0B   | ELS0A   | TOV0    | CHOMAX       |

| \$0026  | T1CH0H        | Bit 15  | Bit 14      | Bit 13          | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8        |

| \$0027  | T1CH0L        | Bit 7   | Bit 6       | Bit 5           | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0        |

| \$0028  | T1SC1         | CH1F    | CH1IE       | 0               | MS1A    | ELS1B   | ELS1A   | TOV1    | CH1MAX       |

| \$0029  | T1CH1H        | Bit 15  | Bit 14      | Bit 13          | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8        |

| \$002A  | T1CH1L        | Bit 7   | Bit 6       | Bit 5           | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0        |

|         |               |         | = Unimpleme | ented or Reserv | ved     |         |         |         |              |

Figure 4. Control, Status, and Data Registers (Sheet 1 of 2)

| Addr.   | Register                      | Bit 7  | 6           | 5               | 4            | 3           | 2       | 1     | Bit 0  |

|---------|-------------------------------|--------|-------------|-----------------|--------------|-------------|---------|-------|--------|

| \$002B- | Unimplemented                 |        |             |                 |              |             |         |       |        |

| \$002F  | Unimplemented                 |        |             |                 |              |             |         |       |        |

| \$0030  | T2SC                          | TOF    | TOIE        | TSTOP           | TRST         | 0           | PS2     | PS1   | PS0    |

| \$0031  | T2CNTH                        | Bit 15 | Bit 14      | Bit 13          | Bit 12       | Bit 11      | Bit 10  | Bit 9 | Bit 8  |

| \$0032  | T2CNTL                        | Bit 7  | Bit 6       | Bit 5           | Bit 4        | Bit 3       | Bit 2   | Bit 1 | Bit 0  |

| \$0033  | T2MODH                        | Bit 15 | Bit 14      | Bit 13          | Bit 12       | Bit 11      | Bit 10  | Bit 9 | Bit 8  |

| \$0034  | T2MODL                        | Bit 7  | Bit 6       | Bit 5           | Bit 4        | Bit 3       | Bit 2   | Bit 1 | Bit 0  |

| \$0035  | T2SC0                         | CH0F   | CHOIE       | MS0B            | MS0A         | ELSOB       | ELS0A   | TOV0  | CHOMAX |

| \$0036  | T2CH0H                        | Bit 15 | Bit 14      | Bit 13          | Bit 12       | Bit 11      | Bit 10  | Bit 9 | Bit 8  |

| \$0037  | T2CH0L                        | Bit 7  | Bit 6       | Bit 5           | Bit 4        | Bit 3       | Bit 2   | Bit 1 | Bit 0  |

| \$0038  | T2SC1                         | CH1F   | CH1IE       | 0               | MS1A         | ELS1B       | ELS1A   | TOV1  | CH1MAX |

| \$0039  | T2CH1H                        | Bit 15 | Bit 14      | Bit 13          | Bit 12       | Bit 11      | Bit 10  | Bit 9 | Bit 8  |

| \$003A  | T2CH1L                        | Bit 7  | Bit 6       | Bit 5           | Bit 4        | Bit 3       | Bit 2   | Bit 1 | Bit 0  |

| \$003B  | Unimplemented                 |        |             |                 |              |             |         |       |        |

| \$0038  | OSCTRIM                       | TRIM7  | TRIM6       | TRIM5           | TRIM4        | TRIM3       | TRIM2   | TRIM1 | TRIM0  |

| \$003C  | ADSCR                         | C0C0   | AIEN        | ADCO            | ADCH4        | ADCH3       | ADCH2   | ADCH1 | ADCH0  |

| \$003D  | ADR                           | AD7    | AD6         | AD5             | AD4          | AD3         | AD2     | AD1   | AD0    |

| \$003E  | ADICLK                        | ADIV2  | ADIV1       | ADIV0           | 0            | 0           | 0       | 0     | 0      |

| \$003F  | Unimplemented                 |        |             |                 |              |             |         |       |        |

| \$FE00  | BSR                           |        |             |                 |              |             |         | SBSW  |        |

| \$FE01  | RSR                           | POR    | PIN         | СОР             | ILOP         | ILAD        | MODRST  | LVI   | 0      |

| \$FE02  | Reserved                      |        |             |                 |              |             |         |       |        |

| \$FE03  | BFCR                          | BCFE   |             |                 |              |             |         |       |        |

| \$FE04  | INT1                          | IF6    | IF5         | IF4             | IF3          | 0           | IF1     | 0     | 0      |

| \$FE05  | INT2                          | IF14   | IF13        | IF12            | IF11         | 0           | 0       | IF8   | IF7    |

| \$FE06  | INT3                          | 0      | 0           | 0               | 0            | 0           | 0       | 0     | IF15   |

| \$FE07  | Reserved                      |        |             |                 |              |             |         |       |        |

| \$FE08  | FLCR                          | 0      | 0           | 0               | 0            | HVEN        | MASS    | ERASE | PGM    |

| \$FE09- | Reserved                      |        |             |                 |              |             |         |       |        |

| \$FE0B  | Reserved                      |        |             |                 |              |             |         |       |        |

| \$FE0C  | BRKH                          | Bit 15 | Bit 14      | Bit 13          | Bit 12       | Bit 11      | Bit 10  | Bit 9 | Bit 8  |

| \$FE0D  | BRKL                          | Bit 7  | Bit 6       | Bit 5           | Bit 4        | Bit 3       | Bit 2   | Bit 1 | Bit 0  |

| \$FE0E  | BRKSCR                        | BRKE   | BRKA        | 0               | 0            | 0           | 0       | 0     | 0      |

| \$FFCF  | FLBPR (non-volatile register) | BPR7   | BPR6        | BPR5            | BPR4         | BPR3        | BPR2    | BPR1  | BPR0   |

| \$FFD0  | MOR (non-volatile register)   | OSCSEL |             |                 |              |             |         |       |        |

| \$FFFF  | COPCTL                        |        |             | WRITE AN        | Y VALUE TO F | RESET COP W | ATCHDOG | •     | •      |

|         |                               |        | = Unimpleme | ented or Reserv | ed           |             |         |       |        |

Figure 4. Control, Status, and Data Registers (Sheet 2 of 2)

| Lowest         IF16         —         Not used           IF15         \$FFDE         ADC conversion complete vector (high)           IF14         \$FFDE         ADC conversion complete vector (low)           IF14         \$FFE0         Keyboard vector (high)           IF14         \$FFE1         Keyboard vector (low)           IF13         \$FFE2         SCI transmit vector (low)           IF12         \$FFE3         SCI transmit vector (low)           IF12         \$FFE6         SCI receive vector (low)           IF11         \$FFE7         SCI error vector (low)           IF11         \$FFE7         SCI error vector (low)           IF11         \$FFE7         SCI error vector (low)           IF10 and IF9         —         Not used           IF7         \$FFE7         TIM2 overflow vector (low)           IF7         \$FFE7         TIM2 channel 1 vector (low)           IF6         \$FFF7         TIM1 overflow vector (low)           IF5         \$FFF3         TIM1 overflow vector (low)           IF3         \$FFF6         TIM2 channel 1 vector (low)           IF4         \$FFF7         \$FFF7           IF4         \$FFF7         TIM1 overflow vector (low)           IF3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       | 100          |         | Addresses                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--------------|---------|---------------------------------------|

| LowestIF15\$FFDEADC conversion complete vector (high)IF14\$FFDFADC conversion complete vector (low)IF14\$FFE0Keyboard vector (low)IF13\$FFE2SCI transmit vector (low)IF13\$FFE3SCI transmit vector (low)IF12\$FFE4SCI receive vector (high)IF12\$FFE5SCI receive vector (high)IF11\$FFE6SCI receive vector (high)IF11\$FFE6SCI error vector (high)IF11\$FFE7SCI error vector (high)IF11\$FFE6SCI error vector (high)IF11\$FFE7SCI error vector (high)IF11\$FFE6SCI error vector (high)IF11\$FFE7SCI error vector (high)IF11\$FFE6TIM2 overflow vector (high)IF11\$FFE7SCI error vector (high)IF7\$FFE6TIM2 channel 1 vector (high)IF7\$FFE7TIM2 channel 1 vector (high)IF6\$FFF7TIM2 channel 0 vector (high)IF5\$FFF3TIM1 overflow vector (high)IF4\$FFF4TIM1 channel 1 vector (high)IF3\$FFF6TIM1 channel 0 vector (high)IF1\$FFF8IRQ vector (high)IF1\$FFF8IRQ vector (high)IF1\$FFF9SWI vector (high)IF1\$FFF0SWI vector (high)\$FFF0SWI vector (high)\$FFF0SWI vector (high)\$FFF0SWI vector (high)\$FFF0SWI vector (high)\$FFF0SW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Vector Priority                       |              | Address | Vector                                |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Lowost                                | IF16         | —       | Not used                              |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Lowest                                | 1515         | \$FFDE  | ADC conversion complete vector (high) |

| IF14       \$FFE1       Keyboard vector (low)         IF13       \$FFE2       SCI transmit vector (high)         IF13       \$FFE3       SCI transmit vector (low)         IF12       \$FFE4       SCI receive vector (high)         IF11       \$FFE6       SCI erceive vector (low)         IF10 and IF9       —       Not used         IF8       \$FFE7       SCI ercor vector (high)         IF8       \$FFE0       TIM2 overflow vector (high)         IF7       \$FFEF       TIM2 channel 1 vector (low)         IF6       \$FFF6       TIM2 channel 0 vector (high)         IF5       \$FFF7       TIM1 channel 0 vector (high)         IF4       \$FFF3       TIM1 channel 1 vector (low)         IF3       \$FFF6       TIM1 channel 1 vector (high)         IF2       —       Not used         IF1       \$FFF6       TIM1 channel 0 vector (high)         IF2       —       Not used         IF2       —       Not used         IF1       \$FFFA       IRQ vector (high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                     | 1115         | \$FFDF  | ADC conversion complete vector (low)  |

| $ \begin{array}{ c c c c c c } & $FFE1 & Keyboard vector (low) \\ \hline & $FFE3 & SCI transmit vector (high) \\ \hline & $FFE3 & SCI transmit vector (low) \\ \hline & $FFE3 & SCI receive vector (low) \\ \hline & $FFE5 & SCI receive vector (low) \\ \hline & $FFE6 & SCI error vector (low) \\ \hline & $FFE7 & SCI error vector (low) \\ \hline & $FFE7 & SCI error vector (low) \\ \hline & $FFE7 & SCI error vector (low) \\ \hline & $FFE7 & SCI error vector (low) \\ \hline & $FFE7 & SCI error vector (low) \\ \hline & $FFE7 & SCI error vector (low) \\ \hline & $FFE7 & SCI error vector (low) \\ \hline & $FFE7 & SCI error vector (low) \\ \hline & $FFE7 & SCI error vector (low) \\ \hline & $FFE7 & SCI error vector (low) \\ \hline & $FFE7 & SCI error vector (low) \\ \hline & $FFF6 & TIM2 overflow vector (low) \\ \hline & $FFF6 & TIM2 channel 1 vector (low) \\ \hline & $FFF7 & TIM2 channel 1 vector (low) \\ \hline & $FFF7 & TIM2 channel 0 vector (low) \\ \hline & $FFF7 & SFF73 & TIM1 overflow vector (low) \\ \hline & $FFF7 & SFF73 & TIM1 overflow vector (low) \\ \hline & $FF75 & SFF73 & TIM1 overflow vector (low) \\ \hline & $FF75 & SFF75 & TIM1 channel 1 vector (low) \\ \hline & $FF76 & TIM1 channel 1 vector (low) \\ \hline & $FF77 & TIM1 channel 1 vector (low) \\ \hline & $FF77 & TIM1 channel 0 vector (low) \\ \hline & $FF76 & SFF76 & TIM1 channel 0 vector (low) \\ \hline & $FF76 & SFF76 & TIM1 channel 0 vector (low) \\ \hline & $FF77 & TIM1 channel 0 vector (low) \\ \hline & $FF76 & SFF77 & TIM1 channel 0 vector (low) \\ \hline & $FF76 & SFF76 & TIM2 channel 0 vector (low) \\ \hline & $FF77 & SF77 & TIM1 channel 0 vector (low) \\ \hline & $FF76 & SWI vector (low) \\ \hline & $FF77 & SF77 & STM1 channel 0 vector (low) \\ \hline & $FF77 & SF77 & STM1 channel 0 vector (low) \\ \hline & $FF77 & SF77 & STM1 channel 0 vector (low) \\ \hline & $FF77 & SF77 & STM1 channel 0 vector (low) \\ \hline & $FF77 & SF77 & STM1 channel 0 vector (low) \\ \hline & $FF77 & SF77 & STM1 channel 0 vector (low) \\ \hline & $FF77 & SF77 & STM1 channel 0 vector (low) \\ \hline & $FF77 & SF77 & STM1 channel 0 vector (low) \\ \hline & $FF77 & SF77 & STM1 channel 0 vector (low) \\ \hline & $FF77 & SF77 & STM1 channel 0 vector (low) \\ \hline & $FF77 & SF77 & STM1 channel 0 vector (low) \\ \hline & $FF77 & SF77 & STM1 channel 0 vect$                                                                                                                                                                         |                                       |              | \$FFE0  | Keyboard vector (high)                |

| IF13       \$FFE3       SCI transmit vector (low)         IF12       \$FFE4       SCI receive vector (high)         IF12       \$FFE5       SCI receive vector (low)         IF11       \$FFE6       SCI error vector (low)         IF11       \$FFE7       SCI error vector (low)         IF10 and IF9       —       Not used         IF8       \$FFE7       SCI error vector (low)         IF8       \$FFE7       TIM2 overflow vector (high)         IF7       \$FFE6       TIM2 channel 1 vector (low)         IF6       \$FFF6       TIM2 channel 0 vector (low)         IF6       \$FFF7       TIM2 channel 0 vector (low)         IF5       \$FFF3       TIM1 overflow vector (low)         IF4       \$FFF6       TIM1 channel 1 vector (low)         IF2       —       Not used         IF1       \$FFF6       TIM1 channel 0 vector (low)         IF2       —       Not used         IF1       \$FFF6       TIM1 channel 0 vector (low)         IF2       —       Not used      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                       | 1614         | \$FFE1  | Keyboard vector (low)                 |

| $ \begin{array}{ c c c c c c } & $FFE3 & SCI transmit vector (low) \\ \hline & $FFE4 & SCI receive vector (high) \\ \hline & $FFE5 & SCI receive vector (low) \\ \hline & $FFE5 & SCI error vector (low) \\ \hline & $FFE6 & SCI error vector (low) \\ \hline & $FFE7 & SCI error vector (low) \\ \hline & $FFE7 & SCI error vector (low) \\ \hline & $FFE7 & SCI error vector (low) \\ \hline & $FFE0 & TIM2 overflow vector (high) \\ \hline & $FFED & TIM2 overflow vector (high) \\ \hline & $FFEF & TIM2 channel 1 vector (high) \\ \hline & $FFFF & TIM2 channel 1 vector (low) \\ \hline & $FFF6 & TIM2 channel 0 vector (high) \\ \hline & $FFF7 & TIM2 channel 0 vector (high) \\ \hline & $FFF7 & TIM2 channel 0 vector (high) \\ \hline & $FFF7 & TIM2 channel 0 vector (high) \\ \hline & $FFF7 & TIM2 channel 0 vector (high) \\ \hline & $FFF7 & TIM1 overflow vector (high) \\ \hline & $FFF7 & TIM1 channel 1 vector (high) \\ \hline & $FFF7 & TIM1 channel 1 vector (high) \\ \hline & $FFF6 & TIM1 channel 1 vector (high) \\ \hline & $FFF7 & TIM1 channel 0 vector (high) \\ \hline & $FFF7 & TIM1 channel 0 vector (high) \\ \hline & $FFF6 & TIM1 channel 0 vector (high) \\ \hline & $FFF6 & TIM2 channel 0 vector (high) \\ \hline & $FFF6 & TIM1 channel 0 vector (high) \\ \hline & $FFF6 & TIM2 channel 0 vector (high) \\ \hline & $FFF6 & SFF7 & TIM1 channel 0 vector (high) \\ \hline & $FFF6 & SFF7 & TIM1 channel 0 vector (high) \\ \hline & $FFF6 & SFF7 & TIM1 channel 0 vector (high) \\ \hline & $FFF6 & SFF7 & SWI vector (high) \\ \hline & $FFF6 & SWI ve$                                                                                                                               |                                       | 1512         | \$FFE2  | SCI transmit vector (high)            |

| IF12       \$FFE5       SCI receive vector (low)         IF11       \$FFE6       SCI error vector (high)         IF11       \$FFE7       SCI error vector (low)         IF10 and IF9       —       Not used         IF8       \$FFEC       TIM2 overflow vector (high)         IF7       \$FFEE       TIM2 overflow vector (low)         IF7       \$FFEE       TIM2 channel 1 vector (high)         IF6       \$FFFF       TIM2 channel 1 vector (low)         IF6       \$FFF7       TIM2 channel 0 vector (high)         IF5       \$FFF2       TIM1 overflow vector (low)         IF5       \$FFF3       TIM1 overflow vector (low)         IF4       \$FFF6       TIM1 channel 1 vector (high)         IF3       \$FFF6       TIM1 channel 1 vector (low)         IF2       —       Not used         IF1       \$FFF6       TIM1 channel 0 vector (low)         IF2       —       Not used         IF1       \$FFFA       IRQ vector (high)         \$FFFB       IRQ vector (high)       \$FFFFB         SFFFD       \$WI vector (low)       \$FFFFE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       | IFIS         | \$FFE3  | SCI transmit vector (low)             |

| $ \begin{array}{ c c c c c } & \$FFE5 & SCI receive vector (low) \\ \hline & \$FFE6 & SCI error vector (high) \\ \hline & \$FFE7 & SCI error vector (low) \\ \hline & \$FFE7 & SCI error vector (low) \\ \hline & \$FFE7 & SCI error vector (low) \\ \hline & \$FFE0 & TIM2 overflow vector (high) \\ \hline & \$FFED & TIM2 overflow vector (low) \\ \hline & \$FFEE & TIM2 channel 1 vector (high) \\ \hline & \$FFEF & TIM2 channel 1 vector (low) \\ \hline & \$FFEF & TIM2 channel 0 vector (high) \\ \hline & \$FFF6 & TIM2 channel 0 vector (high) \\ \hline & \$FFF7 & TIM2 channel 0 vector (high) \\ \hline & \$FFF7 & TIM2 channel 0 vector (high) \\ \hline & \$FFF7 & TIM2 channel 0 vector (high) \\ \hline & \$FFF7 & TIM1 overflow vector (high) \\ \hline & \$FFF5 & TIM1 overflow vector (high) \\ \hline & \$FFF5 & TIM1 channel 1 vector (high) \\ \hline & \$FFF5 & TIM1 channel 1 vector (high) \\ \hline & \$FFF7 & TIM1 channel 0 vector (high) \\ \hline & \$FFF7 & TIM1 channel 0 vector (high) \\ \hline & \$FFF7 & TIM1 channel 0 vector (high) \\ \hline & \$FFF7 & TIM1 channel 0 vector (high) \\ \hline & \$FFF7 & TIM1 channel 0 vector (high) \\ \hline & \$FFF7 & TIM1 channel 0 vector (high) \\ \hline & \$FFF7 & TIM1 channel 0 vector (high) \\ \hline & \$FFF7 & TIM1 channel 0 vector (high) \\ \hline & \$FFF7 & TIM2 channel 0 vector (high) \\ \hline & \$FFF7 & TIM2 channel 0 vector (high) \\ \hline & \$FFF7 & TIM2 channel 0 vector (high) \\ \hline & \$FFF7 & TIM2 channel 0 vector (high) \\ \hline & \$FFF7 & TIM2 channel 0 vector (high) \\ \hline & \$FFF7 & TIM2 channel 0 vector (high) \\ \hline & \$FFF7 & TIM2 channel 0 vector (high) \\ \hline & \$FFF7 & TIM2 channel 0 vector (high) \\ \hline & \$FFF7 & TIM2 channel 0 vector (high) \\ \hline & \$FFF7 & TIM2 channel 0 vector (high) \\ \hline & \$FFF7 & TIM2 channel 0 vector (high) \\ \hline & \$FFF7 & $FFF6 & $IRQ vector (high) \\ \hline & \$FFF7 & $FFF6 & $IRQ vector (high) \\ \hline & \$FFF7 & $FFF0 & $WI vector (high) \\ \hline & \$FFF7 & $FFF6 & $FFF6 & $WI vector (high) \\ \hline & \$FFF7 & $FFF6 & $WI vector (high) \\ \hline & \$FFF7 & $FFF6 & $WI vector (high) \\ \hline & \$FFF7 & $FFF6 & $WI vector (high) \\ \hline & \$FFF7 & $FFF6 & $WI vector (high) \\ \hline & \$FFF7 & $FFF6 & $WI vector (high) \\ \hline & \$FFF7 & $FFF6 & $WI vector (high) \\ \hline & \$FFF7 & $FFF6 & $WI vector (high) \\ \hline & \$FFF6 & $FFF6 & $W$                                                                                                            |                                       | 1540         | \$FFE4  | SCI receive vector (high)             |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       | IF IZ        | \$FFE5  | SCI receive vector (low)              |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | 1544         | \$FFE6  | SCI error vector (high)               |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | 1611         | \$FFE7  | SCI error vector (low)                |

| IF8       \$FFED       TIM2 overflow vector (low)         IF7       \$FFEE       TIM2 channel 1 vector (high)         IF6       \$FFEF       TIM2 channel 1 vector (low)         IF6       \$FFF0       TIM2 channel 0 vector (high)         IF5       \$FFF1       TIM2 channel 0 vector (high)         IF5       \$FFF2       TIM1 overflow vector (high)         IF4       \$FFF5       TIM1 overflow vector (low)         IF3       \$FFF6       TIM1 channel 1 vector (high)         IF2       -       Not used         IF1       \$FFF6       TIM1 channel 0 vector (high)         IF2       -       Not used         IF1       \$FFF6       SWI vector (high)         SFFF0       SWI vector (low)       \$FFF6         IF1       \$FFF6       SFFF0         \$FFF6       SWI vector (high)       \$SFFF0         SFFF0       SWI vector (high)       \$SFFF0         SFFF0       SWI vector (high)       \$SFFF0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       | IF10 and IF9 | —       | Not used                              |

| IF7       \$FFED       TIM2 overflow vector (low)         IF7       \$FFEE       TIM2 channel 1 vector (high)         IF6       \$FFF0       TIM2 channel 0 vector (high)         IF6       \$FFF1       TIM2 channel 0 vector (high)         IF5       \$FFF2       TIM1 overflow vector (low)         IF4       \$FFF3       TIM1 overflow vector (low)         IF3       \$FFF6       TIM1 channel 1 vector (low)         IF2       —       Not used         IF1       \$FFFA       IRQ vector (high)         \$FFFB       IRQ vector (low)         IF1       \$FFFC         \$FFFD       \$WI vector (high)         \$FFFD       \$WI vector (high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | 150          | \$FFEC  | TIM2 overflow vector (high)           |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       | IF8          | \$FFED  | TIM2 overflow vector (low)            |

| $\frac{  F }{ F } = \frac{ F E }{ F E } = \frac{ F E }{ F E$ |                                       |              | \$FFEE  | TIM2 channel 1 vector (high)          |

| IF6       \$FFF1       TIM2 channel 0 vector (low)         IF5       \$FFF2       TIM1 overflow vector (high)         IF4       \$FFF3       TIM1 overflow vector (low)         IF4       \$FFF4       TIM1 channel 1 vector (high)         IF3       \$FFF6       TIM1 channel 0 vector (high)         IF2       -       Not used         IF1       \$FFF7       TIM1 channel 0 vector (high)         \$FFF8       IRQ vector (high)         \$FFF9       SFFF0         SFFF0       \$WI vector (high)         \$FFF0       \$WI vector (high)         \$FFF5       \$WI vector (high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | IF /         | \$FFEF  | TIM2 channel 1 vector (low)           |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | 150          | \$FFF0  | TIM2 channel 0 vector (high)          |

| IF5       \$FFF3       TIM1 overflow vector (low)         IF4       \$FFF4       TIM1 channel 1 vector (high)         IF3       \$FFF5       TIM1 channel 1 vector (low)         IF3       \$FFF6       TIM1 channel 0 vector (low)         IF2       -       Not used         IF1       \$FFFA       IRQ vector (high)         \$FFFB       IRQ vector (low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       | IFO          | \$FFF1  | TIM2 channel 0 vector (low)           |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |              | \$FFF2  | TIM1 overflow vector (high)           |

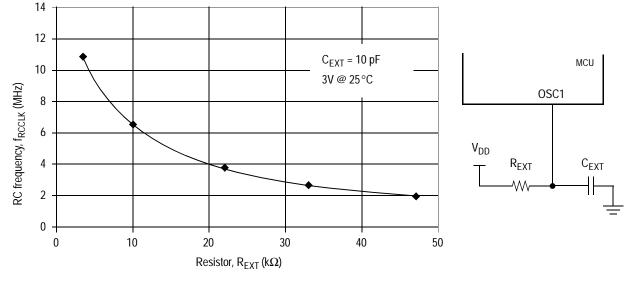

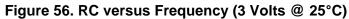

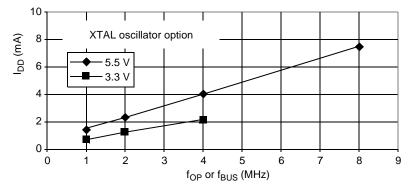

| IF4     \$FFF5     TIM1 channel 1 vector (low)       IF3     \$FFF6     TIM1 channel 0 vector (high)       IF3     \$FFF7     TIM1 channel 0 vector (low)       IF2     -     Not used       IF1     \$FFFA     IRQ vector (high)       \$FFFB     IRQ vector (low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       | IFD          | \$FFF3  | TIM1 overflow vector (low)            |