#### Advance Information

MC71000TB/D Rev. 2, 8/2002

MC71000 Bluetooth Baseband Controller

#### **Freescale Semiconductor, Inc.**

**ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005**

**MOTOROLA** intelligence everywhere digital dna

MC71000

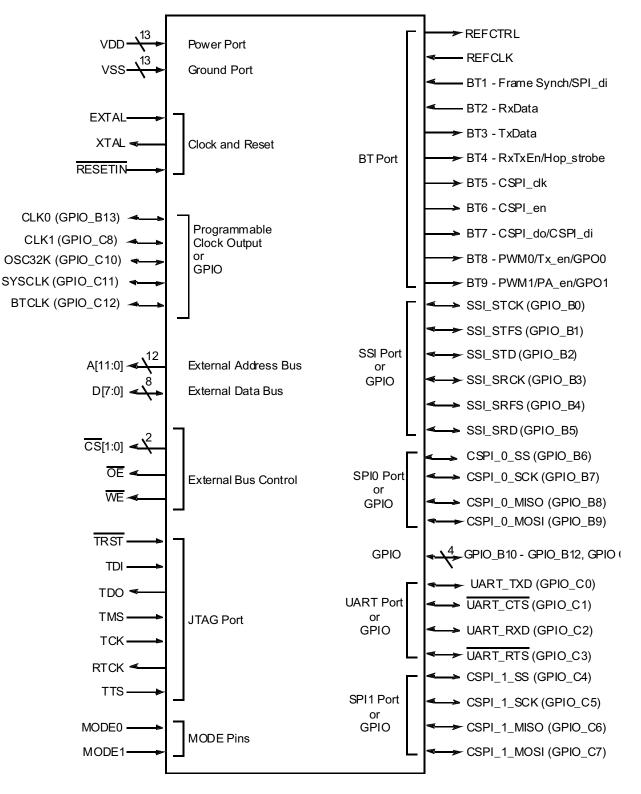

Package Information Plastic Package Case 1347 (MAPBGA–100)

#### **Ordering Information**

| Device  | Operating<br>Temperature Range | Package      |

|---------|--------------------------------|--------------|

| MC71000 | TA = – 40° to 85° C            | MAPBGA – 100 |

# Freescale Semiconductor, Inc.

# AICONDUCTOR, INC. 2005 Contents

| SEM                     | Applications2      |

|-------------------------|--------------------|

| 7                       | Typical Bluetooth  |

|                         | Solution Using the |

| Щ.                      | MC71000 2          |

| <b>ALI</b>              | Overview           |

| 04                      | Architectural      |

| S                       | Overview           |

| Щ                       |                    |

| 5                       | Pin Assignment     |

| R                       | Listing6           |

| 16                      | General            |

| >                       | Characteristics 16 |

| 07                      | Mechanical         |

|                         | Specifications 20  |

|                         | •                  |

| 18                      | Functionality      |

| 2                       | Overview           |

| 219                     | Supported HCI      |

| $\overline{\mathbf{O}}$ | Commands 27        |

| Ř                       |                    |

|                         |                    |

| <                       |                    |

The MC71000 Bluetooth Baseband Controller is a part of the Bluetooth<sup>™</sup> chipset from Motorola that provides a complete, low-power Bluetooth radio system. The design is based on Motorola's third-generation Bluetooth architecture that has set the industry standard for interoperability, complete functionality, and compliance with the Bluetooth specification.

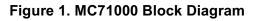

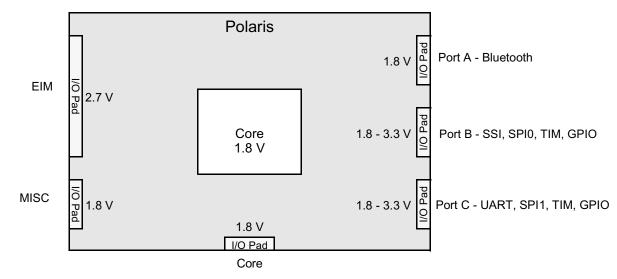

The MC71000 Bluetooth Baseband Controller from Motorola implements the baseband and host controller interface (HCI) of the Bluetooth protocol. It operates with a core voltage of 1.8 V and I/Os between 1.8 V and 3.3 V. The MC71000 is the ideal solution for low-power, short-range Bluetooth applications and includes superior performance features like the dedicated Bluetooth audio processor module and on-chip memory. Debug and production test are fully supported through the joint test action group (JTAG) interface. The MC71000 provides a zero-glue logic interface for the companion MC13180 Bluetooth RF Integrated Circuit (IC), allowing the implementation of a two-chip Bluetooth Class 2 radio. The addition of the MRFIC2408 External Power Amplifier provides a Class 1 solution.

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice. © Motorola, Inc., 2002. All rights reserved.

**ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005**

#### **1** Applications

- Mobile phone connectivity

- Personal digital assistant (PDA) connectivity

- Internet appliance connectivity

- Mobile phone headsets

#### 2 Typical Bluetooth Solution Using the MC71000

The following figure shows a sample two-chip Bluetooth solution.

SEMICONDUCTOR, INC. 2005

FREESCALE

Overview

#### 3 Overview

This section describes the overall system architecture of the MC71000 Bluetooth Baseband Controller. It highlights the main features and requirements, as well as provides an overview of the operational blocks of MC71000 Bluetooth Baseband Controller at a system level. The subsequent sections describe the detailed design requirements by major blocks and functions.

The MC71000 Bluetooth Baseband Controller implements the baseband and host controller interface (HCI) of the Bluetooth protocol and is specifically designed to meet the immediate market needs for low-power Bluetooth applications. To improve the total system throughput and reduce component cost and board size, the MC71000 Bluetooth Baseband Controller integrates a Motorola-unique ARM7TDMI platform with intelligent peripheral modules focused on communications and system integration. The MC71000 Bluetooth Baseband Controller includes superior performance features for audio and power conservation, as well as debug and production test support.

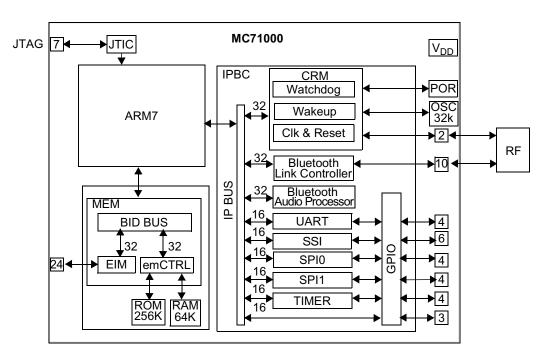

The MC71000 Bluetooth Baseband Controller provides a zero glue logic interface to the MC13180 Bluetooth RF Integrated CircuitC, a 2.4GHz Bluetooth radio for implementing a Bluetooth Class 2 solution. The addition of the MRFIC2408 External Power Amplifier IC provides a Class 1 solution. A power management chip, MC13181, is also available for headset and mobile phone accessory applications. The MC13181 integrates power management functions common to these applications. The architecture of the MC7100 is shown in Figure 1 on page 2.

#### 3.1 MC71000 Bluetooth Features

- Bluetooth Specification 1.1 Compliant

- Point-to-multipoint (piconet) with 7 slaves

- All connection types

- All packet types

- All power saving modes

- Master/slave switch

- Encryption

- HCI UART transport layer

- Superior Audio Performance

- Sample rate synchronization between CODEC and Bluetooth clock domains to avoid "clicking" effects

- 3 simultaneous SCO channels supported

- All Bluetooth encoding/decoding schemes supported (CVSD, A-Law, μ-Law)

- Very low audio delay to avoid the need for echo cancellation

- Support for 8, 16, 32, and 64 kHz Sample Rate CODECs

#### 3.2 MC71000 Hardware Features

The MC71000 is specifically designed to work with the Bluetooth protocol and supports a wide range of Bluetooth user profiles and applications. The MC71000 offers the following features:

- Bluetooth Link Controller

- Bluetooth Audio Processor

- ARM7 Processor Complex

- Peripherals

SEMICONDUCTOR, INC. 2005

FREESCALE

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

- High-speed UART (up to 2 Mbps)

- High-speed SSI (up to 2 Mbps)

- Dual high-speed SPI (up to 2 Mbps)

- Embedded Memory

- SRAM (64K)

- ROM (256K)

- External Interface Module (EIM)

- JTAG Test Interface Controller (JTIC)

- 32 kHz Oscillator (OSC32k) for Low Power Operation

- Operating Voltage: 1.65 V to 1.95 V

- Package: 100-pin MAPBGA, 7 mm x 7 mm, 0.65 mm ball pitch

#### 4 Architectural Overview

The following sections describe the functionality and performance of the MC71000 Bluetooth Baseband Controller.

#### 4.1 ARM7 Platform (A7P)

#### 4.1.1 ARM7TDMI

The MC71000 Bluetooth Baseband Controller architecture is based around the 32-bit ARM7TDMI microprocessor. It is an industry-standard processor recognized for its efficient MIPS/WATT benchmark, along with excellent code efficiency when working in the 16-bit THUMB mode. The architecture is based on RISC principles and supports two instruction sets:

- The 32-bit ARM instruction set

- The 16-bit THUMB instruction set

#### 4.2 Memory Sub-System

Program execution in the MC71000 Bluetooth Baseband Controller is predominantly ROM-based, with internal SRAM being used for code patching. An image can be uploaded from a host system, or a low-cost serial E2PROM (four-wire connection).

#### 4.2.1 External Interface Module (EIM)

The external interface module (EIM) handles the interface to external devices, as well as generation of chip selects for external peripherals and memory. It contains a zero-glue interface to external memories (SRAM, E2PROM, and FLASH chips).

#### 4.3 Peripherals Sub-System

#### 4.3.1 Clock and Reset Module (CRM)

The clock and reset module (CRM) is dedicated to handling all clock, reset, and power management features in the MC71000 Bluetooth Baseband Controller. It assures that the different clock and reset signals are stable before they are fed to the internal logic in the MC71000 Bluetooth Baseband Controller.

SEMICONDUCTOR, INC. 2005

FREESCALE

### Freescale Semiconductor, Inc. Architectural Overview

**ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005**

The CRM is designed to make full use of the facilities supplied by the Bluetooth standard to conserve power, while still maintaining a Bluetooth link. For this purpose, the CRM is connected to an on-chip low-power oscillator, which generates a frequency using an external low cost 32.768 kHz crystal. The CRM module also includes a watchdog to safeguard against any potential software failures.

#### 4.3.2 Bluetooth Link Controller (BTLC)

The Bluetooth link controller module (BTLC) handles all link controller specific functions. Raw data can be read from/written to the module, and the BTLC takes care of transmission related timing, as well as data signal processing functions like encryption and cyclic redundancy check (CRC)/header error correction (HEC) generation. Embedded in the BTLC are also the dedicated Bluetooth timers, which maintain an accurate estimate of time in both the native and the remote module. A small and dedicated Bluetooth serial peripheral interface controller handles all serial communication with the MC13180 Bluetooth RF Integrated Circuit.

#### 4.3.3 Bluetooth Audio Signal Processor (BTASP)

Special attention has been put on audio quality for the end user. For this purpose, a dedicated Bluetooth audio signal processing module (BTASP) has been designed to give users excellent and superior audio performance. With a minimum of processor intervention, this module handles all filtering, interpolation, as well as encoding/decoding (aLaw, uLaw, and CVSD).

#### 4.3.4 High-Speed UART (up to 2 Mb/sec @ 24 MHz)

The Universal Asynchronous Receiver/Transmitter (UART) module provides one of the main interfaces to the MC71000 Bluetooth Baseband Controller. The generated baud rate is based upon a configurable divisor and input clock. It can be configured to send one or two stop bits as well as odd, even, or no parity. The UART transmit and receive buffer sizes are 32 bytes each.

#### 4.3.5 Dual High-speed CSPI (up to 2 Mb/sec @ 24 MHz)

The MC71000 Bluetooth Baseband Controller contains two configurable serial peripheral interface (CSPI) modules, CSPI0 and CSPI1. CSPI0 can connect to a variety of SEEPROM and serial flash devices.

Both CSPI modules are master/slave configurable, equipped with 16 byte data out buffers (transmit and receive FIFOs), and allow the MC71000 Bluetooth Baseband Controller to interface with external CSPI master or slave devices. Incorporating the SPIRDY and SS control signals, it enables fast data communication with a fewer number of software interrupts.

#### 4.3.6 High-Speed SSI (up to 2 Mb/sec @ 24 MHz)

The synchronous serial interface module (SSI) is a full-duplex serial port allowing digital signal processors (DSPs) to communicate with a variety of serial devices, including industry-standard CODECs, other DSPs, microprocessors, and peripherals. The SSI is typically used to transfer samples in a periodic manner and consists of a variety of registers that handle port, status, control, transmit and receive, serial clock generation, and frame synchronization.

SEMICONDUCTOR, INC. 2005

FREESCALE

#### 4.3.7 Timer (TMR)

The dual timer module (TMR) is a general purpose module, used for timing control and application-specific tasks. The TMR can also be configured to perform pulse width modulation (PWM) or put into a quadrature-count mode if needed. The TMR contains two identical 16-bit counter/timer groups, each supports counting, prescaling, comparing, loading, capturing, and holding options.

#### 4.3.8 General Purpose (GPIO)

The MC71000 Bluetooth Baseband Controller supports a maximum of 27 GPIO lines grouped together in two ports. Port B contains 14 lines and Port C contains the other 13. These ports can be configured as GPIO pins or dedicated peripheral interface pins.

#### 4.4 Test

#### 4.4.1 JTAG Test Interface Controller (JTIC)

The JTIC interface offers full JTAG and boundary scan capabilities for debug and production test purposes, as well as access to the JTAG interface on the ARM.

#### 5 Pin Assignment Listing

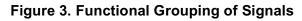

The following table (Table 2-1) shows the pin assignment listing for the MC71000 IC. The pins are organized into functional groups.

- The Pin Name and Description columns show the actual name and a brief description of each pin.

- The Std Pad Drive column lists the typical (minimum) drive current required for the pin.

- The Power Group column lists the Supply Power Group assignment.

- The Reset State column lists the pin input/output direction at chip RESET.

- The Alternate Functions column lists each of the GPIO port alternate input and output selections available. Some selections are test- or development-mode specific.

| Pin Name | Description        | Pin<br>Type | Reset<br>Pull U/D | Std<br>Pad<br>Drive | Power<br>Group | Reset<br>State | Alternate<br>Functions |

|----------|--------------------|-------------|-------------------|---------------------|----------------|----------------|------------------------|

|          |                    |             | EIM               |                     |                |                |                        |

| A0       | EIM - Address line | 0           |                   | 5 mA                | EIMVDD         | O/L            |                        |

| A1       | EIM - Address line | 0           |                   | 5 mA                | EIMVDD         | O/L            |                        |

| A2       | EIM - Address line | 0           |                   | 5 mA                | EIMVDD         | O/L            |                        |

| A3       | EIM - Address line | 0           |                   | 5 mA                | EIMVDD         | O/L            |                        |

| A4       | EIM - Address line | 0           |                   | 5 mA                | EIMVDD         | O/L            |                        |

| A5       | EIM - Address line | 0           |                   | 5 mA                | EIMVDD         | O/L            |                        |

| A6       | EIM - Address line | 0           |                   | 5 mA                | EIMVDD         | O/L            |                        |

| A7       | EIM - Address line | 0           |                   | 5 mA                | EIMVDD         | O/L            |                        |

| A8       | EIM - Address line | 0           |                   | 5 mA                | EIMVDD         | O/L            |                        |

| A9       | EIM - Address line | 0           |                   | 5 mA                | EIMVDD         | O/L            |                        |

| A10      | EIM - Address line | 0           |                   | 5 mA                | EIMVDD         | O/L            |                        |

Table 1. MC71000 Bluetooth Baseband Controller Pin Description

EMICONDUCTOR, INC. 2005

S

FREESCALE

#### Freescale Semiconductor, Inc. Pin Assignment Listing

**ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005**

Table 1. MC71000 Bluetooth Baseband Controller Pin Description (Continued)

| Pin Name | Description                                  | Pin<br>Type     | Reset<br>Pull U/D | Std<br>Pad<br>Drive | Power<br>Group | Reset<br>State | Alternate<br>Functions |

|----------|----------------------------------------------|-----------------|-------------------|---------------------|----------------|----------------|------------------------|

| A11      | EIM - Address line                           | 0               |                   | 5 mA                | EIMVDD         | O/L            |                        |

| D0       | EIM - Data line                              | I/O             | PU                | 5 mA                | EIMVDD         | Z/H            |                        |

| D1       | EIM - Data line                              | I/O             | PU                | 5 mA                | EIMVDD         | Z/H            |                        |

| D2       | EIM - Data line                              | I/O             | PU                | 5 mA                | EIMVDD         | Z/H            |                        |

| D3       | EIM - Data line                              | I/O             | PU                | 5 mA                | EIMVDD         | Z/H            |                        |

| D4       | EIM - Data line                              | I/O             | PU                | 5 mA                | EIMVDD         | Z/H            |                        |

| D5       | EIM - Data line                              | I/O             | PU                | 5 mA                | EIMVDD         | Z/H            |                        |

| D6       | EIM - Data line                              | I/O             | PU                | 5 mA                | EIMVDD         | Z/H            |                        |

| D7       | EIM - Data line                              | I/O             | PU                | 5 mA                | EIMVDD         | Z/H            |                        |

| CS0      | EIM - Chip Select 0                          | 0               |                   | 5 mA                | EIMVDD         | O/H            |                        |

| CS1      | EIM - Chip Select 1                          | 0               |                   | 5 mA                | EIMVDD         | O/H            |                        |

| OE       | EIM - Output enable                          | 0               |                   | 5 mA                | EIMVDD         | O/H            |                        |

| WE       | EIM - Write enable                           | 0               |                   | 5 mA                | EIMVDD         | O/H            |                        |

|          |                                              |                 | MISC              |                     | <b>I</b>       | <u> </u>       |                        |

| EXTAL    | CLK - 32 kHz External<br>crystal clock input | I               |                   | _                   | MISCVDD        | I              |                        |

| XTAL     | CLK - 32 kHz Crystal<br>output               | 0               |                   | ?                   | MISCVDD        | 0              |                        |

| TRST     | JTAG - Test reset                            | ST <sup>1</sup> | PD                |                     | MISCVDD        | I              |                        |

| TDI      | JTAG - Test data input                       | I               | PU                |                     | MISCVDD        | I              |                        |

| TDO      | JTAG - Test data<br>output                   | Tri-O           |                   | 3 mA                | MISCVDD        | O/L            |                        |

| TMS      | JTAG - Test mode<br>select input             | Ι               | PU                |                     | MISCVDD        | I              |                        |

| ТСК      | JTAG - Test clock<br>input                   | ST <sup>1</sup> | PD                | _                   | MISCVDD        | I              |                        |

| RTCK     | JTAG - Test clock<br>output                  | 0               |                   |                     | MISCVDD        | 0              |                        |

| TTS      | JTAG - Test tap select                       | I               |                   | _                   | MISCVDD        | I              |                        |

| MODE0    | Boot mode select pin 0                       | I               | PU                |                     | MISCVDD        | I              |                        |

| MODE1    | Boot mode select pin 1                       | I               | PU                | _                   | MISCVDD        | I              |                        |

| RESETIN  | Reset input - POR                            | I               | ST <sup>1</sup>   |                     | MISCVDD        | Ι              |                        |

|          |                                              | PORT A          | A (BLUETC         | OOTH)               |                |                |                        |

| REFCTRL  | RF Reference clock control                   | 0               |                   | 3 mA                | AVDD           | O/L            |                        |

| REFCLK   | RF Reference clock input                     | I               |                   |                     | AVDD           | I              |                        |

| BT1      | BT - Frame synch/<br>CSPI_di                 | I               |                   |                     | AVDD           | I              |                        |

| BT2      | BT - RXDATA                                  | Ι               |                   |                     | AVDD           | Ι              |                        |

| BT3      | BT - TXDATA                                  | Tri-O           | PU                | 3 mA                | AVDD           | Z/H            |                        |

| BT4      | BT - RXTXEN/<br>HOP_STROBE                   | 0               |                   | 3 mA                | AVDD           | O/L            |                        |

| BT5      | BT - SPI_CLK                                 | 0               |                   | 3 mA                | AVDD           | O/L            |                        |

MOTOROLA

**ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005** Table 1. MC71000 Bluetooth Baseband Controller Pin Description (Continued)

| Pin Name    | Description                         | Pin<br>Type | Reset<br>Pull U/D | Std<br>Pad<br>Drive | Power<br>Group | Reset<br>State | Alternate<br>Functions |

|-------------|-------------------------------------|-------------|-------------------|---------------------|----------------|----------------|------------------------|

| BT6         | BT - SPI_EN                         | 0           |                   | 3 mA                | AVDD           | O/H            |                        |

| BT7         | BT - SPI_DO/SPI_DI                  | I/O         |                   | 3 mA                | AVDD           | O/L            |                        |

| BT8         | BT - PWM0/TX_EN/<br>GPO0            | Tri-O       |                   | 3 mA                | AVDD           | O/L            |                        |

| BT9         | BT - PWM1/PA_EN/<br>GPO1            | 0           |                   | 3 mA                | AVDD           | O/L            |                        |

|             |                                     |             | PORT B            |                     |                |                |                        |

| SSI_STCK    | SSI - Serial Transmit<br>Clock      | I/O         | PU                | 3 mA                | BVDD           | Z/H            | GPIO_B0;<br>BT_TP0     |

| SSI_STFS    | SSI - Serial Transmit<br>Frame Sync | I/O         | PU                | 3 mA                | BVDD           | Z/H            | GPIO_B1;<br>BT_TP1     |

| SSI_STD     | SSI - Serial Transmit<br>Data       | I/O         | PU                | 3 mA                | BVDD           | Z/H            | GPIO_B2;<br>BT_TP2     |

| SSI_SRCK    | SSI - Serial Receive<br>Clock       | I/O         | PU                | 3 mA                | BVDD           | Z/H            | GPIO_B3;<br>BT_TP3     |

| SSI_SRFS    | SSI - Serial Receive<br>Frame Sync  | I/O         | PU                | 3 mA                | BVDD           | Z/H            | GPIO_B4;<br>BT_TP4     |

| SSI_SRD     | SSI - Serial Receive<br>Data        | I/O         | PU                | 3 mA                | BVDD           | Z/H            | GPIO_B5;<br>BT_TP5     |

| CSPI_0_SS   | CSPI #0 - Slave<br>Select           | 0           | PU                | 3 mA                | BVDD           | Z/H            | GPIO_B6;<br>BT_TP6     |

| CSPI_0_SCK  | CSPI #0 - Serial Clock              | 0           | PU                | 3 mA                | BVDD           | Z/H            | GPIO_B7;<br>BT_TP7     |

| CSPI_0_MISO | CSPI #0 - Master In /<br>Slave out  | I/O         | PU                | 3 mA                | BVDD           | O/L            | GPIO_B8;<br>BT_TP8;    |

| CSPI_0_MOSI | CSPI #0 - Master Out /<br>Slave in  | I/O         | PU                | 3 mA                | BVDD           | Z/H            | GPIO_B9;<br>BT_TP9     |

| GPIO_B10    | General Purpose I/O                 | I/O         | PU                | 3 mA                | BVDD           | Z/H            | GPIO_B10<br>UART-TXD   |

| GPIO_B11    | General Purpose I/O                 | I/O         | PU                | 3 mA                | BVDD           | Z/H            | GPIO_B11<br>UART-RTS   |

| GPIO_B12    | General Purpose I/O                 | I/O         | PU                | 3 mA                | BVDD           | Z/H            | GPIO_B12<br>UART-RXD   |

| CLK0        | Programmable Clock<br>Output        | I/O         | PU                | 3 mA                | BVDD           | O/L            | GPIO_B13<br>UART-CTS   |

|             |                                     |             | PORT C            |                     |                | 1              |                        |

| TXD         | UART - TXD                          | Tri-O       | PU                | 3 mA                | CVDD           | Z/H            | GPIO_C0;<br>CSPI0_REQ  |

| CTS_        | UART - CTS                          | Tri-O       | PU                | 3 mA                | CVDD           | Z/H            | GPIO_C1;<br>CSPI1_REQ  |

| RXD         | UART - RXD                          | I/O         | PU                | 3 mA                | CVDD           | Z/H            | GPIO_C2;<br>TIM_0_I    |

| RTS_        | UART - RTS                          | I/O         | PU                | 3 mA                | CVDD           | Z/H            | GPIO_C3;<br>TIM_1_I    |

| CSPI_1_SS   | CSPI #1 - Slave select              | 0           | PU                | 3 mA                | CVDD           | O/H            | GPIO_C4;<br>SYSCLK     |

#### Freescale Semiconductor, Inc. Pin Assignment Listing

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005 Table 1. MC71000 Bluetooth Baseband Controller Pin Description (Continued)

| Pin Name    | Description                        | Pin<br>Type | Reset<br>Pull U/D | Std<br>Pad<br>Drive | Power<br>Group | Reset<br>State | Alternate<br>Functions |

|-------------|------------------------------------|-------------|-------------------|---------------------|----------------|----------------|------------------------|

| CSPI_1_SCK  | CSPI #1 - Serial clock             | 0           | PU                | 3 mA                | CVDD           | O/H            | GPIO_C5;<br>SH_STROBE  |

| CSPI_1_MISO | CSPI #1 - Master In /<br>Slave out | I/O         | PU                | 3 mA                | CVDD           | O/L            | GPIO_C6;<br>ABORT      |

| CSPI_1_MOSI | CSPI #1 - Master Out /<br>Slave in | I/O         | PU                | 3 mA                | CVDD           | Z/H            | GPIO_C7;<br>REFCLK     |

| CLK1        | Programmable clock output          | I/O         | PU                | 3 mA                | CVDD           | O/L            | GPIO_C8;<br>TIM_0_O    |

| GPIO_C9     | General Purpose I/O                | I/O         | PU                | 3 mA                | CVDD           | Z/H            | GPIO_C9;<br>XACK       |

| OSC32K      | Buffered Low Power<br>32 kHz Clock | I/O         | PU                | 3 mA                | CVDD           | O/L            | GPIO_C10;<br>TIM_1_O   |

| SYSCLK      | Buffered System<br>Clock           | I/O         | PU                | 3 mA                | CVDD           | O/L            | GPIO_C11               |

| BTCLK       | Buffered Bluetooth<br>Clock        | I/O         | PU                | 3 mA                | CVDD           | O/L            | GPIO_C12               |

|             |                                    | EIM PO      | WER/GRO           | DUND                |                |                |                        |

| GND_EIM2    | GND                                | GND         |                   |                     | EIMVDD         |                |                        |

| GND_EIM3    | GND                                | GND         |                   |                     | EIMVDD         |                |                        |

| GND_EIM4    | GND                                | GND         |                   |                     | EIMVDD         |                |                        |

| GND_EIM6    | GND                                | GND         |                   |                     | EIMVDD         |                |                        |

| GND_EIM7    | GND                                | GND         |                   |                     | EIMVDD         |                |                        |

| PWR_EIM2    | PWR                                | PWR         |                   |                     | EIMVDD         |                |                        |

| PWR_EIM3    | PWR                                | PWR         |                   |                     | EIMVDD         |                |                        |

| PWR_EIM4    | PWR                                | PWR         |                   |                     | EIMVDD         |                |                        |

| PWR_EIM6    | PWR                                | PWR         |                   |                     | EIMVDD         |                |                        |

| PWR_EIM7    | PWR                                | PWR         |                   |                     | EIMVDD         |                |                        |

|             |                                    | MISC PO     | OWER/GR           | OUND                |                |                |                        |

| GND_MISC    | GND                                | GND         |                   |                     | MISCVDD        |                |                        |

| PWR_MISC    | PWR                                | PWR         |                   |                     | MISCVDD        |                |                        |

|             | F                                  | PORT A      | POWER/G           | ROUND               |                |                |                        |

| GND_PA      | GND                                | GND         |                   |                     | AVDD           |                |                        |

| PWR_PA      | PWR                                | PWR         |                   |                     | AVDD           |                |                        |

|             | F                                  | PORT B      | POWER/G           | ROUND               | •              |                |                        |

| GND_PB      | GND                                | GND         |                   |                     | BVDD           |                |                        |

| <br>PWR_PB  | PWR                                | PWR         |                   |                     | BVDD           |                |                        |

|             | F                                  | PORT C I    | POWER/G           | ROUND               | I              |                |                        |

| GND_PC      | GND                                | GND         | 1                 |                     | CVDD           |                |                        |

| PWR_PC      | PWR                                | PWR         |                   |                     | CVDD           |                |                        |

|             |                                    | CORE P      | OWER/GR           | OUND                |                |                |                        |

| GND_CORE1   | GND                                | GND         |                   |                     | COREVDD        |                |                        |

| GND_CORE2   | GND                                | GND         |                   |                     | COREVDD        |                |                        |

| GND_CORE3   | GND                                | GND         |                   |                     | COREVDD        |                |                        |

**Freescale Semiconductor, Inc.** ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

**ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005** Table 1. MC71000 Bluetooth Baseband Controller Pin Description (Continued)

| Pin Name  | Description | Pin<br>Type | Reset<br>Pull U/D | Std<br>Pad<br>Drive | Power<br>Group | Reset<br>State | Alternate<br>Functions |

|-----------|-------------|-------------|-------------------|---------------------|----------------|----------------|------------------------|

| GND_CORE4 | GND         | GND         |                   |                     | COREVDD        |                |                        |

| PWR_CORE1 | PWR         | PWR         |                   |                     | COREVDD        |                |                        |

| PWR_CORE2 | PWR         | PWR         |                   |                     | COREVDD        |                |                        |

| PWR_CORE3 | PWR         | PWR         |                   |                     | COREVDD        |                |                        |

| PWR_CORE4 | PWR         | PWR         |                   |                     | COREVDD        |                |                        |

1.ST - Schmitt Trigger input

#### 5.1 Pin Descriptions

The following table provides detailed pin descriptions for the external interface module (EIM); clock, reset, and JTAG; Bluetooth; SSI, SPI0, and UART; and UART, SPI1, and TIM including the GPIO shared package pins.

In the following table, the general purpose input/output (GPIO) is designed to share package pins with other peripheral modules on the chip. If the peripheral which normally controls a given pin is not required, then the pin may be programmed to be a general purpose input/output (GPIO) or alternate function 2 with programmable pullup. The GPIO module design has two available ports (Port B and Port C). The individual control for each pin can be in normal functional mode, alternate function mode 2, or GPIO mode. The individual direction control for each pin is in GPIO mode. The individual pullup enable control for each pin is in normal function mode, alternate function mode 2, or GPIO mode.

- Normal mode. The peripheral module controls the output enable and any output data to the pad and any input data from the pad is passed to the peripheral.

- Alternate function 1 mode (GPIO). The GPIO module controls the output enable to the pad and supplies any data to be output.

- Alternate function 2 mode. The peripheral module controls the output enable and any output data to the pad and any input data from the pad is passed to the peripheral.

|                      | EIM Signals                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D7 (Data Bus)     | Active high, bidirectional inputs/outputs. D0 is the least significant bit and D7 is the most significant. These pins provide the bidirectional data bus for external memory access. D0–D7 are held in the previous logic state when there is no external bus activity. This is done with weak "keepers" inside the I/O buffers. They are also kept in their previous state during hardware reset. |

| A0-A11 (Address Bus) | Active high outputs, specifies the address for external memory accesses. ADDR0 is the least significant bit and ADDR11 is the most significant. To minimize power dissipation, ADDR0–ADDR11 do not change state when external memory is not being accessed.                                                                                                                                        |

| CS1 (Chip Select 1)  | This output signal is active low and is asserted based on the decode of the internal address bus.                                                                                                                                                                                                                                                                                                  |

| CS0 (Chip Select 0)  | This active-low output signal is asserted based on the decode of the internal address bus.                                                                                                                                                                                                                                                                                                         |

| OE (Output Enable)   | This active low output signal is used to indicate that the bus access is a read and enables slave devices to drive the data bus with read data. OE is negated during hardware reset.                                                                                                                                                                                                               |

| WE (Write Enable)    | This active low output signal is used to indicate that the bus access is a write and enables slave devices to drive the address bus with the write data.                                                                                                                                                                                                                                           |

| Table 2. | Pin Descriptions |

|----------|------------------|

|----------|------------------|

| 5   | 2005     |

|-----|----------|

| ÷., | 2        |

| 5   | INC      |

| ō   | ۰.       |

| ÷.  | ō        |

| 0   | E E      |

| 5   | Ď        |

| 0   | Ģ        |

| Ž   | NO       |

| 0   | SEMIC    |

| Ŭ   | ≥        |

|     | SE       |

| Ξ   | Щ        |

| Δ   |          |

|     | ESCAI    |

|     | С<br>Ш   |

| 0   | Ĩ        |

|     | Ë        |

|     | ž        |

| X   |          |

| Ä   |          |

| X   | $\geq$   |

| 2   | E        |

| E   | <b>N</b> |

|     | 4        |

|     |          |

÷

1

U

L

#### Freescale Semiconductor, Inc. Pin Assignment Listing

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005 Table 2. Pin Descriptions (Continued)

| Table 2. Pin Descriptions (Continued)         Clock, Reset, and JTAG Signals |                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                              | -                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| EXTAL CLK                                                                    | 32 kHz external crystal clock input                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| XTAL CLK                                                                     | 32 kHz Crystal output                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| TDI (Test Data Input)                                                        | The test data input pin provides a serial input data stream to all TAP controllers. TDI is sampled on the rising edge of TCK.                                                                                                                                                                                                                                               |  |  |  |

| TDO (Test Data Output)                                                       | The test data output pin is tri-statable, providing serial output data from the Master TAP or ARM Core TAP controller. It is actively driven in the shift-IR and shift-DR controller states of the TAP controller state machine. TDO changes on the falling edge of TCK.                                                                                                    |  |  |  |

| TRST (Test Reset)                                                            | This active low Schmitt trigger input pin provides an asynchronously reset signal to all TAP controllers to initialize the test controller.                                                                                                                                                                                                                                 |  |  |  |

| TMS (Test Mode Select)                                                       | The test mode select input pin is used to sequence all TAP controllers. The TAP sequenced is determined by the tap control module and the TTS device port. TMS is sampled on the rising edge of TCK.                                                                                                                                                                        |  |  |  |

| TCK (Test Clock)                                                             | The test clock input pin is used to synchronize the JTAG test logic. It provides the clock to synchronize the test logic and shift serial data to and from all TAP controllers.                                                                                                                                                                                             |  |  |  |

| RTCK (Return Test Clock)                                                     | The return test clock input pin returns the synchronization test clock to ARM development tools to be entered from the serial debug input line.                                                                                                                                                                                                                             |  |  |  |

| TTS (Test TAP select)                                                        | The test tap select input pin directly controls the multiplexing logic to select between the chip TAP and the core TAP. A logic 1 applied to the tap select input will select the chip TAP.                                                                                                                                                                                 |  |  |  |

| MODE[1:0]                                                                    | Test/boot mode select pins. In order to support a flexible development system, the system must be capable to boot from different memories during system reset and power-up. The four different memory maps can be selected by these two pins. All the different boot modes start reading data at address 0x0000_0000, since this is where the ARM7 reset vector is located. |  |  |  |

| RESETIN (Reset In)                                                           | The reset in pin is an active low Schmitt trigger input that provides reset to the internal circuitry. The RESET input will be qualified as valid if it will be asserted for at least 3 CLK cycles.                                                                                                                                                                         |  |  |  |

|                                                                              | Bluetooth Signals                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| REFCTRL<br>(Reference Control)                                               | The reference control pin is a dedicated output from the CRM which enables/disables the reference clock.                                                                                                                                                                                                                                                                    |  |  |  |

| REFCLK (Reference Clock)                                                     | The reference clock pin is a dedicated input into the CRM from the RF interface. (12-32 MHz)                                                                                                                                                                                                                                                                                |  |  |  |

| BT1                                                                          | Input from the RF front end. Frame sync for the MC13180 RF IC; CSPI_din for Silicon Wave                                                                                                                                                                                                                                                                                    |  |  |  |

| BT2                                                                          | RXDATA: Input from the MC13180 RF IC and Silicon Wave RF Front End                                                                                                                                                                                                                                                                                                          |  |  |  |

| BT3                                                                          | TXDATA: Output to the MC13180 RF IC and Silicon Wave RF Front End                                                                                                                                                                                                                                                                                                           |  |  |  |

| BT4                                                                          | Dedicated RF control output to the RF Front Ends. RXTX_EN for the MC13180 RF IC Radio or HOP_STROBE for the Silicon Wave Radio.                                                                                                                                                                                                                                             |  |  |  |

| BT5                                                                          | CSPI_CLK: One of the three CSPI signals which program the MC13180 RF IC Radio or one of the four CSPI signals which program the Silicon Wave Radio.                                                                                                                                                                                                                         |  |  |  |

| BT6                                                                          | CSPI_EN: One of the three CSPI signals which program the MC13180 RF IC Radio or one of the four CSPI signals which program the Silicon Wave Radio.                                                                                                                                                                                                                          |  |  |  |

| BT7                                                                          | CSPI_DOUT/CSPI_DIN: One of the three CSPI signals which program the MC13180<br>RF IC Radio (CSPI_DIN or CSPI_DOUT) or one of the four CSPI signals which program<br>the Silicon Wave Radio (CSPI_DOUT)                                                                                                                                                                      |  |  |  |

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005 2. Pin Descriptions (Continued)

|                             | Table 2. Pin Des                                                                                                                                                                  | CHIVED BY FREESCALE SEMICONDUCTOR, INC<br>scriptions (Continued)                                                                                                    |  |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BT8                         |                                                                                                                                                                                   | l output which can be programmed for different purposes, ulse Width modulator output), or as GPO0.                                                                  |  |  |  |

| BT9                         | The BT9 pin is an RF control output which can be programmed for different purposes,<br>such as PA_EN (power amplifier enable), PWM1 (pulse width modulator output) or as<br>GPO1. |                                                                                                                                                                     |  |  |  |

|                             | SSI, SPI0, a                                                                                                                                                                      | nd UART Signals                                                                                                                                                     |  |  |  |

| SSI_STCK/GPIO_B0/BT_TI      | P0                                                                                                                                                                                |                                                                                                                                                                     |  |  |  |

| Normal Mode                 | SSI_STCK                                                                                                                                                                          | The serial transmit clock signal is used by the transmitter and can be either continuous or gated.                                                                  |  |  |  |

| Alternate Function 1 (GPIO) | GPIO_B0                                                                                                                                                                           | GPIO 0 on Port B                                                                                                                                                    |  |  |  |

| Alternate Function 2        | BT_TP0                                                                                                                                                                            | Bluetooth test port                                                                                                                                                 |  |  |  |

| SSI_STFS/GPIO_B1/BT_TF      | 21                                                                                                                                                                                |                                                                                                                                                                     |  |  |  |

| Normal Mode                 | SSI_STFS                                                                                                                                                                          | The serial transmit frame sync signal is used by the transmitter to synchronize the transfer of data. The frame sync signal can be one bit or one word in length.   |  |  |  |

| Alternate Function 1 (GPIO) | GPIO_B1                                                                                                                                                                           | GPIO 1 on Port B                                                                                                                                                    |  |  |  |

| Alternate Function 2        | BT_TP1                                                                                                                                                                            | Bluetooth test port signal                                                                                                                                          |  |  |  |

| SSI_STD/GPIO_B2/BT_TP2      | 2                                                                                                                                                                                 |                                                                                                                                                                     |  |  |  |

| Normal Mode                 | SSI_STD                                                                                                                                                                           | The serial transmit data signal is used to transmit serial data.                                                                                                    |  |  |  |

| Alternate Function 1 (GPIO) | GPIO_B2                                                                                                                                                                           | GPIO 2 on Port B                                                                                                                                                    |  |  |  |

| Alternate Function 2        | BT_TP2                                                                                                                                                                            | Bluetooth test port signal                                                                                                                                          |  |  |  |

| SSI_SRCK/GPIO_B3/BT_T       | P3                                                                                                                                                                                |                                                                                                                                                                     |  |  |  |

| Normal Mode                 | SSI_SRCK                                                                                                                                                                          | The serial receive clock signal is used by the receiver and<br>is always continuous, however, it is not used in<br>synchronous mode.                                |  |  |  |

| Alternate Function 1 (GPIO) | GPIO_B3                                                                                                                                                                           | GPIO 3 on Port B                                                                                                                                                    |  |  |  |

| Alternate Function 2        | BT_TP3                                                                                                                                                                            | Bluetooth test port signal                                                                                                                                          |  |  |  |

| SSI_SRFS/GPIO_B4/BT_TF      | 24                                                                                                                                                                                |                                                                                                                                                                     |  |  |  |

| Normal Mode                 | SSI_SRFS                                                                                                                                                                          | The serial receive frame sync signal is used by the receiver<br>to synchronize the transfer of data. The frame sync signal<br>can be one bit or one word in length. |  |  |  |

| Alternate Function 1 (GPIO) | GPIO_B4                                                                                                                                                                           | GPIO 4 on Port B                                                                                                                                                    |  |  |  |

| Alternate Function 2        | BT_TP4                                                                                                                                                                            | Bluetooth test port signal                                                                                                                                          |  |  |  |

| SSI_SRD/GPIO_B5/BT_TP       | 5                                                                                                                                                                                 |                                                                                                                                                                     |  |  |  |

| Normal Mode                 | SSI_SRD                                                                                                                                                                           | The serial receive data signal is used to receive serial data.                                                                                                      |  |  |  |

| Alternate Function 1 (GPIO) | GPIO_B5                                                                                                                                                                           | GPIO 5 on Port B                                                                                                                                                    |  |  |  |

| Alternate Function 2        | BT_TP5                                                                                                                                                                            | Bluetooth test port signal                                                                                                                                          |  |  |  |

| CSPI_0_SS/GPIO_B6/BT_T      | ſP6                                                                                                                                                                               |                                                                                                                                                                     |  |  |  |

MC71000 Advance Information For More Information On This Product, Go to: www.freescale.com

#### Freescale Semiconductor, Inc. Pin Assignment Listing

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005 Table 2. Pin Descriptions (Continued)

|                             | Table 2. Pin | Descriptions (Continued)                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Normal Mode                 | CSPI_0_SS    | The CSPI0 slave select bidirectional signal is an output in master mode and an input in slave mode.                                                                                                                                                                                                                                                                                             |

| Alternate Function 1 (GPIO) | GPIO_B6      | GPIO 6 on Port B                                                                                                                                                                                                                                                                                                                                                                                |

| Alternate Function 2        | BT_TP6       | Bluetooth test port signal                                                                                                                                                                                                                                                                                                                                                                      |

| CSPI_0_SCK/GPIO_B7/BT_      | TP7          |                                                                                                                                                                                                                                                                                                                                                                                                 |

| Normal Mode                 | CSPI0 Clock  | This bidirectional signal is the CSPI0 clock output in master mode. In slave mode, CSPI_0_SCK is an input clock signal to the CSPI.                                                                                                                                                                                                                                                             |

| Alternate Function 1 (GPIO) | GPIO_B7      | GPIO 7 on Port B                                                                                                                                                                                                                                                                                                                                                                                |

| Alternate Function 2        | BT_TP7       | Bluetooth test port signal                                                                                                                                                                                                                                                                                                                                                                      |

| CSPI_0_MISO/GPIO_B8/BT      | _TP8         |                                                                                                                                                                                                                                                                                                                                                                                                 |

| Normal Mode                 | CSPI0        | Master In Slave Out: In master mode, this bidirectional signal is the RXD input signal. In slave mode, MISO is the TXD output signal.                                                                                                                                                                                                                                                           |

| Alternate Function 1 (GPIO) | GPIO_B8      | GPIO 8 on Port B                                                                                                                                                                                                                                                                                                                                                                                |

| Alternate Function 2        | BT_TP8       | Bluetooth test port signal                                                                                                                                                                                                                                                                                                                                                                      |

| CSPI_0_MOSI/GPIO_B9/BT      | _ТР9         |                                                                                                                                                                                                                                                                                                                                                                                                 |

| Normal Mode                 | CSPI0        | Master Out Slave In: In master mode, this bidirectional signal is the TXD output signal. In slave mode, MOSI is the RXD input signal.                                                                                                                                                                                                                                                           |

| Alternate Function 1 (GPIO) | GPIO_B9      | GPIO 9 on Port B                                                                                                                                                                                                                                                                                                                                                                                |

| Alternate Function 2        | BT_TP9       | Bluetooth test port signal; Bluetooth 4 MHz clock                                                                                                                                                                                                                                                                                                                                               |

| GPIO_B10/UART_TxD           |              |                                                                                                                                                                                                                                                                                                                                                                                                 |

| Alternate Function 1 (GPIO) | GPIO_B10     | GPIO 10 on Port B                                                                                                                                                                                                                                                                                                                                                                               |

| Alternate Function 2        | UART_TxD     | Transmit data serial (output signal)                                                                                                                                                                                                                                                                                                                                                            |

| GPIO_B11/UART_RTS           |              |                                                                                                                                                                                                                                                                                                                                                                                                 |

| Alternate Function 1 (GPIO) | GPIO_B11     | GPIO 11 on Port B                                                                                                                                                                                                                                                                                                                                                                               |

| Alternate Function 2        | UART_RTS     | UART ready to send (RTS) This input signal, when<br>asserted, indicates that the remote device is ready to<br>accept new data and that the MC71000 Bluetooth<br>Baseband Controller can transmit when it has data to send.                                                                                                                                                                      |

| GPIO_B12/UART_RxD           |              |                                                                                                                                                                                                                                                                                                                                                                                                 |

| Alternate Function 1 (GPIO) | GPIO_B12     | GPIO 12 on Port B                                                                                                                                                                                                                                                                                                                                                                               |

| Alternate Function 2        | UART_RxD     | Receive data serial (input signal)                                                                                                                                                                                                                                                                                                                                                              |

| CLK0/GPIO_B13/UART_CT       | S            | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                           |

| Normal Mode                 | CLK0         | Output to external devices generated by the fractional clock divider in the CRM. CLK0 is a programmable clock and derivative of REFCLK. Frequencies are programmable in the range of REFCLK/127 to REFCLK. CLK0 can be used to feed an external USB, a CODEC, or whatever the applications need. The fractional divider has 16-bit resolution; writing 0x000 to the divisor disables the timer. |

vin Assignment Listing

#### Freescale Semiconductor, Inc.

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005 2. Pin Descriptions (Continued)

|                             | Table 2. Pin D | escriptions (Continued)                                                                                                                                                                                                |

|-----------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Alternate Function 1 (GPIO) | GPIO_B13       | GPIO 13 on Port B                                                                                                                                                                                                      |

| Alternate Function 2        | UART_CTS       | UART clear to send (CTS) This output signal, when<br>asserted, indicates that the MC71000 Bluetooth Baseband<br>Controller is ready to accept new data and the remote<br>device can transmit when it has data to send. |

|                             | UART, SP       | I1, and TIM Signals                                                                                                                                                                                                    |

| TXD/GPIO_C0/CSPI0_REQ       |                |                                                                                                                                                                                                                        |

| Normal Mode                 | TXD            | UART transmit data serial (output signal)                                                                                                                                                                              |

| Alternate Function 1 (GPIO) | GPIO_C0        | GPIO 0 on Port C                                                                                                                                                                                                       |

| Alternate Function 2        | CSPI0_REQ      | External data transfer rate control for CSPI0                                                                                                                                                                          |

| CTS/GPIO_C1/CSPI1_REQ       |                |                                                                                                                                                                                                                        |

| Normal Mode                 | CTS            | UART clear to send (CTS) output signal, when asserted, indicates that the MC71000 is ready to accept new data and the remote device can transmit when it has data to send.                                             |