**MPL3150A2** I<sup>2</sup>C precision pressure sensor Rev. 4 – 19 January 2021

Product data sheet

### **1** General description

The MPL3150A2 is a compact, piezoresistive, absolute pressure sensor with an I<sup>2</sup>C digital interface. MPL3150A2 has a wide operating range of 50 kPa to 150 kPa. The MEMS is temperature compensated utilizing an on-chip temperature sensor. The pressure and temperature data is fed into a high-resolution ADC to provide fully compensated and digitized outputs for pressure in Pascals and temperature in °C. The internal processing in MPL3150A2 removes compensation and unit conversion load from the system MCU, simplifying system design.

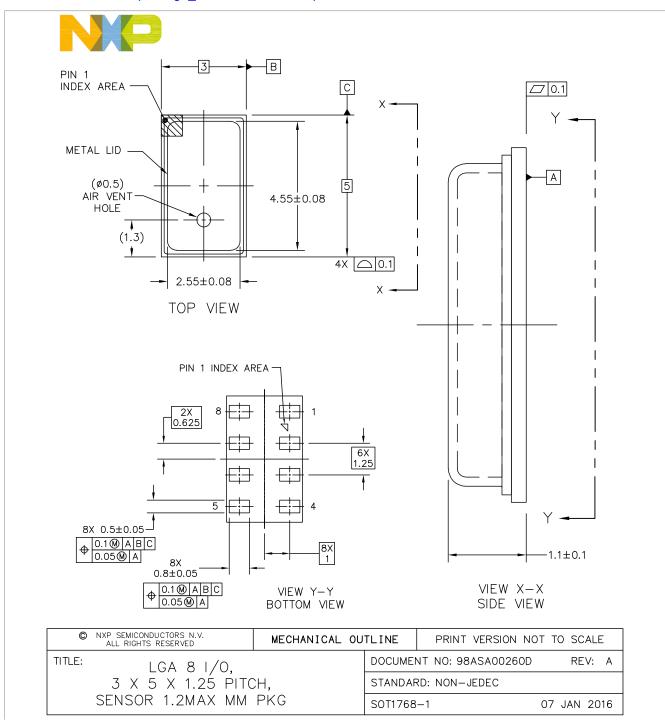

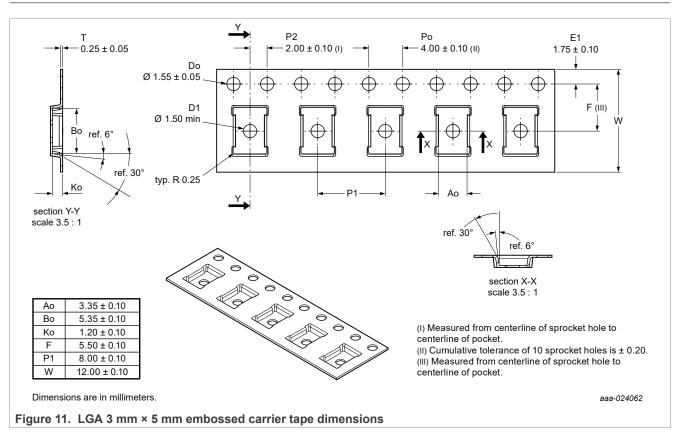

MPL3150A2's advanced ASIC has multiple user programmable modes such as power saving, interrupt and autonomous data acquisition modes, including programmed acquisition cycle timing, and poll-only modes. Typical active supply current is 40  $\mu$ A per measurement-second and is offered in a 5 mm x 3 mm x 1.1 mm LGA RoHS compliant package.

### 2 Features and benefits

- Operating range: 50 kPa to 150 kPa absolute pressure

- Calibrated range: 70 kPa to 150 kPa absolute pressure

- Calibrated temperature output: -40 °C to 85 °C

- I<sup>2</sup>C digital output interface

- Fully compensated internally

- Direct reading

- Pressure: 20-bit measurement (Pascals)

- 50 kPa to 150 kPa

- Temperature: 12-bit measurement (°C)

- –40 °C to 85 °C

- Programmable interrupts

- Autonomous data acquisition

- Embedded 32-sample FIFO

- Data logging up to 12 days using the FIFO

- One-second to nine-hour data acquisition rate

- 1.95 V to 3.6 V supply voltage, internally regulated

- 1.6 V to 3.6 V digital interface supply voltage

- Operating temperature from -40 °C to +85 °C

### **3** Applications

- High-accuracy barometry

- Smartphones, tablets, and wearable devices

- GPS applications: dead reckoning, map assist, navigation, enhancement for emergency services

- Weather station equipment

### 4 Ordering information

### Table 1. Ordering information

| Device number Shipping Package |               | Number of ports |        |      | Pressure Type |              | Digital  |           |   |

|--------------------------------|---------------|-----------------|--------|------|---------------|--------------|----------|-----------|---|

|                                |               | None            | Single | Dual | Gauge         | Differential | Absolute | interface |   |

| MPL3150A2                      | Tray          | 98ASA002260D    | •      | _    | _             | _            |          | •         | • |

| MPL3150A2T1                    | Tape and reel | 98ASA002260D    | •      | _    | _             | _            | —        | •         | • |

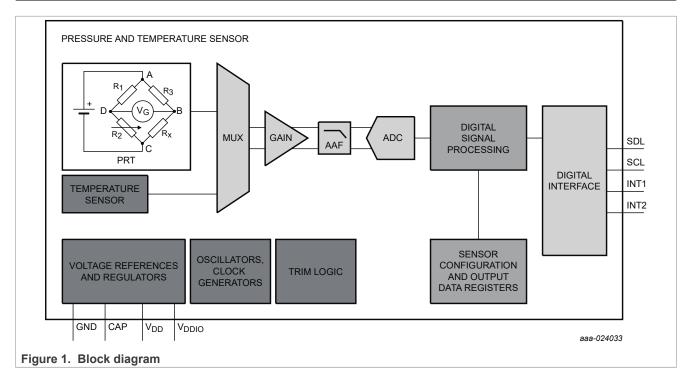

### 5 Block diagram

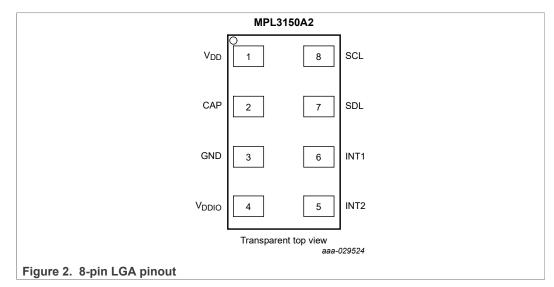

### 6 Pinning information

### 6.1 Pinning

### 6.2 Pin description

### Table 2. Pin description

| Symbol            | Pin | Description                                        |  |

|-------------------|-----|----------------------------------------------------|--|

| V <sub>DD</sub>   | 1   | $V_{DD}$ power supply connection (1.95 V to 3.6 V) |  |

| CAP               | 2   | External capacitor                                 |  |

| GND               | 3   | Ground                                             |  |

| V <sub>DDIO</sub> | 4   | Digital interface power supply (1.62 V to 3.6 V)   |  |

| INT2              | 5   | Pressure interrupt 2                               |  |

| INT1              | 6   | Pressure interrupt 1                               |  |

| SDL               | 7   | l <sup>2</sup> C serial data                       |  |

| SCL               | 8   | I <sup>2</sup> C serial clock                      |  |

MPL3150A2 Product data sheet

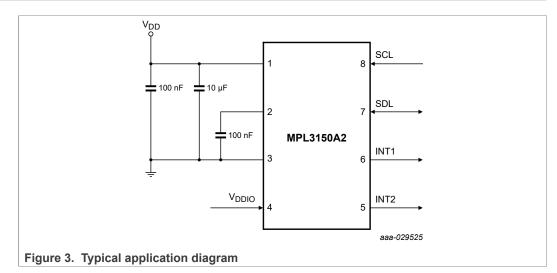

### 7 System connections

The device power is supplied through the V<sub>DD</sub> line. Power supply decoupling capacitors (100 nF ceramic plus 10 µF bulk or 10 µF ceramic) should be placed as near as possible to pin 1 of the device. A second 100 nF capacitor is used to bypass the internal regulator. The functions, threshold, and the timing of the interrupt pins (INT1 and INT2) are user programmable through the I<sup>2</sup>C interface.

### 8 Handling and board mount recommendations

The sensor die is sensitive to light exposure. Direct light exposure through the port hole can lead to varied accuracy of pressure measurement. Avoid such exposure to the port during normal operation.

### 8.1 Methods of handling

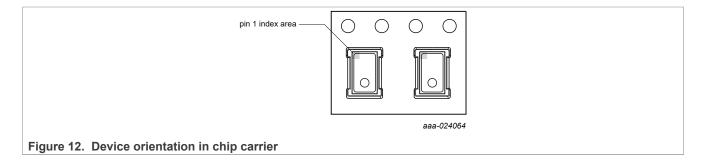

Components can be picked from the carrier tape using either the vacuum assist or the mechanical type pickup heads. A vacuum assist nozzle type is most common due to its lower cost of maintenance and ease of operation. The recommended vacuum nozzle configuration should be designed to make contact with the device directly on the metal cover and avoid vacuum port location directly over the vent hole in the metal cover of the device. Multiple vacuum ports within the nozzle may be required to effectively handle the device and prevent shifting during movement to placement position.

Vacuum pressure required to adequately support the component should be approximately 25 in Hg (85 kPa). This level is typical of in-house vacuum supply. Pickup nozzles are available in various sizes and configurations to suit a variety of component geometries. To select the nozzle best suited for the specific application, NXP recommends that the customer consult their pick and place equipment supplier to determine the correct nozzle. In some cases it may be necessary to fabricate a special nozzle depending on the equipment and speed of operation.

Tweezers or other mechanical forms of handling that have a sharp point are not recommended since they can inadvertently be inserted into the vent hole of the device. This can lead to a puncture of the MEMS element that will render the device inoperable.

### 8.2 Board mount recommendations

Components can be mounted using solder paste stencil, screen printed or dispensed onto the PCB pads prior to placement of the component. The volume of solder paste applied to the PCB is normally sufficient to secure the component during transport to the subsequent reflow soldering process. Use of adhesives to secure the component is not recommended, but where necessary can be applied to the underside of the device.

Solder pastes are available in variety of metal compositions, particle size, and flux types. The solder paste consists of metals and flux required for a reliable connection between the component lead and the PCB pad. Flux aids the removal of oxides that may be present on PCB pads and prevents further oxidation from occurring during the solder process.

The use of a No-Clean (NC) flux is recommended for exposed cavity components. Using pressure spray, wire brush, or other methods of cleaning is not recommended since it can puncture the MEMS device and render it unusable. If cleaning of the PCB is performed, Water Soluble (WS) flux can be used. However, it is recommended the component cavity is protected by adhesive Kapton tape, vinyl cap, or other means prior to the cleaning process. This covering prevents damage to the MEMS device, contamination, and foreign materials from being introduced into device cavity as result of cleaning processes.

Ultrasonic cleaning is not recommended as the frequencies can damage wire bond interconnections and the MEMS device.

### 9 Mechanical and electrical specifications

### 9.1 Terminology

### 9.1.1 Resolution

The resolution of a pressure sensor is the minimum change of pressure that can be reliably measured. The usable resolution of the device is programmable, enabling the user to choose a compromise between acquisition speed, power consumption, and resolution that best fits the application. To simplify the programming, the data is always reported in the same format with differing number of usable bits.

### 9.1.2 Accuracy

### 9.1.2.1 Offset

The offset is defined as the output signal obtained when the reference pressure (a vacuum for an absolute pressure sensor) is applied to the sensor. Offset error affects absolute pressure measurements but not relative pressure measurements. A change in the offset affects the pressure value as it shifts the base reference. An absolute pressure measurement is not the same as relative pressure measurement, where the pressure is compared when raising or lowering pressure in shorter intervals. This would be a walk up a hill, measuring the pressure from start to finish. In the relative case, the offset shifts are shared in the two absolute measurements and negate each other during the pressure calculation.

For the MPL3150A2, the long term offset shift can be removed by adjusting the pressure offset correction. See <u>Section 14.23 "Offset correction registers"</u>. This adjustment is

provided to override the factory programmed values to compensate for offsets introduced by manufacturing and mounting stresses. It is highly recommended that this is utilized to realize the full accuracy potential of the device.

#### 9.1.2.2 Linearity

Linearity compares the slope of the measurement data to that of an ideal transfer function. It refers to how well the transducer output follows the equation  $P_{OUT} = P_{OFF}$  + sensitivity × P straight-line equation over the operating pressure range. The method used by NXP to give the linearity specification is the end-point straight-line method measured at midrange pressure.

#### 9.1.2.3 Absolute pressure

Absolute pressure sensors measure an external pressure relative to a zeropressure reference (vacuum) sealed inside the reference chamber of the die during manufacturing. This standard allows comparison to a standard value set such that 14.7 psi = 101,325 Pa = 1 atm at sea level as a measurement target.

### 9.1.2.4 Span

Span is the value of full-scale output with offset subtracted, representing the full range of the pressure sensor. Ideally the span is a specification over a constant temperature. The device uses internal temperature compensation to remove drift. Span accuracy is the comparison of the measured difference and the actual difference between the highest and lowest pressures in the specified range.

### 9.1.3 Pressure

The device is a high accuracy pressure sensor with integrated data calculation and logging capabilities. Pressure is given in Pascals (Pa), and fractions of a Pa.

### 9.2 Absolute maximum ratings

Absolute maximum ratings are the limits the device can be exposed to without permanently damaging it. Absolute maximum ratings are stress ratings only, functional operation at these ratings is not guaranteed. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

This device contains circuitry to protect against damage due to high static voltage or electrical fields. It is advised, however, that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit.

| Symbol            | Characteristic                              | Value                           | Unit |

|-------------------|---------------------------------------------|---------------------------------|------|

| P <sub>max</sub>  | Maximum applied pressure                    | 500                             | kPa  |

| V <sub>DD</sub>   | Supply voltage                              | -0.3 to 3.6                     | V    |

| V <sub>DDIO</sub> | Interface supply voltage                    | -0.3 to 3.6                     | V    |

| V <sub>IN</sub>   | Input voltage on any control pin (SCL, SDA) | -0.3 to V <sub>DDIO</sub> + 0.3 | V    |

| T <sub>OP</sub>   | Operating temperature range                 | -40 to +85                      | °C   |

| T <sub>STG</sub>  | Storage temperature range                   | -40 to +125                     | °C   |

#### Table 3. Maximum ratings

### I<sup>2</sup>C precision pressure sensor

| Table 4. | ESD | and | latchup | protection | characteristics |

|----------|-----|-----|---------|------------|-----------------|

|----------|-----|-----|---------|------------|-----------------|

| Symbol | Rating                       | Value | Unit |

|--------|------------------------------|-------|------|

| HBM    | Human body model             | ±2000 | V    |

| CDM    | Charge device model          | ±500  | V    |

|        | Latchup current at T = 85 °C | ±100  | mA   |

### Caution

This device is sensitive to mechanical shock. Improper handling can cause permanent damage to the part or cause the part to otherwise fail.

#### Caution This device is sensitive to ElectroStatic Discharge (ESD). Observe precautions for handling electrostatic sensitive devices. Such precautions are described in the ANSI/ESD S20.20, IEC/ST 61340-5, JESD625-A, or equivalent standards.

### 9.3 Mechanical characteristics

#### Table 5. Mechanical characteristics

$V_{DD}$  = 2.5 V, T = 25 °C, over 70 kPa to 150 kPa, unless otherwise noted.

| Symbol          | Parameter                                 | Test conditions                                                                                                                      | Min  | Тур   | Мах | Unit   |

|-----------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----|--------|

| Pressure se     | nsor                                      |                                                                                                                                      | 1    |       |     |        |

| P <sub>FS</sub> | Measurement range                         | Calibrated range                                                                                                                     | 70   |       | 150 | kPa    |

|                 |                                           | Operational range                                                                                                                    | 50   |       | 150 | kPa    |

|                 | Pressure reading noise [1]                | 1x oversample                                                                                                                        |      | 19    |     | Pa RMS |

|                 |                                           | 128x oversample                                                                                                                      |      | 1.5   |     | Pa RMS |

|                 | Pressure absolute accuracy <sup>[2]</sup> | 70 kPa to 150 kPa over 0 °C<br>to 50 °C                                                                                              | -0.4 |       | 0.4 | kPa    |

|                 |                                           | 70 kPa to 150 kPa over −10<br>°C to 70 °C                                                                                            |      | ±0.4  |     | kPa    |

|                 | Pressure relative accuracy                | Relative accuracy during<br>pressure change between<br>90 kPa to 150 kPa at any<br>constant temperature<br>between -10 °C to 50 °C   |      | ±0.05 |     | kPa    |

|                 |                                           | Relative accuracy during<br>changing temperature<br>between -10 °C to 50 °C<br>at any constant pressure<br>between 90 kPa to 150 kPa |      | ±0.15 |     | kPa    |

|                 | Pressure resolution <sup>[3][4]</sup>     |                                                                                                                                      | 0.25 | 1.5   |     | Pa     |

|                 | Output data rate                          | One-shot mode                                                                                                                        |      | 100   |     | Hz     |

|                 |                                           | FIFO mode                                                                                                                            |      |       | 1   | Hz     |

© NXP B.V. 2021. All rights reserved.

I<sup>2</sup>C precision pressure sensor

### Table 5. Mechanical characteristics...continued

V<sub>DD</sub> = 2.5 V, T = 25 °C, over 70 kPa to 150 kPa, unless otherwise noted.

| Symbol          | Parameter                   | Test conditions          | Min | Тур   | Max | Unit |

|-----------------|-----------------------------|--------------------------|-----|-------|-----|------|

|                 | Board mount drift           | After solder reflow      |     | ±0.15 |     | kPa  |

|                 | Long-term drift             | After a period of 1 year |     | ±0.1  |     | kPa  |

| Temperature     | sensor                      | ·                        |     |       | 1   |      |

| T <sub>FS</sub> | Measurement range           |                          | -40 |       | +85 | °C   |

|                 | Temperature accuracy        | @25 °C                   |     | ±1    |     | °C   |

|                 |                             | Over temperature range   |     | ±3    |     | °C   |

| T <sub>OP</sub> | Operating temperature range |                          | -40 |       | +85 | °C   |

Oversample (OSR) modes internally combine and average samples to reduce noise. Pressure offset drift of ±20 Pa from 0 s to 120 s from 25 °C to 40 °C. Verified by characterization.

Reference pressure = 101.325 kPa (sea level).

[1] [2] [3] [4] At 128x oversample ratio.

### 9.4 Electrical characteristics

Table 6. Electrical characteristics

@  $V_{DD}$  = 2.5 V, T = 25 °C unless otherwise noted.

| Symbol             | Parameter                                       | Test conditions                          | Min  | Тур | Мах | Unit              |

|--------------------|-------------------------------------------------|------------------------------------------|------|-----|-----|-------------------|

| V <sub>DDIO</sub>  | I/O supply voltage                              | —                                        | 1.62 | 1.8 | 3.6 | V                 |

| V <sub>DD</sub>    | Operating supply voltage                        | —                                        | 1.95 | 2.5 | 3.6 | V                 |

| I <sub>DD</sub>    | Integrated current 1 update per second          | Highest speed mode<br>oversample = 1     | _    | 8.5 | _   | μΑ                |

|                    |                                                 | Standard mode oversample<br>= 16         | _    | 40  | _   | μA                |

|                    |                                                 | High-resolution mode<br>oversample = 128 | _    | 265 |     | μA                |

| I <sub>DDMAX</sub> | Max current during acquisition and conversion   | During acquisition/<br>conversion        | _    | 2   | —   | mA                |

| IDDSTBY            | Supply current drain in STANDBY mode            | STANDBY mode selected<br>SBYB = 0        | _    | 2   |     | μA                |

| VIH                | Digital high-level input<br>voltage<br>SCL, SDA | _                                        | 0.75 |     |     | V <sub>DDIO</sub> |

| VIL                | Digital low-level input voltage SCL, SDA        | —                                        | _    | -   | 0.3 | V <sub>DDIO</sub> |

| VOH                | High-level output voltage<br>INT1, INT2         | I <sub>O</sub> = 500 μA                  | 0.9  |     | _   | V <sub>DDIO</sub> |

| VOL                | Low-level output voltage<br>INT1, INT2          | I <sub>O</sub> = 500 μA                  | _    | _   | 0.1 | V <sub>DDIO</sub> |

| VOLS               | Low-level output voltage<br>SDA                 | I <sub>O</sub> = 500 μA                  | _    | _   | 0.1 | V <sub>DDIO</sub> |

I<sup>2</sup>C precision pressure sensor

### Table 6. Electrical characteristics...continued

@  $V_{DD}$  = 2.5 V, T = 25 °C unless otherwise noted.

| Symbol                      | Parameter                                                                                                                                                                      | Test conditions      | Min     | Тур | Max  | Unit |  |  |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------|-----|------|------|--|--|

| T <sub>ON</sub>             | Turn-on time <sup>[1][2][3]</sup>                                                                                                                                              | High-speed mode      | _       |     | 60   | ms   |  |  |

|                             |                                                                                                                                                                                | High-resolution mode | _       |     | 1000 | ms   |  |  |

| T <sub>OP</sub>             | Operating temperature range                                                                                                                                                    |                      | -40     | 25  | +85  | °C   |  |  |

| I <sup>2</sup> C addressing |                                                                                                                                                                                | 1                    | 1       | 1   |      | ,    |  |  |

| I <sup>2</sup> C Address    | —                                                                                                                                                                              |                      | 0x62 He |     | Hex  |      |  |  |

|                             | The device uses 7-bit addressing and does not acknowledge general call address 000 0000. Clent address has been set to 62h or 110 0010. 8-bit read is C5h, 8-bit write is C4h. |                      |         |     |      |      |  |  |

Time to obtain valid data from STANDBY mode to ACTIVE mode [1]

[2] [3] High-speed mode is achieved by setting the oversample rate of 1x.

High-resolution mode is achieved by setting the oversample to 128x.

#### **Digital interface** 10

The registers embedded inside the device are accessed through an  $I^2C$  serial interface.

Table 7. Serial interface pin descriptions

| Name | Description                   |

|------|-------------------------------|

| SCL  | I <sup>2</sup> C serial clock |

| SDA  | l <sup>2</sup> C serial data  |

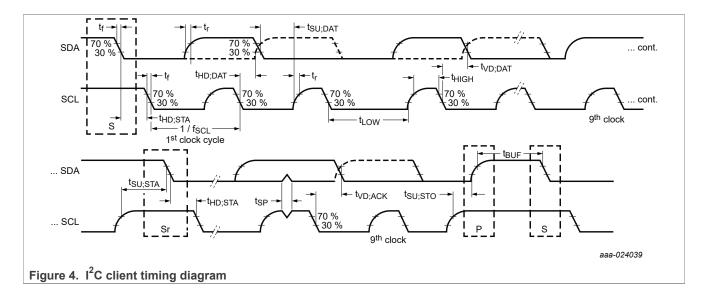

### 10.1 I<sup>2</sup>C characteristics

### Table 8. I<sup>2</sup>C client timing values

All values referred to VIH(min) and VIL(max) levels.

| Symbol              | Parameter                                      | l <sup>2</sup> C                     | Unit                   |     |     |

|---------------------|------------------------------------------------|--------------------------------------|------------------------|-----|-----|

|                     |                                                | Condition                            | Min                    | Max | _   |

| f <sub>SCL</sub>    | SCL clock frequency                            | Pull-up = 1 k $\Omega$ , Cb = 400 pF | 0                      | 400 | kHz |

| f <sub>SCL</sub>    | SCL clock frequency                            | Pull-up = 1 kΩ, Cb = 20 pF           | 0                      | 4   | MHz |

| t <sub>BUF</sub>    | Bus free time between STOP and START condition | _                                    | 1.3                    |     | μs  |

| t <sub>HD;STA</sub> | Repeated START hold time                       | _                                    | 0.6                    |     | μs  |

| t <sub>SU;STA</sub> | Repeated START setup time                      | _                                    | 0.6                    |     | μs  |

| t <sub>SU;STO</sub> | STOP condition setup time                      | _                                    | 0.6                    |     | μs  |

| t <sub>HD;DAT</sub> | SDA data hold time <sup>[1][2][3]</sup>        | _                                    | 50                     |     | ns  |

| t <sub>SU;DAT</sub> | SDA setup time <sup>[4]</sup>                  | _                                    | 100                    |     | ns  |

| t <sub>LOW</sub>    | SCL clock low time                             | _                                    | 1.3                    |     | μs  |

| t <sub>HIGH</sub>   | SCL clock high time                            | _                                    | 0.6                    |     | μs  |

| t <sub>r</sub>      | SDA and SCL rise time <sup>[5]</sup>           | _                                    | 20 + 0.1C <sub>b</sub> | 300 | ns  |

| t <sub>f</sub>      | SDA and SCL fall Time <sup>[2][5][6][7]</sup>  | _                                    | 20+ 0.1C <sub>b</sub>  | 300 | ns  |

## Table 8. I<sup>2</sup>C client timing values...continued All values referred to VIH(min) and VIL(max) levels.

| Symbol          | Parameter I <sup>2</sup> C                                               |           |     |     | Unit |

|-----------------|--------------------------------------------------------------------------|-----------|-----|-----|------|

|                 |                                                                          | Condition | Min | Max |      |

| t <sub>SP</sub> | Pulse width of spikes that are<br>suppressed by internal input<br>filter | _         |     | 50  | ns   |

[1] t<sub>HD;DAT</sub> is the data hold time that is measured from the falling edge of SCL, applies to data in transmission and the acknowledge.

[2] The device must internally provide a hold time of at least 300 ns for the SDA signal (with respect to the VIH(min) of the SCL signal) to bridge the undefined region of the falling edge of SCL

[3] The maximum t<sub>HD;DAT</sub> must be less than the maximum of t<sub>VD;DAT</sub> or t<sub>VD;ACK</sub> by a transition time. This device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal.

[4] A fast mode I<sup>2</sup>C device can be used in a standard mode I<sup>2</sup>C system, but the requirement t<sub>SU;DAT</sub> 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>r</sub>(max) + t<sub>SU;DAT</sub> = 1000 + 250 = 1250 ns (according to the standard mode I<sup>2</sup>C specification) before the SCL line is released. Also the acknowledge timing must meet this set-up time.

[5] Cb = Total capacitance of one bus line in pF.

[6] The maximum tr for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time for the SDA output stage tr is specified at 250 ns. This allows series protection resistors to be connected in between the SDA and the SCL pins and the SDA/SCL bus lines without exceeding the maximum specified tr.

[7] In fast mode plus, fall time is specified the same for both output stage and bus timing. If series resistors are used, designers should allow for this when considering bus timing.

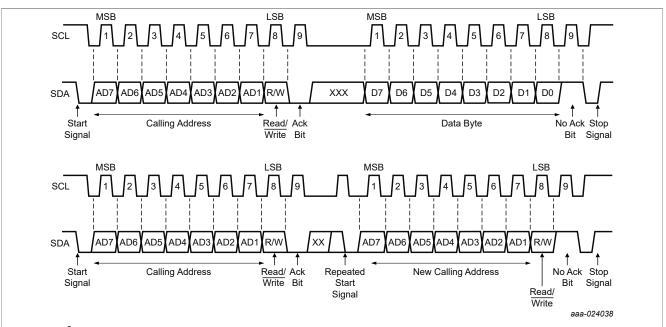

### 10.2 I<sup>2</sup>C operation

The transaction on the bus is started through a start condition (START) signal. START condition is defined as a HIGH to LOW transition on the data line while the SCL line is held HIGH. After START has been transmitted by the host, the bus is considered busy. The next byte of data transmitted after START contains the client address in the first 7 bits, and the eighth bit tells whether the host is receiving data from the client or transmitting data to the client. When an address is sent, each device in the system compares the first 7 bits after a start condition with its address. If they match, the device considers itself addressed by the host. The ninth clock pulse, following the client address byte (and each subsequent byte) is the acknowledge (ACK). The transmitter must release the SDA line during the ACK period. The receiver must then pull the data line low so that it remains stable low during the high period of the acknowledge clock period.

The number of bytes per transfer is unlimited. If the host cannot receive another complete byte of data until it has performed some other function, it can hold the clock line, SCL low to force the transmitter into a wait state. Data transfer only continues when the host is ready for another byte and releases the clock line.

A low to high transition on the SDA line while the SCL line is high is defined as a stop condition (STOP). A data transfer is always terminated by a STOP. A host may also issue a repeated START during a data transfer. Device expects repeated STARTs to be used to randomly read from specific registers.

The standard 7-bit I<sup>2</sup>C client address is 62h or 110 0010. 8-bit read is C5h, 8-bit write is C4h.

I<sup>2</sup>C precision pressure sensor

Figure 5. I<sup>2</sup>C bus transmission signals

Consult factory for alternate addresses. See the application note titled Sensor I<sup>2</sup>C Setup and FAQ (document AN4481).

I<sup>2</sup>C precision pressure sensor

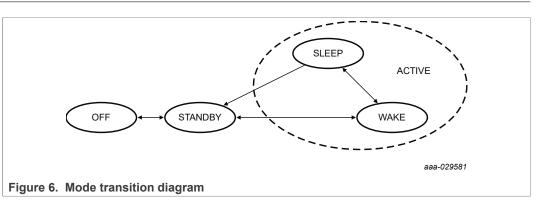

### 11 Modes of operation

Table 9. Mode of operation description

| Mode    | I <sup>2</sup> C-bus state                                           | V <sub>DD</sub> | Condition                        | Function description                                                      |

|---------|----------------------------------------------------------------------|-----------------|----------------------------------|---------------------------------------------------------------------------|

| OFF     | Powered down                                                         | < 1.62 V        | < V <sub>DD</sub> + 0.3 V        | Device is powered off.                                                    |

| STANDBY | I <sup>2</sup> C/SPI<br>communication with<br>the device is possible | ON              | SBYB bit of CTRL_REG1 is cleared | Only POR and digital blocks are enabled.<br>Analog subsystem is disabled. |

| ACTIVE  | I <sup>2</sup> C/SPI<br>communication with<br>the device is possible | ON              | SBYB bit of CTRL_REG1 is set     | All blocks are enabled (POR, digital, analog).                            |

### 11.1 OFF

Unit is powered down and has no operating functionality.  $V_{DD}$  and  $V_{DDIO}$  are not powered.

### 11.2 STANDBY

The digital sections are operational and the unit is capable of receiving commands and delivering stored data. The analog sections are off. The part is waiting for CTRL\_REG1 to be configured and the part to enter active mode.

### 11.3 **ACTIVE**

Both analog and digital sections are running. The unit is capable of gathering new data, and accepting commands. The device is fully functional.

### 12 Quick start setup

For more information, see application note titled Data Manipulation and Basic Settings of the MPL3115A2 Command Line Interface (document AN4519).

### **13** Functionality

The device is a low-power, high accuracy, digital output barometer, and thermometer, packaged in a  $3 \times 5 \times 1.1$  mm form factor. The complete device includes a sensing element, analog and digital signal processing and an  $I^2C$  interface.

In operational mode, the device outputs both pressure and temperature.

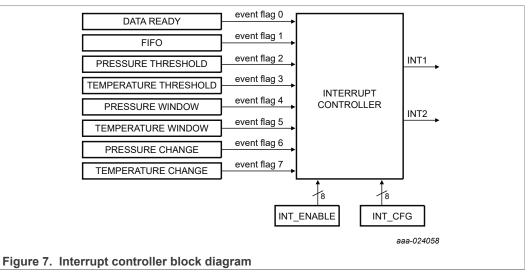

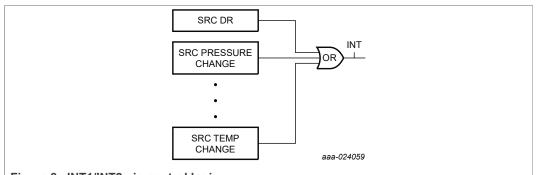

Power consumption and sensitivity are programmable where the data oversampling ratio can be set to balance current consumption and noise/resolution. Serial interface communication is through an I<sup>2</sup>C interface therefore making the device particularly suitable for direct interfacing with a microcontroller. The device features two independently programmable interrupt signals INT1 and INT2. These can be set to generate an interrupt signal when a new set of pressure and temperature data is available, thereby simplifying data acquisition for the host controller. These interrupt pins can also be configured to generate interrupts when a user programmed set of conditions are met (see Section 13.6 "External interrupts").

Examples are:

- interrupt can be triggered when a single new data acquisition is ready

- when a desired number of samples are stored within the internal FIFO

- when a change of pressure or temperature is detected.

### **13.1 Factory calibration**

The device is factory calibrated for sensitivity, offset for both temperature and pressure measurements. Trim values are stored on-chip, in non-volatile memory (NVM). In normal use, further calibration is not necessary. However, in order to realize the highest possible accuracy, the device allows the user to override the factory set offset values after power-up. The user adjustments are stored in volatile registers. The factory calibration values are not affected, and are always used by default on power-up.

### 13.2 Barometer function

The internal sensor gives an absolute pressure signal. The absolute pressure signal is processed to provide a scaled pressure signal. The combination of a high performance sensor and the signal processing enable resolution of pressures below 1 Pa.

Pressure is reported as 20-bit unsigned data in Pascals.

### **13.3 Temperature function**

The unit contains a high-resolution temperature sensor that provides data to the user via a 16-bit data register, as well as for internal compensation of the pressure sensor.

### 13.4 Autonomous data acquisition

The unit can be programmed to periodically capture pressure and temperature data. Up to 32 data acquisitions can be stored in the internal FIFO. The interval between acquisitions is programmable from one second to nine hours.

Data collection capabilities: (up to 32 samples over 12 days). The unit can also be programmed to make a single reading and then go to standby mode.

### 13.5 FIFO

A 32-sample FIFO is incorporated to minimize the overhead of collecting multiple data samples. The FIFO stores both temperature and pressure data. The device can be programmed to autonomously collect data at programmed intervals and store the data in the FIFO. FIFO interrupts can be triggered by watermark full or data contention (FIFO GATE) events.

MPL3150A2

### 13.6 External interrupts

Two independent interrupt out pins are provided. The configuration of the pins is programmable (polarity, open-drain, or push/pull.) Any one of the internal interrupt sources can be routed to either pin.

### 13.6.1 Reach target threshold pressure (SRC\_PTH)

The interrupt flag is set on reaching the value stored in the pressure target register. Additionally, a window value provides the ability to signal when the target is nearing the value in the pressure target register from either above or below.

#### Example:

• Set pressure alert to 100.0 kPa and window value to 5 kPa, interrupt can be sent passing 95 kPa, 100 kPa, and 105 kPa.

**Note:** When the window value is set to 0, then the interrupt will only be generated when reaching or crossing the target value.

### 13.6.2 Reach window target pressure (SRC\_PW)

The interrupt flag is set when the pressure value is within the window defined by the following formula:

$Window = P_T GT_{MSB,LSB} \pm P_W IND_{MSB,LSB}$

**Note:** If the P\_WND value is set to 0, no interrupt is generated.

### 13.6.3 Reach target threshold temperature (SRC\_TTH)

Interrupt flag is set on reaching the value stored in the temperature target register. Additionally a window value provides ability to signal when the target is nearing from either above or below the value in the temperature target register.

**Note:** When the window value is set to 0, then the interrupt will only be generated when reaching or crossing the target value.

### 13.6.4 Reach window target temperature (SRC\_TW)

The interrupt flag is set when the temperature value is within the window defined by the following formula:

$Window = T_TGT \pm T_WIND$

*Note:* No interrupt is generated if the T\_WND value is set to 0.

### 13.6.5 Pressure change (SRC\_PCHG)

Interrupt flag is set if sequential pressure acquisitions exceed value stored in pressure window value register.

### 13.6.6 Temperature change (SRC\_TCHG)

Interrupt flag is set if sequential temperature acquisitions exceed the value stored in pressure window value register.

MPL3150A2

### 13.6.7 Data ready

Interrupt flag is set when new data or a data overwrite event has occurred. PTOW and/or PTDR (DR\_STATUS register) must be set for an interrupt to be generated.

#### 13.6.8 FIFO event

Interrupt flag is set when either an overflow or watermark event has occurred. For more information, see <u>Section 14.8 "FIFO setup registers"</u>.

#### 13.6.9 Pressure and temperature delta

Registers show the differences from the last pressure and temperature samples.

#### 13.6.10 Min/max data value storage

Registers record the minimum and maximum pressure and temperature.

### 14 Register descriptions

#### Table 10. Register address map

| Register<br>Address | Name            | Access | Reset<br>value | Description                                            | Reset when<br>STBY to<br>Active | Comment                                                                               | Auto-increment<br>address | Reference      |

|---------------------|-----------------|--------|----------------|--------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------|---------------------------|----------------|

| 00h                 | STATUS          | R      | 00h            | Sensor status register <sup>[1]</sup> . <sup>[2]</sup> | Yes                             | Alias for DR_STATUS or F_<br>STATUS                                                   | 01h                       | Section 14.1   |

| 01h                 | OUT_P_MSB       | R      | 00h            | Pressure data out MSB <sup>[1][2]</sup>                | Yes                             | Bits 12 to 19 of 20-bit real-time<br>pressure sample.<br>Root pointer to pressure and | 02h                       | Section 14.3   |

|                     |                 |        |                |                                                        |                                 | temperature FIFO data.                                                                | 01h                       |                |

| 02h                 | OUT_P_CSB       | R      | 00h            | Pressure data out CSB <sup>[1][2]</sup>                | Yes                             | Bits 4 to 11 of 20-bit real-time pressure sample                                      | 03h                       | Section 14.3   |

| 03h                 | OUT_P_LSB       | R      | 00h            | Pressure data out LSB <sup>[1][2]</sup>                | Yes                             | Bits 0 to 3 of 20-bit real-time pressure sample                                       | 04h                       | Section 14.3   |

| 04h                 | OUT_T_MSB       | R      | 00h            | Temperature data out MSB                               | Yes                             | Bits 4 to 11 of 12-bit real-time temperature sample                                   | 05h                       | Section 14.4   |

| 05h                 | OUT_T_LSB       | R      | 00h            | Temperature data out LSB                               | Yes                             | Bits 0 to 3 of 12-bit real-time temperature sample                                    | 00h                       | Section 14.4   |

| 06h/00h             | DR_STATUS       | R      | 00h            | Sensor status register [1][2]                          | Yes                             | Data ready status information                                                         | 07h                       | Section 14.2   |

| 07h                 | OUT_P_DELTA_MSB | R      | 00h            | Pressure data out delta MSB<br>[1][2]                  | Yes                             | Bits 12 to 19 of 20-bit pressure change data                                          | 08h                       | Section 14.5   |

| 08h                 | OUT_P_DELTA_CSB | R      | 00h            | Pressure data out delta CSB                            | Yes                             | Bits 4 to 11 of 20-bit pressure change data                                           | 09h                       | Section 14.5   |

| 09h                 | OUT_P_DELTA_LSB | R      | 00h            | Pressure data out delta LSB [1][2]                     | Yes                             | Bits 0 to 3 of 20-bit pressure change data                                            | 0Ah                       | Section 14.5   |

| 0Ah                 | OUT_T_DELTA_MSB | R      | 00h            | Temperature data out delta MSB <sup>[1][2]</sup>       | Yes                             | Bits 4 to 11 of 12-bit temperature change data                                        | 0Bh                       | Section 14.6   |

| 0Bh                 | OUT_T_DELTA_LSB | R      | 00h            | Temperature data out delta LSB $^{[1][2]}$             | Yes                             | Bits 0 to 3 of 12-bit temperature change data                                         | 06h                       | Section 14.6   |

| 0Ch                 | WHO_AM_I        | R      | C4h            | Device identification register                         | No                              | Fixed device ID number                                                                | 0Dh                       | Section 14.7   |

| 0Dh                 | F_STATUS        | R      | 00h            | FIFO status register <sup>[1][2]</sup>                 | Yes                             | FIFO status: no FIFO event detected                                                   | 0Eh                       | Section 14.8.1 |

| 0Eh/01h             | F_DATA          | R      | 00h            | FIFO 8-bit data access [1][2]                          | Yes                             | FIFO 8-bit data access                                                                | 0Eh                       | Section 14.8.2 |

| 0Fh                 | F_SETUP         | R/W    | 00h            | FIFO setup register [1][3]                             | No                              | FIFO setup                                                                            | 10h                       | Section 14.8.3 |

| 10h                 | TIME_DLY        | R      | 00h            | Time delay register <sup>[1][2]</sup>                  | Yes                             | Time since FIFO overflow                                                              | 11h                       | Section 14.9   |

| 11h                 | SYSMOD          | R      | 00h            | System mode register [2]                               | Yes                             | Current system mode                                                                   | 12h                       | Section 14.10  |

| 12h                 | INT_SOURCE      | R      | 00h            | Interrupt source register [1]                          | No                              | Interrupt status                                                                      | 13h                       | Section 14.11  |

| 13h                 | PT_DATA_CFG     | R/W    | 00h            | PT data configuration register                         | No                              | Data event flag configuration                                                         | 14h                       | Section 14.12  |

MPL3150A2

© NXP B.V. 2021. All rights reserved.

### I<sup>2</sup>C precision pressure sensor

| Register<br>Address | Name      | Access | Reset value | Description                                        | Reset when<br>STBY to<br>Active | Comment                            | Auto-increment<br>address | Reference       |

|---------------------|-----------|--------|-------------|----------------------------------------------------|---------------------------------|------------------------------------|---------------------------|-----------------|

| 14h                 | Reserved  | R      |             | -                                                  | _                               | -                                  | 15h                       | Section 14.13   |

| 15h                 | Reserved  | R      |             | -                                                  | _                               | -                                  | 16h                       | Section 14.13   |

| 16h                 | P_TGT_MSB | R/W    | 00h         | Pressure target MSB [1][3]                         | No                              | Pressure target value bits 8 to 15 | 17h                       | Section 14.14   |

| 17h                 | P_TGT_LSB | R/W    | 00h         | Pressure target LSB [1][3]                         | No                              | Pressure target value bits 0 to 7  | 18h                       | Section 14.14   |

| 18h                 | T_TGT     | R/W    | 00h         | Temperature target register [1][3]                 | No                              | Temperature target value           | 19h                       | Section 14.15   |

| 19h                 | P_WND_MSB | R/W    | 00h         | Pressure window MSB <sup>[1][3]</sup>              | No                              | Pressure window value bits 8 to 15 | 1Ah                       | Section 14.16   |

| 1Ah                 | P_WND_LSB | R/W    | 00h         | Pressure window LSB <sup>[1][3]</sup>              | No                              | Pressure window value bits 0 to 7  | 1Bh                       | Section 14.16   |

| 1Bh                 | T_WND     | R/W    | 00h         | Temperature window register                        | No                              | Temperature window value           | 1Ch                       | Section 14.17   |

| 1Ch                 | P_MIN_MSB | R/W    | 00h         | Minimum pressure data out MSB <sup>[1][3]</sup>    | No                              | Minimum pressure bits 12 to 19     | 1Dh                       | Section 14.18   |

| 1Dh                 | P_MIN_CSB | R/W    | 00h         | Minimum pressure data out CSB <sup>[1][3]</sup>    | No                              | Minimum pressure bits 4 to 11      | 1Eh                       | Section 14.18   |

| 1Eh                 | P_MIN_LSB | R/W    | 00h         | Minimum pressure data out LSB <sup>[1][3]</sup>    | No                              | Minimum pressure bits 0 to 3       | 1Fh                       | Section 14.18   |

| 1Fh                 | T_MIN_MSB | R/W    | 00h         | Minimum temperature data out MSB <sup>[1][3]</sup> | No                              | Minimum temperature bits 8 to15    | 20h                       | Section 14.20   |

| 20h                 | T_MIN_LSB | R/W    | 00h         | Minimum temperature data out LSB <sup>[1][3]</sup> | No                              | Minimum temperature bits 0 to 7    | 21h                       | Section 14.20   |

| 21h                 | P_MAX_MSB | R/W    | 00h         | Maximum pressure data out MSB <sup>[1][3]</sup>    | No                              | Maximum pressure bits 12 to 19     | 22h                       | Section 14.19   |

| 22h                 | P_MAX_CSB | R/W    | 00h         | Maximum pressure data out CSB <sup>[1][3]</sup>    | No                              | Maximum pressure bits 4 to 11      | 23h                       | Section 14.19   |

| 23h                 | P_MAX_LSB | R/W    | 00h         | Maximum pressure data out LSB <sup>[1][3]</sup>    | No                              | Maximum pressure bits 0 to 3       | 24h                       | Section 14.19   |

| 24h                 | T_MAX_MSB | R/W    | 00h         | Maximum temperature data out MSB <sup>[1][3]</sup> | No                              | Maximum temperature bits 8 to 15   | 25h                       | Section 14.21   |

| 25h                 | T_MAX_LSB | R/W    | 00h         | Maximum temperature data out LSB <sup>[1][3]</sup> | No                              | Maximum temperature bits 0 to 7    | 26h                       | Section 14.21   |

| 26h                 | CTRL_REG1 | R/W    | 00h         | Control register 1 [1][4]                          | No                              | Modes, oversampling                | 27h                       | Section 14.22.1 |

| 27h                 | CTRL_REG2 | R/W    | 00h         | Control register 2 <sup>[1]</sup>                  | No                              | Acquisition time step              | 28h                       | Section 14.22.2 |

| 28h                 | CTRL_REG3 | R/W    | 00h         | Control register 3 [1][4]                          | No                              | Interrupt pin configuration        | 29h                       | Section 14.22.3 |

| 29h                 | CTRL_REG4 | R/W    | 00h         | Control register 4 [1][4]                          | No                              | Interrupt enables                  | 2Ah                       | Section 14.22.4 |

| 2Ah                 | CTRL_REG5 | R/W    | 00h         | Control register 5 [1][4]                          | No                              | Interrupt output pin assignment    | 2Bh                       | Section 14.22.5 |

| 2Bh                 | OFF_P     | R/W    | 00h         | Pressure data user offset register                 | No                              | Pressure data offset               | 2Ch                       | Section 14.23   |

| 2Ch                 | OFF_T     | R/W    | 00h         | Temperature data user offset register              | No                              | Temperature data offset            | 2Dh                       | Section 14.23.2 |

| 2Dh                 | Reserved  | R      | _           | -                                                  | _                               | -                                  | 0Ch                       | Section 14.23.3 |

#### Table 10. Register address map...continued

Register contents are preserved when transitioning from ACTIVE to STANDBY mode Register contents are reset when transitioning from STANDBY to ACTIVE mode. Register contents can be modified anytime in STANDBY or ACTIVE mode. [1]

[2] [3] [4] Modification of this register's contents can only occur when device in STANDBY mode except the SBYB, OST, and RST bit fields in CTRL\_REG1 register.

### Table 11. Register address map: Area A (F\_Mode = 0, FIFO disabled)

| Register<br>Address | Name                     | Access | Reset<br>value | Description            | Reset when<br>STBY to<br>Active | Comment                                             | Auto-increment<br>address |     | Reference    |

|---------------------|--------------------------|--------|----------------|------------------------|---------------------------------|-----------------------------------------------------|---------------------------|-----|--------------|

| 00h/06h             | DR_STATUS <sup>[1]</sup> | R      | 00h            | Sensor status register | Yes                             | DR_STATUS                                           | 01h                       |     | Section 14.2 |

| 01h                 | OUT_P_MSB <sup>[1]</sup> | R      | 00h            | Pressure data out MSB  | Yes                             | Bits12 to 19 of 20-bit real-time pressure sample.   | 02h                       |     | Section 14.3 |

|                     |                          |        |                |                        |                                 | Root pointer to pressure and temperature FIFO data. |                           | 01h |              |

MPL3150A2

16 / 46

© NXP B.V. 2021. All rights reserved.

### I<sup>2</sup>C precision pressure sensor

| Register<br>Address | Name                     | Access | Reset<br>value | Description              | Reset when<br>STBY to<br>Active | Comment                                             | Auto-increment<br>address | Reference    |

|---------------------|--------------------------|--------|----------------|--------------------------|---------------------------------|-----------------------------------------------------|---------------------------|--------------|

| 02h                 | OUT_P_CSB <sup>[1]</sup> | R      | 00h            | Pressure data out CSB    | Yes                             | Bits 4 to 11 of 20-bit real-time<br>pressure sample | 03h                       | Section 14.3 |

| 03h                 | OUT_P_LSB <sup>[1]</sup> | R      | 00h            | Pressure data out LSB    | Yes                             | Bits 0 to 3 of 20-bit real-time<br>pressure sample  | 04h                       | Section 14.3 |

| 04h                 | OUT_T_MSB <sup>[1]</sup> | R      | 00h            | Temperature data out MSB | Yes                             | Bits 4 to 11 of 12-bit real-time temperature sample | 05h                       | Section 14.4 |

| 05h                 | OUT_T_LSB [1]            | R      | 00h            | Temperature data out LSB | Yes                             | Bits 0 to 3 of 12-bit real-time temperature sample  | 00h                       | Section 14.4 |

#### Table 11. Register address map: Area A (F\_Mode = 0, FIFO disabled)...continued

[1] The Registers in Area A from 00h to 05h depend on the F\_MODE bit setting in FIFO Setup Register (F\_SETUP).

• F MODE = 00, FIFO is disabled.

• F MODE = 01 is circular buffer.

• F\_MODE = 10 is full stop mode.

#### Table 12. Register address map: Area A (F\_Mode > 0, FIFO in circular buffer or full stop mode)

| Register<br>Address | Name                                            | Access | Reset<br>value | Description            | Reset when<br>STBY to<br>Active | Comment  | Auto-<br>increment<br>address | Reference      |

|---------------------|-------------------------------------------------|--------|----------------|------------------------|---------------------------------|----------|-------------------------------|----------------|

| 00h/0Dh             | F_STATUS <sup>[1]</sup>                         | R      | 00h            | Sensor status register | Yes                             | F_STATUS | 01h                           | Section 14.8.1 |

| 01h                 | F_DATA <sup>[1]</sup>                           | R      | 00h            | FIFO 8-bit data access | Yes                             | -        | 01h                           | Section 14.8.2 |

| 02h                 | Read to reserved area returns 00 <sup>[1]</sup> | -      | 00h            | _                      | n.a.                            | _        | 03h                           | -              |

| 03h                 | Read to reserved area returns 00 <sup>[1]</sup> | -      | 00h            | _                      | n.a.                            | _        | 04h                           | -              |

| 04h                 | Read to reserved area returns 00 <sup>[1]</sup> | -      | 00h            | _                      | n.a.                            | _        | 05h                           | -              |

| 05h                 | Read to reserved area returns 00 <sup>[1]</sup> | -      | 00h            | _                      | n.a.                            | _        | 00h                           | _              |

[1] The registers in area A from 00h to 05h depend on the F\_MODE bit setting in FIFO setup register (F\_SETUP).

• F\_MODE = 00, FIFO is disabled.

• F\_MODE = 01 is circular buffer.

• F\_MODE = 10 is full stop mode.

### 14.1 STATUS - sensor status register (address 00h)

The aliases allow the STATUS register to be read easily before reading the current pressure or temperature data, the delta pressure or temperature data, or the FIFO data, using the register address auto-incrementing mechanism.

### Table 13. Alias for DR\_Status (06h) or F\_Status (0Dh) registers

| FIFO data enabled<br>mode bit setting | Status register alias |

|---------------------------------------|-----------------------|

| F_MODE = 00 <sup>[1]</sup>            | 00h = DR_STATUS (06h) |

| F_MODE >00                            | 00h = F_STATUS (0Dh)  |

[1] The F\_MODE is defined in <u>Section 14.8.3 " F\_SETUP- FIFO setup register (address 0Fh)"</u>

### 14.2 DR\_STATUS - status register (address 06h)

The DR\_STATUS register provides the acquisition status information on a per sample basis, and reflects real-time updates to the OUT\_P and OUT\_T registers. The same STATUS register can be read through an alternate address 00h (F\_Mode = 00).

### I<sup>2</sup>C precision pressure sensor

| Table 14. Dr_STATOS - status register (autress off) bit anotation |      |     |     |          |      |     |     |          |  |  |

|-------------------------------------------------------------------|------|-----|-----|----------|------|-----|-----|----------|--|--|

| Bit                                                               | 7    | 6   | 5   | 4        | 3    | 2   | 1   | 0        |  |  |

| Symbol                                                            | PTOW | POW | TOW | reserved | PTDR | PDR | TDR | reserved |  |  |

| Reset                                                             | 0    | 0   | 0   | 0        | 0    | 0   | 0   | 0        |  |  |

| Access                                                            | R    | R   | R   | R        | R    | R   | R   | R        |  |  |

### Table 14. DR\_STATUS - status register (address 06h) bit allocation

#### Table 15. DR\_STATUS - status register (address 06h) bit description

| Bit | Symbol              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PTOW <sup>[1]</sup> | Pressure or temperature data overwrite. PTOW is set to 1 whenever new data is acquired before completing the retrieval of the previous set. This event occurs when the content of at least one data register (OUT_P, OUT_T) has been overwritten. PTOW is cleared when the high-bytes of the data (OUT_P_MSB or OUT_T_MSB) are read, when F_MODE is zero. PTOW is cleared by reading F_DATA register when F_MODE > 0.<br><b>0</b> — No data overwrite has occurred (reset value)<br><b>1</b> — Previous pressure or temperature data was overwritten by new pressure or temperature data before it was read |

| 6   | POW <sup>[2]</sup>  | Pressure data overwrite. POW is set to 1 whenever a new pressure acquisition is completed before the retrieval of the previous data. When this occurs, the previous data is overwritten. POW is cleared anytime OUT_P_MSB register is read, when F_MODE is zero. POW is cleared by reading F_DATA register when F_MODE > 0.<br><b>0</b> — No data overwrite has occurred (reset value)<br><b>1</b> — Previous pressure data was overwritten by new pressure data before it was read                                                                                                                         |

| 5   | TOW <sup>[3]</sup>  | Temperature data overwrite. TOW is set to 1 whenever a new temperature acquisition is completed before the retrieval of the previous data. When this occurs, the previous data is overwritten. TOW is cleared anytime OUT_T_MSB register is read, when F_MODE is zero. TOW is cleared by reading F_DATA register when F_MODE > 0.<br><b>0</b> — No data overwrite has occurred (reset value)<br><b>1</b> — Previous temperature data was overwritten by new temperature data before it was read                                                                                                             |

| 4   | reserved            | This bit is reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3   | PTDR <sup>[1]</sup> | Pressure or temperature data ready. PTDR signals that a new acquisition for either pressure<br>or temperature is available. PTDR is cleared anytime OUT_P_MSB or OUT_T_MSB register<br>is read, when F_MODE is zero. PTDR is cleared by reading F_DATA register when F_MODE<br>> 0.<br>0 — No new set of data ready (reset value)<br>1 — A new set of data is ready                                                                                                                                                                                                                                         |

| 2   | PDR <sup>[2]</sup>  | New pressure data available. PDR is set to 1 whenever a new pressure data acquisition is completed. PDR is cleared anytime OUT_P_MSB register is read, when F_MODE is zero. PDR is cleared by reading F_DATA register when F_MODE > 0.<br><b>0</b> — No new pressure data is available (reset value)<br><b>1</b> — A new set of pressure data is ready                                                                                                                                                                                                                                                      |

| 1   | TDR <sup>[3]</sup>  | New temperature data available. TDR is set to 1 whenever a temperature data acquisition is completed. TDR is cleared anytime OUT_T_MSB register is read, when F_MODE is zero. TDR is cleared by reading F_DATA register when F_MODE > 0.<br><b>0</b> — No new temperature data ready (reset value)<br><b>1</b> — A new temperature data is ready                                                                                                                                                                                                                                                            |

| 0   | reserved            | This bit is reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

[1] PTDR and PTOW flag generation requires the DREM event flag generator to be enabled in the PT data configuration register (PT\_DATA\_CFG).

© NXP B.V. 2021. All rights reserved.

MPL3150A2

### I<sup>2</sup>C precision pressure sensor

- [2] PDR and POW flag generation is required for the pressure event flag generator to be enabled (PDEFE = 1) in the PT data configuration register (PT\_DATA\_CFG).

- [3] TDR and TOW flag generation is required for the temperature event flag generator to be enabled (TDEFE = 1) in the PT data configuration register (PT\_DATA\_CFG).

### 14.2.1 Data registers with F\_MODE = 00 (FIFO disabled)

When the FIFO data output register, F\_DATA (0Eh), is disabled (F\_MODE[7:6] = 00 in the F\_SETUP register, 0Fh), the pressure data registers indicate the real-time status information of the sample data. See <u>Section 14.8 "FIFO setup registers"</u> for additional information.

## 14.3 OUT\_P\_MSB, OUT\_P\_CSB, OUT\_P\_LSB - pressure data registers (address 01h, 02h, 03h)

Pressure data registers 01h, 02h, and 03h comprise the pressure depending on the setting of the ALT bit in the CTRL\_REG1 register in barometer mode. The data stored in registers 01h, 02h, and 03h is pressure data in Pascals.

The pressure data is stored as a 20-bit unsigned integer with a fractional part. The OUT\_P\_MSB (01h), OUT\_P\_CSB (02h), and bits 7 to 6 of the OUT\_P\_LSB (03h) registers contain the integer part in Pascals. Bits 5 to 4 of OUT\_P\_LSB contain the fractional component. This value is representative as a Q18.2 fixed-point format where there are 18 integer bits and two fractional bits.

Table 16. OUT\_P\_MSB, OUT\_P\_CSB, OUT\_P\_LSB - pressure data registers (address 01h, 02h, 03h) bit allocation

| Location |           | Bit |           |       |   |   |      |      |   |  |  |

|----------|-----------|-----|-----------|-------|---|---|------|------|---|--|--|

| Address  | Register  | 7   | 6         | 5     | 4 | 3 | 2    | 1    | 0 |  |  |

| 01h      | OUT_P_MSB |     | PD[19:12] |       |   |   |      |      |   |  |  |

| 02h      | OUT_P_CSB |     | PD[11:4]  |       |   |   |      |      |   |  |  |

| 03h      | OUT_P_LSB |     | PD[       | [3:0] |   |   | rese | rved |   |  |  |

| Reset    | 0 0       |     |           | 0     | 0 | 0 | 0    | 0    | 0 |  |  |

| Access   |           | R   | R         | R     | R | R | R    | R    | R |  |  |

### 14.3.1 Data registers with F\_MODE = 00

The DR\_STATUS, OUT\_P\_MSB, OUT\_P\_CSB, OUT\_P\_LSB, OUT\_T\_MSB, and OUT\_T\_LSB registers are stored in the auto-incrementing address range of 00h to 05h. This allows the host controller to read the status register followed by the 12-bit temperature in a 6 byte  $I^2C$  transaction.

See <u>Section 14.8 "FIFO setup registers"</u> for additional information.

## 14.4 OUT\_T\_MSB, OUT\_T\_LSB - temperature data registers (address 04h, 05h)

The temperature data is stored as a signed 12-bit integer with a fractional part. The OUT\_T\_MSB (04h) register contains the integer part in °C and the OUT\_T\_LSB (05h) register contains the fractional part. This value is representative as a Q8.4 fixed-point format where there are eight integer bits (including the signed bit) and four fractional bits.

Product data sheet

I<sup>2</sup>C precision pressure sensor

| Location         |           |             | Bit              |   |   |   |   |   |   |  |  |  |

|------------------|-----------|-------------|------------------|---|---|---|---|---|---|--|--|--|

| Address          | Register  | 7 6 5 4 3   |                  |   |   |   |   | 1 | 0 |  |  |  |

| 04h              | OUT_T_MSB |             | TD[11:4]         |   |   |   |   |   |   |  |  |  |

| 05h              | OUT_T_LSB |             | TD[3:0] reserved |   |   |   |   |   |   |  |  |  |

| <b>Reset</b> 0 0 |           |             |                  | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

| Access           |           | R R R R R R |                  |   |   |   | R | R |   |  |  |  |

| Table 17. OUT T MSB. | OUT T LSB - temperatu | re data registers (address | 04h. 05h) bit allocation |

|----------------------|-----------------------|----------------------------|--------------------------|

|                      |                       |                            |                          |

## 14.5 OUT\_P\_DELTA\_MSB, OUT\_P\_DELTA\_CSB, OUT\_P\_DELTA\_LSB - pressure delta register (address 07h, 08h, 09h)

The pressure delta registers 07h, 08h, and 09h comprise the pressure and delta data, providing the differences from the last pressure samples.

The pressure is arranged as a 20-bit unsigned integer with a fractional part in Pascals. The first 18 bits are located in OUT\_P\_DELTA\_MSB, OUT\_P\_DELTA\_CSB, and bits 7 to 6 of OUT\_P\_DELTA\_LSB. The two bits in position 5 to 4 of OUT\_P\_DELTA\_LSB represent the fractional component.

**Note:** The OUT\_P\_DELTA register store the difference data information regardless of the state of the FIFO data output register driver bit,  $F_MODE > 00$ .

| Table 18. | OUT_P_DELTA    | MSB, OUT | P_DELTA_ | CSB, OUT_ | P_DELTA | A_LSB - pressure delta register (address 07h, |  |

|-----------|----------------|----------|----------|-----------|---------|-----------------------------------------------|--|

| 08h, 09h) | bit allocation |          |          |           |         |                                               |  |

|         | Location        | Bit        |     |       |   |         |      |      |   |

|---------|-----------------|------------|-----|-------|---|---------|------|------|---|

| Address | Register        | 7          | 6   | 5     | 4 | 3       | 2    | 1    | 0 |

| 07h     | OUT_P_DELTA_MSB | PDD[19:12] |     |       |   |         |      |      |   |

| 08h     | OUT_P_DELTA_CSB | PDD[11:4]  |     |       |   |         |      |      |   |

| 09h     | OUT_P_DELTA_LSB |            | PDD | [3:0] |   |         | rese | rved |   |

| Reset   |                 | 0          | 0   | 0     | 0 | 0 0 0 0 |      |      |   |

| Access  |                 | R          | R   | R     | R | R       | R    | R    | R |

## 14.6 OUT\_T\_DELTA\_MSB, OUT\_T\_DELTA\_LSB - temperature delta register (address 0Ah, 0Bh)

The temperature delta register 0Ah and 0Bh comprise the temperature delta data and provide the difference from the last temperature samples.

The temperature data is arranged as 12-bit signed integer with a fractional part in °C. The eight bits of OUT\_T\_DELTA\_MSB representing degrees and with fractions of a degree stored in four bits in position 7 to 4 of OUT\_T\_DELTA\_LSB.

**Note:** The OUT\_T\_DELTA register store the difference data information regardless of the state of the FIFO data output register driver bit,  $F_MODE > 00$ .

MPL3150A2 Product data sheet

I<sup>2</sup>C precision pressure sensor

|         | Location        | Bit       |     |       |   |         |      |      |   |  |

|---------|-----------------|-----------|-----|-------|---|---------|------|------|---|--|

| Address | Register        | 7         | 6   | 5     | 4 | 3       | 2    | 1    | 0 |  |

| 0Ah     | OUT_T_DELTA_MSB | TDD[11:4] |     |       |   |         |      |      |   |  |

| 0Bh     | OUT_T_DELTA_LSB |           | TDD | [3:0] |   |         | rese | rved |   |  |

| Reset   |                 | 0         | 0   | 0     | 0 | 0 0 0 0 |      |      |   |  |

| Access  |                 | R         | R   | R     | R | R       | R    | R    | R |  |

Table 19. OUT\_T\_DELTA\_MSB, OUT\_T\_DELTA\_LSB - temperature delta register (address 0Ah, 0Bh) bit allocation

### 14.7 WHO\_AM\_I - device ID register (address 0Ch)

This register contains the device identifier which is set to C4h by default. The value is factory programmed. Consult the NXP factory for custom alternate values.

Table 20. WHO\_AM\_I - device ID register (address 0Ch) bit allocation

| Bit    | 7             | 6             | 5             | 4             | 3             | 2             | 1             | 0             |

|--------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| Symbol |               |               | ·             | WHO_A         | M_I[7:0]      | ·             |               |               |

| Reset  | 0             | 0             | 0             | 0             | 0             | 0             | 0             | 0             |

| Access | NVM data<br>1 | NVM data<br>1 | NVM data<br>0 | NVM data<br>0 | NVM data<br>0 | NVM data<br>1 | NVM data<br>0 | NVM data<br>1 |

### 14.8 FIFO setup registers

### 14.8.1 F\_STATUS - FIFO status register (address 0Dh)

| Table 21. F | <b>STATUS - FIFO status</b> | register (address | 0Dh) bit allocation |

|-------------|-----------------------------|-------------------|---------------------|

|             |                             |                   |                     |

| Bit    | 7     | 6           | 5 | 4 | 3    | 2      | 1 | 0 |

|--------|-------|-------------|---|---|------|--------|---|---|

| Symbol | F_OVF | F_WMRK_FLAG |   |   | F_CN | T[5:0] |   |   |

| Reset  | 0     | 0           | 0 | 0 | 0    | 0      | 0 | 0 |

| Access | R     | R           | R | R | R    | R      | R | R |

#### Table 22. F\_STATUS - FIFO status register (address 0Dh) bit description

| F_OVF | F_WMRK_FLAG | Event description                                                             |

|-------|-------------|-------------------------------------------------------------------------------|

| 0     |             | No FIFO overflow events detected.                                             |

| 1     |             | FIFO overflow event detected.                                                 |

| —     | 0           | No FIFO watermark events detected.                                            |

| _     | 1           | FIFO watermark event detected. FIFO sample count greater than watermark value |

The F\_OVF and F\_WMRK\_FLAG flags remain asserted while the event source is still active, but the user can clear the FIFO interrupt bit flag in the interrupt source register (INT\_SOURCE) by reading the F\_STATUS register. Therefore, the F\_OVF bit flag will remain asserted while the FIFO has overflowed and the F\_WMRK\_FLAG bit flag will remain asserted while the F\_CNT value is greater than then F\_WMRK value.

### I<sup>2</sup>C precision pressure sensor

Table 23. F\_STATUS - FIFO status register (address 0Dh) bit description

| Bit    | Symbol | Description                                                                                                                                                                                                                                                           |

|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 to 0 | F_CNT  | <ul> <li>FIFO sample counter. F_CNT[5:0] bits indicate the number of samples currently stored in the FIFO buffer.</li> <li>00_0000 — indicates that the FIFO is empty (reset value)</li> <li>00_0001 to 10_0000 — indicates 1 to 32 samples stored in FIFO</li> </ul> |

### 14.8.2 F\_DATA - FIFO data register (address 0Eh)

F\_DATA is a read only address which provides access to 8-bit FIFO data. FIFO holds a maximum of 32 samples, a maximum of  $5 \times 32 = 160$  data bytes of samples can be read. When F\_MODE bit in FIFO SETUP (F\_SETUP) register is set to logic '1', the F\_DATA pointer shares the same address location as OUT\_P\_MSB (01h), therefore all accesses of the FIFO buffer data use the I<sup>2</sup>C address 01h. Reads from the other data registers (02h, 03h, 04h, 05h) will return a value of 00h.

**Note:** The FIFO will NOT suspend to data accumulation during read transactions to *F\_DATA*.

Table 24. F\_DATA - FIFO data register (address 0Eh) bit allocation

| Bit    | 7 | 6 | 5 | 4     | 3       | 2 | 1 | 0 |

|--------|---|---|---|-------|---------|---|---|---|

| Symbol |   |   |   | F_DA1 | [A[7:0] | · |   |   |

| Reset  | 0 | 0 | 0 | 0     | 0       | 0 | 0 | 0 |

| Access | R | R | R | R     | R       | R | R | R |

#### Table 25. Read accesses through F\_DATA

| 1st read (1 byte)   | OUT_P_MSB (oldest) |

|---------------------|--------------------|

| 2nd read (1 byte)   | OUT_P_CSB (oldest) |

| 3rd read (1 byte)   | OUT_P_LSB (oldest) |

| 4th read (1 byte)   | OUT_T_MSB (oldest) |

| 5th read (1 byte)   | OUT_T_LSB (oldest) |

|                     |                    |

|                     |                    |

|                     |                    |

| 158th read (1 byte) | OUT_T_LSB (oldest) |

| 159th read (1 byte) | 00h                |

| 160th read (1 byte) | 00h                |