# PCA9420

# Power management IC for low-power microcontroller applications

Rev. 3.1 — 13 January 2022

**Product data sheet**

# 1 General description

The PCA9420 is a highly-integrated Power Management IC (PMIC), targeted to provide a full power management solution for low power microcontroller applications or other similar applications.

The device consists of a linear battery charger capable of charging up to 315 mA current. It has an I<sup>2</sup>C programmable Constant Current (CC) and Constant Voltage (CV) values for flexible configuration. Various built-in protection features such as input overvoltage protection, overcurrent protection, thermal protection, etc. are also provided for safe battery charging. It also features JEITA compliant charging.

The device also integrates two step-down (buck) DC/DC converters which have I<sup>2</sup>C programmable output voltage. Both buck regulators have integrated high-side and low-side switches and related control circuitry, to minimize the external component counts; a Pulse-Frequency Modulation (PFM) approach is utilized to achieve better efficiency under light load condition. Other protection features such as overcurrent protection, under-voltage lockout (UVLO), etc. are also provided. By default, the input for these regulators is powered by either VIN or VBAT, whichever is greater.

In addition, two on-chip LDO regulators are provided to power up various voltage rails in the system.

Other features such as FM+ I<sup>2</sup>C-bus interface, chip enable, interrupt signal, etc. are also provided.

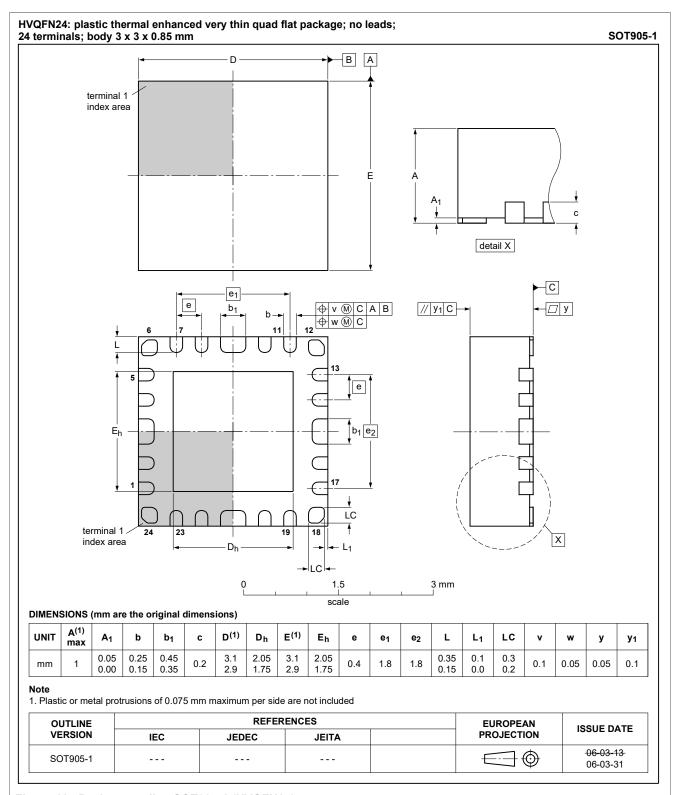

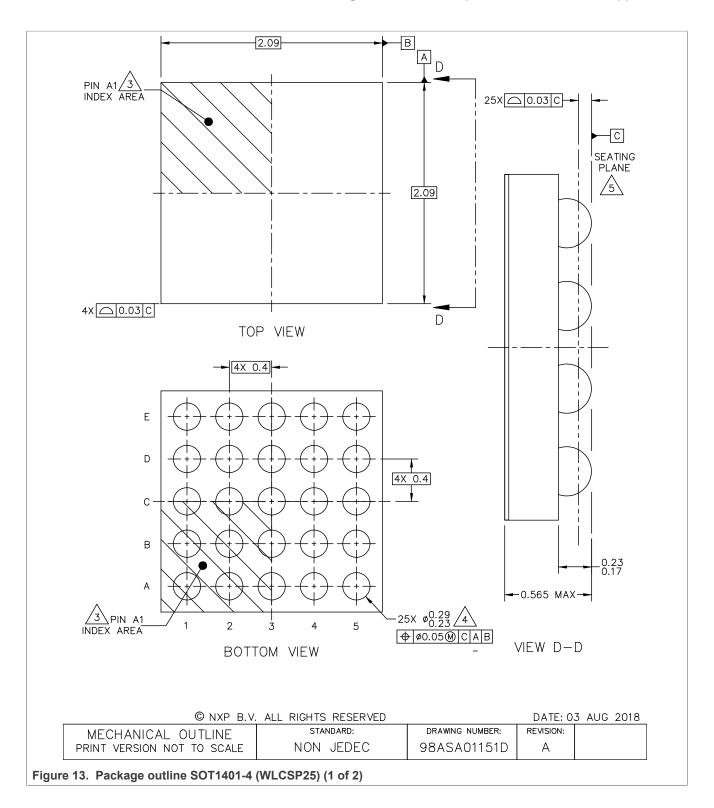

The chip is offered in 2.09 mm x 2.09 mm,  $5 \times 5$  bump, 0.4 mm pitch WLCSP package; and 3 mm x 3 mm, 24-pin QFN package.

#### 2 Features and benefits

- Linear battery charger for charging single cell li-ion battery

- 20 V tolerance on VIN pin

- Programmable input OVP (5.5 V or 6 V)

- Programmable constant current (up to 315 mA) and pre-charge low voltage current threshold

- Programmable constant voltage regulation

- Programmable automatic recharge voltage and termination current threshold

- Built-in protection features such as input OVP, battery SCP, thermal protection

- JEITA compliant

- Battery attached detection

- Over-temperature protection

#### Power management IC for low-power microcontroller applications

- Two step-down DC/DC converters

- Very low quiescent current

- Programmable output voltage

- SW1: core buck converter, 0.5 V to 1.5 V output, 25 mV/step, and a fixed 1.8 V, up to 250 mA

- SW2: system buck converter, 1.5 V to 2.1 V/2.7 V to 3.3 V output, 25 mV/step, up to 500 mA

- Low power mode for extra power saving

- Two LDOs

- Programmable output voltage regulation

- LDO1: always-on LDO, 1.70 V to 1.90 V output, 25 mV/step, up to 1 mA

- LDO2: system LDO, 1.5 V to 2.1 V/2.7 V to 3.3 V output, 25 mV/step, up to 250 mA

- 1 MHz I<sup>2</sup>C-bus slave interface

- -40 °C to +85 °C ambient temperature range

- Offered in 5 x 5 bump-array WLCSP and 24-pin QFN package

# 3 Applications

· Low power microcontroller application

# 4 Ordering information

Table 1. Ordering information

| Type number | Topside | Package |                                                                                                    |           |  |  |  |

|-------------|---------|---------|----------------------------------------------------------------------------------------------------|-----------|--|--|--|

|             | marking | Name    | Description                                                                                        | Version   |  |  |  |

| PCA9420BS   | 420     | HVQFN24 | plastic thermal enhanced very thin quad flat package; no leads; 24 terminals; body 3 x 3 x 0.85 mm | SOT905-1  |  |  |  |

| PCA9420UK   | 9420    | WLCSP25 | wafer level chip-scale package, 25 terminals, 0.4 mm pitch, 2.09 mm x 2.09 mm x 0.525 mm body      | SOT1401-4 |  |  |  |

## 4.1 Ordering options

Table 2. Ordering options

| Type number | Orderable part number | Package | Packing method      | Minimum order quantity | Temperature range |

|-------------|-----------------------|---------|---------------------|------------------------|-------------------|

| PCA9420BS   | PCA9420BSAZ           | HVQFN24 | REEL 7" Q2 NDP      | 1400                   | -40 °C to +85 °C  |

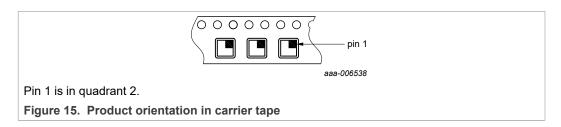

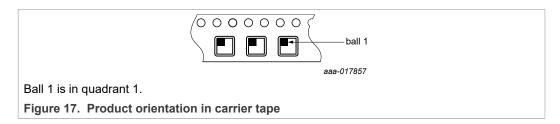

| PCA9420UK   | PCA9420UKZ            | WLCSP25 | REEL 7" Q1 DP CHIPS | 3000                   | -40 °C to +85 °C  |

#### Power management IC for low-power microcontroller applications

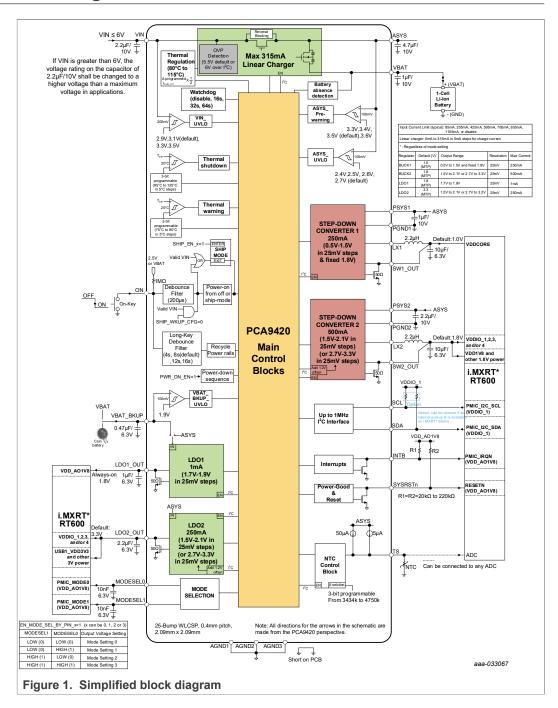

# 5 Simplified block diagram

Power management IC for low-power microcontroller applications

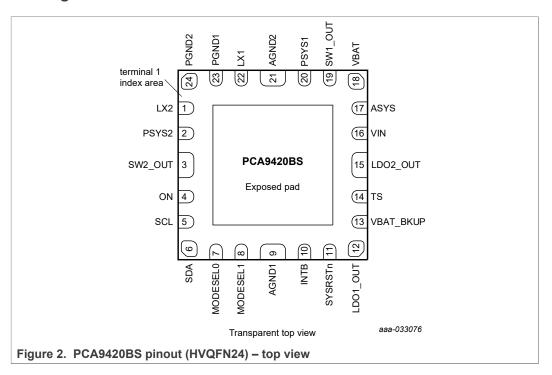

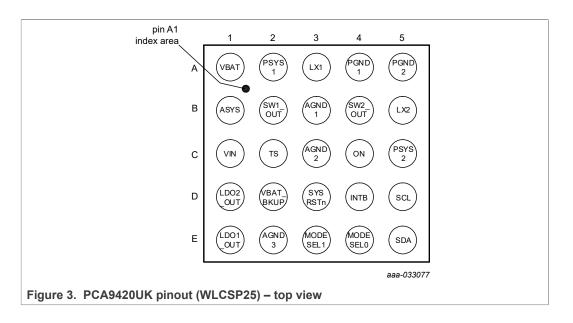

# 6 Pinning information

# 6.1 Pinning

# Power management IC for low-power microcontroller applications

# 6.2 Pin description

Table 3. Pin Description

| Symbol       | Pin         |              | Pin Type | Description                                                                                                                                                                                                                                |  |  |

|--------------|-------------|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|              | HVQFN24     | WLCSP25      |          |                                                                                                                                                                                                                                            |  |  |

| INPUT SUPPLY | ,           |              |          |                                                                                                                                                                                                                                            |  |  |

| VIN          | 16          | C1           | Р        | Input supply voltage. Bypass with a 2.2 μF/10 V ceramic capacitor.                                                                                                                                                                         |  |  |

| ASYS         | 17          | B1           | Р        | Bypass output of VIN and input supply voltage for LDO2 and linear charger, connect with a typical 4.7 $\mu$ F or 10 $\mu$ F/10 V decoupling capacitor.                                                                                     |  |  |

| VBAT_BKUP    | 13          | D2           | P        | Backup battery input voltage. LDO1 is powered by the greater of ASYS or VAT_BKUP. If a back-up battery with a coin cell is not connected, connect the pin to VBAT power domain. Connect with a typical 0.47 μF/6.3 V decoupling capacitor. |  |  |

| LINEAR CHAR  | GER         |              |          |                                                                                                                                                                                                                                            |  |  |

| VBAT         | 18          | A1           | Р        | Battery (+) connection point. A typical 1 $\mu$ F/10 V decoupling capacitor should be connected between VBAT to system ground.                                                                                                             |  |  |

| TS           | 14          | C2           | I        | Battery temperature sensing pin. An external thermistor is connected between TS pin and system ground. If the pin is not used, leave the pin open.                                                                                         |  |  |

| BUCK1 STEP_I | DOWN CONVE  | RTER (SW1)   |          |                                                                                                                                                                                                                                            |  |  |

| PSYS1        | 20          | A2           | Р        | Input supply for SW1. Bypass with a typical 1 µF/10 V ceramic capacitor. Connect to ASYS power domain as short as possible in the system.                                                                                                  |  |  |

| LX1          | 22          | A3           | Р        | Switching node for SW1. Connect to a 2.2 µH inductor. If the pin is not used, leave the pin open.                                                                                                                                          |  |  |

| SW1_OUT      | 19          | B2           | I        | Feedback pin. Bypass with a 10 μF/6.3 V ceramic capacitor. If the pin is not used, tie to PSYS1.                                                                                                                                           |  |  |

| PGND1        | 23          | A4           | Р        | Power ground for buck 1 (SW1). Connect ground nodes of two bypass capacitors for PSYS1 and SW1_OUT as close to PGND1 pin as possible in the system.                                                                                        |  |  |

| BUCK2 STEP_I | DOWN CONVE  | RTER (SW2)   |          |                                                                                                                                                                                                                                            |  |  |

| PSYS2        | 2           | C5           | Р        | Input supply for SW2. Bypass with a typical 2.2 µF/10 V ceramic capacitor. Connect to ASYS power domain as short as possible in the system.                                                                                                |  |  |

| LX2          | 1           | B5           | Р        | Switching node for SW2. Connect to a 2.2 $\mu$ H inductor. If the pin is not used, leave the pin open.                                                                                                                                     |  |  |

| SW2_OUT      | 3           | B4           | I        | Feedback pin. Bypass with a 10 μF/6.3 V ceramic capacitor. If the pin is not used, tie to PSYS2.                                                                                                                                           |  |  |

| PGND2        | 24          | A5           | Р        | Power ground for buck 2 (SW2). Connect ground nodes of two bypass capacitors for PSYS2 and SW2_OUT as close to PGND2 pin as possible in the system.                                                                                        |  |  |

| LOW_DROPOL   | IT REGULATO | RS (LDO1 and | LDO2)    | <del>.</del>                                                                                                                                                                                                                               |  |  |

# Power management IC for low-power microcontroller applications

Table 3. Pin Description...continued

| Symbol                     | Pin            |          | Pin Type | Description                                                                                                                                                      |  |  |

|----------------------------|----------------|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                            | HVQFN24        | WLCSP25  |          |                                                                                                                                                                  |  |  |

| LDO1_OUT                   | 12             | E1       | Р        | LDO1 output. It is always-ON supply. The input supply is a higher voltage between ASYS and VBAT_BKUP. Bypass with a 1 $\mu$ F/6.3 V ceramic capacitor.           |  |  |

| LDO2_OUT                   | 15             | D1       | Р        | LDO2 output. The input supply is ASYS. Bypass with a 2.2 µF/6.3 V ceramic capacitor.                                                                             |  |  |

| LOGIC INPUTS               | 3              | <u>'</u> | '        |                                                                                                                                                                  |  |  |

| ON                         | 4              | C4       | 1        | ON Pin with an internal pull-up resistor, 1 M $\Omega$ typ, to either 2.5 V or VBAT. Refer to Section 8.4 for more details.                                      |  |  |

| MODESEL0                   | 7              | E4       | 1        | Mode selection input pin #1. Place a 10 nF/6.3 V capacitor for noise rejection.                                                                                  |  |  |

| MODESEL1                   | 8              | E3       | 1        | Mode selection input pin #2. Place a 10 nF/6.3 V capacitor for noise rejection.                                                                                  |  |  |

| LOGIC OUTPU                | ITS            |          |          |                                                                                                                                                                  |  |  |

| INTB                       | 10             | D4       | О        | Interrupt output, Open-drain type. Place a pull-up resistor from 20 k $\Omega$ to 220 k $\Omega$ to a system I/O supply rail.                                    |  |  |

| SYSRSTn                    | 11             | D3       | 0        | Reset output for external MCU, Open-drain type. Place a pull-up resistor from 20 k $\Omega$ to 220 k $\Omega$ to a system I/O supply rail.                       |  |  |

| SERIAL I <sup>2</sup> C IN | TERFACE        |          |          |                                                                                                                                                                  |  |  |

| SCL                        | 5              | D5       | I        | I <sup>2</sup> C Interface clock pin. Place a pull-up resistor between 2.2 kΩ and 10 kΩ to a system I/O supply rail. If the pin is not used, leave the pin open. |  |  |

| SDA                        | 6              | E5       | I/O      | I <sup>2</sup> C Interface data pin. Place a pull-up resistor between 2.2 kΩ and 10 kΩ to a system I/O supply rail. If the pin is not used, leave the pin open.  |  |  |

| DEVICE GROU                | IND            |          |          |                                                                                                                                                                  |  |  |

| AGND1                      | 9              | В3       | Р        | Analog ground. It shall be connected to system ground                                                                                                            |  |  |

| AGND2                      | 21             | C3       | Р        | through a via. Do not connect AGND1 and AGND2 to                                                                                                                 |  |  |

| AGND3                      |                | E2       | Р        | PGND1 or PGND2 on the top PCB layer in the system.                                                                                                               |  |  |

|                            | Exposed<br>Pad |          |          | Exposed pad. Connect to system ground                                                                                                                            |  |  |

P = Power, I = Input, I/O = input/output

Power management IC for low-power microcontroller applications

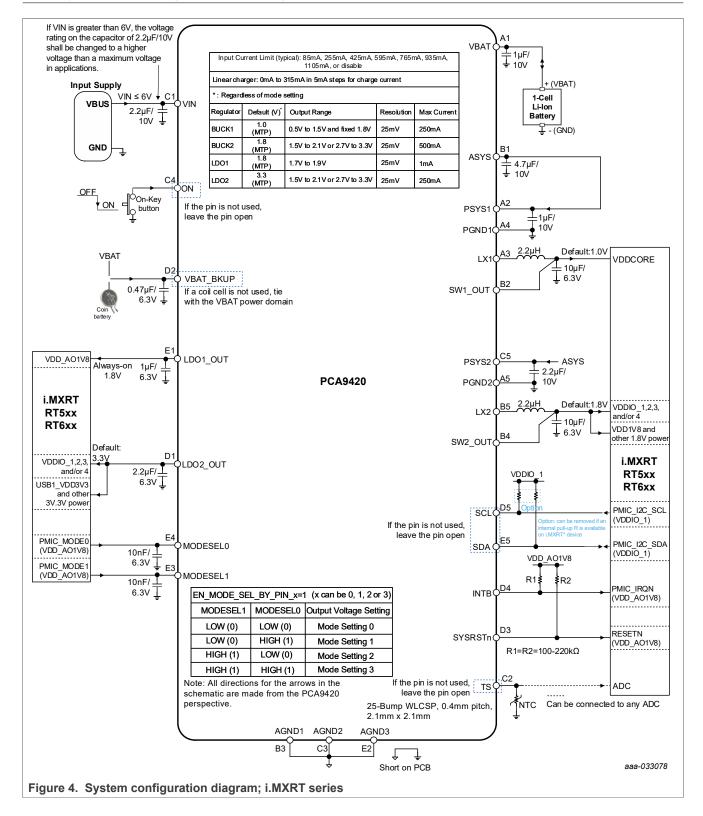

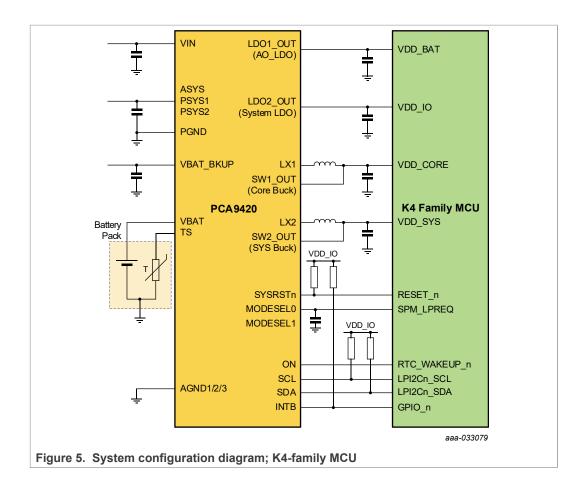

# 7 System configuration diagram

## Power management IC for low-power microcontroller applications

Power management IC for low-power microcontroller applications

# 8 Functional description

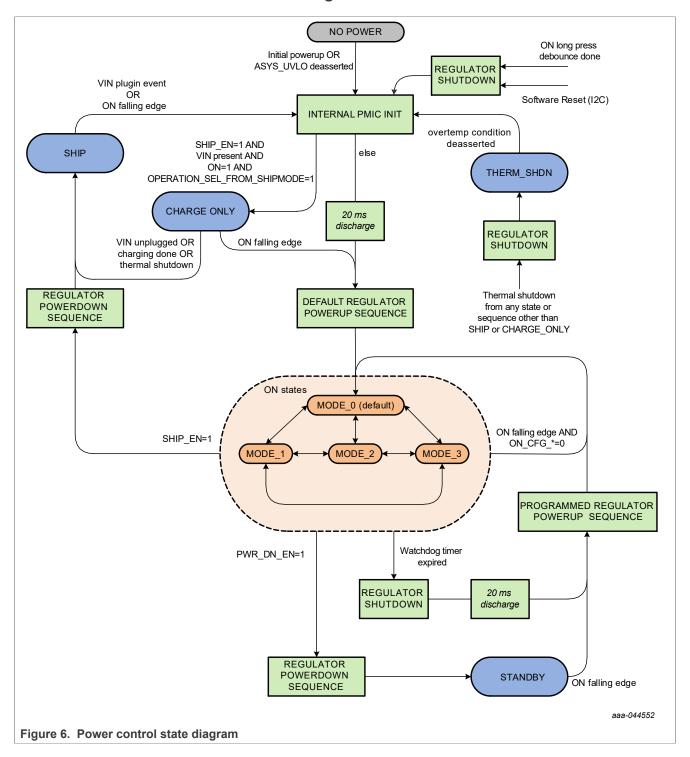

#### 8.1 Power control state diagram

Power management IC for low-power microcontroller applications

#### 8.2 ASYS

The ASYS pin serves as the input power pin for PSYS1, PSYS2 and LDO2. Internally by default it's powered by either VIN or VBAT, whichever is greater. The internal ASYS input selection circuit ensures a seamless transition when its input source changes from VIN to VBAT, or vice versa.

Through I<sup>2</sup>C register setting selection (SYS\_INPUT\_SEL [1:0]), the user also has the option to choose the ASYS input source. However, upon power cycling and/or chip reset, the ASYS input source goes back to the default setting (option 1 below).

#### SYS\_INPUT\_SEL [1:0]

- 1. 2b'00: From either VBAT or VIN, whichever is greater (default setting);

- 2. 2b'01: From VBAT only;

- 3. 2b'10: From VIN only;

- 4. 2b'11: Disconnect from VBAT or VIN (not a normal operation condition, for INTERNAL test purposes only).

An I<sup>2</sup>C programmable pre-warning ASYS voltage threshold (ASYS\_PRE\_WARNING [1:0]) can also be used to indicate when ASYS voltage drops below the ASYS prewarning threshold voltage, which triggers an interrupt event.

If any peripheral regulators are connected to ASYS node, the ASYS node follows a VIN voltage up to a programmed OVP threshold (either 5.5 V or 6 V) with a various voltage difference depending on a load current.

# 8.3 VBAT\_BKUP (back-up battery input)

Internally, the input power source for LDO1 is provided by either VBAT\_BKUP or ASYS, whichever is greater. When a coin cell battery (or similar battery) is used in the system as a backup battery, it can be connected to VBAT\_BKUP; thus the LDO1 is powered by either ASYS or the backup battery. When no such backup battery is used, the VBAT\_BKUP pin should always be connected to VBAT.

#### 8.4 ON

The ON pin has the following functions implemented:

1. ON pin has internal 1 M $\Omega$  pull-up resistor to either 2.5 V or VBAT depending on VBAT voltage. If VBAT is less than 3 V, ON is pulled up to 2.5 V and if VBAT is greater than 3 V, it is pulled to VBAT.

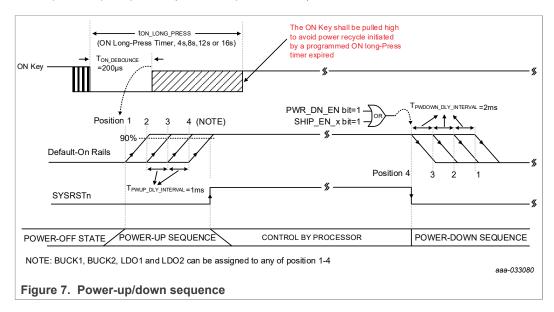

Falling edge (filtered after deglitching time, 200  $\mu$ s typ), active-LOW signal enables the chip and starts the power-up sequence from STANDBY state. If the chip stays in ship mode before applying ON falling edge, upon the filtered falling edge of the ON pin, the chip exits ship mode to start up into Mode Setting 0.

If the device is already in the middle of power-up or power-down sequence, the falling edge applied on the ON pin is ignored by the chip.

- 1. Long press (duration time, 4 s, 8 s, 12 s or 16 s, is programmable via I<sup>2</sup>C, ON\_GLT\_LONG [1:0]). If the logic low signal is applied continuously over a programmed duration, the chip gets reset and recycles all power rails to their default values

- 2. Also, in mode setting 0, 1, 2, or 3, an I<sup>2</sup>C bit "ON\_CFG\_x" (x=0, 1, 2, or 3) is reserved; by setting its value to either 0 or 1, the user can configure whether a mode setting switches back to Mode Setting 0 or not, upon a valid falling edge detected

#### Power management IC for low-power microcontroller applications

from "ON" pin. Refer to ON\_CFG\_x bit description in the relation registers for more details.

3. The filtered falling edge on the ON pin resets the bit of EN\_MODE\_SEL\_BY\_PIN\_X to the default value, 0, at 22h register. The status of the ON pin is available in reset monitor register (address 0x71, bit [7]).

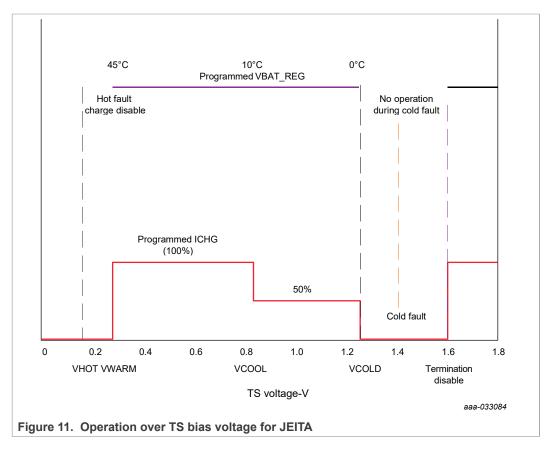

#### 8.5 TS

With the temperature sensing pin, the external thermistor (NTC) is connected between the TS pin and ground. The thermistor may be included in the battery pack to monitor the battery pack temperature, or it may be an additional component user chooses to have on the board level to monitor the temperature at a chosen area.

The voltage at TS pin is monitored, and the user can enable the feature through I<sup>2</sup>C-bus interface (NTC\_EN) to implement JEITA compliant charging at a safe temperature. Per JEITA standard, there are four temperature threshold settings:

- 1. Cold threshold (T1, 0 °C)

- 2. Cool threshold (T2, 10 °C)

- 3. Warm threshold (T3, 45 °C)

- 4. Hot threshold (T4, 60 °C)

Each of the above temperature thresholds represents a voltage threshold. When the monitored temperature, T, falls into a different temperature zone, the charger should adjust the charging method accordingly:

- 1. T > T4 or T < T1, i.e., when the temperature is in a "cold" or "hot" zone, charging is suspended, as well as the safety timer;

- 2. T1 < T < T2, charging current is reduced by 50 % of the programmed current level;

- 3. T2 < T < T3, normal charging;

- 4. T3 < T < T4, the CV mode regulating voltage should be set as VBAT\_REG [5:0]  $\Delta$ VBAT\_REG(HOT), 140 mV typical

To disable this function, set NTC\_EN to "0".

#### 8.6 Mode setting

When the MCU operates in different modes such as overdrive run mode or low power mode, it may require the power supply to operate in different settings accordingly (for example, enable/disable of each rail, output voltage of each rail, etc.) to achieve a better performance and efficiency.

On the PCA9420, there are four modes of registers representing Mode Setting 0/1/2/3 to accommodate such requirements from MCU, where Mode Setting A is the default mode setting (i.e., the initial mode setting upon initial power up). Depending on the user's preference, switching among different mode settings can be controlled by either the external signal (ON pin), external pins (MODESEL0/1) or I<sup>2</sup>C.

Within each mode setting, the user can program the follow parameters providing great flexibility to accommodate different MCU operation modes:

- 1. Enable/disable of the four output voltage rails

- 2. Voltage setting of the four output voltage rails

- 3. Ship mode enable/disable

- 4. Watchdog timer setting

- 5. Mode control selection (EN\_MODE\_SEL\_BY\_PIN\_x, x=0, 1, 2, or 3)

#### Power management IC for low-power microcontroller applications

EN\_MODE\_SEL\_BY\_PIN\_x = 0: under current mode setting, mode setting switch is controlled by internal I<sup>2</sup>C register bits MODE0\_I2C and/or MODE1\_I2C only; signal applied on external MODESEL0/MODESEL1 pins is ignored.

EN\_MODE\_SEL\_BY\_PIN\_x = 1: under current mode setting, mode setting switch is controlled by signal applied on external MODESEL0 and/or MODESEL1 pins only, not by internal I<sup>2</sup>C register bits MODE0\_I2C and MODE1\_I2C.

1. Mode setting switches back to Mode Setting A triggered by ON pin falling edge. Refer to register description for "ON\_CFG\_x" bit for more details.

In the event of switching from one mode setting (initial mode setting) to another mode setting (target mode setting):

- If one output rail remains enabled in both initial mode setting and target mode setting but with different output voltage in each setting, such voltage transition should happen when the mode setting switch command (from either internal I<sup>2</sup>C setting or external signal) is received;

- 2. If there are output rails which may be enabled or disabled from initial mode setting to target mode setting, then always make sure these rails which change from disabled to enabled take higher priority over rails which change from enabled to disabled, i.e., make sure all the rails change from disabled status to enabled status (reaches 90 % of its target value) first, and then start to disable these rails, changing from enable status to disable status.

# 8.7 Mode selection by external pins (MODESEL0, MODESEL1)

Up on initial power-up, PCA9420 enters its default setting (Mode Setting 0). While operating under Mode Setting 0, by default the I<sup>2</sup>C register bit, EN\_MODE\_SEL\_BY\_PIN\_0, is set to "0", and the external signal applied on the MODESEL0 and MODESEL1 pins are ignored. Only when the user sets EN\_MODE\_SEL\_BY\_PIN\_0 to "1", can the mode control on the chip be programmed via MODESEL0 and MODESEL1 pin signal settings. The MODESEL0 and MODESEL1 pins are not allowed to change while a mode change is in progress.

When EN\_MODE\_SEL\_BY\_PIN\_x (x=0, 1, 2, or 3) bits are set to "1", MCU should satisfy the following MODESEL signal conditions:

- No less than 5 µs pulse on each MODESEL signal.

- No more than 0.5 µs delay between MODESEL pins when transit from different modes.

In order to avoid impacting mode transition when there is disturbance in MODESELS pins ( $EN\_MODE\_SEL\_BY\_PIN\_x$  =1), it is proposed to implement one of the following designs:

- Hardware: Adding 10 nF capacitors to remove noise injection on MODESEL pins.

- Software: Send software reset command after wake up from ship mode to reset MODESEL pins. (There is a register 0x71, accessible by I<sup>2</sup>C; SHIP\_EXIT\_DONE status indicates device wake up from ship mode, refer to <u>Table 76</u>.)

Table 4. Mode selection by external pins (MODESEL0, MODESEL1)

| Table 4. Induction by external pine (induction) |                            |                   |  |  |  |

|-------------------------------------------------|----------------------------|-------------------|--|--|--|

| MODESEL1 pin voltage level                      | MODESEL0 pin voltage level | All Settings from |  |  |  |

| LOW (0)                                         | LOW (0)                    | Mode Setting 0    |  |  |  |

| LOW (0)                                         | HIGH (1)                   | Mode Setting 1    |  |  |  |

| HIGH (1)                                        | LOW (0)                    | Mode Setting 2    |  |  |  |

PCA9420

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2022. All rights reserved

#### Power management IC for low-power microcontroller applications

Table 4. Mode selection by external pins (MODESEL0, MODESEL1)...continued

| MODESEL1 pin voltage level | MODESEL0 pin voltage level | All Settings from |

|----------------------------|----------------------------|-------------------|

| HIGH (1)                   | HIGH (1)                   | Mode Setting 3    |

#### 8.8 SYSRSTn

The SYSRSTn is implemented as an open-drain output signal. It is used as an output of "power-good" indication as well as to reset the microcontroller system.

The SYSRSTn signal is held from high to low under one of following conditions:

- 1. When any of the **enabled** voltage rail output voltage drops below 90 % (typ) of its target value.

- 2. When any of the **enabled** voltage rail output voltage goes above 110 % (typ) of its target value

If any of the voltage rail is disabled by the user (by setting the corresponding enable bit in I<sup>2</sup>C register in each mode setting, i.e., LDO1\_EN\_x, LDO2\_EN\_x, SW1\_EN\_x, SW2\_EN\_x), the SYSRSTn signal should NOT assert (stays high) under such scenario.

This also applies during the power-up/power-down sequence events, i.e., during power-up or power-down event, the SYSRSTn signal should assert when any of the enabled rail has not reaches the 90 % to 110 % of its target value. In other words, the SYSRSTn = 0 (low) needs to remain at such state until all enabled rails reach 90 % of the target values.

Once the condition that caused the SYSRSTn signal to go low is removed, then the SYSRSTn should refresh accordingly.

Meanwhile, during the voltage change on-the-fly, this could be caused by:

- 1. Mode setting remains the same, but the user chooses to change one or some of the enabled output rail voltage by programming its output voltage I<sup>2</sup>C register setting

- Mode setting changes by setting different values on MODESEL0/MODESEL1 pins or MODE0\_I2C/MODE1\_I2C bits, and it causes one or some of the output rail voltage change

In such case, the SYSRSTn signal does NOT assert when any of the **enabled** voltage rail output voltage is in the middle of the transition from initial output voltage level to target level.

#### 8.9 SHIP mode

PCA9420 features a "SHIP mode", in which the chip provides the lowest quiescent consumption.

To enter the SHIP mode, set the bit of SHIP\_EN\_x (x can be 0, 1, 2 or 3) in each Mode register to 1. Once the bit is set to 1, the ship mode immediately takes place regardless of any operation under any mode setting. It means that the SHIP mode has a higher priority over any conditions and operations.

Upon request to enter the ship mode while the device is running in active mode, a power-down sequence should take place first and then enter the ship mode. Once the device enters ship mode, all the I<sup>2</sup>C register values are reset to their default setting.

To exit ship mode, one of the following conditions must be satisfied:

1. ON pin falling edge (filtered) applied, less than the long-press duration of time

#### Power management IC for low-power microcontroller applications

- A valid VIN attached. For the VIN attached plugin event, depending on OPERATION\_SEL\_FROM\_SHIPMODE bit setting, there are two possible operations as described below:

- a. OPERATION\_SEL\_FROM\_SHIPMODE=0, upon VIN attached, the chip enables the charging process, as well as start the power-up sequence for LDO1/LDO2/ SW1/SW2 per the setting

- b. OPERATION\_SEL\_FROM\_SHIPMODE=1, upon VIN attached, the chip enables the charging process, LDO1/LDO2/SW1/SW2 remains in shutdown mode and the chip will only enable the power-up sequence upon ON pin falling edge signal.

#### 8.10 Watchdog timer

PCA9420 provides an on-chip watchdog timer, the duration of this watchdog can be programmed via I<sup>2</sup>C register setting (WD\_TIMER\_x [1:0] in each mode configuration registers), or disabled if needed in each mode setting.

Upon initial enable, the watchdog timer starts counting. If the watchdog timer expires before reset, an interrupt signal is issued (WD\_TIMER). Depending on the I<sup>2</sup>C register setting (nEN\_CHG\_IN\_WATCHDOG), the following action is also taken:

- 1. nEN\_CHG\_IN\_WATCHDOG = 0: when the watchdog timer expires, the following operations are expected.

- The SYSRSTn signal asserted (high to low)

- · Charging is continued based on battery condition

- All settings for LDO1/LDO2/SW1/SW2 set to Mode 0 settings

- nEN\_CHG\_IN\_WATCHDOG=1: when the watchdog timer expires, the following operations are expected.

- · The SYSRSTn signal asserted (high to low)

- Charging is suspended

- All settings for LDO1/LDO2/SW1/SW2 set to Mode 0 settings

The following events reset the watchdog timer:

- 1. When WD TIMER CLR bit is set to 3b'001 at 0Dh register

- 2. When the device changes the mode settings

#### 8.11 Regulators

There are four regulators on PCA9420, which include two buck regulators and two LDOs. Table 5 shows the outline for each regulator:

Table 5. Regulator summary

| Regulator name       | Output regulation voltage range  | Adjustable resolution | Max output current |

|----------------------|----------------------------------|-----------------------|--------------------|

| SW1 (Core Buck)      | 0.5 V to 1.5 V and a fixed 1.8 V | 25 mV/step            | Up to 250 mA       |

| SW2 (System Buck)    | 1.5 V to 2.1 V or 2.7 V to 3.3 V | 25 mV/step            | Up to 500 mA       |

| LDO1 (Always-on LDO) | 1.7 V to 1.9 V                   | 25 mV/step            | Up to 1 mA         |

| LDO2 (System LDO)    | 1.5 V to 2.1 V or 2.7 V to 3.3 V | 25 mV/step            | Up to 250 mA       |

For each rail, its output target voltage can be set independently in mode setting 0, 1, 2 or 3. User can also choose to switch among any of the mode settings.

#### Power management IC for low-power microcontroller applications

## 8.11.1 Enable/disable and active discharge

**Enable/disable**: Each rail can be enabled/disabled via I<sup>2</sup>C register setting independently in each mode setting.

**Active discharge**: Additionally, there is an active discharge resistor on each rail, and the user can choose to enable/disable such feature through I<sup>2</sup>C register setting, so that when the output rail is disabled, it can quickly discharge the output voltage to ground. In addition, the active discharge is also enabled during voltage step down. This can be disabled by MTP bit.

If the active discharge bleeding resistor is enabled AND there is a change of the Buck regulators' output voltage to a lower value (i.e. from 0.9 V to 0.75 V) there could be a small voltage peak of 5 % higher than the initial voltage (for 10  $\mu$ s) during the transition. If this behavior is not desired, the bleeding resistor can be disabled (nEN\_SW1\_BLEED = 1 or nEN\_SW2\_BLEED = 1) but with the effect of a potentially longer transition to the new voltage of the buck regulator output

#### 8.11.2 Power-good indication

There is an output voltage comparator for each rail, comparing the actual output voltage against 90 % and 110 % of its target value; when the actual voltage is between 90 % and 110 % of its target value, the read-only related bits in I<sup>2</sup>C register, Regulator Status\_1 (address: 20h) are updated accordingly to report the output voltage status (Power-good Indication). These comparators can be enabled/disabled by setting I<sup>2</sup>C register bit, PG\_EN. A corresponding interrupt is triggered if unmasked. During steady state, only 90 % threshold is monitored.

The power-good indication is shown as "not good", and refreshes upon the completion of any of the following events:

- 1. During the power-up sequence stage

- 2. During power-down sequence stage

- 3. During the on-the-fly change of output voltage

## 8.11.3 Power-up/down sequence and on-the-fly voltage change

#### Power-up sequence

The device initiates the default power-up sequence in three different conditions.

**Condition 1)** The device is off with no any power supply (No valid VIN and No battery with 2.7 V or above attached). In this condition, two signals below are able to start the default power-up sequence.

- A valid VIN supply on VIN pin

- A voltage on ASYS higher than ASYS\_UVLO, a 2.8 V typical

**Condition 2)** The device stays off by enabling SHIPMODE or in SHIP mode with a battery ≥ 2.8 V attached. In this condition, two signals are able to start the default power-up sequence.

- · A valid VIN supply on VIN pin

- A falling edge on ON key over a 200 µs

**Condition 3)** The device stays off by enabling PWR\_DN\_EN bit setting to 1 with a battery ≥ 2.8 V attached. In this condition, only one signal is able to start the default power-up sequence.

#### Power management IC for low-power microcontroller applications

• A falling edge on ON key over a 200 μs

**Condition 4)** The device stays at VIN OVP condition with no any valid supply attached at VBAT. In result, all enabled power rails have been off. The following condition reinitiates the power-up sequence.

• The VIN goes below its VIN OVP hysteresis (typ 100 mV)

The power-up sequence by ON key=Low over the debounce time is described as shown in Figure 7.

For the power-up sequence, the chip can set the default sequence per the customer requirement at factory setting (i.e. MTP option), from one of the 64 options. Once the chip enters the power-down stage, the power-down sequence is implemented as the reverse of the power-up sequence (i.e., first up, last down).

#### On-the-fly output voltage change sequence

On-the-fly output voltage change is defined as the following: for any output rail, its output voltage changes from one level (initial level) to another level (target level). Note this assumes the output rail is always enabled before and after the on-the-fly change transition. It does not include the case when any output rail is changed from disabled state to enabled state, or vice versa.

If a user prefers to change any rail voltage on-the-fly, depending on the scenarios listed below, the chip behavior is described as follows:

- 1. While the chip remains in its current operation mode, and the user programs the output voltage setting I<sup>2</sup>C register value or enables/disables any or some of output voltage rail(s), the chip simply executes the I<sup>2</sup>C command

- While the user chooses to switch modes, i.e. change mode between any of the two

mode settings among Mode 0/1/2/3, and if this involves on-the-fly voltage change for

one or some output rails, such change should occur simultaneously when the chip

switches from initial mode to the target mode.

**CAUTION**: The user should not send an I<sup>2</sup>C command related to changing the setting of the output rails during the power up/down or mode setting change process.

Power management IC for low-power microcontroller applications

## 8.11.4 BUCK1 (SW1, core buck regulator)

The SW1 supplies the core power.

Its output voltage can be programmed via  $I^2C$  from 0.5 V to 1.5 V at 25 mV step and a fixed 1.8 V, which is capable of providing up to 250 mA loading. The application circuit uses typical 2.2  $\mu$ H inductor and 10  $\mu$ F/6.3 V output capacitor.

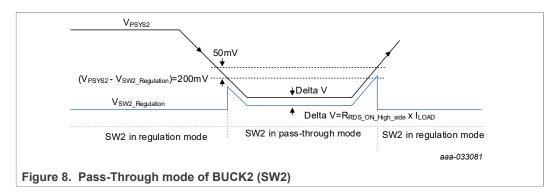

#### 8.11.5 BUCK2 (SW2, system buck regulator)

The SW2 output voltage can be programmed via  $I^2C$  register from 1.5 V to 2.1 V, or from 2.7 V to 3.3 V in both at 25 mV/step and is capable of providing up to 500 mA loading. The application circuit uses a 2.2  $\mu$ H inductor and 10  $\mu$ F output capacitor.

In SW2, a pass-through mode is implemented. When its input (ASYS) is close to the output voltage (within typical 200 mV), the SW2 enters the pass-through mode operation; the high-side switch is fully turned on and the low-side switch is turned off, and the output voltage can be calculated as input voltage – (RDSON\* $I_{LOAD}$ ), where RDSON is the onresistance of the high-side switch, and the  $I_{LOAD}$  refers to the load current. When the input voltage rises again, so that the voltage different between input and output crosses the typical 250 mV threshold, the SW2 exits the pass-through mode and re- enters the normal switching mode operation.

While SW2 operates in pass-through mode, protection features such as over-current protection are also implemented as well.

#### 8.11.6 LDO1 (always-on LDO)

The LDO1 (Always-on LDO) output can be programmed from 1.7 V to 1.9 V at 25 mV step, depending on the system requirements (selectable through  $I^2C$  register). Typically, a 1  $\mu$ F/6.3 V MLCC output capacitor providing at least 1 mA loading capability is needed.

LDO1 operates based on the principle of hysteretic on/off regulation. The LDO1 output voltage is generated from a frequent activation/deactivation of the output stage connecting VBAT to the LDO1 output depending on the programmed output voltage for LDO1. The ripple frequency and amplitude will greatly depend on the load current and external capacitance. The greater the load current, the higher the on/off activation of this output stage to ensure LDO1 stays within the defined output voltage accuracy specified in the electrical specification section. LDO1 is powered by the greater of ASYS or VBAT BKUP.

SW\_RST event will not shut down LDO1, but sets LDO1 to default value. Watchdog Reset will not shut down LDO1, but changes LDO1 to Mode 0 setting. SHIP mode/

#### Power management IC for low-power microcontroller applications

Hardware Reset (ON Long Press) shuts down LDO1 and recycles power up to default output voltage.

#### 8.11.7 LDO2 (system LDO)

The LDO2 (system LDO) output can be programmed via the  $I^2C$  register from 1.5 V to 2.1 V, or 2.7 V to 3.3 V at 25 mV/step. Typically, a 2.2  $\mu$ F/6.3 V MLCC output capacitor providing at least 250 mA loading current is needed.

# 8.12 Linear battery charger

The battery charger is a linear charger. Its charging is done through a linear switch with the following output protections:

- Reverse current protection

- (triggers when ASYS < VBAT+ VINBAT HEADROOM\*)

- · Charging current limiting

- (a function of programmed threshold and battery temperature)

If the battery voltage is below the  $V_{BAT\_LOW}$  threshold, the battery is considered discharged and a preconditioning cycle begins. The amount of pre-charge current (ICHG\_LOW) can be programmed through I²C register setting. This feature is useful when there is a load connected directly across the battery (at VBAT pin) "stealing" the battery current. The pre-charge current can be set higher to account for the system loading while allowing the battery to be properly conditioned. Once the battery voltage has charged to the  $V_{BAT\_LOW}$  threshold, fast charge is initiated and a programmed fast charge current ( $I_{CHG\_CC}$ ) is applied. The fast charge constant current is programmed using  $I^2C$  register. The constant current provides the bulk of the charge. Power dissipation in the device is greatest in fast charge with a lower battery voltage.

If the device reaches a programmed thermal regulation threshold temperature (defined by the configuration on the THM\_REG bit fields on the CHG\_CNTL7 register) from 85 °C to 115 °C in 5 °C steps, the device enters thermal regulation. This is indicated by the TREG\_STATUS bit field on the CHG\_STATUS\_1 register. Thermal regulation increases the safe-charging-timer period by 2x and reduces the charge current in half (if the initial current is 5 mA, it will remain unchanged) to keep the temperature from rising any further when battery charger works in constant current charging mode, or at a reduced regulated voltage when battery charger works in constant voltage charging mode.

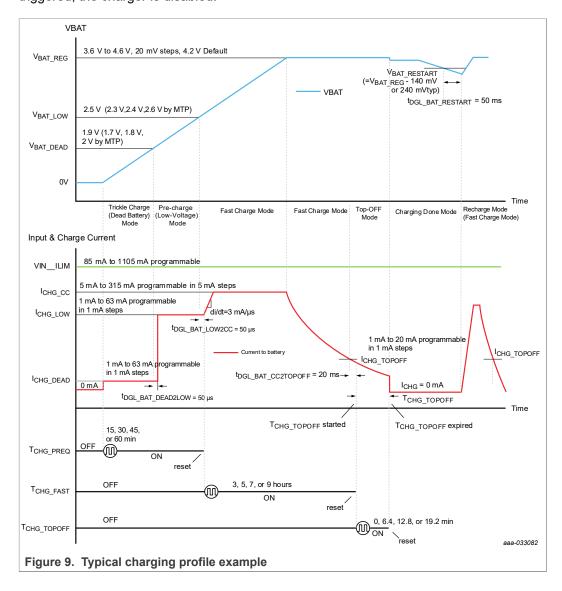

<u>Figure 9</u> shows the charging profile with a dead battery condition. Once the cell has charged to the regulation voltage (V<sub>BAT\_REG</sub>) the voltage loop takes control and holds the battery at the regulation voltage until the current tapers to the termination threshold (I<sub>CHG\_TOPOFF</sub>).

CHG\_LOCK [4:0] bits on Battery charger control\_0 (CHG\_CTL0, address 10h) register should be set to '10101' to be able to perform I<sup>2</sup>C "write" command. Otherwise, when "write" command is performed on the 'locked registers', it keeps the present register value.

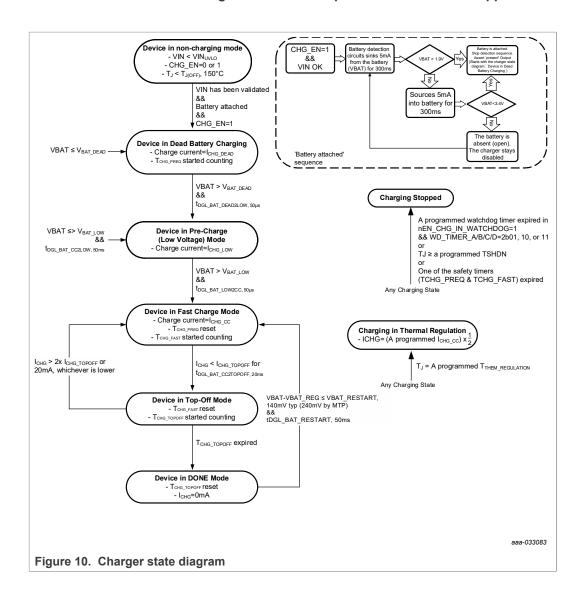

#### 8.12.1 Battery charging management

Battery charging management supports typical constant current/constant voltage charging profile for single cell Li-lon battery, as well as pre-qualification (dead battery, low battery), top-off mode, etc.; JEITA and thermal regulation compliant.

#### Power management IC for low-power microcontroller applications

In PCA9420, there is an initial stage in the charger operation which sources  $I_{CHG\_DEAD}$  current into VBAT and compares the voltage to 1.9 V level.

- If the voltage is higher than this threshold, the charger immediately proceeds to the next state (pre-charge/I<sub>CHG</sub> LOW current).

- Otherwise, there is a timer running for 5...40s (I<sup>2</sup>C programmable) called ICHG\_DEAD\_TIMER, bits [7:6] in register 0x14 chg\_ctl4. If the timer expires, the battery doesn't accept charge and is detected as a short.

ICHG\_DEAD\_CURRENT is sourced by the charger and is I<sup>2</sup>C programmable.

The dead charge fault timer can assert an interrupt (bit [6] (ICHG\_DEAD\_TIMER\_INT\_MASK) from Sub\_INT1\_Mask register 05h), and the software can make the final decision. If left masked, the charger always proceeds to the next stage. This is the default PCA9420 operation. If the interrupt was enabled and has triggered, the charger is disabled.

## Power management IC for low-power microcontroller applications

Power management IC for low-power microcontroller applications

#### 8.12.2 Battery temperature sensing and JEITA-compliant charging profile

Please refer to Section 8.5 for more details

#### 8.12.3 Battery attach detection

The device has a unique battery detection scheme with two comparators, 1.9 V and 3.4 V. When the detection scheme is executed, a 5 mA current sink is activated to determine battery presence by detecting the fall threshold,  $V_{BAT\_DET\_LOW}$ , 1.9 V typ. In addition, a 5 mA current source is used to detect battery voltage whether it stays above the threshold,  $V_{BAT\_DET\_UP}$ , 3.4 V. If both conditions are met, absence of battery is declared.

Battery detection sequence steps:

- 1. VBAT Sources 5 mA current to the PMIC Battery Detection Circuit.

- 2. If VBAT voltage is above 1.9 V, the battery is present. Stop the detect sequence, assert the "present" output.

- 3. Else if VBAT voltage is below 1.9 V, source 5 mA from PMIC into VBAT pin.

- 4. If VBAT voltage is below 3.4 V, the battery is present. Stop the detect sequence, assert the "present" output.

- 5. Else if VBAT voltage is above 3.4 V, the battery is absent (open). The charger stays disabled.

NOTE: The battery detect source and sink are separate dedicated circuits; 5 mA is a constant, not programmable. The reset source is recorded on the "Reset monitor" register (address 0x71h)

#### Power management IC for low-power microcontroller applications

For more details, see Figure 10.

#### 8.12.4 Low-battery/dead-battery (pre-qualification) charging

If the battery is detected and VBAT < VBAT\_LOW, the charger initiates pre-charging using a predefined (I<sup>2</sup>C register) current.

When it is under the dead-battery condition, the charging current  $I_{CHG\_DEAD}$  is programmed by ICHG\_DEAD [5:0]; and when it is under the low-battery condition, the charging current  $I_{CHG\_LOW}$  is programmed by ICHG\_LOW [5:0]. When  $V_{BAT} \ge V_{BAT\_LOW}$ , the charger moves to the next state, fast charging mode.

# 8.12.5 Constant current charging/constant voltage charging (fast charging) and termination

When  $V_{BAT} \ge V_{BAT\_LOW}$ , the charger enters Fast Charge Mode (Constant Current). In this state, the battery voltage VBAT continues to rise, while the battery is being charged with the current set by ICHG\_CC [5:0], until VBAT reaches the maximum allowable voltage set by VBAT\_REG [5:0].

At this time, the charger enters the Constant Voltage (CV) mode. While operating in the CV mode, the voltage is still regulated at the level set by VBAT\_REG [5:0], and the charging current continues to decrease.

When the charging current drops below the top-off current threshold, set by ICHG\_TOPOFF [5:0], the charger enters TOPOFF mode, and upon expiration of TOPOFF timer (set by T\_TOPOFF [1:0]), the charger enters DONE mode.

#### 8.12.6 Charger safety timers

Two sets of charging safety timers are implemented on PCA9420. These timers ensure the charging is terminated if the charging time is longer than its predefined limit (programmed via I<sup>2</sup>C registers) at given states:

- Pre-qualification timer, set by ICHG PREQ TIMER [1:0], 15 min to 60 min

- Fast charge timer, set by ICHG FAST TIMER [1:0], 3 hr to 9 hr

#### 8.12.7 Recharging

While in DONE mode, if the voltage of VBAT stays below (a programmed VBAT\_REG – 140 mV or 240 mV) over the deglitch time (t<sub>DGL\_BAT\_RESTART</sub>), 50 ms the battery charger resumes back to Constant Current (CC) Mode.

#### 8.12.8 Starting a new charge cycle

When a VIN plug in, VBAT attached, or CHG\_EN are set to "1", the device initializes a new charging process.

#### 8.13 Hardware and software reset

Please refer to description for ON pin for the hardware reset function by a long time ON key pressed. The "software reset" is achieved by setting "1" to SW\_RST bit in I<sup>2</sup>C register. If the user writes a "1" to this bit, it resets all other I<sup>2</sup>C register bits to their default setting; this bit is cleared and reset back to "0" as well.

Power management IC for low-power microcontroller applications

# 8.14 Device level protection features

The device contains several protection features at both the complete IC level and have a reaction at each of the functional blocks (linear charger, DC/DC converters, LDOs). There are additional protection mechanisms at the functional block level, but those are already documented on its respective functional description section.

Table 6. Device level protection features

| Condition                 | Triggering point                      | Protection reaction                                    |                                                             |                                                                                              |                                                                                              |                                                                  |  |

|---------------------------|---------------------------------------|--------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

|                           |                                       | Overall Device state                                   | Linear charger                                              | DC/DC converters                                                                             | LDOs                                                                                         | Register contents                                                |  |

| VIN undervoltage          | VIN < VIN_UVLO                        | Operational                                            | Disabled                                                    | Remain operational<br>although might deliver a<br>reduced output voltage<br>(due to low VIN) | Remain operational<br>although might deliver a<br>reduced output voltage<br>(due to low VIN) | Maintained. Interrupt triggered, status reported.                |  |

| VIN overcurrent<br>(ILIM) | VIN current is > VIN_ILIM             | Reset if ASYS<br>< ASYS_UVLO;<br>otherwise Operational | RESET state if ASYS < VBAT_Vheadroom; otherwise operational | Remain operational up to the point of ASYS_UVLO                                              | Remain operational up to the point of ASYS_UVLO                                              | Maintained unless reset happened; Interrupt and status reported. |  |

| ASYS undervoltage         | ASYS < ASYS_UVLO                      | RESET                                                  | RESET state                                                 | Turned off, restarted in initial state when condition goes away                              | Turned off, restarted in initial state when condition goes away                              | Reset to their default value                                     |  |

| IC overtemperature        | Chip temperature > THM_REG            | RESET                                                  | RESET state                                                 | Turned off, restarted in initial state when condition goes away                              | Turned off , restarted in initial state when condition goes away                             | Reset to their default value. Status available in register 0x71. |  |

| Watchdog timer expiration | Watchdog counter > WD_Timer_0 setting | Operational                                            | Depends on the value of nEN_CHG_IN_WATCHDOG bit             | Set to mode 0                                                                                | Set to mode 0                                                                                | Maintained. Status available in register 0x71.                   |  |

# 9 I<sup>2</sup>C-bus interface and register

The PCA9420 implements an I<sup>2</sup>C-bus slave interface to communicate with the host system. The interface supports Fast Mode plus Fm+ with up to 1 Mbit/s. A detailed description of the I<sup>2</sup>C-bus specification is given in <u>UM10204</u>, <u>Rev. 06</u>, <u>4 April 2014</u>, "I<sup>2</sup>C-bus specification and user manual".

Features such as clock-stretching and 10-bit slave address are not supported; general call is supported by default but can be disabled via metal option. Auto increment with address wrap-around is supported as well.

## 9.1 I<sup>2</sup>C slave address

Following a START condition, the bus master must send the target slave address followed by a read or write operation. The slave address of the PCA9420 is shown below:

Table 7. I<sup>2</sup>C Slave Address

| Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|------------|-------|-------|-------|-------|

| 1     | 1     | 0     | 0          | 0     | 0     | 1     | 0/1   |

| Fixed | Fixed | Fixed | MTP option | Fixed | Fixed | Fixed | R/W   |

Bit 4 should be reserved as MTP option, with its default value set as "0" but can be trimmed to "1" when needed.

#### 9.2 General call and device ID addresses

The device implements two different addresses for general call and device ID.

#### 9.3 Register type

There are four register types used on the device:

© NXP B.V. 2022. All rights reserved

#### Power management IC for low-power microcontroller applications

- Read and Write (R/W)

- Read Only (R)

- Write Only (W)

- Write and Clear (W/C)

For Write and Clear (W/C), a write to a register with a bit-mask specifies which interrupts to clear.

For example, if the status register shows 8'b0000\_1001 as an interrupt status (i.e. interrupt [0] and interrupt [3] are both set), user may write 8'b0000\_1000, meaning the intent is to only clear interrupt [3] (but interrupt [0] should NOT be "cleared"). If the intent is to clear both interrupts, then the user could write back 8'b0000\_1001.

# 9.4 Register map

Table 8. Register map

| Address (Hex)  | Register Name                                 | Description                           | Туре | Reset Value (Binary) |

|----------------|-----------------------------------------------|---------------------------------------|------|----------------------|

| System Contro  | l Registers                                   |                                       |      | ,                    |

| 00             | Device Information, DEV_INFO                  | Device ID, revision                   | R    | 0000 0001            |

| 01             | Top Level Interrupt Status, TOP_INT           | Top level interrupt event status      | R/C  | 0000 0000            |

| 02             | Sub Level Interrupt_0, SUB_INT0               | Sub-level interrupt indication_0      | W/C  | 0000 0000            |

| 03             | Sub Level Interrupt_0 Mask, SUB_INT0_<br>MASK | Sub-level interrupt mask for SUB_INT0 | R/W  | 0011 1111            |

| 04             | Sub Level Interrupt_1, SUB_INT1               | Sub-level interrupt indication_1      | W/C  | 0000 0000            |

| 05             | Sub Level Interrupt_1 Mask, SUB_INT1_<br>MASK | Sub-level interrupt mask for SUB_INT1 | R/W  | 0111 1111            |

| 06             | Sub Level Interrupt_2, SUB_INT2               | Sub-level interrupt indication_2      | W/C  | 0000 0000            |

| 07             | Sub Level Interrupt_2 Mask, SUB_INT2_<br>MASK | Sub-level interrupt mask for SUB_INT2 | R/W  | 1111 1111            |

| 08             | RSVD                                          | Reserved                              | R/W  | 0000 0000            |

| 09             | Top Level Control_0, TOP_CNTL0                | Top level system control_0            | R/W  | 0100 0001            |

| 0A             | Top Level Control_1, TOP_CNTL1                | Top level system control_1            | R/W  | 1000 1001            |

| 0B             | Top Level Control_2, TOP_CNTL2                | Top level system control_2            | R/W  | 1100 1110            |

| 0C             | Top Level Control_3, TOP_CNTL3                | Top level system control_3            | R/W  | 0000 0001            |

| 0D             | Top Level Control_4, TOP_CNTL4                | Top level system control_4            | W    | 0000 0000            |

| 0E – 0F        | RSVD                                          | Reserved                              |      |                      |

| Battery Charge | er Control                                    |                                       | '    | ,                    |

| 10             | Battery Charger Control_0, CHG_CNTL0          | Battery charger control register_0    | R/W  | 0000 0011            |

| 11             | Battery Charger Control_1, CHG_CNTL1          | Battery charger control register_1    | R/W  | 0000 1000            |

| 12             | Battery Charger Control_2, CHG_CNTL2          | Battery charger control register_2    | R/W  | 0000 0100            |

| 13             | Battery Charger Control_3, CHG_CNTL3          | Battery charger control register_3    | R/W  | 0000 1000            |

| 14             | Battery Charger Control_4, CHG_CNTL4          | Battery charger control register_4    | R/W  | 0000 0100            |

| 15             | Battery Charger Control_5, CHG_CNTL5          | Battery charger control register_5    | R/W  | 0001 1110            |

| 16             | Battery Charger Control_6, CHG_CNTL6          | Battery charger control register_6    | R/W  | 1001 0101            |

| 17             | Battery Charger Control_7, CHG_CNTL7          | Battery charger control register_7    | R/W  | 0010 0100            |

# Power management IC for low-power microcontroller applications

Table 8. Register map...continued

| Address (Hex)  | Register Name                                      | Description                              | Туре     | Reset Value (Binary) |

|----------------|----------------------------------------------------|------------------------------------------|----------|----------------------|

| 18             | Battery Charger Status_0, CHG_<br>STATUS_0         | Battery charger status indication_0      | R        | 0001 0000            |

| 19             | Battery Charger Status_1, CHG_<br>STATUS_1         | Battery charger status indication_1      | R        | 0000 0000            |

| 1A             | Battery Charger Status_2, CHG_<br>STATUS_2         | Battery charger status indication_2      | R        | 0111 1000            |

| 1B             | Battery Charger Status_3, CHG_<br>STATUS_3         | Battery charger status indication_3      | R        | 0000 0000            |

| 1C – 1F        | RSVD                                               | Reserved                                 |          |                      |

| Regulator Cont | trol                                               |                                          | '        |                      |

| 20             | Regulator Status, REG_STATUS                       | Regulators status indication             | R        | 0000 0000            |

| 21             | Active Discharge Control, ACT_<br>DISCHARGE_CNTL_1 | Active Discharge control register        | R/W      | 0000 0000            |

| 22             | Mode Configuration Mode Setting 0_0, MODECFG_0_0   | Mode configuration settings for Mode 0_0 | R/W      | 0001 0100            |

| 23             | Mode Configuration Mode Setting 0_1, MODECFG_0_1   | Mode configuration settings for Mode 0_1 | R/W      | 0000 1100            |

| 24             | Mode Configuration Mode Setting 0_2, MODECFG_0_2   | Mode configuration settings for Mode 0_2 | R/W      | 0100 1111            |

| 25             | Mode Configuration Mode Setting 0_3, MODECFG_0_3   | Mode configuration settings for Mode 0_3 | R/W      | 0011 1001            |

| 26             | Mode Configuration Mode Setting 1_0, MODECFG_1_0   | Mode configuration settings for Mode 1_0 | R/W      | 0001 1100            |

| 27             | Mode Configuration Mode Setting 1_1, MODECFG_1_1   | Mode configuration settings for Mode 1_1 | R/W      | 0100 1100            |

| 28             | Mode Configuration Mode Setting 1_2, MODECFG_1_2   | Mode configuration settings for Mode 1_2 | R/W      | 0100 1111            |

| 29             | Mode Configuration Mode Setting 1_3, MODECFG_1_3   | Mode configuration settings for Mode 1_3 | R/W      | 0000 1100            |

| 2A             | Mode Configuration Mode Setting 2_0, MODECFG_2_0   | Mode configuration settings for Mode 2_0 | R/W      | 0001 1100            |

| 2B             | Mode Configuration Mode Setting 2_1, MODECFG_2_1   | Mode configuration settings for Mode 2_1 | R/W      | 0100 1100            |

| 2C             | Mode Configuration Mode Setting 2_2, MODECFG_2_2   | Mode configuration settings for Mode 2_2 | R/W      | 0100 1111            |

| 2D             | Mode Configuration Mode Setting 2_3, MODECFG_2_3   | Mode configuration settings for Mode 2_3 | R/W      | 0000 1100            |

| 2E             | Mode Configuration Mode Setting 3_0, MODECFG_3_0   | Mode configuration settings for Mode 3_0 | R/W      | 0001 1100            |

| 2F             | Mode Configuration Mode Setting 3_1, MODECFG_3_1   | Mode configuration settings for Mode 3_1 | R/W      | 0100 1100            |

| 30             | Mode Configuration Mode Setting 3_2, MODECFG_3_2   | Mode configuration settings for Mode 3_2 | R/W      | 0100 1111            |

| 31             | Mode Configuration Mode Setting 3_3, MODECFG_3_3   | Mode configuration settings for Mode 3_3 | R/W      | 0000 1100            |

| 71             | Reset monitor                                      | Reset reason monitor                     | R RO R/W | 1000 0000            |

Power management IC for low-power microcontroller applications

# 9.5 Register description

#### 9.5.1 Device information (DEV\_INFO, address 00h)

The device identification code stores a unique identifier for each version and/or revision of device, so that the connected MCU recognizes it automatically.

This is a READ ONLY register.

Table 9. DEV\_INFO register bit description

| Bit | Symbol      | Default value | Туре | Function        |

|-----|-------------|---------------|------|-----------------|

| 7   | DEV_ID [4]  | 0             | R    | Device ID       |

| 6   | DEV_ID [3]  | 0             | R    |                 |

| 5   | DEV_ID [2]  | 0             | R    |                 |

| 4   | DEV_ID [1]  | 0             | R    |                 |

| 3   | DEV_ID [0]  | 0             | R    |                 |

| 2   | DEV_REV [2] | 0             | R    | Device revision |

| 1   | DEV_REV [1] | 0             | R    |                 |

| 0   | DEV_REV [0] | 1             | R    |                 |

# 9.5.2 Top level interrupt status (TOP\_INT, address 01h)

The top-level interrupt register contains flags indicating various top level interrupt events as indicated below. An event will be latched and only its first occurrence triggers the interrupt signal INTB (if it is not being masked). Reoccurring events will not change the flag's status or trigger an additional interrupt. If multiple interrupt events happen, its corresponding interrupt bits in the related registers will be "triggered", however, the INTB signal will be only triggered upon the first interrupt event.

The interrupt event reporting on the device is structured in a two-layer configuration. The interrupt events are grouped as (1) system level; (2) charger block; (3) buck regulator block; (4) LDO block. When any interrupt event is triggered, based on which mode it falls into, the related bit for that mode in TOP\_INT flags "1". Any of the related bits in TOP\_INT will only change back to 0 when all the interrupt events in its affiliated mode have been cleared.

This is READ Only register.

Table 10. TOP\_INT register bit description

| Bit | Symbol  | Default value | Туре | Function                                                                                                                               |

|-----|---------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RSVD    | 0             | R    | Reserved bit                                                                                                                           |

| 6   | RSVD    | 0             | R    | Reserved bit                                                                                                                           |

| 5   | RSVD    | 0             | R    | Reserved bit                                                                                                                           |

| 4   | RSVD    | 0             | R    | Reserved bit                                                                                                                           |

| 3   | SYS_INT | 0             | R    | System level interrupt event trigger indication 0: no system level interrupt event triggered 1: system level interrupt event triggered |

## Power management IC for low-power microcontroller applications

Table 10. TOP\_INT register bit description...continued

| Bit | Symbol  | Default value | Туре | Function                                                                                                                                                                                 |

|-----|---------|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2   | CHG_INT | 0             | R    | Linear battery charger block interrupt event trigger indication  0: no linear battery charger block interrupt event triggered  1: linear battery charger block interrupt event triggered |

| 1   | SW_INT  | 0             | R    | Buck regulator blocks (SW1, SW2) interrupt event trigger indication 0: no interrupt event on SW1 and/or SW2 blocks triggered 1: interrupt event on SW1 and/or SW2 blocks triggered       |

| 0   | LDO_INT | 0             | R    | LDO block (LDO1, LDO2) interrupt event trigger indication 0: no interrupt event on LDO1 and/or LDO2 blocks triggered 1: interrupt event on LDO1 and/or LDO2 blocks triggered             |

# 9.5.3 Sub level interrupt\_0 (SUB\_INT0, address 02h)

The sub-level interrupt register contains flags indicating the second-tier interrupt event. For this register, it contains system level related interrupt events.

This is WRITE AND CLEAR register.

Table 11. Sub\_INT0 register bit description

| Bit | Symbol              | Default value | Туре | Function                                                                                                                                                                                                                |

|-----|---------------------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RSVD                | 0             | W/C  | Reserved bit                                                                                                                                                                                                            |

| 6   | RSVD                | 0             | W/C  | Reserved bit                                                                                                                                                                                                            |

| 5   | ON_PUSH_INT         | 0             | W/C  | ON falling edge longer than 5 ms happened                                                                                                                                                                               |

| 4   | TEMP_<br>PREWARNING | 0             | W/C  | Die temperature pre-warning interrupt  1: die temp ≥ TWARNING  0: die temp < TWARNING. TWARNING threshold is configured by T_WARNING [1:0]                                                                              |

| 3   | THEM_SHDN           | 0             | W/C  | Thermal shutdown interrupt 0: thermal shutdown is not triggered 1: die temp ≥ TSHDN (set in THEM_SHDN [2:0], thermal shutdown is triggered                                                                              |

| 2   | ASYS_<br>PREWARNING | 0             | W/C  | ASYS Pre-Warning Voltage Interrupt 0: ASYS voltage does NOT fall below the threshold set in ASYS_ PREWARNING [1:0] 1: ASYS voltage falls below the threshold set in ASYS_PREWARNING [1:0]                               |

| 1   | WD_TIMER            | 0             | W/C  | Watchdog Timer Expiration Interrupt 0: The watchdog timer expiration has not happened since the last time this bit was cleared. 1: The watchdog timer expiration has happened since the last time this bit was cleared. |

| 0   | IN_PWR              | 0             | W/C  | Input Voltage Interrupt  0: The IN_PWR bit has not changed since the last time this bit was cleared.  1: The IN_PWR bit has changed since the last time this bit was cleared.                                           |

Power management IC for low-power microcontroller applications

## 9.5.4 Sub level interrupt\_0 mask (Sub\_INT0\_Mask, address 03h)

This is a READ AND WRITE register.

Table 12. Sub\_INT0\_Mask bit description

| Bit | Symbol               | Default value | Туре | Function                                                             |

|-----|----------------------|---------------|------|----------------------------------------------------------------------|

| 7   | RSVD                 | 0             | R/W  | Reserved bit                                                         |

| 6   | RSVD                 | 0             | R/W  | Reserved bit                                                         |

| 5   | ON_PUSH_INT_MASK     | 1             | R/W  | ON Key falling interrupt mask bit 0: Not Masked 1: Masked            |

| 4   | TEMP_PREWARNING_MASK | 1             | R/W  | Die temp pre-warning interrupt mask bit 0: Not Masked 1: Masked      |

| 3   | THEM_SHDN_MASK       | 1             | R/W  | Thermal shutdown interrupt mask bit 0: Not Masked 1: Masked          |

| 2   | ASYS_PREWARNING_MASK | 1             | R/W  | ASYS Pre-Warning Voltage Interrupt Mask bit 0: Not Masked 1: Masked  |

| 1   | WD_TIMER_MASK        | 1             | R/W  | Watchdog Timer Expiration Interrupt Mask bit 0: Not Masked 1: Masked |

| 0   | IN_PWR_MASK          | 1             | R/W  | Input Voltage Interrupt Mask bit 0: Not Masked 1: Masked             |

# 9.5.5 Sub level interrupt\_1 (Sub\_INT1, address 04h)

The sub-level interrupt register contains flags indicating the second-tier interrupt event. For this register, it contains battery charger related interrupt events.

This is WRITE AND CLEAR register.

Table 13. Sub\_INT1 register bit description

| Bit | Symbol              | Default value | Type | Function                                                                                                                                                                                                                                                 |

|-----|---------------------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RSVD                | 0             | W/C  | Reserved bit                                                                                                                                                                                                                                             |

| 6   | ICHG_DEAD_TIMER_INT | 0             | W/C  | Dead charge timer expiration Interrupt  0: The dead charge timer expiration has not happened since last time this bit was cleared  1: The dead charge timer expiration has happened since last time this bit was cleared For more details, see Figure 10 |

| 5   | VIN_ILIM            | 0             | W/C  | Input Current Limit Interrupt 0: no Input current limit has been triggered since the last time this bit is cleared; 1: input current limit event is triggered since last time this bit is cleared.                                                       |

PCA9420

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2022. All rights reserved.

## Power management IC for low-power microcontroller applications

Table 13. Sub\_INT1 register bit description...continued

| Bit | Symbol            | Default value | Туре | Function                                                                                                                                                                                                                                                    |

|-----|-------------------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | ICHG_FAST_TIMER   | 0             | W/C  | Fast Charging Timer Expiration Interrupt  0: The fast charging timer expiration has not happened since the last time this bit was cleared.  1: The fast charging timer expiration has happened since the last time this bit was cleared.                    |

| 3   | ICHG_PREQ_TIMER   | 0             | W/C  | Pre-qualification Charging Timer Expiration Interrupt 0: The pre-qual charging timer expiration has not happened since the last time this bit was cleared. 1: The pre-qual charging timer expiration has happened since the last time this bit was cleared. |

| 2   | BATTERY_DETECTION | 0             | W/C  | Battery presence Interrupt  0: The VBAT_DET_OK bit has not changed since the last time this bit was cleared.  1: The VBAT_DET_OK bit has changed since the last time this bit was cleared.                                                                  |

| 1   | VBAT              | 0             | W/C  | Battery Interrupt 0: The VBAT_OK bit has not changed since the last time this bit was cleared. 1: The VBAT_OK bit has changed since the last time this bit was cleared.                                                                                     |

| 0   | CHG_OK            | 0             | W/C  | Charger Status Interrupt 0: The CHG_OK bit has not changed since the last time this bit was cleared. 1: The CHG_OK bit has changed since the last time this bit was cleared                                                                                 |

# 9.5.6 Sub level interrupt\_1 mask (Sub\_INT1\_Mask, address 05h)

This is a READ AND WRITE register.

Table 14. Sub\_INT1\_Mask register bit description

| Bit | Symbol                   | Default value | Туре | Function                                                                      |

|-----|--------------------------|---------------|------|-------------------------------------------------------------------------------|

| 7   | RSVD                     | 0             | R/W  | Reserved bit                                                                  |

| 6   | ICHG_DEAD_TIMER_INT_MASK | 1             | R/W  | Dead charge timer Interrupt Mask bit 0: Not Masked 1: Masked                  |

| 5   | VIN_ILIM_MASK            | 1             | R/W  | Input Current Limit Interrupt Mask bit 0: Not Masked 1: Masked                |

| 4   | ICHG_FAST_TIMER_MASK     | 1             | R/W  | Fast Charging Timer Expiration Interrupt Mask bit 0: Not Masked 1: Masked     |

| 3   | ICHG_PREQ_TIMER_MASK     | 1             | R/W  | Pre-qual Charging Timer Expiration Interrupt Mask bit 0: Not Masked 1: Masked |

## Power management IC for low-power microcontroller applications

Table 14. Sub\_INT1\_Mask register bit description...continued

| Bit | Symbol                 | Default value | Type | Function                                                    |

|-----|------------------------|---------------|------|-------------------------------------------------------------|

| 2   | BATTERY_DETECTION_MASK | 1             | R/W  | Battery presence Interrupt Mask bit 0: Not Masked 1: Masked |

| 1   | VBAT_MASK              | 1             | R/W  | Battery Interrupt Mask bit<br>0: Not Masked<br>1: Masked    |

| 0   | CHG_OK_MASK            | 1             | R/W  | Charger Interrupt Mask bit 0: Not Masked 1: Masked          |

# 9.5.7 Sub level interrupt\_2 (Sub\_INT2, address 06h)

The sub-level interrupt register contains flags indicating the second-tier interrupt event. For this register, it contains LDO1/LDO2, SW1/SW2 related interrupt events.

This is WRITE AND CLEAR register.

Table 15. Sub\_INT2 register bit description