I

## Advance Information Sandpoint Motherboard Technical Summary

This document describes the features of the "Sandpoint" Processor PCI Mezzanine Card (PPMC) host board. This board contains one PMC/PPMC-compatible slot, four PCI slots, and complement of standard PC motherboard logic such as an ISA bridge, serial, parallel, keyboard/mouse, floppy, and IDE disk controllers. Sandpoint is intended for hardware and software development and evaluation purposes only, and is not intended for operation in commercial environments.

This document contains the following topics:

| Торіс                                  | Page   |

|----------------------------------------|--------|

| Section 1.1, "Overview"                | page 2 |

| Section 1.2, "Description"             | page 2 |

| Section 1.3, "Reference Documentation" | page 3 |

| Section 1.4, "Glossary"                | page 3 |

| Section 1.5, "Board Layout"            | page 4 |

| Section 1.6, "Configuration"           | page 5 |

|                                        |        |

To locate any published errata or updates for this document, refer to the website at http://www.mot.com/SPS/PowerPC/.

This document contains information on a new product under development by Motorola. Motorola reserves the right to change or discontinue this product without notice.

© Motorola, Inc., 2000. All rights reserved.

PRELIMINARY-SUBJECT TO CHANGE WITHOUT NOTICE

## 1.1 Overview

The Sandpoint motherboard is an evaluation baseboard which accepts one processor PMC (PPMC) card as well as up to four PCI cards. Sandpoint provides a flexible base for the evaluation of the new PPMC architecture, as well as for hardware and software design for new-generation processors which have integrated PCI and memory controllers. The previous reference/evaluation platform, Yellowknife, could only support new devices which implement the 60X bus protocol, while Sandpoint can support 60X busbased devices as well as PCI-based devices (both through the design of PPMC cards).

Since the majority of the high-speed and processor-specific logic is relegated to the PPMC card, Sandpoint need only provide little more than a multi-slot PCI backplane and an ISA-based (PC-compatible) I/O system. As such, it should remain a stable environment for the evaluation of the next few generations of PowerPC processor devices, both integrated and desktop types. Future design efforts will therefore concentrate on processor-specific PPMC cards.

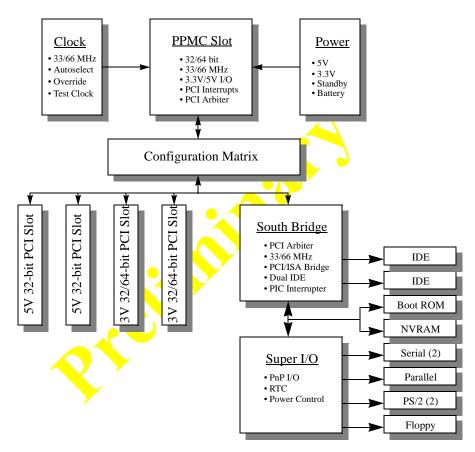

Figure 1-1 shows a block diagram of the Sandpoint system.

Figure 1-1. Sandpoint Block Diagram

## **1.2 Description**

The Sandpoint motherboard is a "host" board which accepts a PMC or PPMC card as well as up to four PCI cards. Sandpoint has the following features:

- One PMC slot with PPMC, 64-bit and 66 MHz extensions.

- Switch-selectable operating modes.

#### **Reference Documentation**

- Four PCI slots: 2 5V 32-bit slots, 2 3.3V 32/64-bit slots.

- PCI slots support 33 or 66 MHz operation.

- Two standard 16650-compatible ESD-protected serial ports.

- IEEE 1284 parallel port.

- Floppy disk port.

- Two IDE ports.

- PS/2 Mouse and keyboard connectors.

- NVRAM and real-time clock (RTC).

- Advanced Power Controller ("soft on/off").

- LED monitors for critical functions.

- Automatic sense of PCI bus speed (33 or 66 MHz).

The I/O subsystem is identical to that of "EC" version of the Yellowknife development platform, the current PowerPC evaluation platform. When properly configured, software written for the Yellowknife/EC platform should operate identically when executed on a Sandpoint.

### **1.3 Reference Documentation**

The following list describes reference documentation which may be of interest in understanding the operation of the Sandpoint:

| Document                                                                                    | Number/Reference                                                 |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Yellowknife Hardware Reference Manual                                                       | http://www.mot.com/SPS/PowerPC/teksupport/<br>index.html         |

| MPC8240 User's Manual                                                                       | Pending, contact Motorola Sale/FAEs for preliminary information. |

| Draft Standard Physical and Environmental Layers for Processor PCI<br>Mezzanine Cards: PPMC | Pending, contact Motorola Sale/FAEs for preliminary information. |

| PCI 2.1 Specification                                                                       |                                                                  |

| Draft Standard Physical and Environmental Layers for PCI Mezzanine<br>Cards: PMC            | IEEE P1386.1/Draft 2.0 04-APR-1995                               |

| Draft Standard for a Common Mezzanine Card Family: CMC                                      | IEEE P1386/Draft 2.0 04-APR-1995                                 |

#### Table 1-1. Reference Documentation

### 1.4 Glossary

The following list explains some terminology used in this document:

| Term | Definition                                                                                            |

|------|-------------------------------------------------------------------------------------------------------|

| РМС  | PCI Mezzanine Card a small form-factor PCI-compliant daughtercard standard.                           |

| РРМС | Processor-PCI-Mezzanine Card an extension to the IEEE1386 PMC standard adding host-related functions. |

## 1.5 Board Layout

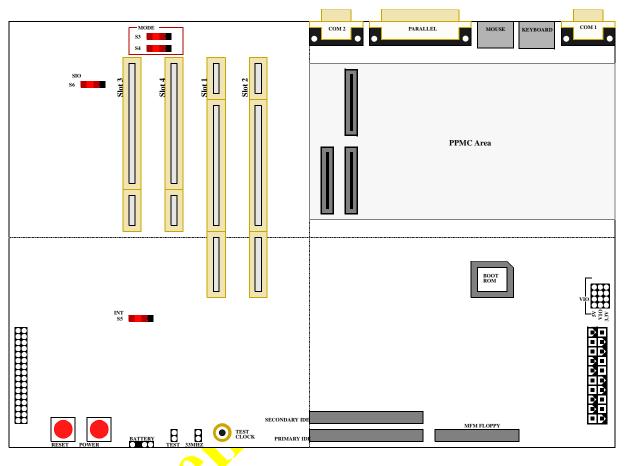

Figure 1-1 shows the physical layout of the Sandpoint board. The physical size is 245 cm x 305 cm (9.5 in. x 12.0 in.) and follows the physical size, mounting hole and I/O placement standards of an ATX motherboard.

#### Figure 1-1. Sandpoint Board Connectors and Jumpers

## **1.6 Configuration**

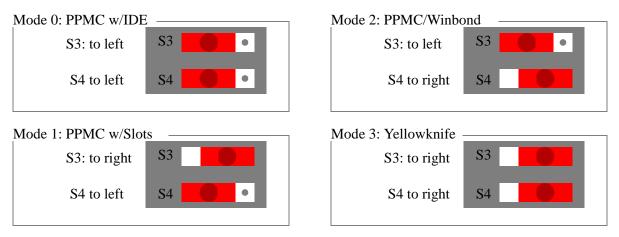

To support existing Yellowknife/PPMC software environments, as well as the new Sandpoint/PPMC environment, Sandpoint supports four different modes which are selectable via a pair of switches. Table 1-1 describes the modes.

| Mode    |   | Name                    | Description                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

|---------|---|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Default | 0 | PPMC Host with<br>IDE   | <u>PPMC Host Mode w/IDE support</u> : The PPMC slot is the system controller and provides arbitration and interrupt control. The Winbond IDE disk controllers replace slots 1 and 2 (3.3V PCI slots). The 5V PCI slots 3 and 4 are available. The on-board I/O shares interrupts with slots 2 or 3. |  |  |  |  |  |  |  |

|         | 1 | PPMC Host with<br>Slots | <u>PPMC Host Mode w/Four slot support</u> : The PPMC slot is the system controller and provides arbitration and interrupt control. The Winbond IDE disk controllers are unavailable. All slots are available. The on-board I/O shares interrupts with slots 2 or 3.                                 |  |  |  |  |  |  |  |

|         | 2 | PPMC/Winbond            | <u>PPMC/Winbond Mode</u> : The PMC slot is an agent, and the Winbond provides arbitration and interrupt control. The Winbond interrupt output drives the INTA pin of the PPMC slot.                                                                                                                 |  |  |  |  |  |  |  |

|         | 3 | Yellowknife             | <u>Yellowknife Mode</u> : The PPMC slot is an agent, and the Winbond provides arbitration and interrupt control. The Winbond interrupt output drives the $\overline{INTA}$ pin of the fourth PCI slot.                                                                                              |  |  |  |  |  |  |  |

#### Table 1-1. Sandpoint Modes

Which mode should be selected? The first two modes are the principal modes which will be used for new development, and can be selected between by deciding whether four PCI slots are needed or IDE is needed.

The latter two modes are intended as transitional settings, and may be used to aid conversion from a modified Yellowknife platform, where a PPMC is connected through a PMC->PCI adapter card. A modified Yellowknife system is identical to a Sandpoint operating in mode 3. Mode 2 is architecturally similar except that the adapter card may be eliminated. Mode 2 is also useful for early PPMC cards such as the PPMC750 which do not include a PCI arbiter, since the Winbond provides this feature; however, it requires hardware modification to the PPMC card (to convert an interrupt output to an input), so it is not recommended except for initial hardware evaluation.

In short, avoid using mode 3 and particularly mode 2 unless you have specific, short-term requirements such as porting software written for a different platform.

The Sandpoint board uses switches to select one of the four configuration choices. Logic on the Sandpoint host board switches the connections of the PCI request/grant signals, the PCI interrupt signals, and the component configuration modes (SYSCON, ARBDIS, etc.) to provide the required environment. Appendix A shows how the different signals on the motherboard are interconnected.

### **1.6.1** Configuration Switches

To select one of the modes shown in Table 1-1, ". Sandpoint Modes", set the two mode switches as shown in Figure 1-2.

### 1.6.2 Local I/O Interrupt Share Selection

PPMC cards support up to four interrupt sources. When operating in modes 0 or 1, there are a total of five possible interrupt sources (four slots and the Winbond PIC (handling the local I/O resources such as serial ports)). When on-board I/O is needed, it must be shared with or replace PCI devices in slot 2 or slot 3. Software must poll multiple sources to determine the interrupt source if both the slot and local I/O are needed; otherwise, the slot can be left unused or used with non-interrupting devices such as graphics cards.

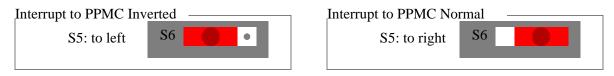

To select which slot replaces/shares interrupts with the Sandpoint local I/O, set the switch as shown in Figure 1-3. This switch setting is ignored when the board is configured in modes 2 or 3.

Figure 1-3. Shared Interrupt Selection Switch

### 1.6.3 Interrupt Polarity

Some PPMC cards, such as the PPMC8240, are configured with an active-high interrupt input when operated in the default configuration, which conflicts with PCI requirements. This is one example in which the MPC8240 is not quite identical to an MPC603+MPC106, so software moved as-is from the Yellowknife to the PPMC8240 will find interrupts are not working. The short-term work-around is to configure Sandpoint to invert the PMC interrupt signal; since this violates the specs, it is intended only for a short-term assistance; the correct solution is to program the EPIC of the MPC8240 to accept the correct polarity.

To invert the interrupt input of the PPMC slot, set the switch as shown in Figure 1-4.

Figure 1-4. Interrupt Inversion Switch

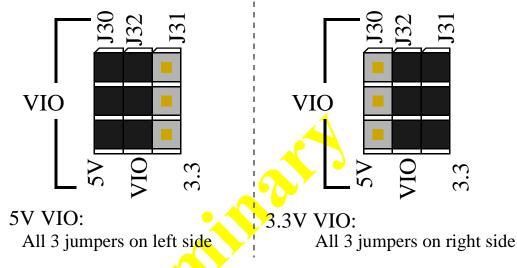

### 1.6.4 VIO Selection

Jumpers J30, J31 and J32 are used to set the I/O voltage signalling level for the PPMC card. As with PCI slots, the PPMC slot provides the ability to provide I/O power on certain pins, and compatibility is maintained using keying methods (for PCI slots, a key is present in the slot, while for PPMC slots, a keying pin protrudes from the motherboard into the PPMC card). For flexibility in testing purposes, Sandpoint allows any type of VIO-keyed board to be installed, with the proper VIO selected by jumpers J30-J32.

- **NOTE**: This flexibility requires that the Sandpoint be configured to match the PPMC card before powering up.

- **NOTE**: All three jumpers must be set in an identical fashion; if any are different, the power supply will short and the board can be damaged or destroyed.

- Set the jumpers as shown in Figure 1-5 to match the PPMC card which will be installed in the PPMC slot.

Figure 1-5. VIO Jumper Selection

### 1.6.5 33MHZ PCI Force

If jumper J34 is installed, the PCI bus will operate at 33 MHz regardless of the status of the M66EN signal. The PCI bus ordinarily selects 66 MHz operation if (and only if) all PPMC and PCI devices installed support 66 MHz clock rates; otherwise, the slower 33 MHz rate is used. However, for testing purposes, this jumper may be used to evaluate slower bus clock rates. In addition, it may be needed for systems using 66 MHz capable cards which also wish to use the Winbond or on-board I/O. Since these devices operate at 33 MHz only, yet do not have an M66EN pin to control clock selection, jumper J34 is required to force the PCI bus to operate at 33 MHz.

### **1.6.6 Test Clock Enable**

If jumper J33 is installed, the on-board 66 MHz oscillator is disabled and an external clock source is used to drive the PCI bus. The signal provided must be 3.3V LVTTL logic levels into a 50<sup>3</sup>/<sub>4</sub> load. The input clock is supplied as-is, or divided by two, depending upon the state of the M66EN (66MHz PCI) status and the 33MHz force jumper (see 1.6.5, "33MHZ PCI Force").

Care must be used that the devices receiving the clock are capable of and are configured to operate at the new clock speed. In particular, PowerPC devices have internal PLLs which require a minimum clock input to operate properly.

## **1.7 Interrupt Configuration**

The following table describes the interrupt sources seen by the PMC when the Sandpoint has been configured for mode 0. This is the default configuration, and assumes that the on-board I/O interrupt is shared with slot 1 (also the default).

|        | PMC Inter<br>INT | -      |        | Description                                                                                               |

|--------|------------------|--------|--------|-----------------------------------------------------------------------------------------------------------|

| 0      | 1                | 2      | 3      |                                                                                                           |

| Slot 1 | Slot 2           | Slot 3 | Slot 4 | Each slot's primary interrupt output (INTA) is routed to a corresponding interrupt input on the PMC card. |

| INTA   | INTA             | INTA   | INTA   |                                                                                                           |

| Slot 2 | Slot 3           | Slot 4 | Slot 1 |                                                                                                           |

| INTB   | INTB             | INTB   | INTB   |                                                                                                           |

| Slot 3 | Slot 4           | Slot 1 | Slot 2 |                                                                                                           |

| INTC   | INTC             | INTC   | INTC   |                                                                                                           |

| Slot 4 | Slot 1           | Slot 2 | Slot 3 |                                                                                                           |

| INTD   | INTD             | INTD   | INTD   |                                                                                                           |

|        | SIOINT           |        |        | On-board I/O interrupts are shared with "Slot 2" by default.                                              |

| Table 1-1. | Sandpoint | Interrupt | Connection | (Mode 0 Only)    |

|------------|-----------|-----------|------------|------------------|

|            | our point |           | 00111000   | (1120000000000)) |

### **1.8 PCI Slot Information**

The following table describes the PCI slot information of the Sandpoint host board. This information is constant for any mode selected. The following table shows the "Type 0" configuration cycles as used for Map A or Map B.

| PCI Slot/<br>Device | Physical Location     | Configuration<br>IDSEL | Configuration<br>Address | Note                                                                                                                                        |

|---------------------|-----------------------|------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Winbond             | N/A                   | AD11                   | 0x8000_58XX              |                                                                                                                                             |

| РМС                 | PMC                   | AD12                   | 0x8000_60XX              | The PMC device should not issue configuration<br>cycles to itselt. Sandpoint does not prevent this, but it<br>is a undefined PCI operation. |

| 1                   | Second-nearest<br>PMC | AD13                   | 0x8000_68XX              |                                                                                                                                             |

| 2                   | Nearest PMC           | AD14                   | 0x8000_70XX              | ALL the slots are mis-labeled on Sandpoint X2;                                                                                              |

| 3                   | Furthest from<br>PMC  | AD15                   | 0x8000_78XX              | the actual ordering is 2-1-4-3 (from the PMC outward).                                                                                      |

| 4                   | Third from PMC        | AD16                   | 0x8000_80XX              |                                                                                                                                             |

| Table 1 1 C  | andnoint | DCT CI | at/Davia  | Information |

|--------------|----------|--------|-----------|-------------|

| 1 able 1-1.5 | anabomit |        | ou/Device | Information |

|              |          |        |           |             |

# **Appendix A: Interconnection Diagram**

The following diagram shows the connections established between the PPMC card, the PCI slots, and the WinBond for various modes.

|      |        | Interconnections |               |               |               |               |               |               |               |               |               |               |               |              |              |              |               |              |              |              |              |              |               |               |               |               |              |        |

|------|--------|------------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|--------------|---------------|--------------|--------------|--------------|--------------|--------------|---------------|---------------|---------------|---------------|--------------|--------|

| Mode | NO     | РМС              |               |               |               |               |               |               |               | PCI Slots     |               |               |               |              |              |              |               | WinBond      |              |              |              |              |               |               |               |               |              |        |

| Mo   | SYSCON |                  | PMC_          | REQ           |               |               | PMC_INT       |               |               | SLOT_REQ      |               |               |               | SLOT_INT     |              |              |               | WB_REQ       |              |              |              | CPUREQ       | WB_INT        |               |               |               | r            | DIS    |

|      |        | 0                | 1             | 2             | 3             | 0             | 1             | 2             | 3             | 0             | 1             | 2             | 3             | 0            | 1            | 2            | 3             | 0            | 1            | 2            | 3            | CPUI         | 0             | 1             | 2             | 3             | INI          | ARBDIS |

| 0    | 0      | $\Rightarrow$    | ⇒             | $\Rightarrow$ | ⇒             |               |               |               |               |               |               | ⇐             | $\downarrow$  |              |              |              |               | $\downarrow$ | ĥ            |              |              |              |               |               |               |               |              | 0      |

|      |        |                  |               |               |               | $\Rightarrow$ | $\uparrow$    | $\Rightarrow$ | $\Rightarrow$ |               |               |               |               |              |              | $\Leftarrow$ | $\downarrow$  |              |              |              |              |              | $\downarrow$  | Ų             |               |               |              |        |

|      |        |                  |               |               |               |               |               |               |               |               |               |               |               |              | ?=           | >            |               |              |              |              |              |              |               |               |               |               | ĥ            |        |

| 1    | 0      | $\Rightarrow$    | $\Rightarrow$ | $\Rightarrow$ | $\Rightarrow$ |               |               |               |               | $\downarrow$  | $\downarrow$  | $\downarrow$  | $\downarrow$  |              |              |              |               |              |              |              |              |              |               |               |               |               |              | 0      |

|      |        |                  |               |               |               | $\Rightarrow$ | $\Rightarrow$ | $\Rightarrow$ | $\Rightarrow$ |               |               |               |               | ¢            | $\Leftarrow$ | ¢            | $\Leftarrow$  |              |              |              |              |              |               |               |               |               |              |        |

|      |        |                  |               |               |               |               |               |               |               |               |               |               |               |              | ?=           | >            |               |              |              |              |              |              |               |               |               |               | ⇐            |        |

| 2    | 1      | $\Rightarrow$    |               |               |               |               |               |               |               |               |               |               |               |              |              |              |               |              |              |              |              | $\leftarrow$ |               |               |               |               |              | 1      |

|      |        |                  |               |               |               |               |               |               |               | $\Rightarrow$ | $\Rightarrow$ | $\Rightarrow$ | $\Rightarrow$ |              |              |              |               | $\downarrow$ | $\Leftarrow$ | $\leftarrow$ | $\Leftarrow$ |              |               |               |               |               |              |        |

|      |        |                  |               |               |               |               |               |               |               |               |               |               |               | $\Downarrow$ | $\downarrow$ | ¢            | $\downarrow$  |              |              |              |              |              | $\Rightarrow$ | $\Rightarrow$ | $\Rightarrow$ | $\Rightarrow$ |              |        |

|      |        |                  |               |               |               | $\Rightarrow$ |               |               |               |               |               |               |               |              |              |              |               |              |              |              |              |              |               |               |               |               | $\downarrow$ |        |

| 3    | 1      | $\Rightarrow$    |               |               |               |               |               |               |               |               |               |               |               |              |              |              |               |              |              |              |              | $\Leftarrow$ |               |               |               |               |              | 1      |

|      |        |                  |               |               |               |               |               |               |               | ⇒             | $\Rightarrow$ | $\Rightarrow$ | ⇒             |              |              |              |               | ¢            | ¢            | $\downarrow$ | ¢            |              |               |               |               |               |              |        |

|      |        |                  |               |               |               |               |               |               |               |               |               |               |               | $\downarrow$ | $\downarrow$ | $\Leftarrow$ |               |              |              |              |              |              | $\Rightarrow$ | $\Rightarrow$ | $\Rightarrow$ |               |              |        |

|      |        |                  |               |               |               |               |               |               |               |               |               |               |               |              |              |              | $\Rightarrow$ |              |              |              |              |              |               |               |               |               | $\downarrow$ |        |

#### Table 0-1. Configuration Matrix

- 1. The symbol  $\Rightarrow$  denotes an input, ? $\Rightarrow$  denotes a selectable (choose one) input, and  $\Leftarrow$  denotes an output.

- 2. Request (\*REQ) and grant (\*GNT) signals are routed as pairs. Only requests are shown to minimize (ha!) confusion. Grant signals are connected in the same manner as requests but in a reverse direction (viz., for every \*REQ output there is a matching \*GNT input).

- 3. Bus numbering is preserved from input to output unless otherwise noted. For example, in the first line of the table, <u>PMC\_REQ(0)</u> is connected to <u>WB\_REQ(0)</u>, while <u>PMC\_REQ(3)</u> is connected to <u>SLOT\_REQ(3)</u>.

- 4. If an input is not shown as connected to anything, it is pulled up and unused. Outputs are ignored.

Mfax is a trademark of Motorola, Inc.

The PowerPC name, the PowerPC logotype, and PowerPC 603e are trademarks of International Business Machines Corporation used by Motorola under license from International Business Machines Corporation.

Information in this document is provided solely to enable system and software implementers to use PowerPC microprocessors. There are no express or implied copyright licenses granted hereunder to design or fabricate PowerPC integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### Motorola Literature Distribution Centers:

USA/EUROPE: Motorola Literature Distribution; P.O. Box 5405; Denver, Colorado 80217; Tel.: 1-800-441-2447 or 1-303-675-2140; World Wide Web Address: http://ldc.nmd.com/

JAPAN: Nippon Motorola Ltd SPD, Strategic Planning Office 4-32-1, Nishi-Gotanda Shinagawa-ku, Tokyo 141, Japan Tel.: 81-3-5487-8488

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd Silicon Harbour Centre 2, Dai King Street Tai Po Industrial Estate Tai Po, New Territories, Hong Kong

Mfax<sup>TM</sup>: RMFAX0@email.sps.mot.com; TOUCHTONE 1-602-244-6609; US & Canada ONLY (800) 774-1848; World Wide Web Address: http://sps.motorola.com/mfax INTERNET: http://motorola.com/sps

Technical Information: Motorola Inc. SPS Customer Support Center 1-800-521-6274; electronic mail address: crc@wmkmail.sps.mot.com. Document Comments: FAX (512) 895-2638, Attn: RISC Applications Engineering. World Wide Web Addresses: http://www.motorola.com/PowerPC

http://www.motorola.com/netcomm http://www.motorola.com/Coldfire